# Bonding of Multi-Functional Fiber to a Micro-fabricated Robotic Appendage for Use in Biologic Environments

A. Parrott<sup>2</sup>\*, J. Pelster<sup>1</sup>\*, Y. Liu<sup>2</sup>, Y. Zhang<sup>2</sup>, H. Huang<sup>2</sup>, J. Kim<sup>2</sup>, Q. Liu<sup>1</sup>, X. Jia <sup>2</sup>, I. Cohen <sup>1</sup>

Cornell University, Ithaca, NY, USA

<sup>2</sup>Virginia Tech, Blacksburg, VA, USA

Abstract— A bonding method combining two distinct technologies, flexible multifunctional, multi-electrode fibers [1] and robotic appendages that make use of electrochemical actuators [2], is demonstrated, showing successful operation in phosphate buffer solution (PBS). The resulting robotic fibers were  $\sim\!300\,\mu\mathrm{m}$  in diameter allowing us to shrink state of the art surgical tools by nearly an order of magnitude. This technique was demonstrated for two robotic prototypes, one in a gripper formation, and one in a sensor formation. These two distinct designs, when connected to a fiber, open the door to many new techniques for neural tissue biopsy and chronic neural recording with minimal damage to surrounding tissue.

#### I. INTRODUCTION

Thermally drawn, polymer based fibers have become an important technology for applications requiring sensing and stimulation via optical, chemical, and electrical signals. For example, they have been shown to be very effective as biocompatible multi-functional neural devices capable of optical stimulation, drug delivery, and electric recording. In contrast to many rigid neuroprobes [3]-[5], fibers are flexible and enable chronic recording over long time periods. Despite their utility, however, once inserted, fibers remain rather limited in their ability to mechanically manipulate their environments beyond rudimentary operations such as spatial expansion [6], [7]. Here, we show that recent developments in microscopic robotics can be harnessed to vastly increase the mechanical manipulation capabilities of such fibers. Microscopic robots are lithographically fabricated in 2D and folded via electrochemical µ-actuators [8] to adopt their final 3D shapes and enable actuations. This technology has been used to demonstrate a variety of self-folding origami shapes ranging from Miura Ori to birds [2], autonomous walking robots [9], and artificial cilia [10], all at the 100 µm scale. Our idea is simple. We aim to use conducting wires embedded in fibers to drive and control simple actuations of a robot bonded to a fiber's tip. Our ultimate goal is to develop surgical tools that are an order of magnitude smaller than those currently available.

#### II. DEVICE FABRICATION

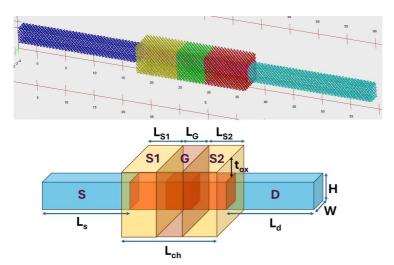

The robotic fiber is composed of two elements, a fiber that allows for in vivo implantation and can transmit electrical control signals and a fabricated microscopic robotic attachment with movable appendages.

#### A. The Fiber

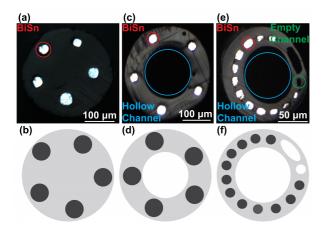

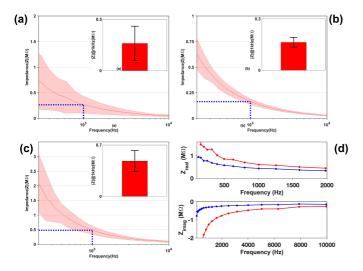

The fiber portion of the device is fabricated using a threestep process: 1) fabrication of a fiber preform; 2) a macroscopic thermal drawing process [1]; 3) followed by a precise thermal tapering process [7]. The fiber preform is fabricated with channels that are filled with BiSn. This preform is drawn into thin fibers using the thermal drawing and thermal tapering processes. The final fibers have a large backend, approximately 2mm in diameter, and a micron scale tip, approximately 300 um in diameter (Fig. 1 and 2). Three designs were used to demonstrate the bonding capabilities: five electrode BiSn with a solid core, five electrode BiSn with a hollow core, and high electrode count of BiSn with a hollow core, (Fig. 3). The hollow channel can be used for integration of additional sensors, delivery of chemicals, or for storing medical epoxy to aid in strengthening the bonding process with the robotic appendage. The electrochemical impedance spectrum (EIS) is measured for each design to ensure the impedance is optimal for control signals to be sent to the robot (Fig. 9).

#### B. The Robotic Appendage

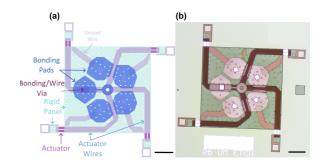

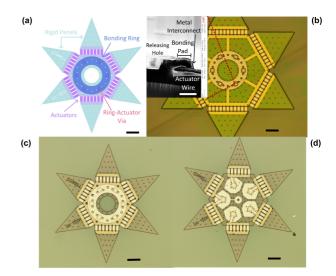

The robotic appendage is composed of a rigid panel that contains bonding pads for connecting to the fiber as well as signal wires that connect to the actuating appendages. The layout for the two devices is shown in Fig. 4 and 5. The actuators are fabricated using a process similar to that described in [2]. Briefly, they consist of a nanometer thin metal layer such as Pt that under an applied voltage can absorb ions from solution and expand. This metal layer is bonded to an insulating layer such as Ti to form a bimorph. When the metal layer expands, the bimorph bends. Rigid panels composed of approximately 3 µm Si3N4 restrict the actuation so that bending occurs along fold lines. A 100 nm insulation layer also composed of Si3N4 prevents electrochemical reactions from occurring on the signal wire during actuation. Finally, we fabricate a metallic bonding layer on top of the rigid panels that connects to the wires through vias as shown in Fig. 4. The chip is then diced into individual devices using a DISCO dicing saw. The entire robot is fabricated on a fused silica wafer coated with approximately 180 nm AIN and 40 nm Al2O3. These two coatings act as a releasing layer, allowing the fabricated devices to be removed from the microfabricated robot before bonding to the fiber.

#### C. Connection Design

The individual connection pads were designed to allow the maximum area for bonding and increase alignment tolerance. A distance of 5  $\mu m$  is kept between the individual bonding pads to prevent signal contamination from other channels and shorting. While the ring connection pad allows easier alignment during bonding at the cost of individual actuator movement. In the current formulation, the fiber is composed of 5 wires, equispaced in a circle of diameter 300  $\mu m$ , with BiSn wires  ${\sim}40~\mu m$  in diameter.

#### III. BONDING METHOD

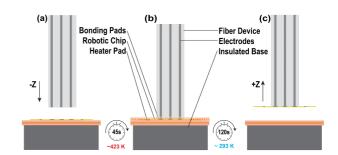

The microfabricated robotic appendage is cleaned using standard methods and then submersed in 2.38% tetramethyl ammonium hydroxide (TMAH) to etch away the release layer and remove the device from the substrate. After a final cleaning, the robotic appendage is then moved to a polyimide substrate sitting on an insulated flexible heater strip. The fiber is then aligned via a customized multidirectional manipulator. The manipulator controls the X, Y, Z, and theta alignment for the fiber and, when combined with a microscope, allows for a precise alignment. Once the alignment is complete, the fiber is lowered onto the bonding pads allowing for good contact with the heater strip (Fig. 6). The voltage source is set at 7.5 V for 45 seconds when using the solid core fiber and 35 seconds when using the hollow core fiber. In this process, the heater reaches a temperature of ~423 K allowing the BiSn to melt onto the bonding pad and for the polycarbonate to spread onto the robotic base. The now connected devices are left to cool down for 2 minutes before lifting off the substrate. At this point, the fiber and robotic appendage are bonded and can be tested in solution (Fig. 7 and 8).

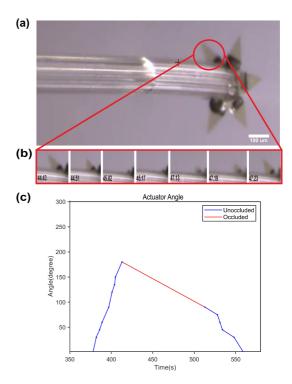

#### IV. ACTUATION IN SOLUTION

We tested two robot prototypes: a neural probe and a biopsy tool. Actuation and electrochemical impedance spectrum tests were conducted in phosphate buffer solution (PBS), shown in Fig. 10 and Fig. 11. Actuation tests were conducted using Gamry Virtual Front Panel Software with the single point function, to apply a fixed potential, or using Gamry Framework with the cyclic voltammetry function, for sweeping through a voltage range. The EIS test was conducted using the Gamry Framework software and analyzed at 1 kHz. For the neural probe actuation, we used the solid core fiber coated with a thin layer of medical epoxy. The device was submerged in a petri dish of PBS with an Ag/AgCl reference electrode and a platinum counter electrode. A cyclic voltammogram was chosen to cycle through -1.2V and 0.6V at a rate of 50 mV/s. This voltage sweep allowed for the neural probe actuator arms to sweep through their range of motion, as seen in Fig. 10. For the gripper probe actuation, the hollow core BiSn design was used since it did not need epoxy for a stronger connection due to the thin polycarbonate side walls heating faster and conforming to the microfabricated robot more reliably than the solid core fiber. The gripper actuation demonstration (Fig. 11) utilizes a high electrode count fiber with a hollow core; this

configuration reduced the error associated with misalignment with the robot design containing 5 bonding pads as opposed to a bonding ring. After connection, the device is moved to a petri dish filled with PBS where it is lowered into solution. Using an Ag/AgCl reference electrode and platinum counter electrode, a single point voltage was applied and cycled manually through -1.2V and 0.6V; this method of voltage cycling allows for a longer period of time at each voltage before stepping to the next. These exciting results demonstrate our ability to bond microfabricated robotic appendages to fibers and, through electrical wires embedded in the fibers, control their actuation.

#### V. CONCLUSION

By successfully marrying state of the art fiber and microscopic robot technologies we have developed a new powerful platform for microscopic manipulation in tissues. The proof of concept actuation of multiple robotic designs demonstrated here could for example enable applications ranging from improved omnidirectional neural recording to minimally invasive neural tissue biopsy for potentially cancerous tumors for diagnosis. The different fiber designs show that successful bonding can be achieved without jeopardizing the multiple fiber functionalities, which will allow for new device development. For example, the center hollow channel design, when combined with mechanical functions such as robotic grippers, allows for device designs that, through fluid exchange, can chemically sense or stimulate as desired and then extract a desired tissue sample. As such, these demonstrations represent a critical step for miniaturization of surgical tools to the 100 µm scale.

#### ACKNOWLEDGMENT

We gratefully acknowledge funding support from the National Institute of Health (R21EY033080).

- A. Canales et al., "Multifunctional fibers for simultaneous optical, electrical and chemical interrogation of neural circuits in vivo," *Nature biotechnology*, vol. 33, no. 3, pp. 277–284, 2015.

- [2] Q. Liu et al., "Micrometer-sized electrically programmable shapememory actuators for low-power microrobotics," Science Robotics, vol. 6, no. 52, p. eabe6663, 2021.

- [3] J. J. Jun et al., "Fully integrated silicon probes for high-density recording of neural activity," *Nature*, vol. 551, no. 7679, pp. 232–236, 2017.

- [4] N. A. Steinmetz et al., "Neuropixels 2.0: A miniaturized high-density probe for stable, long-term brain recordings," *Science*, vol. 372, no. 6539, p. eabf4588, 2021.

- [5] C. M. Lopez *et al.*, "A neural probe with up to 966 electrodes and up to 384 configurable channels in 0.13 μm SOI CMOS," *IEEE Trans. Biomed. Circuits Syst.*, vol. 11, no. 3, pp. 510–522, 2017.

- [6] S. Jiang et al., "Spatially expandable fiber-based probes as a multifunctional deep brain interface," *Nature communications*, vol. 11, no. 1, p. 6115, 2020.

- [7] J. Kim et al., "T-dope probes reveal sensitivity of hippocampal oscillations to cannabinoids in behaving mice," Nature Communications, vol. 15, no. 1, p. 1686, 2024.

- [8] M. Z. Miskin et al., "Electronically integrated, mass-manufactured, microscopic robots," Nature, vol. 584, no. 7822, pp. 557–561, 2020.

- [9] M. F. Reynolds et al., "Microscopic robots with onboard digital control," Science Robotics, vol. 7, no. 70, p. eabq2296, 2022.

- [10] W. Wang et al., "Cilia metasurfaces for electronically programmable microfluidic manipulation," *Nature*, vol. 605, no. 7911, pp. 681–686, 2022.

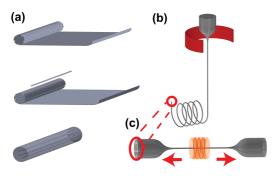

Fig. 1. (a) Fiber fabrication starts with rolling a macroscale preform with 5 channels milled into the polycarbonate and filled with BiSN ( $\sim$ 28 mm in diameter). (b) After thermal drawing, the preform is drawn to a minipreform ( $\sim$ 2 mm in diameter) and cut into 10 mm long segments. (c) Minipreforms then undergo thermal tapering, resulting in a device with a large backend for connections and a small interface for implantation.

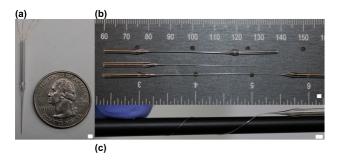

Fig. 2. (a) Copper backend connections in the tapered fiber device next to a quarter. (b) Top device is an uncut 5 electrode hollow core fiber, the middle device is a cut 5 electrode solid core fiber, and the bottom device is an uncut 5 electrode solid core fiber. (c) Tapered fiber wrapped around rod to demonstrate flexibility. Scale bars are 2 mm.

Fig. 3. (a) Optical image of 5 BiSn electrode solid core fiber cross section. (b) Ideal schematic of 5 electrode, solid core fiber cross section. (c) Optical image of 5 BiSn hollow core fiber cross section. (d) Ideal schematic of 5 electrode, hollow core fiber cross section. (e) Optical image of high electrode count fiber containing a hollow channel, 12 electrodes, and 2 empty channels for housing epoxy. (f) Ideal schematic of high electrode count fiber cross section.

Fig. 4. (a) Schematic of neural probe chip base showing bonding pads with wire vias, actuator wires, actuators, rigid panels connecting to movable actuators creating arm like structures. (b) Optical microscope image of microrobotic neural probe. Scale bars are  $100~\mu m$ .

Fig. 5. (a) Schematic of robotic gripper chip base design showing ring shaped bonding pad with actuator vias, actuators, and rigid panels to form movable arms. Scale bar is 100  $\mu$ m. (b) Optical image of microrobotic gripper design with wider actuator arms and SEM image showing various layers. Scale bar is 5  $\mu$ m. (c) Optical image of microrobotic gripper with ring bonding pad. Scale bar is 100  $\mu$ m. (d) Optical image of microrobotic gripper with 5 bonding pads. Scale bar is 100  $\mu$ m.

Fig. 6. Schematic of fiber to microscopic robot bonding process. (a) Fiber is lowered onto the microscopic robot base sitting on a thermal heater pad. (b) Once alignment is completed and the fiber is lowered onto the robot, the thermal pad is heated to  $\sim$ 423 K for 45 seconds by utilizing a voltage source set to 7.5V. After 45 seconds, the device is left to cool for 120 seconds until it returns to room temperature. (c) Once bonded, the robotic fiber is lifted off of the thermal heating pad.

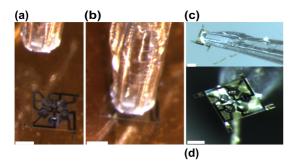

Fig. 7. Pre (a) and Post (b) bonding images for microrobotic neural probe connection to fiber device. (c) Bonded device from chip side and (d) Bonded device from fiber side. Scale bars are 200  $\mu m$ .

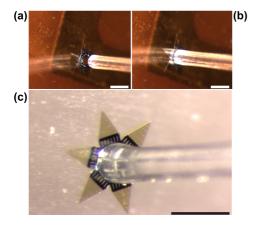

Fig. 8. Pre (a) and Post (b) bonding images for microrobotic gripper show successful bonding to fiber device. (c) Bonded device from fiber side. Scale bars are  $500 \mu m$ .

Fig. 9. (a) EIS plot for solid core fibers with shaded area and error bar representing standard deviation, n=4. (b) EIS plot for high electrode count fibers with shaded area and error bar representing standard deviation, n=4. (c) EIS plot for hollow core fibers with shaded area and error bar representing standard deviation, n=4. For each plot, the red line indicates the mean impedance and the blue signifies the 1.004 kHz impedance. (d) EIS Pre and Post bonding high electrode count fiber to microrobotic gripper base. The red plot shows the before bonding EIS and the blue plot shows the post bonding for the magnitude (upper) and phase (bottom). The decreased impedance indicates good electrical connections post bonding.

Fig. 10. (a) Bonded Neural Probe device. (b) Series of images showing actuator movement. (c) Actuation angle change versus time. Blue region represents the segment visible during actuation while the red region represents the occluded segment of actuation.

Fig. 11. (a) Bonded Gripper Probe device (b) Series of images showing actuator movement. (c) Plot of actuation angle change versus time. Blue area shows the angles that were visible during actuation while the red area represents the occluded segment of the actuation.

# Implementation of double-side calibration and probing for Q-band 50GHz system application

Chia-Chu Lai<sup>1</sup>, Sam Lin, Teny Shih, Andrew Kang, and Yu-Po Wang Siliconware Precision Industries Co., Ltd., email: <sup>1</sup>chiachulai@spil.com.tw

Abstract—The double-side calibration and measurement on probing system for single-end GSG (Ground-Signal-Ground) and differential pairs GSSG (Ground-Signal-Signal-Ground) type is presented in this paper. Calibration is the most important procedure before measurement due to it is used to remove the effect of cable and RF probe, and then extract the performance of DUT purely. The common calibration kit in the market is including below patterns: Open, Short, Load, and Thru for SOLT/SOLR standard calibration method, but there is still no standard thru/reciprocal pattern for double-side measurement system at present, therefore we design a reciprocal kit which is applicable for GSG-150um and GSGSG-150um RF probe and the frequency is up to 60GHz.

The reciprocal pattern is designed in the 4-layer stack up and simulated in ANSYS HFSS environment, the return loss is under -10dB for all 60GHz frequency range, and the insertion loss is -0.6dB at 60GHz. The actual measurement results after calibration with SOLR showed -10dB of the return loss under 60GHz, and -1dB of insertion loss at 60GHz. Finally, we successfully calibrated the double-side differential system by the reciprocal kit in Q-band 50GHz and also measured the two transmission lines with total 36mm length. First transmission line is all built in one layer, and the second one is divided in two layers. The measurement result showed the trace in one layer is better about 0.56dB@30GHz.

#### I. INTRODUCTION

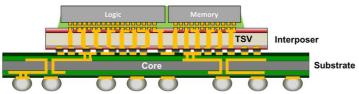

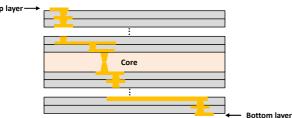

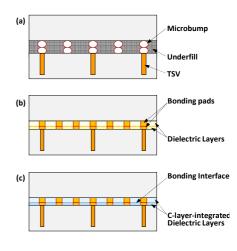

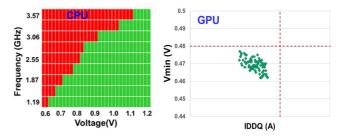

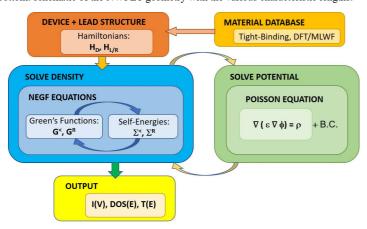

Recently, there are a lot of discussions about advanced packaging technology below 7nm process node. Especially driven by the application for artificial intelligence (AI) application, the demand for the GPU die is continuing to rise up those results in demand exceeds provision. Especially the advanced packaging CoWoS (Chip on Wafer on Substrate) is mainly suitable for the GPU. Fig.1 is the schematic diagram of the CoWoS package. Connect the logic chip and the High Band Memory (HBM) chip on the interposer by the u-bumps, and integrate the signal between logic chip and HBM chip by the RDL, and connect down to the substrate through TSVs and u-bumps, and finally go to the position of the bottom ball through the metal layers, vias, and core vias. The interfaces of the vertical interconnect are including the u-bumps, TSVs, vias, and the PTHs in a package substrate. It is interesting to understand the effect of these interface, but the double-side measurement is the challenging over a wide range of frequencies.

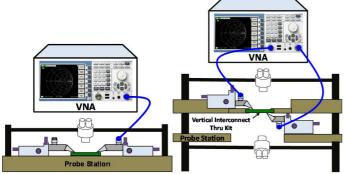

The common configuration of frequency measurement system is composed of a probe station and a VNA (Vector Network Analyzer) instrument which is shown in Fig.2. The probe station is to load the wafer or DUT board and the VNA is specialized for high frequency power sweep. Before starting the DUT test, we must do the calibration step to eliminate the noise and effect of the cable and probe, and then extract the pure characterization of DUT. And the calibration kit in the market is ready for single-side probe but not for double-side probe. The main key point is there is no standard Thru kit for double-side calibration. Therefore, some literatures descript different structures of the Thru kit, for example, the first is Thru kit with non-contact technology [1], the second is developing a whole double-side probe system and design a via in 2-layer PCB as a Thru kit [2], the third is design a paralleled and a diagonal Thru kit in only a layer PCB structure to implement differential double-side calibration [3].

In this paper, we organized as follows. Section II presents the different calibration methods and the design conception of the calibration Thru kit. Section III gives the measurement results for the calibration Thru Kit and the differential transmission lines which are built in 22-layer substrate. Finally, a conclusion is given in Section IV.

#### II. Double-Side Calibration

#### A. Calibration Method

There are many calibration choices. The common probing calibration is SOLT and SOLR. For SOLT (Short-Open-Load-Thru), it is very simple and not band-limited, but requires very well-defined standards. For SOLR (Short-Open-Load-Reciprocal), the advantages are the same as SOLT but it doesn't need very good for the thru line with symmetrical type. For SSST (Short-Short-Thru), the advantages are the same as SOLT but it has better accuracy at higher frequency. For LRL/TRL (Line-Reflect-Line), the advantages are the highest accuracy and minimal standard definition, but it requires very good transmission lines. The total comparison with different calibration is arranged in Table I. In this paper, we chose the SOLR to calibrate the measurement system due to the thru line is no need very well performance. The short, open, and load kits are using the standard calibration kit and the design conception is descripted in next portion.

#### B. Design Conception of the Thru Kit

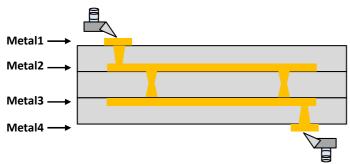

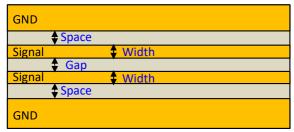

The Thru kit is designed in 4-layer substrate with dielectric constant 3.4, and each thickness of the dielectric layer is 60um

and metal thickness is 20um. The width and spacing of the Thru kit are optimized to comply with 50ohm impedance. The signal traces are layout in layer 2 and 3 and these two traces are connected by multiple vias in order to get symmetrical structure as like Fig. 3. In the top side and bottom side, we design a 150um pitch pad for GSG RF probing.

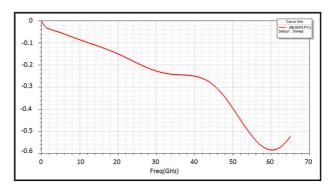

The Thru kit is simulated by the software ANSYS HFSS. The frequency range is up to 70GHz including Q-band 33GHz~50GHz. And the simulation results are shown in Fig4. The return loss is under -12.5dB for all frequency range and the insertion loss is about -0.6dB at 60GHz. It meets our target the return loss is under -10dB and the insertion loss is under -1dB for all frequency range.

#### III. MEASUREMENT RESULT

#### A. GSG Transmission Line & Thru Kit Measurement

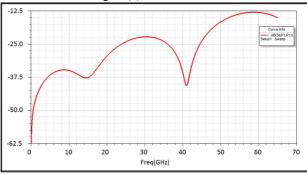

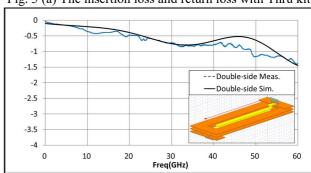

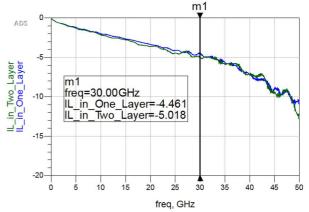

Before measuring the DUT, we did the double-side calibration. The parameters of the standard calibration kit need be set in the instrument Anritsu Vector Star MS4647B in advance. Firstly, we probed on the short, open, and load of the standard calibration kit on the top side with the 150um GSG RF probe, and on the back side also repeat the same step. The calibration kit could be attached on the back side of the probe station by the vacuum. Secondly, use the clamps and insulation screws to fix the thru kit, and then the RF probes could touch on the top and back side of the thru kit simultaneously. Finally, calculate the error terms by the VNA instrument and completed the calibration steps. The reciprocal thru kit and transmission line with 2mm length are measured after the calibration and the results are displayed in Fig.5 which's curves are all reasonable. The insertion loss is about -1dB and return loss is under -12.5dB for DC-60GHz frequency range. We could find it has -0.4dB difference of insertion loss between the simulation in section II and measurement, it maybe that we didn't consider the roughness effect of the copper in the simulation. The Fig.5(b) shows the insertion loss with the 2mm double-side line, the light blue curve is the measurement and the black curve is the simulation, the correlation is over 90% and the difference is about 0.5dB between simulation and measurement.

#### B. GSSG Differential Pair Measurement

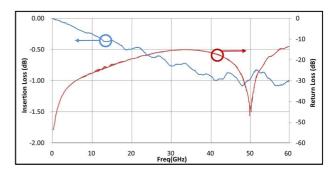

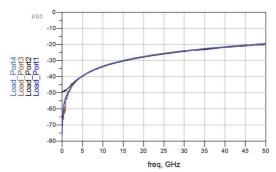

Fig. 6 displayed the structure for GSSG differential pairs layout. Two differential pairs are built in multi-layer substrate, and both pairs meet the  $85\Omega$  impedance by calculating the space, gap, and width based on the dielectric thickness 35um and dielectric constant 3.4. The difference of the two differential pairs is one pair is all signal trace placed in one layer, and the other pair is divided in two layers. The probing pad on the top side and bottom side are designed in the form of GSGSG arrangement for 150um differential RF probes due to GSGSG RF probe has better isolation and calibrated performance. Before measuring the DUT, we also did the calibration step by using the same design thru kit. Initially we define port1 and port3 is one set, port2 and port4 is another set. Different from the GSG calibration is the thru measured: we need to measure the design thru kit twice with two paths of the port1 to port2 and port3 to port4, and measure the thru

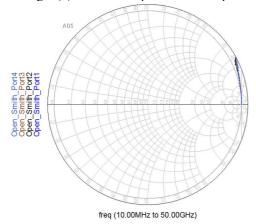

lines of the standard calibration kit for port1 to port3 and port2 to port4. The open, short, load measured are the same as the steps of the GSG calibration for each port. Complete the above steps, we finished the all steps of the calibration and let instrument VNA calculate and eliminate the error terms. The calibration results are shown in Fig. 7. The load response with each port is good that return loss is all under -20dB with DC-50GHz frequency range. The open smith chart of each port in air is no abnormality with DC-50GHz frequency range.

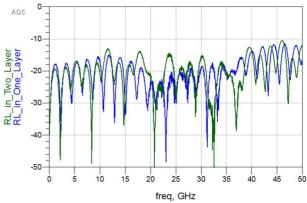

The two differential pairs were measured after calibration and shown in Fig.8. The pair routed in one layer with 36mm length is blue curve and the pair routed in two layers which the ratio is 2:1 with total 36mm length is the green curve. We could see the return loss of green curve is slightly worse compared to blue curve, but both are well design since the return losses are less than -10dB. Another comparison is the insertion loss, the pair routed in one layer is better 0.56dB at 30GHz. This is because the conversion interface is added once for the pair routed in two layers.

#### C. Measurement Environment

Fig. 9 shows the testing environment of double-side probing and the probe positioners are moved manually to the right position and observe the testing pad touching on the top side and bottom side under the respective microscope. Measure the signal performance in the substrate with the Anritsu MS4647B vector star.

#### IV. CONCLUSION

This paper successfully demonstrated the double-side measurement. Both GSG single-end signal and GSSG differential pairs have been tested the reasonable curves. The frequency range of the calibration in Double-side system is DC-60GHz for GSG Probe and DC-50GHz for GSGSG Probe. The correlation is over 90% and the difference is about 0.5dB between simulation and measurement with GSG single-end signal. For the measurement results of the GSSG differential pairs, it is recommended to route the differential pairs in one layer. Finally, the hole double-side test system could be used for Q-band applications.

#### ACKNOWLEDGMENT

The authors would like to acknowledge the assistance and support from RD, Substrate, Material Section, and Leaders in SPIL.

- H. -J. Hsu, M. -H. Tu, S. -M. Wu and C. -C. Chen, "Study of doubleside Thru calibration kit by non-contact coupling structure," 2015 Asia-Pacific Microwave Conference (APMC), Nanjing, China, 2015, pp. 1-3.

- [2] K. -C. Lu et al., "Vertical interconnect measurement techniques based on double-sided probing system and short-open-load-reciprocal calibration," 2011 IEEE 61st Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 2011, pp. 2130-2133.

- [3] H. -H. Shih, M. -H. Tu and S. -M. Wu, "Non-exchanging structure calibration kit for double-side direct contact measurement," 2015 Asia-Pacific Microwave Conference (APMC), Nanjing, China, 2015, pp. 1-3.

Fig 1. 2.5D Advanced package

Fig. 2(a) Single-Side System Fig. 2(b) Double-Side System

Table I. The Comparison of Different Calibration

| Calibration Method                                                | Advantages                                          | Disadvantages                                                                        |  |

|-------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------|--|

| SOLT (Short-Open-Load-Thru)                                       | - Simple<br>- Not band-limited                      | - Requires very well-defined standards                                               |  |

| SSST(Short-Short-Short-Thru) (shorts w/ different offset lengths) | - Same as SOLT - better accuracy at high frequency  | <ul><li>Requires very well-defined<br/>standards</li><li>Band-limited</li></ul>      |  |

| SOLR(Short-Short-<br>Reciprocal)                                  | Same as SOLT     Does not require well-defined thru | - Some accuracy degradation due to less defined thru.                                |  |

| LRL/TRL (Line-Reflect-Line)                                       | - Highest accuracy - Minimal standard definition    | <ul> <li>Requires very good<br/>transmission lines</li> <li>Band-limited.</li> </ul> |  |

Fig. 3 The Cross-section Diagram of the Thru kit

Fig. 4 (a) Insertion loss

Fig. 4(b) Return Loss of Thru kit

Fig. 5 (a) The insertion loss and return loss with Thru kit

Fig. 5(b)The insertion loss with 2mm length line

Fig. 6(a) The top view of GSSG layout in the substrate

Fig. 6(b) The cross-section connected in the substrate

Fig. 7(a) The load response for each port

Fig. 7(b) The open smith chart for each port

Fig. 8(a) The comparison of return loss

Fig. 8(b) The comparison of insertion loss

Fig. 9 The Double-side Probe station and Probing status

# Antiferroelectric Multilayers: a Multifunctional Platform for Energy and Information Storage

Hung-Wei Li, Sadegh Kamaei, Cyrille Masserey, Pascal Morel, Niccolò Martinolli, Tom Schlatter, Océane Mauroux, Igor Stolichnov, and Adrian M. Ionescu.

EPFL, Nanoelectronic Devices Laboratory (NanoLab), 1015, Lausanne, Switzerland

Abstract— This work demonstrates the integration of energy storage and multi-bit memory functionalities in a single platform device using multilayer dielectric (DE) with ferroelectric (FE) or antiferroelectric (AFE) materials. Employing a hafnium-based oxide, we achieve an energy storage density of approximately 50 J/cm<sup>3</sup> and advanced multi-bit storage capabilities. We investigate the effects of adjusting silicon doping concentration in multilayer Si:HfO2 during the atomic layer deposition (ALD) process to form and compare both FE and AFE layers. Inserting an Al<sub>2</sub>O<sub>3</sub> dielectric (DE) layer between the FE or AFE layers, we create a built-in electric field, enhancing both energy storage efficiency and multibit memory storage beyond the current state of the art. Our innovative approach harnesses the intrinsic properties of these materials to boost energy efficiency and data storage capacity, significantly improving device functionality and advancing electronic component design. Our results reveal that strategically layering DE with AFE materials enhances energy and multi-bit storage, opening new avenues for future multifunctional electronic applications.

#### I. INTRODUCTION

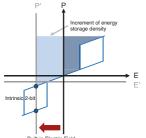

Hafnium oxide-based ferroelectric (FE) and antiferroelectric (AFE) thin films are emerging as key materials in the evolution of advanced memory and energy storage technologies. Integrating these materials into commercially viable devices demands not only comprehensive material characterization but also innovative engineering to enhance both endurance and performance. This study introduces a groundbreaking device that seamlessly integrates high-density energy storage with robust multi-bit memory functionality within a technological framework. Utilizing multilayer configurations of dielectric (DE), FE, and AFE materials, we have achieved an unprecedented energy density of approximately 50 J/cm<sup>3</sup>, coupled with enhanced multi-bit storage capabilities. This advancement is made possible through meticulous control of silicon doping in Si:HfO2 during atomic layer deposition (ALD), allowing for the precise formation of distinct FE and AFE phases. A key innovation in our device is the incorporation of an Al<sub>2</sub>O<sub>3</sub> dielectric layer between the FE and AFE layers, which generates a built-in electric field. This field significantly boosts energy storage efficiency while simultaneously stabilizing data retention in multi-bit memory configurations (Fig. 1). As the demand for ultracompact electronic devices increases, particularly in wearable and implantable technologies, our research addresses the *multi-functional need for devices that not only store energy efficiently but also retain data reliably.* The miniaturized energy autonomous systems enabled by this technology will integrate energy harvesting and storage with memory, offering a comprehensive solution for long-term, reliable device operation. Our findings not only demonstrate substantial improvements in energy and memory performance but also pave the way for the development of next-generation electronic components.

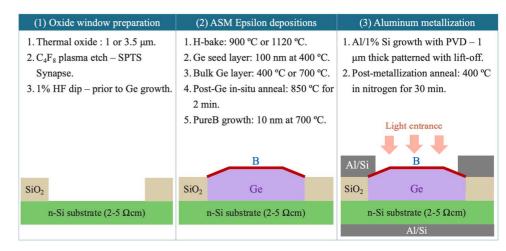

#### II. DEVICE FABRICATION PROCESS

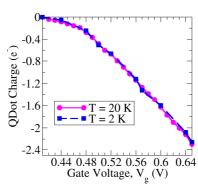

#### A. Tailoring silicon doped hafnium oxide properties

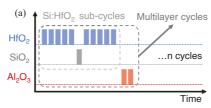

In the ALD process for Si:HfO<sub>2</sub> thin films, adjusting the  $SiO_2$  and  $HfO_2$  cycle ratios (Fig. 2a) yields either ferroelectric (FE) or antiferroelectric (AFE) behavior [1]. The metal-ferroelectric-metal (MFM) capacitor exhibits ferroelectric (Fig. 2(b)) or antiferroelectric (Fig. 2(c)) behavior depending on the  $SiO_2$  doping concentration.

#### B. FeCap fabrication

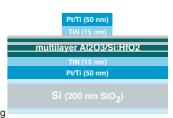

The fabrication process for the multilayer capacitors illustrated in Fig. 3(a). We begin by preparing a silicon substrate with a 200-nm thermally grown SiO<sub>2</sub> layer on both sides. After the standard cleaning process, the bottom electrodes composed of titanium (Ti) and platinum (Pt) were deposited by sputtering. Without breaking the vacuum, we sputter a titanium nitride (TiN) layer. The multi-layer structure is then created through ALD. Table 1 provides details on the various sample configurations. For consistency in comparison, we maintained the overall thickness of FE/AFE layers at 40 nm across all samples. After the multi-layer structure is complete, we deposit a second TiN and the entire stack then undergoes a rapid thermal annealing (RTA) in a nitrogen atmosphere. This step is crucial in achieving the desired orthorhombic crystalline phase, which is essential for tuning the FE or AFE properties of our device. The final stage of fabrication involves defining individual capacitors, by sputtering Ti and Pt layers, followed by a ion beam etching (IBE) process. This results in capacitors with a well-defined area of in the range of 100 µm<sup>2</sup> for characterization and performance evaluation.

#### III. RESULTS AND DISCUSSION

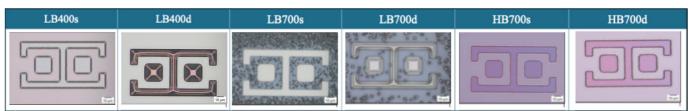

#### A. Multi-layer Capacitor Characterization

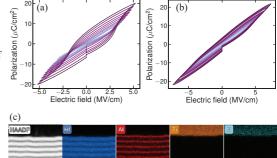

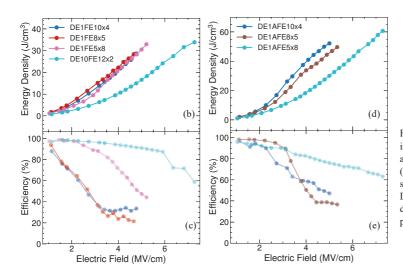

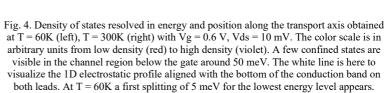

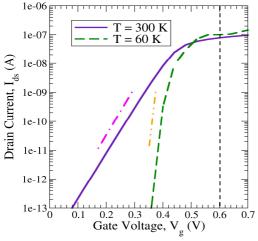

Fig 5 illustrates the experimental hysteresis curves of dielectric and ferroelectric behaviors in fabricated multilayer

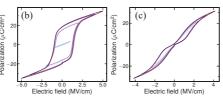

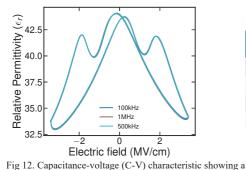

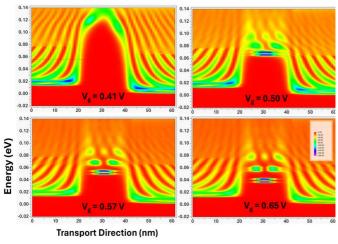

capacitors, highlighting the influence of interfacial engineering and material composition on electrical properties. Fig. 5(a) and (b) show the polarization-electric field (P-E) curves for DE1FE10×4 and DE1AFE10×4, respectively. The P-E curve for DE1FE10×4 displays characteristic ferroelectric behavior with suppressed remanent polarization  $(P_r)$ , attributed to the dielectric layer's effect on ferroelectric switching. While the MFM capacitor exhibits a  $2P_r$  of 40  $\mu$ C/cm<sup>2</sup>, DE1FE10×4 shows a reduced  $2P_r$  of 20  $\mu$ C/cm<sup>2</sup>. The P-E curve of DE1AFE10×4 demonstrates antiferroelectric characteristics and the versatility of layering strategies in tailoring material properties. The observed crossover of capacitance-voltage (C-V) branches (Figs 5(c) and (d)) at a non-zero electric field indicates the presence of a built-in electric field, likely resulting from asymmetric charge distributions or interfacial dipole moments within the multilayer structure. Fig. 6(a) and (b), representing DE1FE5×8 and DE1AFE5×8 respectively, demonstrate how a thicker dielectric layer alters the P-E response. This is evident from the linear capacitor behavior observed at lower electric fields, which also contributes to an increase in the electric breakdown voltage at high electric fields.

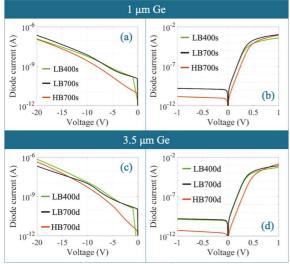

#### B. Energy storage enhancement with multilayered AFE/FE

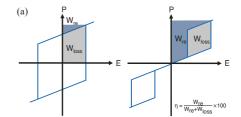

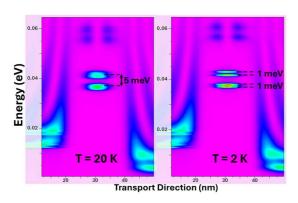

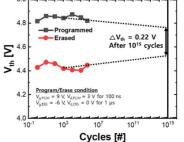

Fig. 7(b) and (c) compares energy storage capabilities of ferroelectric (FE) and antiferroelectric (AFE) multilayers. Our work demonstrated that AFE materials exhibit superior performance due to their unique phase transition properties. Energy storage is calculated from the area under the P-E curve, revealing total stored energy and hysteresis losses (Fig 7(a)). This method highlights fundamental differences in dipole behavior between FE and AFE materials under electric fields. FE multilayers like DE10FE12×2 achieve energy densities up to 30 – 40 J/cm<sup>3</sup> but are limited by breakdown electric field. In contrast, AFE multilayers, particularly DE1AFE10×4, exceed 60 J/cm<sup>3</sup> with efficiencies up to 80% at 3 MV/cm. This performance stems from AFE materials' ability to switch between non-polar and polar states, allowing for controlled energy discharge. To further increase the breakdown voltage, we compared more stacks of the multilayer. However, while increasing the number of layers achieves a higher breakdown voltage, it also results in lower energy density. Both phenomena can be observed in FE and AFE devices, which is due to the more pronounced DE contribution suppressing the dipole from FE and AFE layers. Unlike the rapid discharge in ferroelectrics, AFE materials demonstrate controlled energy release. This driven by reversible phase transitions, enhancing energy storage capacity and efficiency, and making AFE multilayers suitable for applications requiring efficient, highdensity energy storage. Charge-discharge characteristics of FE and AFE multilayer capacitors, providing insights into their practical performance. The setup uses a DC power supply and controlled discharge through a resistor to simulate real-world conditions (Fig. 8(a)). The voltage-time curves in Fig. 8(b) and 8(c) compare different multilayer configurations during charge-discharge cycles, using a 2.2 nF capacitor as a reference which is close to the maximum capacitance (Fig.5 (d)) we can obtain from AFE device. FE structures display rapid voltage decay, typical of quick energy release due to polarization switching, with DE1FE10×4 showing a slightly slower but still significant drop from 15V to near 0V within about 100  $\mu$ s. In contrast, AFE structures exhibit more controlled voltage decay, with DE1AFE10×4 maintaining higher voltage for longer. This confirms the superior performance of AFE materials in controlled energy release, making them ideal for applications requiring energy efficiency and longevity. Fig. 9 demonstrates the long-term stability of AFE materials under extensive field cycling, crucial for durable energy storage applications.

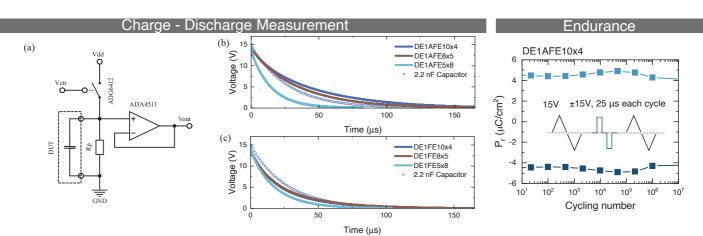

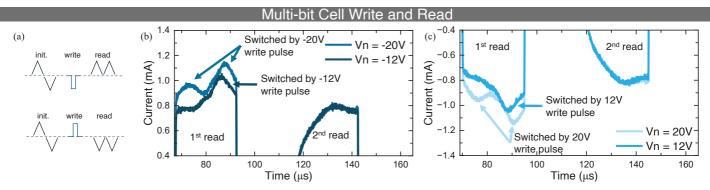

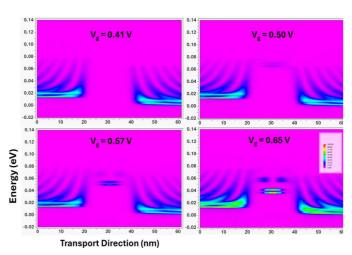

#### C. Multibit memory storage enabled by multilayered AFE/FE

FORC measurements (Fig. 9(a-f)) offer insights into the switching behavior of these materials. By inserting the DE layer, the current peaks can be finely tuned due to the builtin electric field (Fig. 9(b)). The DE1FE10×4 structure shows typical ferroelectric hysteresis with distinct current peaks at coercive fields. The presence of the DE layer subtly shifts these coercive fields closer to ±2 MV/cm. Integrating DE layers making DE1FE10×4 suitable for memory and energy storage technologies with fast response times and improved endurance. For DE1AFE10×4 (Fig. 9(e)), the FORC diagram reveals a shift in current peaks towards the same field polarity, a phenomenon not observed without the DE layer. This shift, caused by the DE layer's influence on the internal electric field, indicates multibit nonvolatile properties. By stabilizing specific states, this shift ensures reliable quaternary multibit memory operations. The read-out transient current data further supports these findings (Fig. 11). A ±12V pulse switches one peak, while a ±20V pulse switches both, with the current in the mA range. This demonstrates precise control, enabling accurate multibit memory storage and retrieval. The C-V characteristics of AFE materials (Fig. 12) display a double-peak butterfly shape with significant frequency dispersion, indicating rapid switching speeds in DE+AFE structures.

#### IV. CONCLUSION

This study comprehensively analyzes for the first time the energy storage capabilities, switching behavior, and memory performance of ferroelectric (FE) and antiferroelectric (AFE) multilayer capacitors. Through detailed charge-discharge measurements, C-V characteristics, and FORC analysis, it is demonstrated that AFE multilayers exhibit superior energy storage capacity, controlled energy release, and enhanced nonvolatile properties compared to FE structures. These advantages position AFE materials as a promising platform candidate for next-generation advanced electronic devices with multifunctional energy storage and memory capability.

#### REFERENCES

[1] T. Boscke, et al, *Applied Physics Letters*, vol. 99, 2011. [2] F. Ali, et al, . *J Appl Phys*, vol. 122, 2017. [3] J. P. B. Silva, et al, *J Mater Chem A*, vol. 8, 2020. [4] Cheema, S. S., et al, *Nature*, 2024.

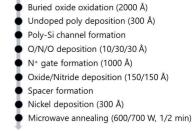

#### Multilayer Structure Fabrication Process

Fig 1. Schematic illustration of the qualitative P-E loop for the multilayer metal-insulator-ferroelectric-metal (MIFM) capacitor structure. The integration of a dielectric (DE) layer with antiferroelectric (AFE) or ferroelectric (FE) materials introduces a built-in electric field. This field significantly enhances the energy storage density and enables multi-bit memory functionality within the same MIFM capacitor structure, optimizing both memory capacity

Fig 2. (a) ALD process schematic for Si:HfO<sub>2</sub> thin films. Si:HfO<sub>2</sub> sub-cycle ratio adjustments yield FE or AFE behavior.

P-E hysteresis loops of MFM capacitors: (b) 3.12% Si concentration (ferroelectric), (c) 5% Si concentration (antiferroelectric).

Top electrode pattering IBE

Ti/Pt (5/50 nm) Sputtering

600°C 2 min RTP

TiN (15 nm) Sputtering

Al<sub>2</sub>O<sub>3</sub>/Si:HfO<sub>2</sub> multilayer ALD

Ti/Pt/TiN (5/50/15 nm) Sputtering

Fig 3. Key fabrication steps for the multilayer capacitor structure. The ALD multilayer cycles are adjusted to achieve different material combinations in the multilayer structure.

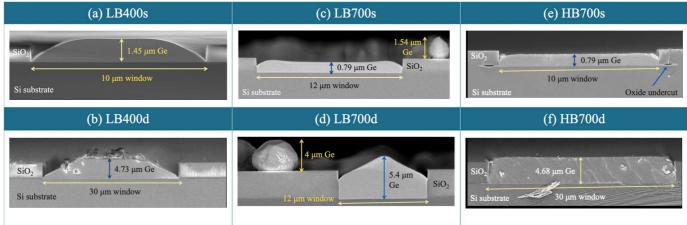

| Sample ID  | T <sub>AIO</sub> (nm) | T <sub>SiHfO</sub> (nm) | Layer number | s Si:HfO <sub>2</sub> properties |

|------------|-----------------------|-------------------------|--------------|----------------------------------|

| DE10FE10x2 | 10                    | 10                      | 2            | Ferroelectric                    |

| DE1FE10x4  | 1                     | 10                      | 4            | Ferroelectric                    |

| DE1FE8x5   | 1                     | 8                       | 5            | Ferroelectric                    |

| DE1FE5x8   | 1                     | 5                       | 8            | Ferroelectric                    |

| DE1AFE10x4 | 1                     | 10                      | 4            | Antiferroelectric                |

| DE1AFE8x5  | 1                     | 8                       | 5            | Antiferroelectric                |

| DE1AFE5x8  | 1                     | 5                       | 8            | Antiferroelectric                |

Fig 4. The tables summarize key samples, providing its thickness of each layer and the ferroelectric/antiferroelectric properties.

#### **Experimental Device Characterisitics**

- Fig 5. (a) P-E curve of DE1FE10x4 showing typical ferroelectric behavior, with suppressed remanent polarization due to the dielectric layer's contribution. (b) P-V curve of DE1AFE10x4 demonstrating antiferroelectric characteristics. (c) Butterfly-like dielectric response of the FE capacitor after interfacial engineering of interlayers, with a crossover of C-V branches at a non-zero electric field indicating a built-in field. (d) Butterfly-like dielectric response

- (d) Butterfly-like dielectric response of the AFE capacitor under similar conditions, also showing a crossover due to a built-in field.

- (e) TEM image and EDS results for the multilayer structure, providing a detailed view of the material composition and interfaces.

Fig 6. (a) P-E curve of DE1FE5x8, showing ferroelectric properties with a noticeable linear capacitor response at low electric fields due to the increased dielectric layer contribution. (b) P-V curve of DE1AFE5x8, also exhibiting a linear capacitor response at low electric fields, influenced by the dielectric layer.

(c) TEM image and EDS results, providing detailed insights into the material structure and composition.

#### Experimental Device Characterisitics: Energy Storage Density

Fig 7. (a) Calculation of energy density and efficiency derived from the P-E loop, involving the integration of the area under the polarization-electric field curve to assess the energy stored and the corresponding efficiency based on energy loss. (b, c) Energy density versus electric field plots for ferroelectric multilayers, showing the material's capacity to store more energy when adjusting the inserting DE layers. (d, e) Similar plots for antiferroelectric multilayers, highlighting the distinct energy storage characteristics compared to their ferroelectric counterparts, including differences in energy density and efficiency.

Fig 8. (a) Schematic of the charge-discharge setup: A DC power supply charges the capacitor, which then discharges through a  $12~\mathrm{k}\Omega$  resistor. The pulse duration ( $10~\mathrm{\mu}s$ ) is controlled by a switch (ADG6412), and the voltage is monitored using an oscilloscope. A follower (ADA4511) reduces the parastics from the oscilloscope. (b, c) Comparison of discharge curves for ferroelectric and antiferroelectric multilayer structures with those of an ideal 2.2 nF capacitor. These simulated values are used as a reference to assess the performance of the multilayer structures.

Fig 9. The device demonstrates fatigue-free behavior during field cycling, benefiting from the intrinsic properties of the antiferroelectric (AFE) material.

Fig 10 (a) Schematic outlining the First-order Reversal Curve (FORC) measurement approach. The applied field is swept from positive saturation to a reversal point, then back to positive saturation. This process is repeated for multiple reversal points to generate a series of curves that together form a comprehensive map of the material's electric behavior. (b) Schematic of AFE with DE multilayer, the current peaks will shift. FORC result of the MFM capacitors exhibiting (c) FE properties and (d) AFE properties. (e) FORC results showing the effect of the DE layer on the FE multilayer capacitor, illustrating changes in the coercive field and interaction fields due to the DE layer. (f) FORC result of the AFE multilayer capacitor with a DE interlayer, where the addition causes the two peaks at opposite field polarities to shift toward the same polarity, indicating multi-bit nonvolatile properties. This shift suggests a modification in the energy landscape of the AFE material due to the presence of DE layers.

Fig. 11 (a) Schematic of the pulse sequence used to verify the write operation. After the write operation, two pulses (18V) with opposite polarity are applied to read out the switching polarization achieved during the write process. (b, c) Read-out transient current for different write pulse levels. The results show that  $a \pm 12$  V pulse can switch only one peak, while  $a \pm 20$ V pulse can switch both peaks, demonstrating the control over the switching behavior with varying pulse levels.

the multilayer DE AFE structure

double-peak antiferroelectric (AFE) butterfly shape. The robust frequency dispersion observed indicates a fast switching speed in

|                           | Material                                            | ESD (J/cm³) | Efficiency | Memory and Energy<br>Storage Integration |

|---------------------------|-----------------------------------------------------|-------------|------------|------------------------------------------|

| F. Ali, et al [2]         | Si-HfO <sub>2</sub>                                 | 61          | 65%        | -                                        |

| J. P. B. Silva, et al [3] | $Al_2O_3$ : $DIL	ext{-}Hf_{0.5}Zr_{0.5}O_2$         | 54          | 51%        | -                                        |

| Cheema, S. S. et al [4]   | HfO <sub>2</sub> /ZrO <sub>2</sub>                  | 115         | 90%        | -                                        |

| This work                 | Al <sub>2</sub> O <sub>3</sub> /Si:HfO <sub>2</sub> | 50          | 80%        | Yes                                      |

Table 2. Benchmarking of various on-chip CMOS compatible energy storage capacitors.

### Thermal Management for In-Vehicle Emergency Call Systems

Boyoun Park and Chungwoo Park

Samsung Electronics, Hwaseong, South Korea, email: boyoun.park@samsung.com

Abstract—Given the life-saving significance of eCall, it is imperative that it operates reliably under extreme environmental conditions such as high external temperatures. To address this, this paper proposes an integrated thermal management solution from a product perspective, transcending the traditional SoC approach. This solution holds potential for widespread application across various embedded systems where external cooling methods are not available.

#### I. INTRODUCTION

eCall is an emergency call system for vehicles to assist in road traffic accidents, which is legislated by the European Union Parliament (EU-2015/758). eCall is triggered automatically when an accident is detected or manually when the eCall SOS button is pressed, providing the vehicle's precise location (Fig. 1). Since eCall is essential for saving lives, it needs to operate even in extreme conditions such as high ambient temperature ranging from -40 °C to 85 °C. However, a TCU (Telematics Control Unit) that is an embedded device supporting eCall is mainly positioned in a place that is not suitable for cooling (e.g., between a vehicle's roof and roof liner). In addition, the increased power consumption of MPSoC (Multi-Processor System-On-Chip) due to high power density also results in a significantly higher temperature. Under the circumstances, the existing temperature solutions have been insufficient to solve those problems. Therefore, this paper suggests an integrated temperature control solution at the product level surpassing the SoC level and from the total power perspective, not being limited to the perspective of the dynamic power.

#### II. POWER AND THERMAL CHARACTERISTICS OF SOC

In modern processors, to improve performance, both the number of transistors per die and clock frequencies have been increased. The increase in power density and performance has led to heat dissipation. As the transistors consume more power, the temperature of the transistors, which is also known as the junction temperature, increases ((1) in Table 1). Therefore, by taking into account the ambient temperature, the thermal resistance value, and the maximum temperature that the chip can withstand, the maximum allowed power dissipation, which is also called power budget, can be determined.

Another one of the important features of SoC is that the power increases as the ambient temperature increases. The total power can be divided into dynamic and static as (2) in Table 1 and static power or leakage power, which is primarily composed of sub-threshold current, is highly sensitive to temperature as (3) in Table 1 [1] and increases exponentially as the temperature rises [2].

Based on the two main characteristics, an increase in the ambient temperature can increase power, and an increase in power leads to greater heat dissipation. This circular relationship could result in a thermal runaway [3]. Therefore, it is important to ensure the appropriate cooling of the SoC.

Various cooling systems have been designed including heat pipe cooling, liquid cooling, fan cooling, and others. However, these methods are commonly used for CPUs in high end server platforms [4]. Since it is hard to add external cooling methods in embedded systems with limited size and allowed amounts of power consumption, SoC-internal approaches have been generally applied.

Dynamic Thermal Management (DTM) refers to "a range of possible software and hardware strategies while work dynamically to control a chip's operating temperature at runtime" [3]. Most widely used method is CPU Throttling which is constraining voltage and frequency (Dynamic Voltage and Frequency Scaling; DVFS) [5]. It slows down the CPUs whenever it reached trip points. If a critical trip point is reached (e.g. 105 °C), then thermal shutdown will be triggered. However, as (4) in Table 1, DVFS can only reduce dynamic power. Since leakage power has the property of increasing with the external temperature, it is also important to reduce leakage power. There are several methods that can control leakage power. For example, unused CPUs could be disabled (CPU hotplug out) [6] and unrelated power domains could be turned off [7]. Although the methods reducing leakage power are not widely used to control the temperature of the chip, this paper considers both dynamic and leakage power to minimize consumed power.

Another limitation of traditional methods is that the temperature and power are only considered from the perspective of SoC. However, according to the results in this paper, 34% of the total power consumed by the board was consumed by SoC and the remaining 66% of the power was consumed by other components on the board. Therefore, to reduce the total power, all components on the board should be considered to lower the overall temperature inside the product.

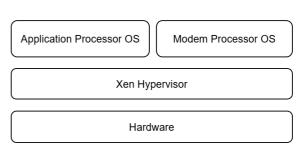

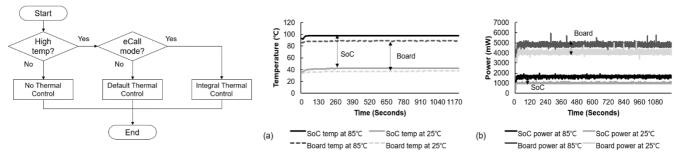

#### III. PROPOSED THERMAL MANAGEMENT SYSTEM

The system configured in this paper with Exynos Auto T5123 was same as the virtualized system from [8]. To support eCall, operating systems for AP (Application Processor) and MP (Modem Processor; Communication Processor) were virtualized based on Xen Hypervisor (Fig. 2). The sequence of this system is shown in Fig. 3. When the chip reaches a high junction temperature threshold (e.g. 65 °C) in a normal situation, it triggers default thermal management such as DVFS. However, if it is in eCall mode and reaches a high temperature, then it goes into the restricted mode to reduce the power consumption as much as possible using all possible methods.

All the methods applicable in the restricted mode can be categorized into the following four categories in Table 2. To reduce the dynamic power of SoC, we minimized the voltage and frequency (CPU Throttling). Also, by setting the logging level to the minimum, CPU loads were reduced. On the other hand, to reduce the static power of SoC, CPUs or power domains could be turned off. However, in this paper, there was

no isolated power domain that could be turned off during call operation and only one unnecessary CPU could be turned off.

At the board level, external devices can be dynamically or statically controlled. For example, the throughput for an Ethernet device could be reduced from 1000 Mbps to 10 Mbps. In this paper, to maximize the effect of optimization, the link connected to the Ethernet device was disconnected.

#### IV. MEASUREMENT AND RESULTS

#### A. Experimental Setup

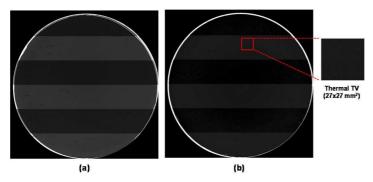

Temperature and power samples were collected at both ambient room temperature (25 °C) and high temperature (85 °C). The high temperature was artificially created using a hightemperature chamber (ESPEC, SH-662), while the room temperature data was collected outside the chamber for comparison. The junction temperature of the chip was measured using a Samsung temperature sensor located near the CPUs which is the hottest spot. On the other hand, the surrounding temperature of the chip was measured by a thermistor (Murata Electronics, NCU15WF104F6SRC) attached to the board. The resolution of the both temperature sensors was 1 °C and the data was read for every 10 seconds. Meanwhile, the power consumption data for the chip and its CPUs were measured by a DAQ system (National Instruments, USB-6289) with a sampling rate of 5 Hz and the data for the board was measured by another power measurement system (Monsoon Solutions, AAA10F power monitor) with the sampling rate of 5 Hz.

Test steps are as follows. First, for high temperature, the ambient temperature was gradually increased to 85 °C by the high temperature chamber, which takes about 20 minutes. Second, after turning on the board power using the power monitor, we waited 5 minutes for saturation. Third, we began collecting data on the temperature and power consumption. Forth, we triggered a voice call using 3G (UMTS) networks. After maintaining the call for 20 minutes, the measurements were stopped. After completing these test steps without hanging up, we calculated the CPU utilization based on the unscheduled idle time over a period of 30 seconds to compare the CPU loads under different conditions.

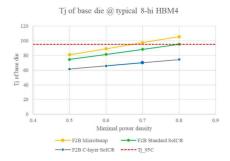

#### B. Results and Discussion

For analysis, the temperature and power consumption data from last 5 minutes were averaged to eliminate the influence of unsaturated data. As shown in Fig. 4, under the high ambient temperature, the temperature and power consumption were remarkably higher than under the room temperature. The junction temperature of the SoC increased by 56 °C under the high ambient temperature compared to the low ambient temperature and that of the board increased by 50.9 °C. Also, the power consumption of the SoC increased by 604.91 mW and that of the board increased by 720.55 mW when comparing the high ambient temperature to the low ambient temperature condition.

The dynamic power and static power of CPUs of the SoC could be estimated based on (5) and (2) in Table 1. The CPU utilization was calculated to be 0.42 at the low ambient temperature (25 °C) and the high ambient temperature (85 °C) (Table 3). Therefore, the dynamic power under the low and high temperature is estimated to be 40.52 mW. As the leakage power

is the remainder after subtracting the dynamic power from the total power, the leakage power is estimated to be 123.53 mW and 193.58 mW at the low and high ambient temperature, respectively because the total power for CPUs were 164.05 mW and 234.1 mW. The results indicate that the leakage power highly increased at the high ambient temperature and this is a characteristic equally applied to other semiconductor components.

According to Table 4, most of the conditions reduced temperature and power consumption. The CPU throttling was the most effective in reducing the junction temperature and power of SoC. Reducing CPU loads by reducing the log level resulted in lower CPU utilization (0.33) compared to the default condition (0.42) as in Table 3. Although it lowered the power consumed by SoC, it was not obviously observed in the junction temperature results due to the low resolution of the temperature measurement. Contrary to expectations, turning off an unnecessary CPU had no effect. It seems that turning off just one CPU of ARM Cortex-A55 is not that effective, as it is a low power processor and is generally used as a 'LITTLE' CPU in big.LITTLE architectures. On the other hand, disconnecting the Ethernet links reduced the power and temperature of the board, which also resulted in a reduction in the junction temperature of the SoC. Finally, applying all the methods achieved the greatest reduction in the temperature and power, both at the SoC and board level, thereby increasing the power budget based on the maximum junction temperature that the SoC can withstand. The increased power budget would allow the SoC to operate longer before thermal shutdown even at higher temperatures.

#### V. CONCLUSION

In this paper, we proposed an integrated thermal management solution for eCall systems that not only reduces the dynamic power of SoC but also static power and a more expanded perspective than SoC. The measured results showed that disconnecting external components was effective in lowering leakage power and the temperature surrounding the SoC, which also resulted in a decrease in the junction temperature of the SoC. The implemented solution could be modified in various ways. For example, the CPU load could be reduced by shutting down applications unrelated to eCall, instead of changing the log level. Also, if it is hard to power off external components to reduce the leakage power, it is possible to restrict their maximum operating speed to reduce the dynamic power. In addition, if the chip is designed to power off unused sub-components, then the leakage power could be significantly decreased by turning them off. In conclusion, the proposed solution could not only be applied to automotive systems but also to all embedded systems which cannot use external cooling.

REFERENCES [1] D. Helms et al., "Leakage models for high-level power estimation." [2] K. Roy et al., "Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits." [3] D. Brooks et al., "Dynamic thermal management for high-performance microprocessors." [4] G. Xu et al., "Extension of air cooling for high power processors." [5] L. Zhou et al., "Thermal management of ARM SoCs using Linux CPUFreq as cooling device." [6] S. P. Kamat, "Thermal management in embedded systems: A software approach." [7] A. K. Thakur et al., "Physical Implementation of Multi Power Domain SoC Design." [8] B. Park et al., "DRX mode implementation based on virtual machine."

Fig. 1. The concept of eCall systems cited from IZT Labs.

Fig. 2. Overall Architecture of the proposed solution

Fig. 3. Overall flow of the system under different conditions.

Fig. 4. Temperature (a) and power measurement data (b) under the low and high ambient

| $T_i = T_a + R_{ia} \times P$                                                                                                  |      |

|--------------------------------------------------------------------------------------------------------------------------------|------|

| $T_a$ : ambient temperature                                                                                                    | (1)  |

| $R_{ja}$ : thermal resistance between the junction and ambient temperature                                                     | (1)  |

| P: total power dissipated in the chip.                                                                                         |      |

| $P_{total} = P_{dynamic} + P_{static}$                                                                                         | (2)  |

| $P_{total} = P_{dynamic} + P_{static}$ $I_{sub-threshold} = \alpha \frac{w}{L} T^2 e^{-\beta V_{th}/T}$                        |      |

| L, W: channel length and width for transistors.                                                                                | (3)  |

| $V_{th}$ : threshold voltage, which is the minimum voltage needed for the transistor to begin conducting current.              |      |

| T: absolute temperature, which is the temperature measured using the Kelvin scale where zero indicates absolute zero.          |      |

| $P_{dynamic} = C \times V_{dd}^2 \times f$                                                                                     |      |

| $V_{dd}$ : supply voltage                                                                                                      | (4)  |

| f: operating frequency                                                                                                         | ( ') |

| C: switching capacitance that is the ability of a circuit to collect and store energy.                                         |      |

| $P_{dynamic} = \text{Coeff} \times Volt^2 \times Freq \times U$ til                                                            |      |

| Coeff: coefficient value. The coefficient value for ARM Cortex-A55, taken from the Linux Kernel for Google's GS101 SoC, is 70. |      |

| Volt: voltage. The voltage for CPUs in this paper was set to 0.9375 V.                                                         | (5)  |

| Freq: clock frequency. The clock frequency for CPUs in this paper was set to 1.568 GHz.                                        |      |

| Util: CPU utilization                                                                                                          |      |

Table 1. Equations used in this paper

| Types             | Examples                                            |  |

|-------------------|-----------------------------------------------------|--|

| SoC and Dynamic   | CPU Throttling (DVFS), reducing CPU loads, and etc. |  |

| SoC and Static    | CPU hotplug out (CPU off) and power domain off.     |  |

| Board and Dynamic | restricting performance of external device          |  |

| Board and Static  | external device off                                 |  |

Table 2. Four types of methods for lowering the temperature of the system

| Ambient temp (°C) | Condition     | CPU0 | CPU1 | CPU2 | CPU3 | Sum  |

|-------------------|---------------|------|------|------|------|------|

| 25                | Default       | 80.0 | 0.09 | 0.25 | 0    | 0.42 |

|                   | Default       | 0.11 | 0.07 | 0.24 | 0    | 0.42 |

|                   | Throttle      | 0.4  | 0.35 | 0.67 | 0    | 1.42 |

| 85                | Load down     | 0.05 | 0.11 | 0.17 | 0    | 0.33 |

| 83                | CPU disable   | 0.15 | 0    | 0.26 | 0    | 0.41 |

|                   | Eth link down | 0.1  | 0.07 | 0.31 | 0    | 0.48 |

|                   | All           | 0.57 | 0    | 0.42 | 0    | 0.99 |

Table 3. The ratio of idle time per CPU over a 30-second period and total sum under different conditions (with a maximum utilization value of 1 per CPU)

|    | Ambient temp (°C) | Condition     | SoC temp (°C) | Board temp (°C) |

|----|-------------------|---------------|---------------|-----------------|

|    | 25                | Default       | 42.00         | 37.97           |

|    |                   | Default       | 98.00         | 88.87           |

|    |                   | Throttle      | 95.00         | 88.00           |

|    | 85                | Load down     | 98.00         | 88.63           |

|    | 85                | CPU disable   | 98.00         | 88.70           |

|    |                   | Eth link down | 97.03         | 88.00           |

| a) |                   | All           | 94.97         | 88.00           |

| Ambient temp (℃) | Condition     | SoC power (mW) | Board power (mW) |

|------------------|---------------|----------------|------------------|

| 25               | Default       | 1033.30        | 4052.26          |

|                  | Default       | 1638.21        | 4772.81          |

|                  | Throttle      | 1321.69        | 4458.70          |

| 85               | Load down     | 1604.06        | 4745.07          |

| 65               | CPU disable   | 1632.37        | 4774.76          |

|                  | Eth link down | 1627.66        | 4216.56          |

|                  | All           | 1286.63        | 3868.53          |

Table 4. Temperature (a) and power (b) under different conditions. Board power includes SoC power.

(b)

(a)

## Wafer-Scale 2D MoS<sub>2</sub> Transistors Using Transfer-Free Location-on-Demand Selective Synthesis

Anthony Cabanillas,¹ Chu Te Chen,¹ Asma Ahmed,¹ Anthony Butler,¹ Yu Fu,¹ Ajay Yadav,² Gabriel Lee,² Keith Wong,²\* Fei Yao,¹\* and Huamin Li¹\*

<sup>1</sup>University at Buffalo, The State University of New York, Buffalo, NY, USA <sup>2</sup>Applied Materials, Inc., Sunnyvale, CA, USA

\*Email: keith wong@amat.com, feiyao@buffalo.edu, huaminli@buffalo.edu

Abstract — Compatible integration of emerging two-dimensional (2D) materials with mature Si-CMOS technology is promising to enable high-performance energy-efficient electron devices. In this work, we exploited wafer-scale, location-on-demand, selective growth of 2D semiconducting transition metal dichalcogenide (TMD), MoS<sub>2</sub>, on a SiO<sub>2</sub>/Si substrate for transfer-free electron device applications. We investigated the impact of native oxide MoO<sub>3</sub> dielectrics on the performance of MoS<sub>2</sub> field-effect transistor (FET) arrays through a comparative study with SiO<sub>2</sub> dielectrics, and demonstrated great potential of the selective growth of 2D semiconductors to lower down the technological requirement for practical integration with Si-CMOS technology.

#### I. INTRODUCTION

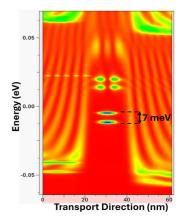

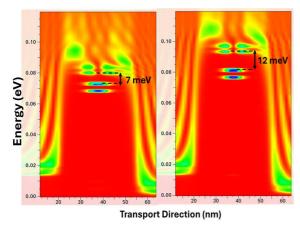

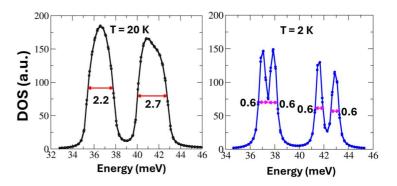

To continue the Moore's law and maintain device miniaturization, 2D semiconducting TMDs have been extensively explored as one of the most promising channel materials. Despite the early success in fundamental science explorations and proof-of-concept device demonstrations [1-4], TMD films with good scalability, uniformity, crystallinity, and compatibility on suitable substrates remain a significant roadblock to the realization of commercially viable TMD-based electron devices [5, 6]. To mitigate this problem, we investigate a location-on-demand selective growth methodology to realize high-quality TMD layers with consistent layer characteristics. Without any wet or dry transfer process which inevitably leads to material degradation, the TMD growth is catalyzed directly at the desired channel area with improved time and cost effectiveness. Specifically, we take 2D MoS<sub>2</sub> as an example, and exploit patterned MoO<sub>3</sub> seedings to enable wafer-scale location-on-demand selective growth of MoS<sub>2</sub> arrays for transfer-free FET applications. We directly observe the chemical vapor deposition (CVD) growth of MoS<sub>2</sub> on micrometer scale within a few seconds (a high growth rate of 0.5 µm/s), and investigate the impacts of the dielectric interfaces (MoO<sub>3</sub>, SiO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub>) on the synthetic MoS<sub>2</sub> FET performance in terms of on-current density  $(J_{D,on})$ , field-effect mobility ( $\mu_{FE}$ ), on/off ratio, contact resistance ( $R_C$ ), transfer length  $(L_{\rm T})$ , and Schottky barrier height (SBH) etc. We find that the polycrystal MoS<sub>2</sub> with MoO<sub>3</sub> dielectric interface has comparable and even superior performance compared to other MoS<sub>2</sub> FETs using selective and non-selective growth, despite the presence of rich grain boundaries (GBs). Our work demonstrates the wafer-scale, transfer-free, location-ondemand selective growth of 2D TMD, which can significantly ease the integration with Si-CMOS processing and paves a feasible way for realizing 2D semiconductor implementation.

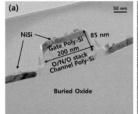

#### II. DEVICE FABRICATION AND MEASUREMENT

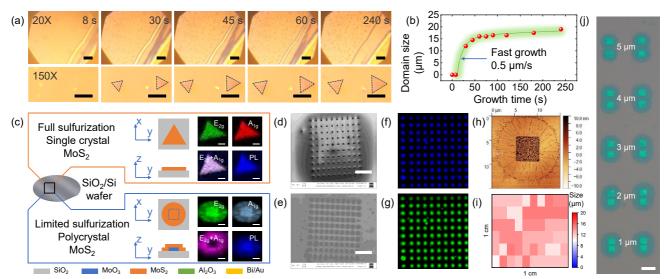

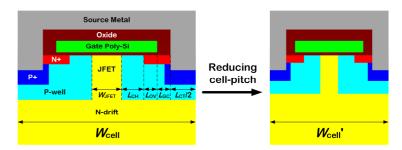

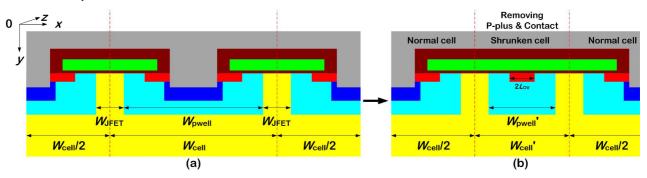

MoS<sub>2</sub> growth and its dynamic evolution. First, the MoO<sub>3</sub> seedings were patterned using electron-beam lithography (EBL) and sputtered on p-Si substrates (1-10  $\Omega$ ·cm) with 285 nm SiO<sub>2</sub> dielectric. Next, the sample was loaded in a two-zone CVD furnace for controlled sulfurization, and the MoS<sub>2</sub> thin films were formed at the seeding areas, which spatial morphology and crystallinity can be manipulated by the CVD synthetic parameters. Especially, the dynamic evolution of MoS<sub>2</sub> growth was monitored by a micro-chamber CVD with time-resolved in-situ microscopy, as shown in Fig. 1(a) and (b). A single crystal MoS<sub>2</sub> domain, up to 10  $\mu$ m in size, can be grown within ~20 s, indicating a high growth rate of 0.5  $\mu$ m/s.

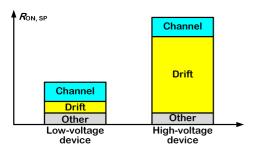

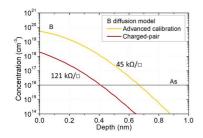

Controlled sulfurization. MoO<sub>3</sub> is not only a Mo precursor but also a high-k dielectric ( $k = \sim 35$ ) [7]. In principle, MoO<sub>3</sub> can serve as a better dielectric interface to screen the charge impurities and boost the charge transport. Compared to a full sulfurization process which leads to a single crystal "triangle" domain formation, a limited sulfurization process only at the MoO<sub>3</sub> surface creates polycrystal MoS<sub>2</sub> around the MoO<sub>3</sub> seedings, as shown in Fig. 1(c). This "circular" MoS<sub>2</sub> pattern suggests isotropic homogeneity of MoS<sub>2</sub> growth on SiO<sub>2</sub>, and the remaining MoO<sub>3</sub> layer provides a native high-k dielectric interface, benefiting the charge transport of the synthetic MoS<sub>2</sub> on top of it. Confocal Raman and photoluminescence (PL) spectroscopies also confirm the signature modes of MoS<sub>2</sub> on both MoO<sub>3</sub> and SiO<sub>2</sub> dielectrics, suggesting excellent uniformity of localized homogeneity.

Large-scale location-on-demand selective growth of MoS<sub>2</sub>. Scanning electron microscopy (SEM) and Raman spectroscopy were performed to confirm the MoO<sub>3</sub> seedings (e.g., an array of  $5\times5~\mu m^2$  squares) and the corresponding MoS<sub>2</sub> growth (e.g., an array of circular MoS<sub>2</sub> with a diameter of ~14 um) across a  $1\times1~cm^2$  area, as shown in Fig. 1(d-g). Atomic force microscopy (AFM) confirms the presence of a nonsulfurized MoO<sub>3</sub> layer which is less than 10 nm, as shown in Fig. 1(h). Excellent uniformity of the synthetic MoS<sub>2</sub> size across a  $1\times1~cm^2$  area was evaluated, as shown in Fig. 1(i). With the increased seeding density (i.e., the miniaturized spacing distance down to  $1~\mu m$ ), the selective MoS<sub>2</sub> growth is still consistent, as shown in Fig. 1(j). All these characterizations suggest excellent reproducibility and uniformity of selective growth for the ease of integration, especially at a large scale.

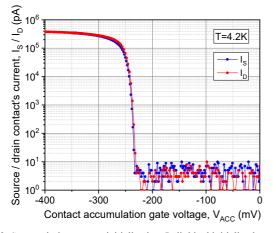

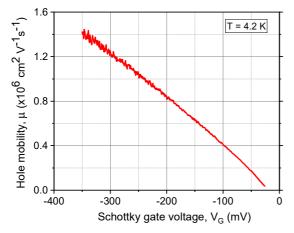

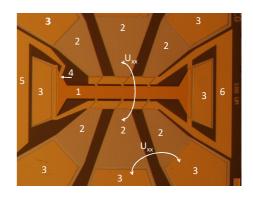

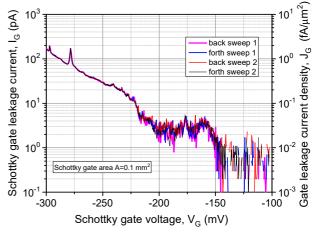

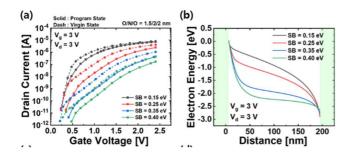

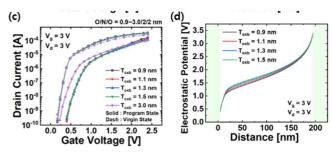

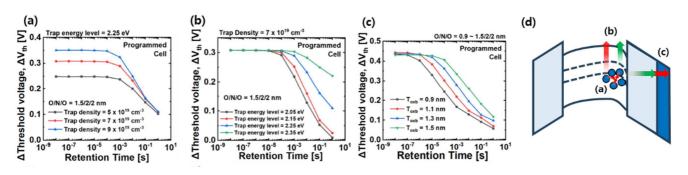

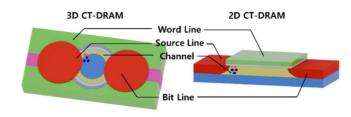

**Device fabrication and measurement.** On top of the asgrown MoS<sub>2</sub>, Bi/Au electrodes (20 nm/50 nm) were patterned by EBL and sputtered to form a back-gate FET configuration, and Al<sub>2</sub>O<sub>3</sub> was deposited by atomic layer deposition (ALD) to form a top dielectric in a top-gate FET configuration. Electrical and photoresponse characterizations were performed using a semiconductor parameter analyzer, a temperature-variable vacuum probe station, and an integrated laser system. With the grounded source, drain current ( $I_D$ ) was measured as a function of the applied drain, back-gate, and top-gate voltages ( $V_D$ ,  $V_{BG}$ , and  $V_{TG}$ ), and was normalized in current density ( $J_D = I_D/W$  where W is the channel width) for comparison.

#### III. DEVICE RESULTS AND DISCUSSION

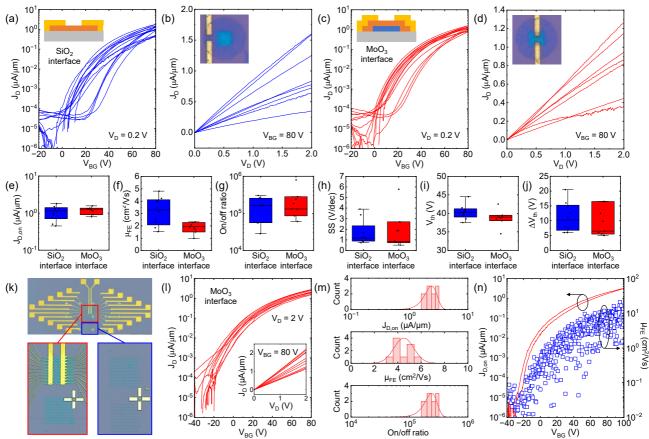

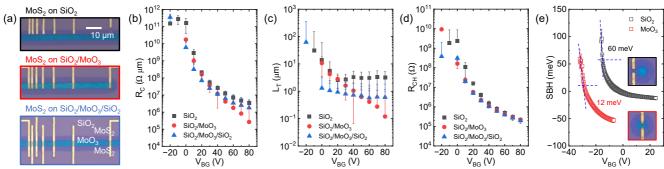

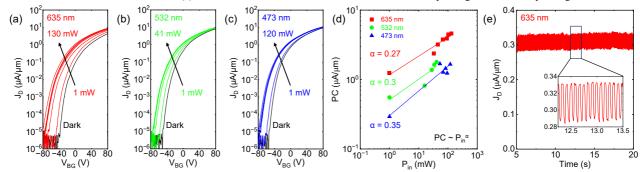

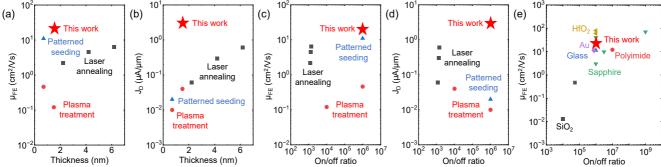

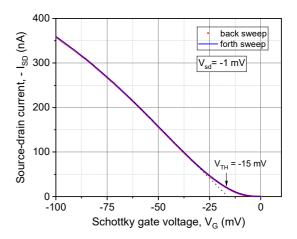

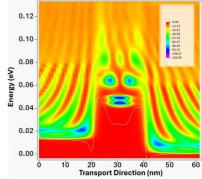

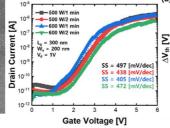

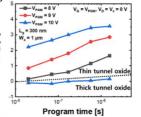

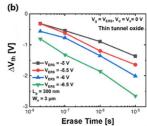

MoO<sub>3</sub> dielectric interface. A comparative investigation is performed for the synthetic MoS<sub>2</sub> FETs with the MoO<sub>3</sub> and SiO<sub>2</sub> dielectric interfaces, in terms of output and transfer characteristics ( $J_D$ - $V_D$  and  $J_D$ - $V_{BG}$ ), and a statistical analysis of  $J_{\rm D,on}$ , subthreshold swing (SS),  $\mu_{\rm FE}$ , threshold voltage ( $V_{\rm th}$ ), hysteresis window ( $\Delta V_{\text{th}}$ ), and on/off ratios, as shown in Fig. 2(a-i). The linear  $J_D$ - $V_D$  characteristics suggest Ohmic contact for both FET types. With the identical synthetic process and device geometry, the MoO<sub>3</sub> interface provides comparable FET performance metrics, and more importantly, in much narrower distributions. On the wafer scale, the MoS<sub>2</sub> arrays formed by the controlled sulfurization at on-demand locations are still reproduceable, which gives the average  $J_{D,on}$  of 2  $\mu$ A/ $\mu$ m,  $\mu_{FE}$  of 5 cm<sup>2</sup>/Vs, and on/off ratio exceeding 10<sup>5</sup>, as shown in Fig. 2(km). By optimizing the synthetic parameters, our best MoS<sub>2</sub> FET device possesses  $J_{D,on}$  of 3  $\mu$ A/ $\mu$ m,  $\mu_{FE}$  of 20 cm<sup>2</sup>/Vs, and on/off ratio up to  $10^6$ , as shown in Fig. 2(n).

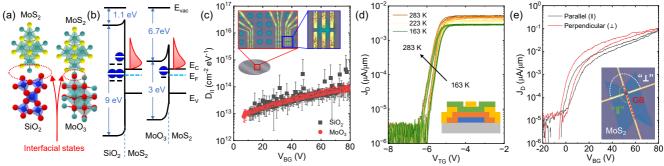

Compared to conventional  $SiO_2$ ,  $MoO_3$  as both the precursor and native oxide provides a much intimate contact to  $MoS_2$  with less defects, traps, mismatch, strain, or interfacial states, as shown in Fig. 3(a) and (b). These facts are evidenced by the extracted interfacial trap density ( $D_{it}$ ), as shown in Fig. 3(c). Here  $D_{it}$  was calculated from SS [8], and the  $MoO_3$  dielectric interface provides much higher homogeneity compared to the  $SiO_2$  dielectric interface through a wafer-scale statistical analysis. We also fabricated the top-gate  $MoS_2$  FETs, and the synthetic  $MoS_2$  has good interfacial states to enable ALD-produced  $Al_2O_3$  dielectrics, as shown in Fig. 3(d).

Impacts of crystallinity and GBs. Compared to the single crystal triangle MoS<sub>2</sub>, the polycrystal circular MoS<sub>2</sub> possesses abundant GBs. To understand the impact of crystallinity and GBs on synthetic MoS<sub>2</sub>, we design one MoS<sub>2</sub> FET with the channel being parallel with a GB, and another device with the channel being perpendicular to the same GB, as shown in Fig. 3(e). Our results show comparable FET performance including  $J_{\rm D,on}$ , on/off ratio, and  $V_{\rm th}$ , suggesting negligible impact of GMs on the synthetic MoS<sub>2</sub> in this work.

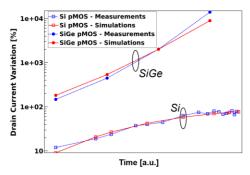

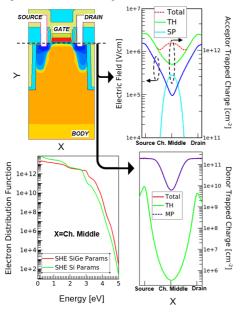

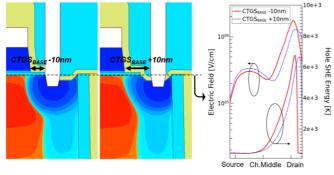

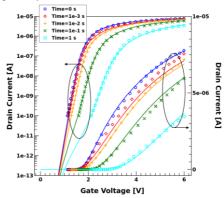

On-demand geometric manipulation of MoS<sub>2</sub> growth and metal contact improvement. Owing to the well-controlled growth, we can define the geometry of as-grown MoS<sub>2</sub> in arbitrary shapes without any lithography and etching process. For example, we create a long MoO<sub>3</sub> ribbon (5  $\mu$ m  $\times$  200  $\mu$ m) for transmission line measurement (TLM). The MoS<sub>2</sub> growth is remarkably uniform along the seeding pattern, as