## Vertical Inner Gate (VIG) Transistors for 4F<sup>2</sup> DRAM Cell

| Journal:                      | Electron Device Letters                                                                                                                                                                                                                                                                                                                                   |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Manuscript ID                 | EDL-2019-07-1573                                                                                                                                                                                                                                                                                                                                          |  |  |

| mstype:                       | Letters                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Date Submitted by the Author: | 1 3(1-1)11-7(1)19                                                                                                                                                                                                                                                                                                                                         |  |  |

| Complete List of Authors:     | Min, Kyungkyu; Seoul National University, ; SK Hynix Inc,<br>Hwang, Sungmin; Seoul National University, Department of Electrical<br>Engineering and Computer Science<br>Lee, Jong-Ho; Seoul National University, Department of Electrical and<br>Computer Engineering<br>Park, Byung-Gook; Seoul National University, School of Electrical<br>Engineering |  |  |

| Keyword:                      | Dynamic random access memory, 4F2 DRAM cell transistor, vertical gate transistor, vertical cell array transistor, floating body effect, transient bipolar effect                                                                                                                                                                                          |  |  |

|                               |                                                                                                                                                                                                                                                                                                                                                           |  |  |

SCHOLARONE™ Manuscripts

# Vertical Inner Gate (VIG) Transistors for 4F<sup>2</sup> DRAM Cell

Kyung Kyu Min, Student Member, IEEE, Sungmin Hwang, Student Member, IEEE, Jong-Ho Lee, Fellow, IEEE, and Byung-Gook Park, Member, IEEE

Abstract— In this paper, we propose a novel cell transistor structure to realize mass production of 4F<sup>2</sup> DRAM. 3D TCAD simulation results show that the proposed structure exhibits better DRAM operation margin than conventional vertical transistors. In particular, we confirmed that the fail mode due to the secondary effect of the floating body, which is the biggest problem of the 4F<sup>2</sup> DRAM, is dramatically improved by adopting this structure.

Index Terms—Dynamic random access memory (DRAM), 4F<sup>2</sup> DRAM cell transistor, vertical gate transistor, vertical cell array transistor, floating body effect, transient bipolar effect.

### I. Introduction

Dynamic random access memory (DRAM), the most important element of the memory-centric computing era, has been continuously scaled based on the simple structure of 1 transistor - 1 capacitor (1T1C). As with other semiconductor devices, the most common DRAM scaling method is to shrink the minimum feature size (F). Up to now, several generations have used the same buried gate (BG) structure [1]-[6] and a lot of optimizations are applied, which limits the scaling.

Another method of scaling DRAM is to reduce the space occupied by each unit cell. Unlike the current DRAM cell, if the storage node (SN) capacitor and the bit line (BL) are vertically arranged in the same space, the area occupied by unit cell is reduced from 6F<sup>2</sup> to 4F<sup>2</sup> [4], [7]-[12]. Such a change in scheme would result in a die area decrease of 33% at the identical technology node. In addition, the 4F<sup>2</sup> DRAM cell has advantage of completely eliminating row hammer failures due to word line (WL) disturbance, which is the biggest problem of DRAM in recent years [4], [13], [14].

However, the 4F<sup>2</sup> DRAM cell has disadvantages in the complicated integration process for structure formation and floating body effect (FBE) from vertical transistor [15], [16]. When the gate is turned off, a potential well is formed in the body region. Electron-hole pairs are generated by the gate

This work was supported in part by the Brain Korea 21 Plus Program in 2019.

K.K. Min is with the Inter-University Semiconductor Research Center, Department of Electrical Engineering and Computer Science, Seoul National University, Seoul 151-744, South Korea, and also with SK Hynix Inc., Icheon 17336, South Korea.

S. Hwang, J.-H. Lee and B.-G. Park are with the Inter-University Semiconductor Research Center, Department of Electrical Engineering and Computer Science, Seoul National University, Seoul 151-744, South Korea (e-mail: bgpark@snu.ac.kr).

induced drain leakage (GIDL) at the junction region, and generated holes are accumulated in the body potential well. Although body potential change by charged holes is the same as the general FBE [17], it causes another problem in the DRAM cell transistor. In the 1T-1C DRAM unit cell, one node of the transistor is connected to the SN capacitor. When the BL bias changes from high to low, the pn junction between hole charged p-type body and n-type BL is forward biased and turns on. At this moment, electrons injected from BL instantaneously move to the SN capacitor through the body and cause an additional loss of charges stored in the capacitor. This phenomenon, called the transient bipolar effect (TBE), causes severe retention deterioration [9]–[12].

In addition, implementation of conventional gate-all-around (GAA) type  $4F^2$  DRAM cell requires area for cell-to-cell isolation layer / WL / gate oxide / silicon (Si) channel / gate oxide / WL / cell-to-cell isolation layer within a limited space of 2F (Fig. 1 (c)). As the technology shrink progresses, however, the WL resistance increases sharply, and the problem of bias transfer to the target cell and the formation of the storage node due to the shortage of the Si open space in which the capacitor contact is formed are added. Thus, the mass production of  $4F^2$  DRAM cell has been delayed for more than a decade [18].

In this paper, we propose a vertical inner gate (VIG) transistor to solve the problem of conventional vertical gate (vertical outer gate - VOG) cell and improve the margin characteristics of DRAM cell transistor.

#### II. PROPOSED INNER VG CELL STRUCTURE

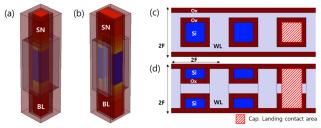

Fig. 1. (a) VOG structure. (b) Proposed VIG structure. Plan view of DRAM array through WL of (c) VOG and (d) VIG.

Like conventional DRAM cell transistor of 6F<sup>2</sup>, NMOSFET is used for VG transistor of the 4F<sup>2</sup> DRAM cell. n-type junction under p-type Si pillar channel is connected to the buried BL, and the top of the transistor is connected to the capacitor. In the GAA type VOG cell (Fig 1(a)), WL is separated into two parts at Si pillar passing region, resulting in a thin metal line which

causes a WL bias transfer problem [19]. Therefore, a VIG is proposed in which WL can pass through the Si pillar so that there is no thin metal line (Fig. 1. (b), (d)).

The form in which the WL passes through the Si is a process used in the existing 6F<sup>2</sup> DRAM cell in BG structure, which can be used to create a proposed structure easily. Because Si pillar size needs to be increased to apply this structure, there are also the advantage of reducing process difficulty due to increased area of capacitor landing contact. (Fig. 1.)

TABLE 1. Device Parameters for TCAD simulations.

| Minimum Feature Size (F)  | 25 nm                           | WL to WL Isolation width | 5 nm                  |

|---------------------------|---------------------------------|--------------------------|-----------------------|

| Si width                  | 20 nm                           | Gate oxide thickness     | 5 nm                  |

| WL width (Isolation area) | 5 nm x 2 (VOG)<br>5~10 nm (VIG) | Channel doping conc.     | 1e18 cm <sup>-3</sup> |

| WL width (Active area)    | 40 nm                           | Source (BL) Doping conc. | 5e20 cm <sup>-3</sup> |

| Gate length               | 100 nm                          | Drain (SN) Doping conc.  | 5e20 cm <sup>-3</sup> |

| S/D overlap length        | 200 Å                           | SN capacitance           | 10 fF/Cell            |

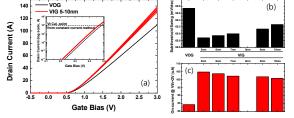

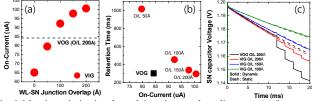

Fig. 2. Device characteristics of VIG and VOG cell. (a)  $I_d$ - $V_g$  curve at  $V_d = 1.2$ V (b) subthreshold swing (c) On-current (at V<sub>th</sub> + 2 V)

In this study, 3D TCAD Sentaurus (Synopsys<sup>TM</sup>) simulator (version K-2015.06-SP1) [20] was used to verify the characteristics of the proposed VIG cell. The simulation uses the dimension and doping concentration of Table 1 to target the 2x technology node. In order to reflect the characteristics of the DRAM, parameters and models correlated with the conventional DRAM cell transistor were applied.

#### III. CHARACTERISTICS OF VIG CELL

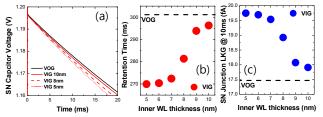

In the VIG cell, Si areas are divided into two regions, each of which is in the form of a thin tri-gate silicon-on-insulator (SOI). As a result, gate controllability will be reduced compared with the VOG cell which has a GAA structure. Unexpectedly, however, the simulation results show improved on-off margin (Fig. 2). Since each divided Si thickness is thinner than before, the channel region is fully depleted, which improves the controllability of the gate [21], [22] and adds a fringing field by the tri-gate type. However, since one of the surfaces surrounding the gate is removed, the region far from the gate is affected by the drain bias more than the gate in the off state, and the leakage current increases. Therefore, as shown in Fig. 3, the retention characteristic of VIG cell becomes worse than that of the VOG cell.

The resistance of one metal line with thickness of 8 nm can be smaller than that of two metal lines of 5 nm connected in parallel when the metal line thickness varies significantly depending on position [19]. Therefore, the thickness of WL of VIG structure can be adjusted considering the resistance. At this

time, if the Si pillar area is equalized to secure the SN contact area, on-off characteristic and retention characteristic change depending on the thickness of the inner WL (Fig. 2, 3). This is due to the effect of the fringing field caused by the gate out of the Si region in the tri-gate structure. The thinner WL increases the fringing field, improving on-off characteristics and deteriorating retention characteristics. However, if the inner WL becomes too thin, the voltage drop issue of the WL should be resolved by the structure.

Fig. 3. Retention characteristics of VIG and VOG cell. After a write pulse of 16 ns was applied for capacitor charging, the bias of WL and BL off state was maintained. (a) SN capacitor voltage through time (b) retention time of VGs (c) SN junction leakage current through time.

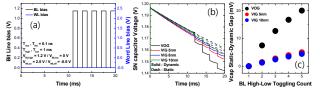

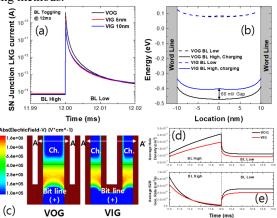

Fig. 4. Dynamic retention characteristic (a) WL/BL toggling pulse scheme for the transient simulation (b) SN capacitor voltage through time (c) additional SN voltage drop from BL toggling count

Since the floating body occurs naturally in the form of a VG DRAM cell, the dynamic retention is deteriorated by the TBE due to the body charged hole in the potential well. When data '1' is written in the target cell and WL is off, the BL bias may change to access to other cells sharing the BL with target cell. At this time, charge loss occurs in the SN capacitor, resulting in retention failure as BL togging is repeated. To confirm the dynamic retention characteristic, a time transient simulation was performed by applying a BL toggling bias shown in Fig 4 (a). The result shows that the VIG cell, which has relatively poor static response characteristics, shows better dynamic retention characteristics than the VOG cell. (Fig. 4) As with the other characteristics, dynamic retention changes according to the thickness of the inner WL, but the degree is smaller than that of the structural change. Therefore, the thickness of the inner WL should be determined in relation to the device margin and WL resistance rather than the dynamic retention.

When '1' data is written to SN and high bias is applied to BL, electron-hole pair generation occurs in two junction-gate overlap regions by gate off field. In this case, holes move to the potential well formed by the gate off bias at the channel region, and electrons move to the BL where positive bias is applied. Since the superposition effect of the field is reduced in the VIG structure where one side gate is missing, the gate off field is decreased in the VIG structure (Fig. 5(c)). Therefore, band-toband generated holes are reduced in the VIG structure and body accumulated holes are also reduced (Fig 5. (d)). As a result, the electron energy barrier between body (base) and BL (emitter), which causes TBE, is increased by 66mV, which reduces the

BJT current flow that generates charge loss from the SN. (Fig 5(e)) Therefore, the dynamic retention characteristic according to BL toggling is improved. Studies on improving the TBE in 4F<sup>2</sup> DRAM Cells have been conducted in terms of body contact formation [10]-[12] and junction engineering [9]. With our proposed structure, the problem can be solved by adopting the existing methods.

Fig. 5. (a) SN junction leakage current at BL toggling from high to low. (b) energy diagram of body region, BL low and HL high with hole charging state. (Channel center cut A-A' at (c), modified location of VIG cell for easy comparison) (c) electric field at BL high and WL off state. (d) average of accumulated hole density at body region (e) average band to band generation through BL toggling.

Fig. 6. Margin optimization through junction overlap adjustment (a) On-current characteristic (b) static retention time—on-current relationship through junction overlap. (c) Dynamic, Static retention characteristics.

In the DRAM cell, the write margin (on current) and the retention characteristics due to the GIDL characteristics are in a trade-off relation. The easiest way to deal with this trade-off relationship is to control the junction overlap. By reducing the junction overlap in the VIG structure, the on current improvement due to the structure can be used to compensate for poor retention characteristics. Fig 6 shows the margin optimization results using this trade-off relationship. Even if the overlap is reduced by 10 nm, the on current is still improved compared with the VOG structure, and the static retention characteristic can be improved by the reduction of GIDL. At the same time, the decreased overlap reduces the accumulated hole in the potential well during high BL condition, thereby also improving the dynamic retention characteristic. This shows the possibility of improving the overall operating margin characteristics in the 4F2 DRAM through the optimization of the VIG structure.

#### IV. CONCLUSION

In this paper, we proposed a novel 4F<sup>2</sup> DRAM cell scheme called VIG cell and verified its characteristics. In order to solve the problem of bias transmission in WL and lower the process

difficulty, we devised a VIG structure in which the gate is embedded in Si pillar. VIG structure has been confirmed to improve DRAM margins in terms of electrical characteristics and mitigate the dynamic retention issue caused by TBE, which is a key problem in 4F<sup>2</sup> DRAM. Through this novel DRAM cell transistor structure, the mass production of 4F<sup>2</sup> DRAM, which has been delayed for more than a decade, can be realized. The proposed cell is expected to make a significant contribution to sustaining computing innovation triggered by machine leaning and big data.

60

[1] H. Lee, D.-Y. Kim, B.-H. Choi, G.-S. Cho, S.-W. Chung, W.-S. Kim, M.-S. Chang, Y.-S. Kim, J. Kim, T.-K. Kim, H.-H. Kim, H.-J. Lee, H.-S. Song, S.-K. Park, J.-W. Kim, S.-J. Hong, and S.-W. Park, "Fully integrated and functioned 44nm DRAM technology for 1GB DRAM," 2008 Symposium on VLSI Technology, Honolulu, HI, 2008, pp. 86-87. doi: 10.1109/VLSIT.2008.4588572

REFERENCES

- [2] J.M. Park, Y.S. Hwang, S.-W. Kim, S.Y. Han, J.S. Park, J. Kim, J.W. Seo, B.S. Kim, S.H. Shin, C.H. Cho, S.W. Nam, H.S. Hong, K.P. Lee, G.Y. Jin, and ES Jung, "20nm DRAM: A new beginning of another revolution," 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, 2015, pp. 26.5.1-26.5.4. doi: 10.1109/IEDM.2015.7409774

- [3] K. K. Min, I.-W. Kwon, S. Cho, M. Kwon, T.-S. Jang, T.-K. Oh, Y.-T. Kim, S.-Y. Cha, S.-K. Park, and S.-J. Hong, "Study on the Sub-Threshold Margin Characteristics of the Extremely Scaled 3-D DRAM Cell Transistors," 2015 IEEE International Memory Workshop (IMW), Monterey, CA, 2015. doi: 10.1109/IMW.2015.7150305

- [4] S. Lee, "Technology scaling challenges and opportunities of memory devices," 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 2016, pp. 1.1.1-1.1.8. doi: 10.1109/IEDM.2016.7838026

- [5] K. Kim, "1.1 Silicon technologies and solutions for the data-driven world," 2015 IEEE International Solid-State Circuits Conference -(ISSCC) Digest of Technical Papers, San Francisco, CA, 2015, pp. 1-7. doi: 10.1109/ISSCC.2015.7062845

- [6] S. Park, "Technology Scaling Challenge and Future Prospects of DRAM and NAND Flash Memory," 2015 IEEE International Memory Workshop (IMW), Monterey, CA, 2015. doi: 10.1109/IMW.2015.7150307

- [7] S. Maeda, S. Maegawa, T. Ipposhi, H. Nishimura, H. Kuriyama, O. Tanina, Y. Inoue, T. Nishimura and N. Tsubouchi, "Impact of a vertical /spl Phi/-shape transistor (V/spl Phi/T) cell for 1 Gbit DRAM and beyond," in IEEE Transactions on Electron Devices, vol. 42, no. 12, pp. 2117-2123, Dec. 1995. doi: 10.1109/16.477769

- [8] K.-W. Song, J.-Y. Kim, J.-M. Yoon, S. Kim, H. Kim, H.-W. Chung, H. Kim, K. Kim, H.-W. Park, H. C. Kang, N.-K. Tak, D. Park, W.-S. Kim, Y.-T. Lee, Y. C. Oh, G.-Y. Jin, J. Yoo, D. Park, K. Oh, C. Kim and Y.-H. Jun, "A 31 ns Random Cycle VCAT-Based 4F<sup>2</sup> DRAM With Manufacturability and Enhanced Cell Efficiency," in IEEE Journal of Solid-State Circuits, vol. 45, no. 4, pp. 880-888, April 2010. doi: 10.1109/JSSC.2010.2040229

- [9] H. Chung, H. Kim, H. Kim, K. Kim, S. Kim, K.-W. Song, J. Kim, Y. C. Oh, Y. Hwang, H. Hong, G.-Y. Jin, C. Chung, "Novel 4F2 DRAM cell with Vertical Pillar Transistor(VPT)," 2011 Proceedings of the European Solid-State Device Research Conference (ESSDERC), Helsinki, 2011, pp. 211-214. doi: 10.1109/ESSDERC.2011.6044197

- [10] B. Goebel, J. Lutzen, D. Manger, P. Moll, K. Miimmler, M. Popp, U. Scheler, T. Schlosser, H. Seidl, M. Sesterhenn, S. Slesazeck and S. Tegen, "Fully depleted surrounding gate transistor (SGT) for 70 nm DRAM and beyond," *Digest. International Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, 2002, pp. 275-278. doi: 10.1109/IEDM.2002.1175831

- [11] Y. Cho, P. Choi, Y. Hyeon, J. Song, Y. Hwang and B. Choi, "Novel Band-to-Band Tunneling Body Contact (BTBC) Structure to Suppress the Floating- Body Effect in a Vertical-Cell DRAM," in IEEE Electron Device Letters, vol. 39, no. 12, pp. 1860-1863, Dec. 2018. doi: 10.1109/LED.2018.2874303

- [12] Y. Cho, H. Kim, K. Jung, B. Kim, Y. Hwang, H. Hong, and B. Choi., "Suppression of the Floating-Body Effect of Vertical-Cell DRAM With the Buried Body Engineering Method," in IEEE Transactions on Electron Devices, vol. 65, no. 8, pp. 3237-3242, Aug. 2018. doi: 10.1109/TED.2018.2849106

- [13] Y. Kim, R. Daly, J. Kim, C. Fallin, J. H. Lee, D. Lee, C. Wilkerson, K. Lai, and O. Mutlu, "Flipping bits in memory without accessing them: An experimental study of DRAM disturbance errors," in Proc. ACM/IEEE 41st Int. Symp. Comput. Archit., Jun. 2014, pp. 361–372, doi: 10.1109/ISCA.2014.6853210

- [14] T. Yang and X. Lin, "Trap-Assisted DRAM Row Hammer Effect," in IEEE Electron Device Letters, vol. 40, no. 3, pp. 391-394, March 2019. doi: 10.1109/LED.2019.2891260

- [15] A. Wei and D. A. Antoniadis, "Measurement of transient effects in SOI DRAM/SRAM access transistors," in IEEE Electron Device Letters, vol.

- 17, no. 5, pp. 193-195, May 1996. doi: 10.1109/55.491826

- [16] M. M. Pelella, J. G. Fossum, D. Suh, S. Krishnan, K. A. Jenkins and M. J. Hargrove, "Low-voltage transient bipolar effect induced by dynamic floating-body charging in scaled PD/SOI MOSFETs," in IEEE Electron Device Letters, vol. 17, no. 5, pp. 196-198, May 1996. doi: 10.1109/55.491827

- [17] J.-Y. Choi and J. G. Fossum, "Analysis and control of floating-body bipolar effects in fully depleted submicrometer SOI MOSFET's," in IEEE Transactions on Electron Devices, vol. 38, no. 6, pp. 1384-1391, June 1991. doi: 10.1109/16.81630

- [18] International Roadmap For Devices and Systems. More Moore. https://irds.ieee.org/images/files/pdf/2017/2017IRDS\_MM.pdf

- [19] F. Piallat and J. Vitiello, "At the edge between metal organic chemical vapor deposition and atomic layer deposition: Fast Atomic Sequential Technique, for high throughput conformal deposition", *Journal of Vacuum Science & Technology B*, vol 34, no 2, p 021202, 2 2016. doi: 10.1116/1.4942497

- [20] Sentaurus Sdevice User's Manual, Synopsys, Mountain View, CA, USA, 2018.

- [21] D. Tekleab, "Device Performance of Silicon Nanotube Field Effect Transistor," in IEEE Electron Device Letters, vol. 35, no. 5, pp. 506-508, May 2014. doi: 10.1109/LED.2014.2310175

- [22] B. S. Doyle, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, A. Murthy, R. Rios and R. Chau, "High performance fully-depleted tri-gate CMOS transistors," in *IEEE Electron Device Letters*, vol. 24, no. 4, pp. 263-265, April 2003. doi: 10.1109/LED.2003.810888