## TSMC/INTEL SOIC BRAINSTORM

Satish D., Scott S

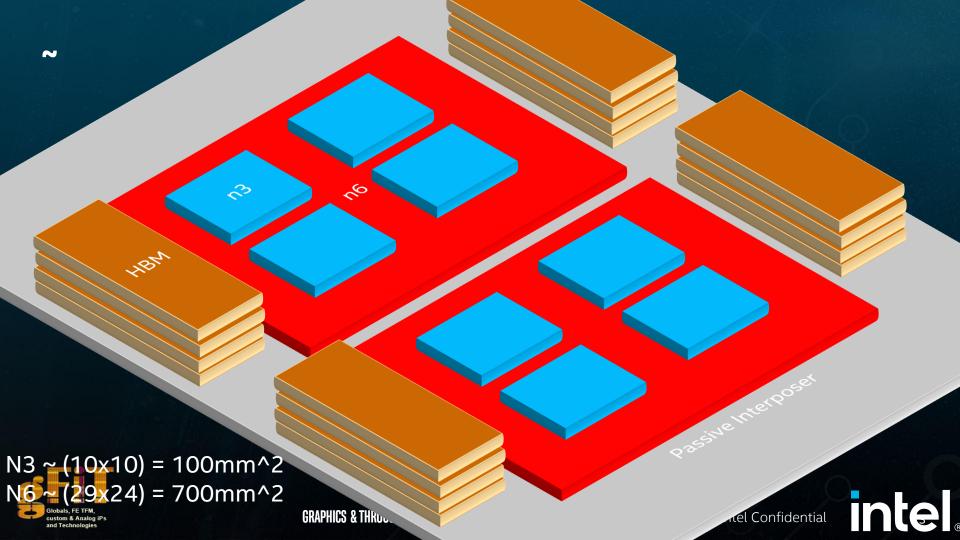

#### PROPOSAL CARTOON

# HBM Die1 – n3 Die2 – n3 Pa sive Interposer SolC –F2B 9um 40um to HBM? Larger over center of base die?

Pkg Substrate

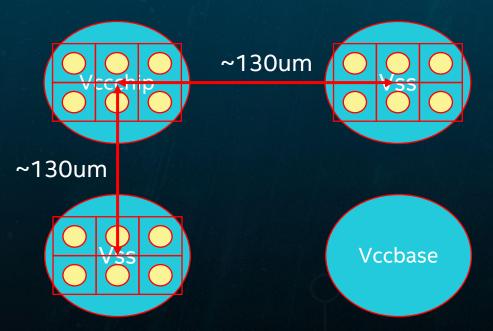

#### POTENTIAL POWER CONNECTION USING F2B

Put power TSV farm over C4 bump @ 130x130um pitches. No TSVs

needed over Vccbase C4s

#### MEETING THE DENSITY METRIC

- Proposed power TSV Align a group to the C4 bump to punch through to the top die.

- Propose a 3x2 array of TSV over top die power C4 bump plus miscellaneous power going to the top die.

- For a 100mm die(10x10) with 130um pitch C4, 77x77 C4 bump grid

- 5929 C4's

- 3000 VSS

- 750 base Vcc(no TSVs required), 2250 Top die Vcc+misc powers

- 5250 TSV groups \* 6 TSV/C4 = 31,500 TSVs

- 215k signal TSVs

- ~2\*4=46.5k \* 4um^2/TSV = 986k um^2 or 0.986mm^2

- Estimate about 1% total TSV density across the die for PDN only.

- Allows up to 1% additional opportunistic TSV placement for improved PDN in areas with no signal, and 1% additional for signal in area of signal.

#### POTENTIAL HIP CONNECTION USING F2B

36um between Hybrid Bond buffers (50% depopulation in X, none in Y)

Intel Confidential

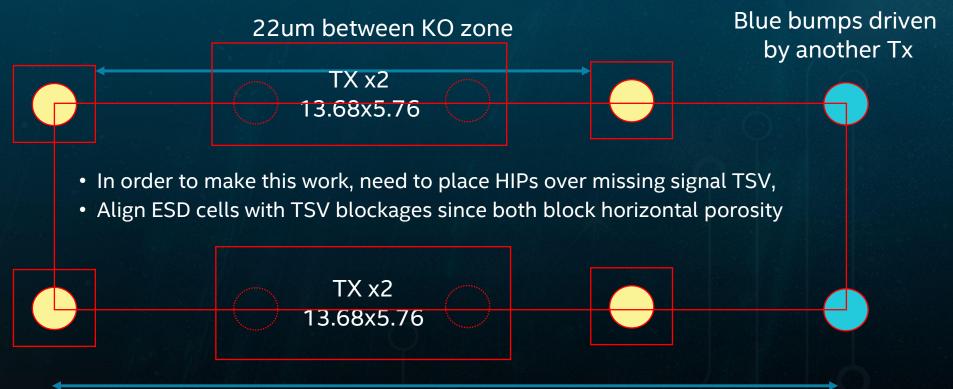

#### POTENTIAL HIP CONNECTION USING F2B

22um between KO zone

TX x2

13.68x5.76

- 6.28/324 = ~1.94% Just under max density of 2% -

- And we had ~1% for power TSV density looks to limit area for Hybrid Bond pads

- 45um = 1.55%

- Let's discuss this (window size=112/112 need to plan with power TSV's as well to get combined picture)

#### **IMAX CALCULATION**

• 50mA/TSV ~T=105C

• 50mA \* 2250 C4 for Vcctop \* 6 tsvs/C4 = 675A Imax.

• No issue with Imax ©

#### OTHER TOPICS

- Thermal Coefficients to do thermal analysis.

- How many die can we stack in this way?

- If base die contained memory, can we stack multiple base dies with a signal top die to increase memory capacity.

#### **SUMMARY**

- Power delivery –TSV density well within the bounds for density and easily meets Imax limits

- But 112um by 112um window may mean some windows have no TSV's (foils mention no minimum so assume this is OK)

- Signal density seems to be an issue

- At current n5 sizes for the HIP, TSV density will limit how tightly we can pack Hybrid Bond buffers

- We exceeded 2% with signals only

- How much of the 1% power overhead needs to be factored into the signal limit – requires further study of a full D2D Hybrid Bond pad plan including power Hybrid Bond pads.

### **BACKUP**

#### PROPOSAL CARTOON

F2B – Base die – which implementation?

2x2 diameter