# Memory shrink N7 to N5P

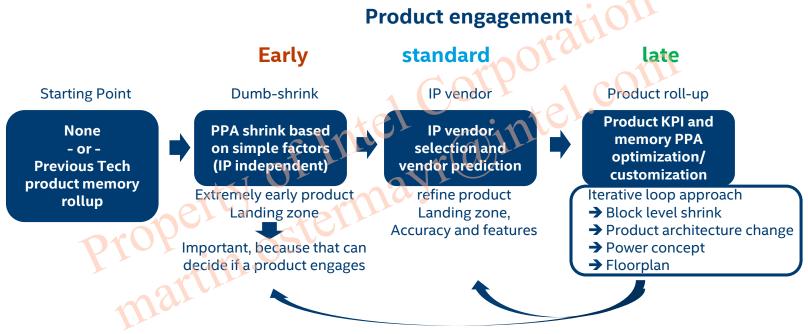

Iterative loop is applied through PLC

# **Dumb-shrink** → **Memory Technology**

|                    |                          | _                          |          |                          |                            |          |

|--------------------|--------------------------|----------------------------|----------|--------------------------|----------------------------|----------|

|                    | HC (high<br>current) 122 | HSHC (high<br>density) 122 | HC macro | HD (high<br>density) 111 | HSHD (high<br>density) 111 | HD macro |

| Area               | 75                       | 5%                         | 77%      | 78                       | 3%                         | 77%      |

| Performance        | -14% Iread               | -1% Iread                  | 11%      | -16.5% Iread             | -2% Iread                  | 13%      |

| Dynamic<br>Power   | -3%                      |                            | -8%      | -4%                      |                            | -9%      |

| Leakage<br>(Istby) | 1.05x                    | 2.2x                       | -30%     | 1x                       | 1.5x                       | -38%     |

| Assists            | NA/optional              | NA/optional                | t //     | WA                       |                            |          |

### SRAM Comparison (HD)

- N5 SRAM with aggressive cell size shrinkage. And offer same Vmin as all generations and same write assist amount...

- N5 introduce white space reduction for area further shrinkage 5%.

| HD                                   | N7        | N5     |

|--------------------------------------|-----------|--------|

| SRAM Cell                            | 0.0274    | 0.0214 |

| xFP                                  | 8         | 7.5    |

| SRAM Cell Shrink (%)                 | 76%       | 78%    |

| OD Pitch                             | 30        | 28     |

| PO Pitch                             | 57        | 51     |

| OD-PO Shrink (%)                     | 81%       | 84%    |

| Vmin                                 | +0        | +0     |

| sb (nA) 0.75V TT 125C                | 0.8       | 0.7    |

| Speed (ps) CV/I, TT                  | 0.246     | 0.249  |

| Design-Assist                        | WA        | WA     |

| Macro Area<br>(LEF to LEF)           | REF       | 73.5%  |

| Macro Area<br>(white space reduction | <b>OF</b> | 70%    |

# N5P v0.9 SRAM Offering (1)

Corner tighten, similar speed at corner

| N5P SRAM<br>(vs N7 v1.1)       | HC<br>N5P V0.5 |        |        | HSHC<br>N5P V0.9<br>(vs N7 HC |  |

|--------------------------------|----------------|--------|--------|-------------------------------|--|

| Cell Size (um^2)               | 0.0257         | 0.0257 | 0.0257 | 0.0257                        |  |

| Shrink                         | 75%            | 75%    | 75%    | 75%                           |  |

| Delay CV/I @0.75V<br>(TT, 25C) | -3%            | -3%    | -21%   | -20%                          |  |

| Iread                          | -14%           | -14%   | +1%    | -1%                           |  |

| sb@0.75V TT 25C                | 1.1X           | 1.05X  | 2.2X   | 2.2X                          |  |

| Isb (FFG 85C)                  | 1.0X           | 0.85X  | 3.0X   | 3.0X                          |  |

| Vmin                           | 675mV          | 675mV  | 675mV  | 675mV                         |  |

| R/W Asstssit                   | NA             | NA     | NA     | NA                            |  |

# N5P v0.9 SRAM Offering (2)

Corner tighten, more speed gain at corner

| N5P SRAM<br>(vs N7 v1.1)       | HD<br>N5P V0.5 | HD<br>N5P V0.9 | HSHD<br>N5P v0.5<br>(vs N7 HD) | HSHD<br>N5P V0.9<br>(vs N7 HD) |

|--------------------------------|----------------|----------------|--------------------------------|--------------------------------|

| Cell Size (um^2)               | 0.0214         | 0.0214         | 0.0214                         | 0.0214                         |

| Shrink                         | 78%            | 78%            | 78%                            | 78%                            |

| Delay CV/I @0.75V<br>(TT, 25C) | -3%            | -4%            | -22%                           | -21%                           |

| Iread                          | -17.5%         | -16.5%         | -2%                            | -2%                            |

| lsb@0.75V TT 25C               | 1.0X           | 1.0X           | 1.6X                           | 1.5X                           |

| Isb (FFG 85C)                  | 0.7X           | 0.62X          | 1.7X                           | 1.65X                          |

| Vmin                           | 675mV          | 675mV          | 675mV                          | 675mV                          |

| R/W Asstssit                   | WA             | WA             | WA                             | WA                             |

- HSHD write assist amount is under evaluation

- All SRAM target is subject to be changed.

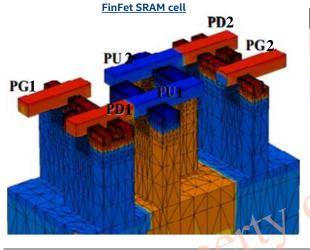

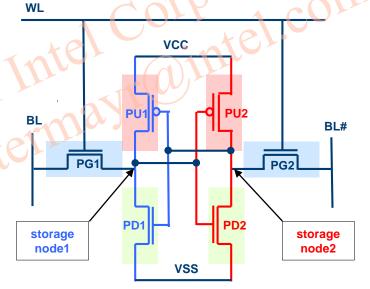

# Memory Bitcell Technology

|    | Description |      |

|----|-------------|------|

| PU | Pull up     | pFET |

| PD | Pull down   | nFET |

| PG | Pass gate   | nFET |

|    |             |      |

|          | Description |                       |

|----------|-------------|-----------------------|

| BL       | Bitline     | BL for storage node 1 |

| BL#, BLB | Bitline bar | BL for storage node 2 |

| WL       | Wordline    |                       |

xed width and length (FinPitch and PolyPitch)

→ tune the SRAM cell by number of fin's

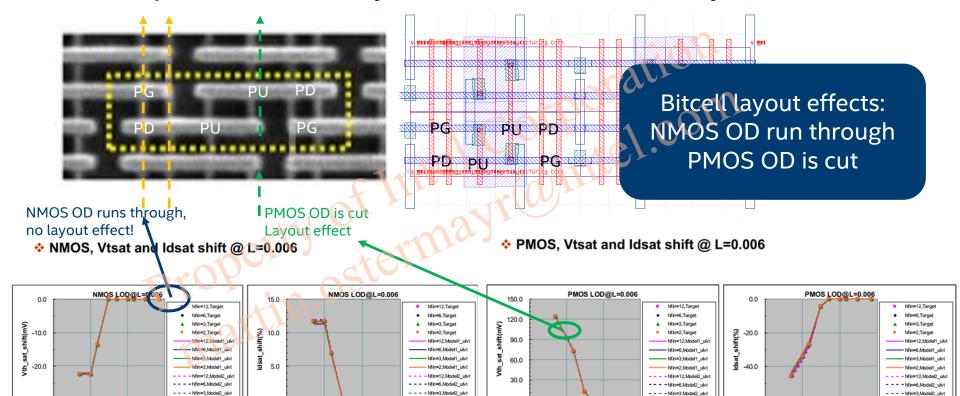

# Device impact on memory bitcell architecture (layout effects)

0.0

TSA1/TSB1(um)

-60.0

0.01

TSA1/TSB1(um)

- - Nfin=2,Model2\_ulvt

0.01

TSA1/TSB1(um

- Nfin=2.Model2\_ulvt

0.01

TSA1/TSB1(um)

- - - Nfin=2,Model2\_ulvt

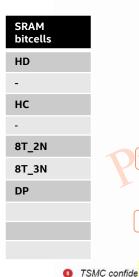

# Dump Shrink & Technology Bitcell offering

## **N7 SRAM**

# N5P SRAM Vt Proposal (Q3'19)

| SRAM Vt     | 6       | Т      | RP/DP/  |

|-------------|---------|--------|---------|

| (vs. Logic) | PU      | PG/PD  | Compare |

| HD          | SVT     | LVT_LL |         |

| HSHD        | LVT     | LVT    |         |

| HC          | SVT     | LVT_LL |         |

| нѕнс        | ULVT_LL | LVT    |         |

| 8T_2N (400) | SVT     | LVT_LL | ULVT_LL |

| 8T_3N (428) | SVT     | LVT_LL | ULVT_LL |

| DP          | SVT     | LVT_LL | LVT_LL  |

| 10T         | SVT     | LVT_LL | ULVT_LL |

| HP2 8T      | SVT     | LVT_LL | ULVT    |

| HP2 10T     | SVT     | LVT_LL | ULVT    |

→ Mixing up memory IP and

PPA shrink!

Change in bitcell offering is our fault

→ Intel requested it ⊗

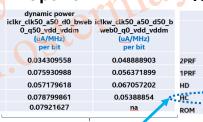

# Memory compiler 3<sup>rd</sup> party IP impact

## Thunder Bay Harbor (THB) memory content

### Synopsys N7 Memory leakage/dynamic power

#### leakage SRAM ref standby SRAM ref power OFF leakage TT SRAM ref retention leakage TT 25degC leakage TT 25degC VDD=0.75V 25degC VDD=0.55V (periphery off, Memory content lost) VDDM=0.75V [nA/bit] VDDM=0.525V [nA/bit] VDD = 0.55V VDDM 0.525V [nA/bit] 0.280241242 0.07168774 0.017990286 0.111254785 0.02839581 0.00504106 0.037010477 0.008463197 0.002224324 0.001613665 0.049712827 0.016193336 0.002343828 0.000570947

|                                                                        | leakage                                                                      |                                                                                                                     | dyna                                                          | mic power                                    |

|------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------|

| SRAM ref standby leakage<br>TT 25degC VDD=0.75V<br>VDDM=0.75V [nA/bit] | SRAM ref retention<br>leakage TT 25degC<br>VDD=0.55V<br>VDDM=0.525V [nA/bit] | SRAM ref power OFF leakage TT<br>25degC<br>(periphery off, Memory content lost)<br>VDD = 0.55V VDDM 0.525V [nA/bit] | iclkr_clk50_a50_d0_bw<br>eb0_q50_vdd_vddm<br>(uA/MHz) per bit | iclkw_clk50_i<br>0_q0_vdd_vd<br>(uA/MHz) per |

| 0.322277                                                               | 0.07219                                                                      | 0.0318428                                                                                                           | 0.046317903                                                   | 0.055                                        |

| 0.120155                                                               | 0.034643                                                                     | 0.0074608                                                                                                           | 0.046317903                                                   | 0.055                                        |

| 0.042192                                                               | 0.013456                                                                     | 0.0029361                                                                                                           | 0.058895006                                                   | 0.080                                        |

| 0.069101                                                               | 0.028338                                                                     | 0.0027755                                                                                                           | 0.066191883                                                   | 0.065                                        |

| 0.002039                                                               | na                                                                           | 0.00007422                                                                                                          | 0.035647321                                                   |                                              |

| *****************                                                      |                                                                              |                                                                                                                     |                                                               | 1                                            |

Leakage: values are in A br → Need to be multiplied with amount of bit per state Dynamic Power: values are in uA per bit

→ Need to be multiplied with WW (word-width) to be read/write

30% difference in 3rd party IP

Leakage: values are in mA/bit.

→ Need to be multiplied with amount of bit per state

TSMC N7 Memory leakage/dynamic power

Dynamic Power: values are in (MA/M)

per bit

Need to be multiplied with WV

→ Need to be multiplied with WW (word-width) to be read/write

a50 d50 bweb

er bit

5244461

5244461

0468642

5205133

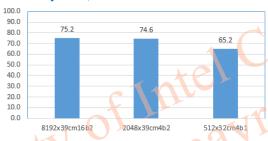

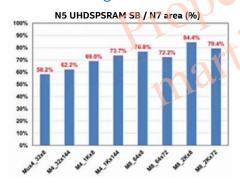

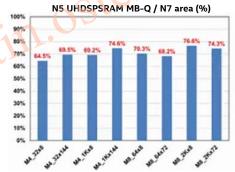

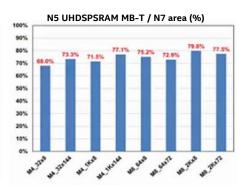

# N7 to N5 memory bitcell and compiler area scaling

### HC cell

- Bitcell scaling: 75.2%

- Macro scaling: 77% based on GPU/SoC benchmark

- → Macro scaling dependency on array size, CM and Bank

#### HD cell

- Bitcell scaling: 78.3%

- Macro scaling: 77% based on Intel SoC

# Memory compiler N7 to N5P evolution

#### PPA Comparison 1Kx32

|                                     | 28HPM         | 28HPC | 28HPC+ | 16FF+ LL | 16FFC/12FFC | 16FF+ GL | N7    | N5                |

|-------------------------------------|---------------|-------|--------|----------|-------------|----------|-------|-------------------|

| Silicon Area                        | ×             | ×     | ×      | 0.7x     | 0.7x        | 0.7x     | 0.30x | 0.23<br><b>77</b> |

| Freq<br>( SS_Vnom-10%40C)           | y<br>(1.6Ghz) | 1.1y  | 1.3y   | 1.5y     | 1.5y/1.6y   | 1.75y    | 70000 | 11%               |

| Leakage<br>(FFG_Vnom+10%_125C)      | z             | 0.73z | 0.8z   | 0.42z    | 0.45z       | 0.5z     | 0.30z | 30% <sup>21</sup> |

| Dynamic Power<br>(FF_Vnom+10%_125C) | р             | 1.0p  | 0.97p  | 0.85p    | 0.85p       | 0.85p    | 0.70p |                   |

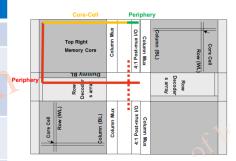

Memory options impacting PPA and shrink

### - bank

- bist mux in hip

- center decode

- column mux

- power gating

- \_dual rail

- periphery vt

- read assist

- repair

- scan in hip

- word depth

- word width

- write assist

### N7 Synopsys Memory Compiler Offering

|                         | 6T 1rw                            | 6T 1rw                         | 8T 2rw                     | 8T 2PRF<br>1r1w                                    | 2T 1r                  | 6T 1rw                        | 6T 1rw                   | 6T 1rw (de                          | 6T 1r1w<br>ouble pumped)            | 6T 1rw                            | 6T 1r1w<br>(double pumpe          |

|-------------------------|-----------------------------------|--------------------------------|----------------------------|----------------------------------------------------|------------------------|-------------------------------|--------------------------|-------------------------------------|-------------------------------------|-----------------------------------|-----------------------------------|

|                         | High<br>Speed SP<br>SRAM<br>(1RW) | High<br>Speed<br>Mini-<br>SRAM | High<br>Density<br>DP SRAM | High<br>Density<br>Register<br>File w/ 2<br>clocks | High<br>Density<br>ROM | High<br>Density<br>SP<br>SRAM | High<br>Density<br>1P RF | Ultra<br>High<br>Density<br>SP SRAM | (1R1W<br>/w 1 clk<br>but 1M<br>bit) | Ultra<br>High<br>Density<br>1P RF | Ultra<br>High<br>Density<br>2P RF |

| Total bits              | 256 -<br>1280k                    | 64-128k                        | 256 -<br>1280k             | 64-128k                                            | 256 -1280k             | 256 -<br>2560k                | 64-256k                  | 256 - 2560k                         | 256 - 1280k                         | 32-10K                            | 64-128k                           |

| Word range              | 32-16K                            | 8-1K                           | 32-16K                     | 8-1K                                               | 64 - 64k               | 32-32K                        | 8-2K                     | 32-32K                              | 32-32K                              | 4-256                             | 8-1K                              |

| I/O range               | 8-320                             | 8-256                          | 8-320                      | 8-256                                              | 4-160                  | 8-320                         | 8-256                    | 8-320                               | 8-320                               | 4-160                             | 8-256                             |

| Column mux              | 4,8,16                            | 2,4                            | 4,8,16                     | 1,2,4                                              | 8,16,<br>32,64         | 4,8,16                        | 1,2,4                    | 4,8,16                              | 4,8,16                              | 1                                 | 1, 2,4                            |

| Bank                    | 1,2,4,8                           | 1,2                            | 1,2,4,8                    | 1,2                                                | 1,2,4,8                | 1,2,4,8                       | 1,2                      | 1,2,4,8                             | 1,2,4,8                             | 1                                 | 1,2                               |

| Redundancy              | C,R                               | С                              | C,R                        | С                                                  |                        | C,R                           | С                        | C,R                                 | C,R                                 |                                   | С                                 |

| Periphery Vt<br>Options | LVT, uLVT                         | LVT, uLVT                      | SVT, LVT,<br>uLVT          | SVT, LVT,<br>uLVT                                  | SVT, LVT               | SVT, LVT                      | SVT, LVT                 | SVT, LVT                            | LVT, uLVT                           | SVT, LVT                          | SVT, LVT                          |

| Bitcell                 | 1-2-2<br>(0.0342)                 | 1-2-2                          | 1-2-2-4                    | 1-2-2-2 (0.049)                                    | Logic                  | 1-2-2                         | 1-2-2                    | 1-1-1<br>(0.0274)                   | 1-2-2                               | 1-2-2                             | 1-2-2                             |

<sup>·</sup> Optional assist circuitry for robust low voltage operation

# Memory Compiler Range

| Subject to Change 8T 2PRF |                       |                           |                         |                      |                     |                         |                       | (double pumped)                  |                                  |                             |                             |              |  |

|---------------------------|-----------------------|---------------------------|-------------------------|----------------------|---------------------|-------------------------|-----------------------|----------------------------------|----------------------------------|-----------------------------|-----------------------------|--------------|--|

| Oubject                   | 6T 1rw                | 6T 1rw                    | 8T 2rv                  | 8T 2rw 1r1w 2T 1     |                     |                         | 6T 1rw                | 6T 1rw (double pumped)           |                                  |                             | 6T 1rw                      |              |  |

| N5                        | High Speed SP<br>SRAM | High Speed 1P<br>RF Cache | High Density<br>DP SRAM | High Density<br>2PRF | High Density<br>ROM | High Density<br>SP SRAM | High Density<br>1P RF | Ultra High<br>Density SP<br>SRAM | Ultra High<br>Density 2P<br>SRAM | Ultra High<br>Density 2P RF | Ultra High<br>Density 1P RF | тсам         |  |

| Total bits                | 256 - 1280k           | 128-288k                  | 256 - 1280k             | 64-128k              | 256 -1280k          | 256 - 2560k             | 128-256K              | 256 - 2560k                      | 256 - 2560k                      | 128-256k                    | 128-256K                    | 256-80K      |  |

| Word range                | 32-16K                | 16-2K                     | 32-4K                   | 8-1K                 | 64 - 64k            | 32-32K                  | 16-2K                 | 32-32K                           | 32-32K                           | 8-2K                        | 16-2K                       | 32-512       |  |

| I/O range                 | 8-320                 | 8-288                     | 8-320                   | 8-256                | 4-160               | 8-320                   | 8-256                 | 8-320                            | 8-320                            | 16-256                      | 8-256                       | 8-160        |  |

| Column mux                | 4,8,16                | 2,4                       | 4*                      | 1,2,4                | 8,16,32,64          | 4,8,16                  | 1,2,4                 | 4,8,16                           | 4,8,16                           | 1,2,4                       | 1,2,4,8                     | 1            |  |

| Bank                      | 1,2,4,8               | 1,2                       | 1,2,4,8                 | 1,2,4,8              | 1,2,4,8             | 1,2,4,8                 | 1,2                   | 1,2,4,8                          | 1,2,4,8                          | 1,2                         | 1,2                         | 1            |  |

| Redundancy                | C,R                   | С                         | C,R                     | С                    | -                   | C,R                     | С                     | C,R                              | C,R                              | С                           | С                           | С            |  |

| Periphery Vt<br>Options   | eLVT, LVT,<br>ULVT    | eLVT, LVT,<br>ULVT        | SVT, LVT, ULVT          | SVT, LVT, ULVT       | SVT, LVT, ULVT      | SVT, LVT, ULVT          | SVT, LVT, ULVT        | SVT,LVT, ULVT                    | SVT,LVT, ULVT                    | SVT, LVT,ULVT               | SVT, LVT,ULVT               | SVT, LVT,ULV |  |

| Bitcell                   | 1-2-2                 | 1-2-2                     | 1-2-2-4                 | 1-2-2-2              | Logic               | 1-2-2                   | 1-2-2                 | 1-1-1                            | 1-2-2                            | 1-2-2                       | 1-1-1                       | 1-2-2        |  |

| Bitcell (Area)            | 0.0257                | 0.0257                    |                         | 0.0428, HC           |                     | 0.0257                  | 0.0257                | 0.0214                           | 0.0257                           | 0.0257                      | 0.0214                      |              |  |

For High Speed SP SRAM & 1P RF Cache

Read Port -120mV (requires keeper ...

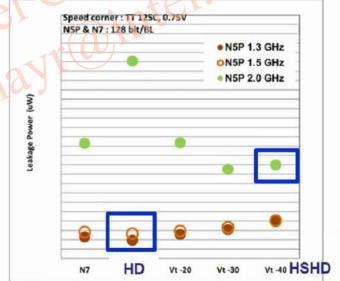

# N5P HD/HSHD PPA Comparison

2019-07-17, Session: N5P SRAM

- HSHD for high speed (2G), HD for SOC memories (1G/1.3G/1.5G)

- HD/HSHD co-exists to optimize active leakage power

### N5P V0.5P SRAM

| N5P SRAM V0.5p<br>(vs N7 v1.1) | HC<br>(vs N7 HC) | HSHC<br>(vs N7 HC) | HD<br>(vs N7 HD)   | (vs N7 HD)         |

|--------------------------------|------------------|--------------------|--------------------|--------------------|

| Cell Size (um^2)               | 0.0              | 257                | 0.0                | 214                |

| Shrink                         | 75               | 5%                 | 78                 | 3%                 |

| Delay CV/I @0.75V<br>(TT, 25C) | -3%              | -21%               | -2%                | -21%               |

| Iread                          | -14%             | +1%                | -18.5%             | -3%                |

| Isb@0.75V TT 25C               | 1.1X             | 2.6X               | 1.0X               | 1.8X               |

| Isb (FFG 85C)                  | 1.0X             | 3.3X               | 0.7X               | 1.7X               |

| Vmin                           | 675mV            | 675mV              | 675mV              | 675mV              |

| R/W Assist                     | NA               | NA                 | WA<br>(=N7, 150mV) | WA<br>(=N7, 150mV) |

- HSHD write-assist amount: Same as HD.

- All SRAM target is subject to be changed.

### Remark:

Value proposition of HSHD cell.

N5P vs. N7 Active Lkg Power @ same speed

TSMC confidential materials

# N5P memory compiler SNPS-TSMC matrix

|                                    | 1                                                                                                     |                                                                                                                                                       |  |  |  |  |  |

|------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Memory compiler IP vendor overview |                                                                                                       |                                                                                                                                                       |  |  |  |  |  |

|                                    | TSMC                                                                                                  | Synopsys                                                                                                                                              |  |  |  |  |  |

| memory portfolio                   | •                                                                                                     | ++                                                                                                                                                    |  |  |  |  |  |

| Special memory compiler            | -                                                                                                     | + (TCAM added to std. offering)                                                                                                                       |  |  |  |  |  |

| memory compiler range              | limited WW/WD need SoW for larger config → need precise instances early! → customization hardly used! |                                                                                                                                                       |  |  |  |  |  |

| Metal usage                        | finished at M3, M4 over-routing on custom request (WL-doubling)                                       | finished at M3. M4 over-routing on custom request (WL-doubling)                                                                                       |  |  |  |  |  |

| Margin Methodology                 | +                                                                                                     |                                                                                                                                                       |  |  |  |  |  |

| Trimming Capability                | +<br>TSMC will make EMA pins available                                                                | Intensive RM/Assist trimming capability                                                                                                               |  |  |  |  |  |

| Read / Write Assist                | +<br>write assist for HD compiler                                                                     | Read Assist always in, Write Assist optional Protential for lower Voltage operation                                                                   |  |  |  |  |  |

| Repair capability                  | IO repair offered (contradicting to repair rules) unsuitable for large memory content products        | IO repair and Row repair available                                                                                                                    |  |  |  |  |  |

|                                    |                                                                                                       |                                                                                                                                                       |  |  |  |  |  |

| Area                               | +<br>Best on instance level                                                                           | Can realize larger instances at higher speed → area gain due to less logical memories                                                                 |  |  |  |  |  |

| Implementation Area overhead       |                                                                                                       | (overlay concept densest option available)                                                                                                            |  |  |  |  |  |

| Performance                        | HD/SP compiler requires additional custivation                                                        | ME gating option for chip enable time improvement Better performance allows SVT periphery usage = save Power SVT / LVT / LLVT memory periphery option |  |  |  |  |  |

| Power Management                   | diode and diode bypass for Retention feature                                                          | +<br>diode and diode bypass for Retention feature                                                                                                     |  |  |  |  |  |

| Power Features                     | tstdby, deep sleep, power off                                                                         | ++<br>Istdby, light retention, deep sleep, power off, POFF retention, POFF SD, input gating for dynamic power reduction                               |  |  |  |  |  |

| Level shifter                      | -<br>LS at the boundary                                                                               | ++ LS in the middle of WL-dec (periphery) → power benefit   LS at the boundary   virtual level shifter                                                |  |  |  |  |  |

| Dynamic Power                      |                                                                                                       | +                                                                                                                                                     |  |  |  |  |  |

| Leakage (Istby)                    | +                                                                                                     | +                                                                                                                                                     |  |  |  |  |  |

| Leakage (light sleep)              | not available                                                                                         | +                                                                                                                                                     |  |  |  |  |  |

| Leakage (Retention)                |                                                                                                       | +                                                                                                                                                     |  |  |  |  |  |

| Leakage (PWROFF)                   | + (VDDM collapse)                                                                                     | + (VDDP collapse)                                                                                                                                     |  |  |  |  |  |

| Silicon Verification               | ++ will have intensive verification (accept further customizations)                                   | + Silicon verification on SNPS testchip; improved coverage after Intel request                                                                        |  |  |  |  |  |

| Schedule                           | + PDK 0.5; customization needs to be planned                                                          | +<br>PDK 0.5; PVT sign-off corners required                                                                                                           |  |  |  |  |  |

| Implementation Risk                | +                                                                                                     | + (N7 multi product usage)                                                                                                                            |  |  |  |  |  |

| Memory optimizer/explorer          | ++ → Covered by IPSG TEG memlister integration!                                                       | ++  → Covered by IPSG TEG memlister integration!                                                                                                      |  |  |  |  |  |

# Memory IP customization

### **Gracemont N5 Testchip customization**

### Intel N5 Instances

IP : ATOM (Optimize : Performance)

| IP   | Functional Name                           | Target<br>Tcc<br>(ps) | Target<br>Tcq<br>(ps) | Depth | Width | СМ     | вк    | Center<br>Decode | Bit<br>Write<br>Enable | Periphery<br>Vt | Vdda<br>Enable | Power<br>Gating | Redund<br>ancy<br>Enable | Bist<br>Enable | Scan<br>Enable | Area<br>(μ²) | N5<br>Tccrm4<br>(ps) | N5<br>Tcqrm4<br>(ps) | N5<br>Tac<br>(ps) | N5<br>Tccrm7<br>(ps) | N5<br>Tcqrm7<br>(ps) |

|------|-------------------------------------------|-----------------------|-----------------------|-------|-------|--------|-------|------------------|------------------------|-----------------|----------------|-----------------|--------------------------|----------------|----------------|--------------|----------------------|----------------------|-------------------|----------------------|----------------------|

|      | HD2PRF (1-2-2-3-3): ts05n0g42p11sacri128s |                       |                       |       |       |        |       |                  |                        |                 |                |                 |                          |                |                |              |                      |                      |                   |                      |                      |

| Atom | 128ex48b                                  | 300                   | 135                   | 128   | 48    | 1      | 4     | TRUE             | TRUE                   | ULTRALOW        | FALSE          | FALSE           | FALSE                    | FALSE          | FALSE          | 902          | 298                  | 149                  | 44                | 272                  | 144                  |

| Atom | 256x68                                    | 300                   | 135                   | 256   | 68    | 2      | 4     | TRUE             | TRUE                   | ULTRALOW        | FALSE          | FALSE           | FALSE                    | FALSE          | FALSE          | 1869         | 307                  | 164                  | 44                | 282                  | 160                  |

| Atom | 512x36                                    | 300                   | 135                   | 512   | 36    | 4      | 4     | TRUE             | TRUE                   | ULTRALOW        | <b>FALSE</b>   | FALSE           | FALSE                    | FALSE          | FALSE          | 1958         | 307                  | 169                  | 45                | 282                  | 164                  |

| Atom | 64ex72*                                   | 300                   | 135                   | 64    | 72    | 1      | 2     | TRUE             | TRUE                   | ULTRALOW        | FALSE          | FALSE           | FALSE                    | FALSE          | FALSE          | 770          | 271                  | 139                  | 51                | 246                  | 135                  |

|      |                                           |                       |                       |       | HS1   | PRF    | (1-2- | -2) : ts05       | n0g41p1                | 1sasrl256s      |                |                 |                          |                |                |              |                      |                      |                   |                      |                      |

| Atom | 1024W x 62b cm4                           | 600                   | 200                   | 1024  | 62    | 4      | 2     | TRUE             | TRUE                   | ULTRALOW        | <b>FALSE</b>   | FALSE           | FALSE                    | FALSE          | FALSE          | 3187         | 214                  | 214                  | 43                | 186                  | 186                  |

| Atom | 1536x72 cm4                               | 600                   | 200                   | 1536  | 72    | 4      | 2     | TRUE             | FALSE                  | ULTRALOW        | FALSE          | FALSE           | FALSE                    | FALSE          | FALSE          | 4743         | 262                  | 224                  | 50                | 234                  | 195                  |

| Atom | 2048x72 cm4                               | 600                   | 220                   | 2048  | 72    | 4      | 2     | TRUE             | FALSE                  | ULTRALOW        | FALSE          | FALSE           | FALSE                    | FALSE          | FALSE          | 5884         | 306                  | 252                  | 58                | 278                  | 220                  |

| Atom | 1024W x 56b cm4                           | 600                   | 270                   | 1024  | 56    | 4      | 2     | TRUE             | TRUE                   | ULTRALOW        | FALSE          | FALSE           | FALSE                    | FALSE          | FALSE          | 2938         | 212                  | 212                  | 43                | 184                  | 183                  |

| Atom | 1024W x 40b cm4                           | 600                   | 270                   | 1024  | 40    | 4      | 2     | TRUE             | TRUE                   | ULTRALOW        | FALSE          | FALSE           | FALSE                    | FALSE          | FALSE          | 2064         | 212                  | 207                  | 43                | 184                  | 179                  |

|      |                                           |                       |                       |       | HD    | SP (1  | -2-2  | ) : ts05n0       | g41p11s                | sadcl02ms       |                |                 |                          |                |                |              |                      |                      |                   |                      | . 1                  |

| Atom | 4096x68 cm4                               | 600                   | 300                   | 4096  | 68    | 4      | 4     | TRUE             | FALSE                  | ULTRALOW        | FALSE          | FALSE           | FALSE                    | FALSE          | FALSE          | 10109        | 482                  | 365                  | 107               | 453                  | 326                  |

|      |                                           |                       |                       |       | ROM   | ۸ (Via | MD    | ) : ts05n(       | )g41p10a               | asdvd01ms       |                |                 |                          |                | $\mathcal{I}$  |              |                      |                      |                   |                      |                      |

| Atom | rom 4608ex12b                             | 600                   | 440                   | 4608  | 12    | 16     | 2     |                  |                        | ULTRALOW        | FALSE          | FALSE           | FALSE                    | FALSE          | FALSE          | 787          | 427                  | 406                  | 68                | 395                  | 382                  |

| Atom | rom 1024ex16b                             | 600                   | 340                   | 1024  | 16    | 8      | 1     | FALSE            | FALSE                  | ULTRALOW        | FALSE          | FALSE           | FALSE                    | FALSE          | FALSE          | 324          | 365                  | 340                  | 49                | 332                  | 323                  |

Meets & beats the required Freq target @ RM7 Timing Mode at TT/0.95V/85C

RM4 Timing Mode at TT/0.95V/85C

\*All the data with 1R1W memory for this instance instead of 2R1W memory

No further push on Tcg values

N5 PVTs

### Timelines and deliveries

### Intel N5 Instances

ATOM / MIG / OTP (HD 2PRF using 12233, HDSP SRAM, ROM, HS1PRF RF)

| Si No | . Milestone             | Views                                                                                                                                                                             | Required Schedule                           | Synopsys Commit<br>(17th June 2019)                                 | Comments                                                        |

|-------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------|

| 1     | FE views                | Preliminary FE view - (LEF - Prelim ; Timing - Prelim meeting the<br>Freq target, Hold and Setup are also prelim)<br>PVT - Priority 1; Views from Table 1.1                       | ASAP                                        | 20th June 2019<br>(Atom)<br>26 <sup>th</sup> June 2019<br>(MIG/OTP) | Delivered                                                       |

| 1.1   | Preliminary<br>FF views | Preliminary FE view - (LEF - Prelim ; Timing - Prelim meeting the<br>Freq target, Hold and Setup are also prelim)<br>PVT - Priority 1 (2 PVTs); Views from Table 1.1              | ASAP                                        | 10th July 2019                                                      | Re-deliver the Atom<br>package for new<br>instances and targets |

| 2     | Not to Grow             | Not to Grow - (LEF - Not to Grow X/Y; Signal pin order final; Signal<br>/ power pin position could change; Timing - Not to grow timing)<br>PVT - Priority 1; Views from Table 1.1 | Jul-19                                      | 31st July 2019                                                      |                                                                 |

| 2.1   | Back End                | Backend Views (LEF - Final; power pin position frozen up to 80%;<br>Timing – Not to grow; GDSII – LVS, DRC Unclean)<br>PVT - Priority 1 & 2; Views from Table 1.2                 | 31st Aug 2019                               | 31st Aug 2019                                                       | New Milestone                                                   |

| 3     | Back End                | Backend Views (LEF - Final; Timing - Final; GDSII - LVS Clean , DRC<br>Unclean)<br>PVT - Priority 1 & 2; Views from Table 1.3                                                     | 7th Oct 2019                                | 7th Oct 2019                                                        |                                                                 |

| 4     |                         | Final GDSII<br>PVT - Priority 1 & 2; Views from Table 1.3                                                                                                                         | 11th Nov 2019<br>31 <sup>st</sup> Oct. 2019 | 11th Nov 2019<br>31 <sup>st</sup> Oct. 2019                         | This GDSII will be Plug<br>and verify for Intel                 |

### Views Table 1.1

| Views      | Details                                                   | Views    |

|------------|-----------------------------------------------------------|----------|

| pief       | LEF                                                       | atpg_t   |

| silpvt     | Combined Datasheet for all PVT corners                    | stid or  |

| allpythtml | Datasheet for HTML                                        | std or   |

| dssum      | Summary                                                   | shd_ce   |

| veniog     | Verling Behavioral/RTL Model                              | std : ce |

| syn        | Synopsys Model                                            | fast fu  |

| fastscan   | Fastscan Model                                            | masks    |

| tof        | Fastscan Initialization File                              | pawer    |

| tetramax   | Tetramax Model                                            | apt      |

| tol        | Tetramax Initialization File                              | ct       |

| Mib        | Tessent MemoryBIST Model                                  | upf      |

| vhd_rtl    | VHDL RTL Model                                            | ikos     |

| stim       | Verling Behavioural Model and Verling Netlist Testbench   | core     |

|            | Markon Saltonian and Market and Wast Baltonian and Market |          |

## Views

|     | Verliog Netlist for ATPG                      |

|-----|-----------------------------------------------|

|     | Verling cell library for behavioral model     |

| ,   | Fastscan cell library for ATPG                |

|     | Verling cell library for Tetramax             |

|     | Liberty Model for Standard cells              |

| log | Fast functional Verilog Model                 |

|     | Memory and SMS Information Standard           |

|     | Power Verling Model                           |

|     | Common Power Format Model                     |

|     | Core Test Language Model                      |

|     | IP UPF Model                                  |

|     | Synthesizable RTL Model for ikos              |

|     | Core used by Synthesizable RTL Model for itos |

|     |                                               |

INFRASTRUCTURE & PLATFORM SOLUTIONS GROUP (IPSG) | INTEL CONFIDENTIAL

# Memory

### **Memory Technology**

- Memory bitcell offering:

- Vmin yield trend

- EOL commit and screening recommendation

- HD/HC Vmin and Vsdr through temp

- HD/HC Vmin and Vsdr through process corner

2 new cells offered HSHC/HSHD; special cells, CRAM, TCAM ... on customer request native Vnom: HD86%/72%; HC 87%/77% slightly ahead of plan!

0.675V EOL, 95% 256Mbit, 75mV aging GB, 0.6V T0 screen 95% Vmin 530mV/500mV; Vsdr 380mV/370mV no flyers!

|    | 5 256M<br>in @95% | spec | SF  | TT  | FS  |

|----|-------------------|------|-----|-----|-----|

| нс | Vmin (mV)         | 675  | 640 | 538 | 575 |

| HD | Vmin (mV)         | 675  | 557 | 554 | 612 |

Operation voltage and operation voltage range (Power supply voltage)

Overdrive capability and absolute Vmax floor

identical to N7; 0.96V Vmax ceiling incl. ripple! Higher Vmax possibible with reduced product profile (TSMC 10y always on 125C)

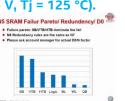

### **Memory QnR**

- N5 SRAM redundancy and IFR/ECC rules

- N5 DVS memory condition

- N5 memory reliability and EB

- SRAM fail pareto (HD/HC)

- Memory test algorithms

N5 memory product qualification (technology capability) 256Mbit as major vehicle, for both HD/HC (512Mbit total)

follow TSMC guideline and increase ECC free density by product require DVS at 1.6V for logic and 1.4V for SRAM, 25C ~1sec?

HD/HSHD requires 128bit strapping

HC/HD passed 3lots 1000h (Samples have been screened prior to HTOL by applying DVS (1.40 V, 25 °C, 1 s), and post-DVS Vmin-limit of 0.600 V at 25 °C. HTOL read-outs have been done at 85 °C and after 1000 hrs of stress (1.19 V = 1.4 x 0.85 V, Tj = 125 °C).

VTB is still there and HTB became 3rd place in the pareto plot

identical to N7 → follow Intel TEG bottom up approach!!!

# N5P Vmin yield and comparison to N5

# **N5P SRAM General Offering**

|                  | N5P                      | SRA                      | AM G   | ene    | ral O           | fferi           | ng     | Security-C | ors | t |

|------------------|--------------------------|--------------------------|--------|--------|-----------------|-----------------|--------|------------|-----|---|

| N5 SRAM          | HD                       | HSHD                     | нс     | нѕнс   | 8T2P<br>(RP=2N) | 8T2P<br>(RP=3N) | DP     | 10T        | +01 |   |

| Size (um2)       | 0.0214                   | 0.0214                   | 0.0257 | 0.0257 | 0.0400          | 0.0428          | 0.0571 | 0.0571     | VIC |   |

| Vdd (V)          | 0.75                     | 0.75                     | 0.75   | 0.75   | 0.75            | 0.75            | 0.75   | 0.75       |     |   |

| Vmin (V)         | 0.675                    | 0.675                    | 0.675  | 0.675  | 0.675           | 0.675           | 0.675  | 0.675      |     |   |

| Design<br>Assist | Write<br>Assist<br>(=N7) | Write<br>Assist<br>(=N7) | NA     | NA     | SNAC            | NA              | NA     | NA         |     |   |

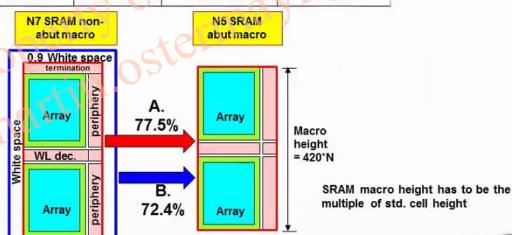

# N5 HC SRAM macro scaling

Security C –

- HC SRAM bit cell scaling 75.2%

- N5 macro area scaling vs. N7 77.5% (LEF vs. LEF) and 72.4% (if count in N7 white space)

- White space reduction only works for H210 standard cell

| НС    | 1PRF (ref.) | w/o white space<br>(LEF vs. LEF, N5<br>abut macro) (A) |       |

|-------|-------------|--------------------------------------------------------|-------|

| Macro | 256x144M2   | 77.5%                                                  | 72.4% |

White space