## From Technologies to Markets

# Memory Packaging

Market and Technology Report 2021

## **GLOSSARY**

ASIC: Application Specific Integrated Circuit

ASSP: Application Specific Standard Product

**ASP**: Average Selling Price

**APU**: Application Processor Unit

**BEOL**: Back End of Line

**CAGR**: Compound Annual Growth Rate

**CMOS**: Complementary Metal Oxide Semiconductor

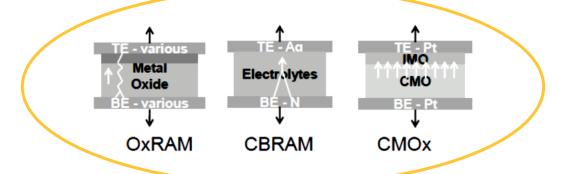

**CMOX**: Conductive Metal-Oxide

**DDR**: Double Data Rate

**DIMM**: Dual In-Line Memory Module

**DRAM**: Dynamic Random-Access Memory

**ECC**: Error Code Correction EUV: Extreme Ultra-Violet

$F^2$ : Memory-cell size unit (F is the smallest feature size)

FC: Flip-Chip

**FEOL**: Front End of Line

**FFET**: Ferroelectric Field-Effect Transistor

**FRAM**: Ferroelectric RAM

FPGA: Field-Programmable Gate Array

GDDR: Graphics DDR (used in GPU)

**HBM**: High Bandwidth Memory

**HMC**: Hybrid Memory Cube

IOPS: Input/Output Operations Per Second

**LPDDR**: Low-Power DDR (used in mobile applications)

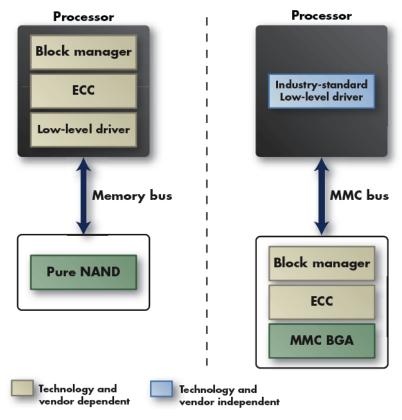

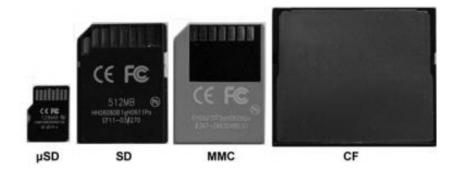

MMC: Multimedia Card (Packaging Standard)

MCP: Multi-Chip Package

ML: Machine Learning

MLC: Multi-Level Cell

**MPU**: Microprocessor Unit

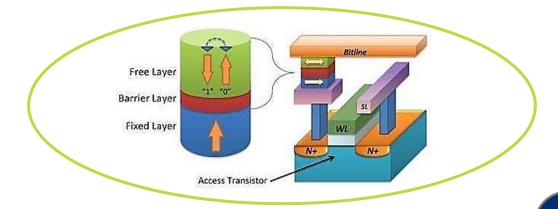

MRAM: Magnetic Random-Access Memory

NAND: Flash memory with logical NAND-type structure

NOR: Flash memory with logical NOR-type structure

**NRAM**: Nanotube RAM

**NV**: Non-Volatile

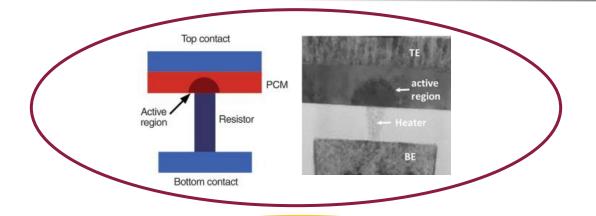

PCM: Phase-Change Memory

PCB: Printed Circuit Board

PoP: Package-on-package

QLC: Quad Level Cell

**RRAM**: Resistive Random-Access Memory

**SAM**: Serviceable Available Market

**SAQP:** Self-Aligned Quadruple Patterning

**SCM**: Storage Class Memory

SiP: System-in-Package SLC: Single-Level Cell

**SoC**: System-on-Chip

**SRAM**: Static Random-Access Memory

**SSD**: Solid-State Drive

**STT**: Spin-Transfer Torque Magnetic RAM

**TAM**: Total Accessible Market

**TLC**: Triple Level Cell **TSV**: Through-Silicon Via

**WLCSP**: Wafer Level Chip Scale Packaging

WB-BGA: Wire-bond Ball Grid Array

x, y, z: indicate the technology generation in a given class, e.g., ly denotes

the 2<sup>nd</sup> generation of the "10nm class"

## **DEFINITIONS – MEMORY TECHNOLOGIES**

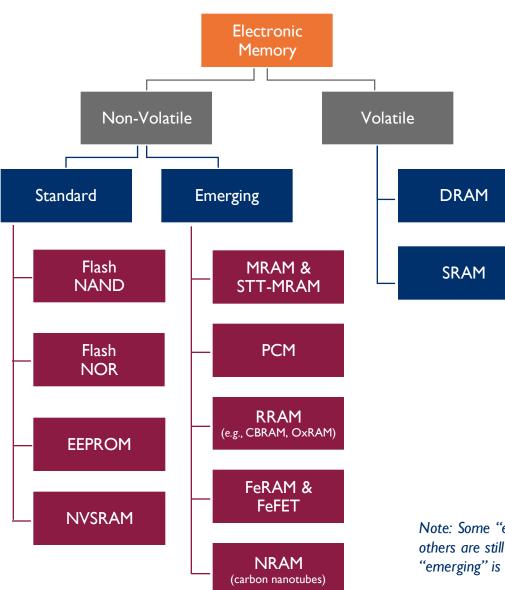

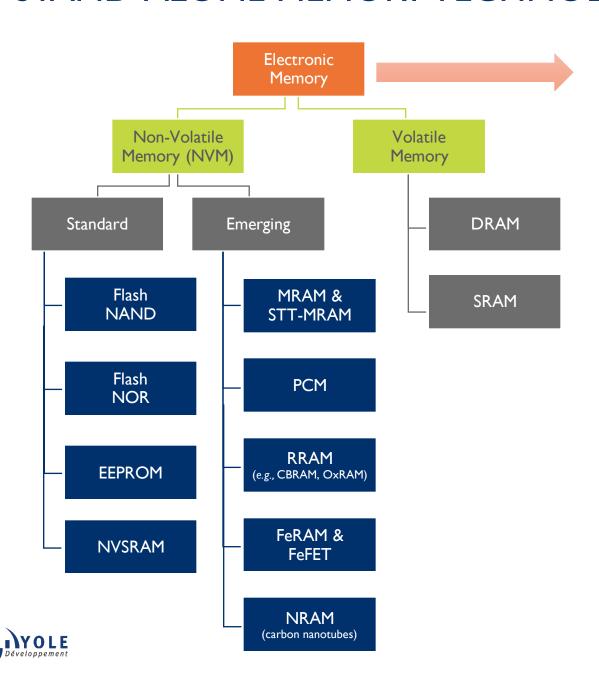

### **Volatile memory**

- Requires power supply to retain information.

- Examples: DRAM, SRAM.

#### Non-volatile memory

- Retains stored information even when unpowered. Mainstream NVM technologies are based on electrical charge storage.

- Examples: Flash NAND and NOR.

#### **Random Access Memory**

• Data can be read and written in the same amount of time irrespective of the physical location inside the memory.

### **Emerging Non-Volatile Memory**

- Based on principles different from retention of charges.

- Some products are already available in the market, and mass production has started. Certain newly emerging types of memory are still under development.

Note: Some "emerging" types of memory have actually already emerged and are now in mass production, whereas some others are still in R&D or in pre-production and could be more appropriately referred to as "prototypical". Here, the term "emerging" is used to indicate all recent technologies and to distinguish them from their mainstream counterparts.

## **DEFINITIONS – STAND-ALONE AND EMBEDDED MEMORY**

### **Stand-Alone Memory**

- Discrete chips dedicated to a memory/storage function

- Very concentrated market with five IDMs sharing up to 95% of the total business

## **Embedded Memory**

- Typically, two types of memory are referred to as embedded:

- On-chip memory integrated into CPUs, Microcontrollers (MCUs), Systems-on-Chips (SoC), mobile Application Processors (AP), etc.

- → Foundries are key manufacturing players

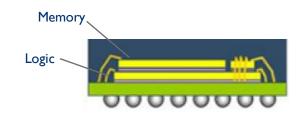

- In-package memory, where a memory die is enclosed in System in Package (SiP) together with other integrated circuit (IC) chips

- → Stand-alone IDMs and integrator companies are key players

### Embedded memory characteristics differ from those of stand-alone memory:

On-chip memory density is often much lower than its stand-alone counterpart since the fabrication process is more complex, and the footprint is typically larger.

Stand-alone DRAM chips

Embedded MRAM + SRAM Source: Intel

**SiP = Memory** (off the shelf from market) + Logic (customer's logic die)

## **DEFINITIONS – MEMORY DENSITY**

## Mind the Unit!

| Name of the Unit           | Abbreviation | Size                          |

|----------------------------|--------------|-------------------------------|

| bit                        | b            | "0 or I"                      |

| byte                       | В            | 8 bits                        |

| Kilobit                    | Kb           | 10³ bits                      |

| Kilobyte                   | КВ           | 10³ bytes (8 Kb)              |

| Megabit                    | Mb           | 10 <sup>6</sup> bits          |

| Megabyte                   | МВ           | 10 <sup>6</sup> bytes (8 Mb)  |

| Gigabit                    | Gb           | 10 <sup>9</sup> bits          |

| Gigabyte                   | GB           | 10 <sup>9</sup> bytes (8 Gb)  |

| Terabit                    | Tb           | 10 <sup>12</sup> bits         |

| Terabyte                   | ТВ           | 10 <sup>12</sup> bytes (8Tb)  |

| Petabit (million of Gb)    | Pb           | 10 <sup>15</sup> bits         |

| Petabyte (million of GB)   | РВ           | 10 <sup>15</sup> bytes (8 Pb) |

| Exabit (billion of Gb)     | Eb           | 10 <sup>18</sup> bits         |

| Exabyte (billion of GB)    | ЕВ           | 10 <sup>18</sup> bytes (8 Eb) |

| Zettabit (trillion of Gb)  | <b>Z</b> b   | 10 <sup>21</sup> bits         |

| Zettabyte (trillion of GB) | ZB           | 10 <sup>21</sup> bytes (8 Zb) |

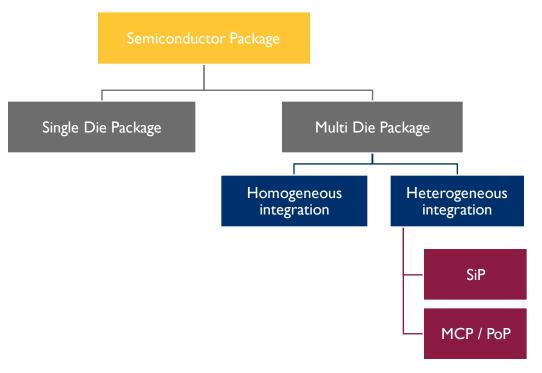

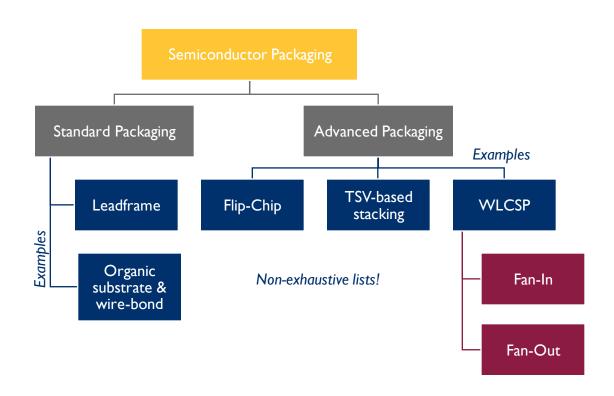

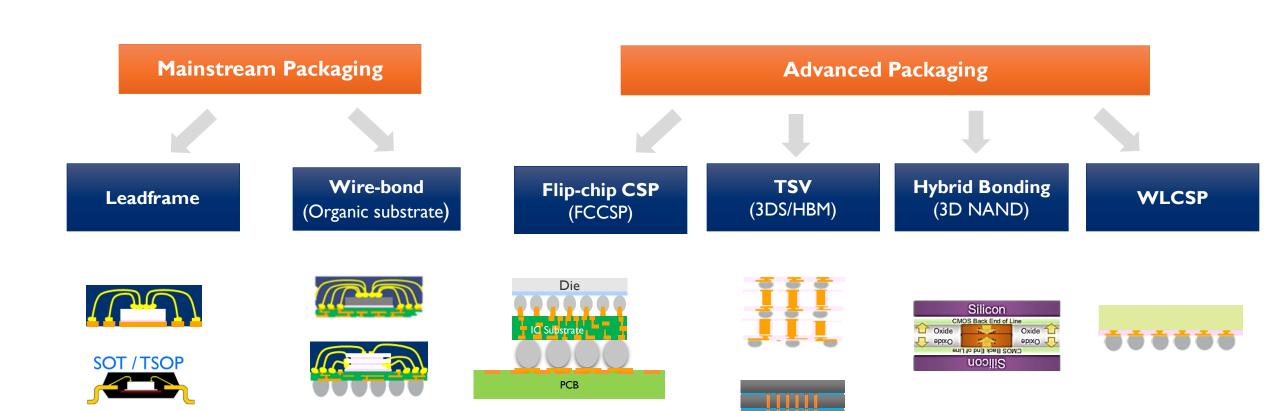

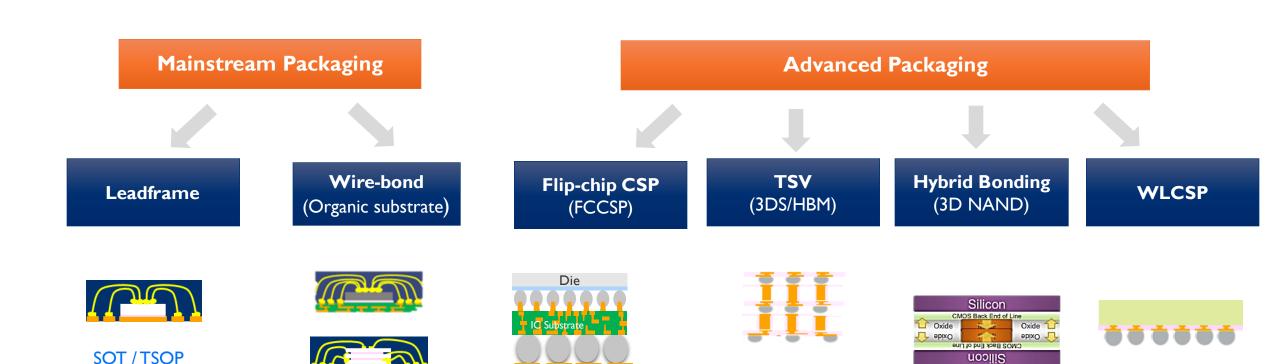

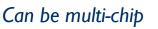

## DEFINITIONS – SEMICONDUCTOR PACKAGING

Packaging may be done by a separate vendor (OSAT) although IDMs and foundries are expanding their packaging activities.

- **Packaging** is an essential part of the manufacturing and design of integrated circuits (ICs). It affects power, performance and cost of the semiconductor chip.

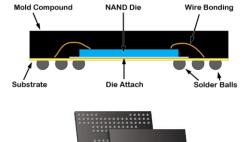

- A package is a container that holds one or more semiconductor dies and has 3 main functions: (1) it protects the die, (2) it connects electrically the chip to a board or to other chips, and (3) it dissipates heat.

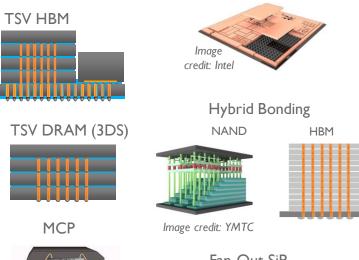

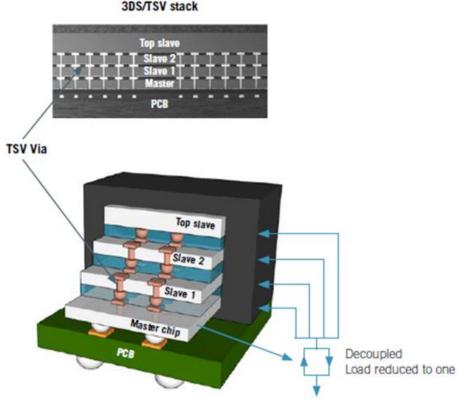

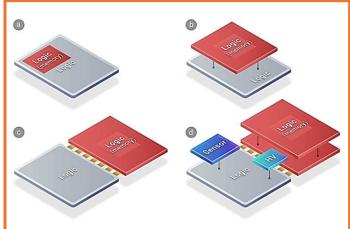

- Integration techniques are used to stack or combine multiple dies in a same package. If the dies correspond to different devices (e.g., memory, controller, CPU..) we refer to **heterogeneous integration**; otherwise, if the devices are the same (e.g., only memory) we refer to **homogeneous integration**.

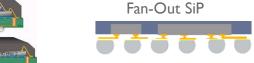

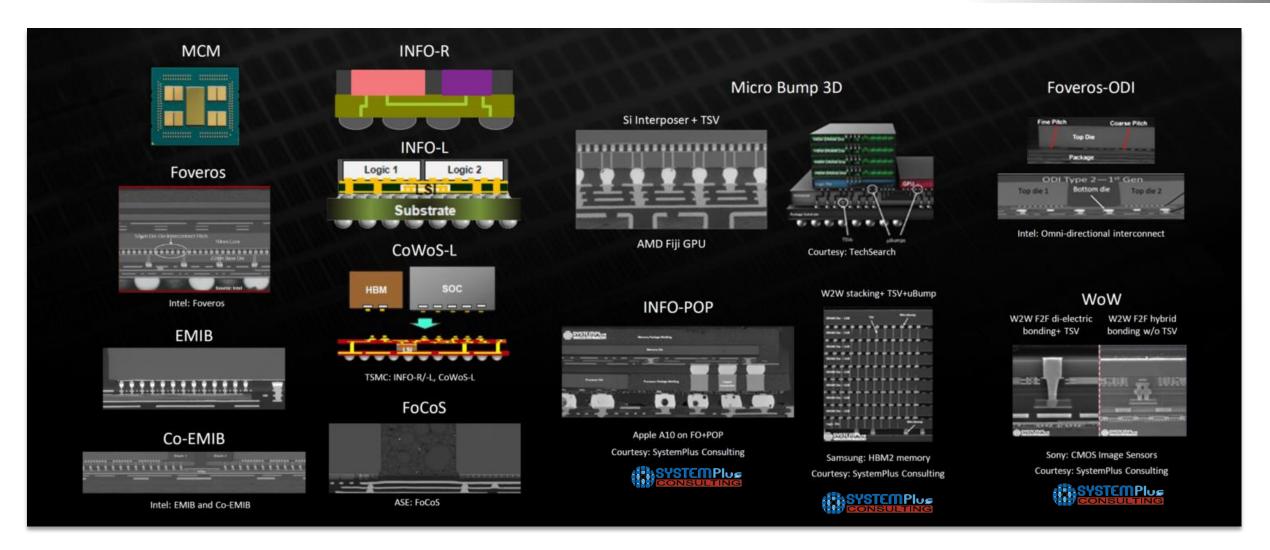

- Advanced packaging is a general grouping of a variety of distinct techniques, including flip-chip, 2.5D, 3D-IC, fan-out wafer-level packaging and system-in-package.

## **DEFINITIONS – PACKAGING GLOSSARY**

3DS: 3D Stacking InFO: Integrated Fan-Out

AP: Advanced Packaging LCC: Leadless Chip Carrier

**BGA:** Ball Grid Array Large Scale Integration

BOC: Board on Chip MCM: Multi Chip Module

COB: Chip on Board MCP: Multi-Chip Package

CoWoS: Chip on Wafer on Substrate NCF: Non-conductive film

CPGA: Ceramic Pin Grid Array NCP: Non-conductive paste

CSP: Chip Scale Package OSAT: Outsourced Semiconductor Assembly & Test

DIP: Dual In Line Package PCB: Printed Circuit Board

EMIB: Embedded Multi-die Interconnect Bridge PoP: Package-on-Package

eMMC: Embedded Multi Chip Package QFN: Quad Flat No leads

ePLP: Enhanced Panel Level Packaging Redistribution Layer

eUFS: Embedded Universal Flash Storage System-in-Package

SoC: System-on-Chip eWLB: Embedded Wafer Level Ball grid array

FBGA: Fine Pitch Ball Grid Array

SolC: System-on-Integrated-Chip

This Small Quality Bodges

TSOP: Thin Small Outline Package

FC-BGA: Flip-Chip Ball Grid Array

FC-CSP: Flip-Chip Scale Package TSV: Through-Silicon Via

FOCOS: Fan-Out Chip on Substrate

UBM: Under Bump Metallization

VALUE BOOK Series Package

Under Bump Metallization

OCoS: Fan-Out Chip on Substrate WB BGA: Wire-bond Ball Grid Array

FOPLP: Fan-Out Panel Level Packaging WB CSP: Wire-bond Chip Scale Package

FOWLP: Fan-Out Wafer Level Packaging WLCSP: Wafer Level Chip Scale Packaging

**HBM:** High Bandwidth Memory WoW: Wafer on Wafer

HTCC: High Temperature Co-Fired Ceramic ZIP: Zig-zag in Line Package

## **DEFINITIONS – PACKAGING FAMILY PLATFORMS**

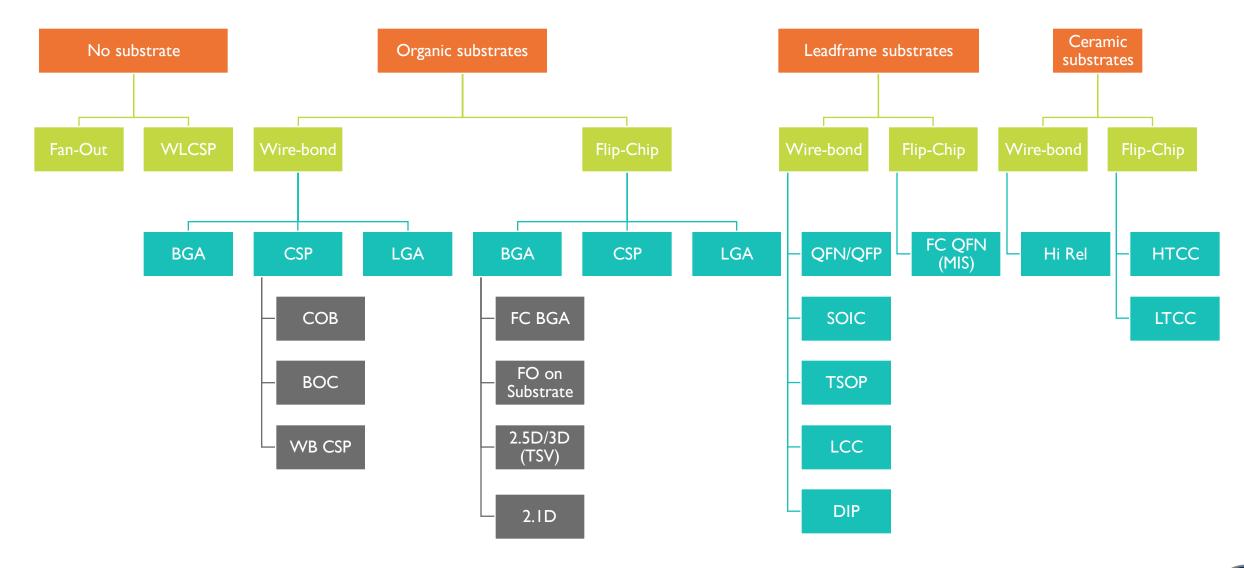

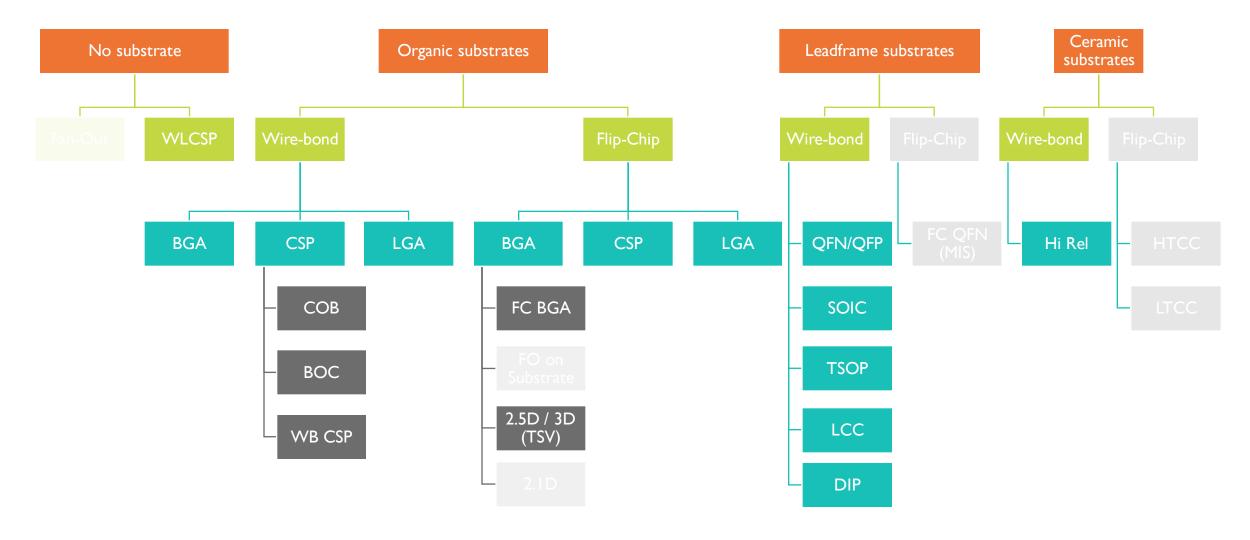

## DEFINITIONS – MEMORY PACKAGING FAMILY PLATFORMS

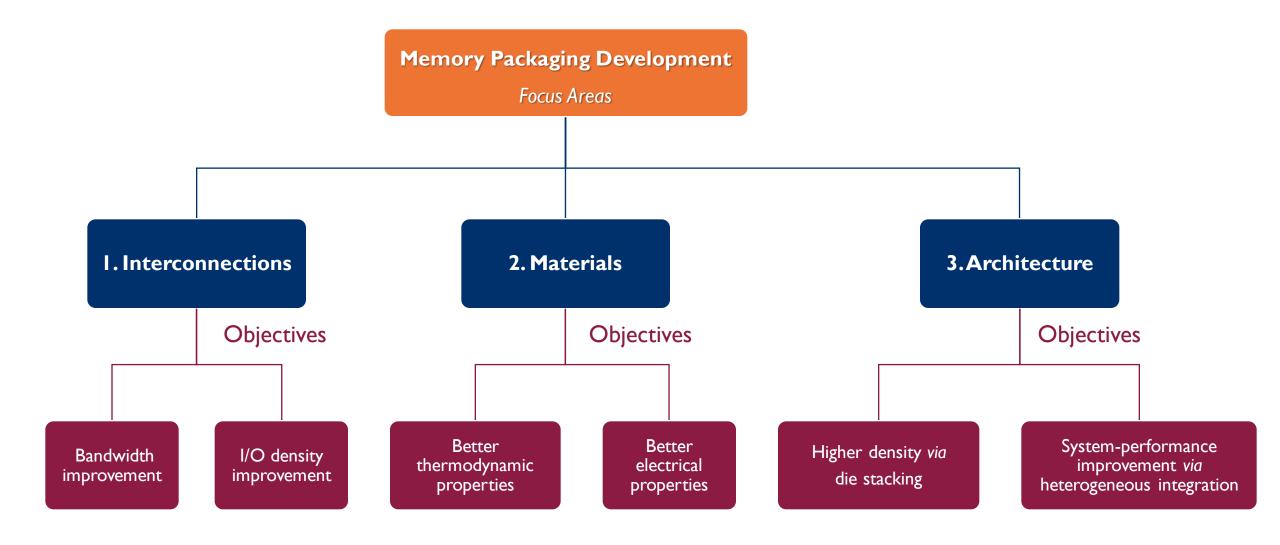

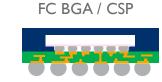

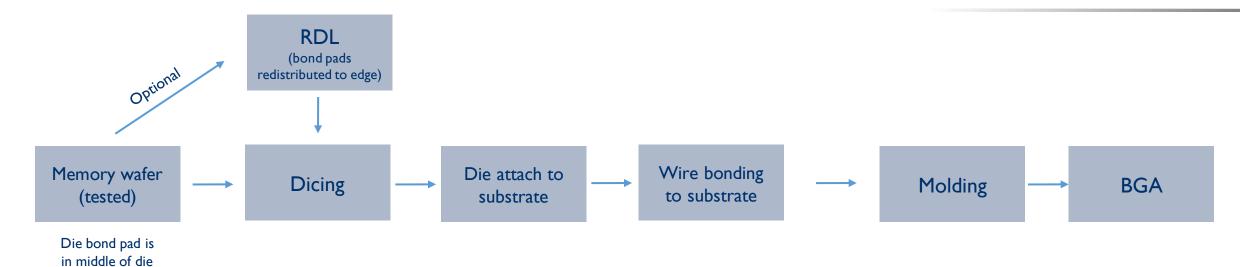

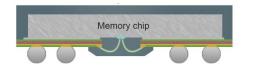

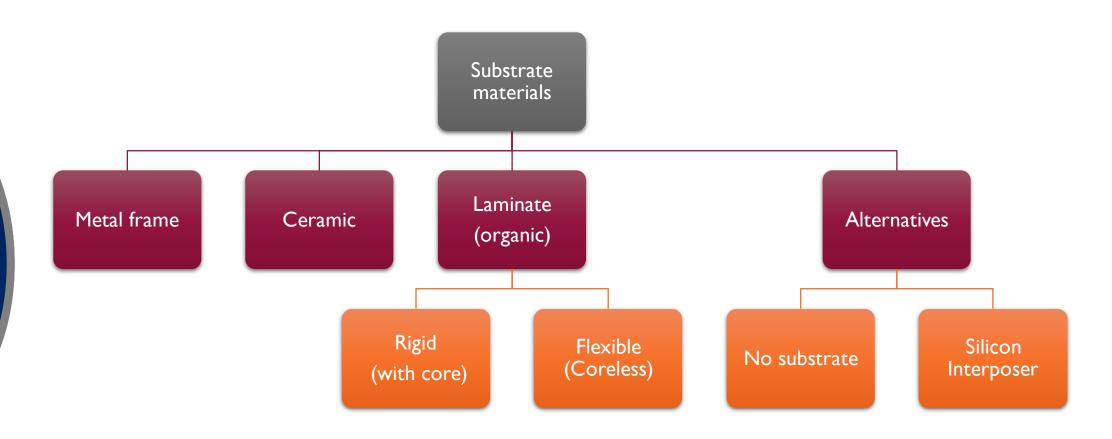

- The most common memory packages are: wire-bond BGA on organic substrates, flip-chip CSP (for DRAM), leadframe and WLCSP (mainly used for NOR).

- In this market study. the term wire-bond refers to packages with organic substrates (not leadframe).

- Packages based on ceramic substrates are currently utilized for niche high-reliability applications (e.g., defense, aerospace). Given their relatively small volume, they are not included in the market analysis in this report.

## TABLE OF CONTENTS

| Glossary and definitions                                      | 2   | <ul> <li>Mobile</li> </ul>                                       | 164 |

|---------------------------------------------------------------|-----|------------------------------------------------------------------|-----|

| • Table of contents                                           | 10  | <ul> <li>Personal computer (Client)</li> </ul>                   | 175 |

| • Report objectives                                           | Н   | <ul> <li>Consumer</li> </ul>                                     | 182 |

| • Scope of the report                                         | 12  | <ul> <li>Automotive</li> </ul>                                   | 189 |

| <ul> <li>Methodology &amp; definitions</li> </ul>             | 13  | Memory packaging forecast                                        | 199 |

| • About the authors                                           | 14  | O NAND packaging market forecast – in \$M, units, and wafers     | 210 |

| • Companies cited in this report                              | 15  | O DRAM packaging market forecast – in \$M, units, and wafers     | 218 |

| • Comparison with the 2017 report                             | 16  | Other stand-alone memory packaging forecast                      | 226 |

| • Who should be interested in this report                     | 17  | • Ecosystem                                                      | 236 |

| Yole Group related reports                                    | 18  | <ul> <li>Supply chain mapping</li> </ul>                         | 237 |

| Three-slide summary                                           | 20  | <ul> <li>Supply chain challenges – Focus on shortages</li> </ul> | 246 |

| • Executive summary                                           | 24  | <ul> <li>M&amp;A and partnerships</li> </ul>                     | 255 |

| <ul> <li>Context – Overview of the memory business</li> </ul> | 70  | China's memory business                                          | 260 |

| O Stand-alone memory technology and market                    | 77  | Advanced packaging for memory-logic integration                  | 282 |

| O Stand-alone memory market players                           | 90  | Hybrid bonding - Overview                                        | 301 |

| Overview of memory packaging                                  | 101 | Packaging materials - Overview                                   | 317 |

| <ul> <li>Memory packaging technology</li> </ul>               | 112 | General conclusions                                              | 327 |

| <ul> <li>Memory packaging players</li> </ul>                  | 138 | Noteworthy news                                                  | 331 |

| <ul> <li>Memory packaging trends by end markets</li> </ul>    | 154 | How to use our data?                                             | 337 |

| O Data center                                                 | 157 | Yole Développement presentation                                  | 338 |

## REPORT OBJECTIVES

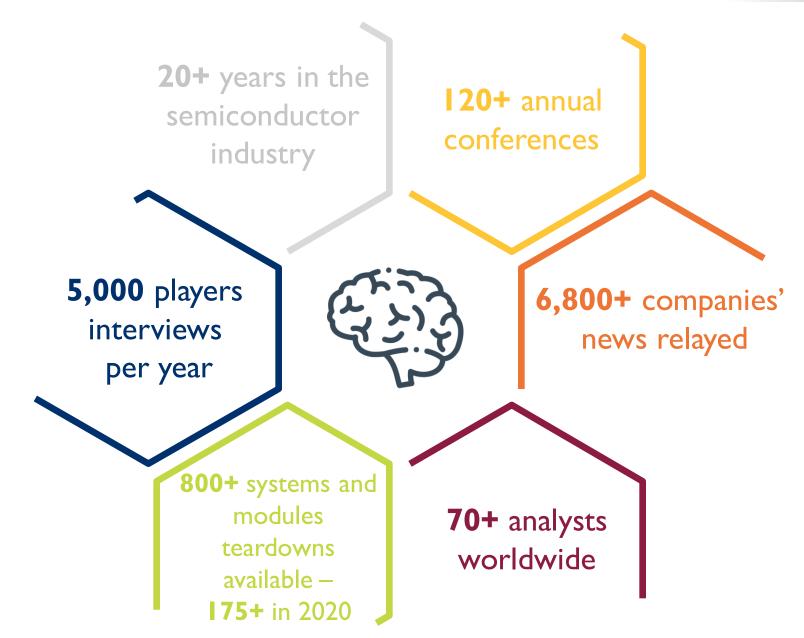

Yole has combined its multi-decade expertise in semiconductor packaging and memory technologies/markets to deliver this new edition of the "Memory Packaging" report, which has the following main objectives:

- Present an overview of the semiconductor memory market:

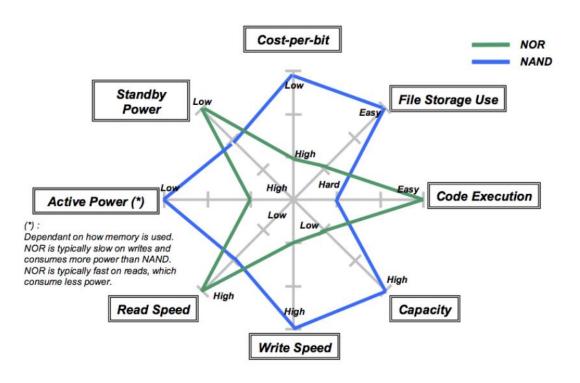

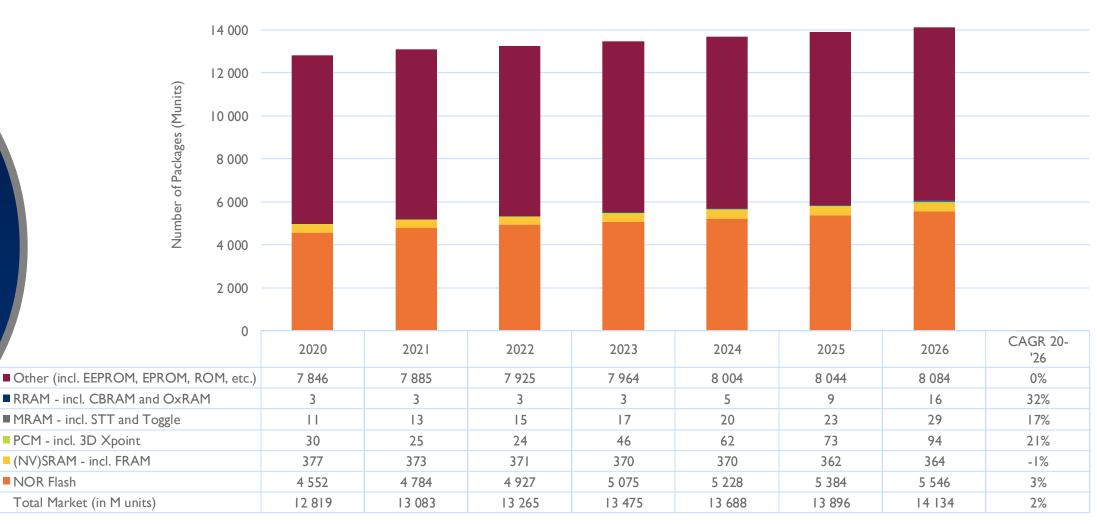

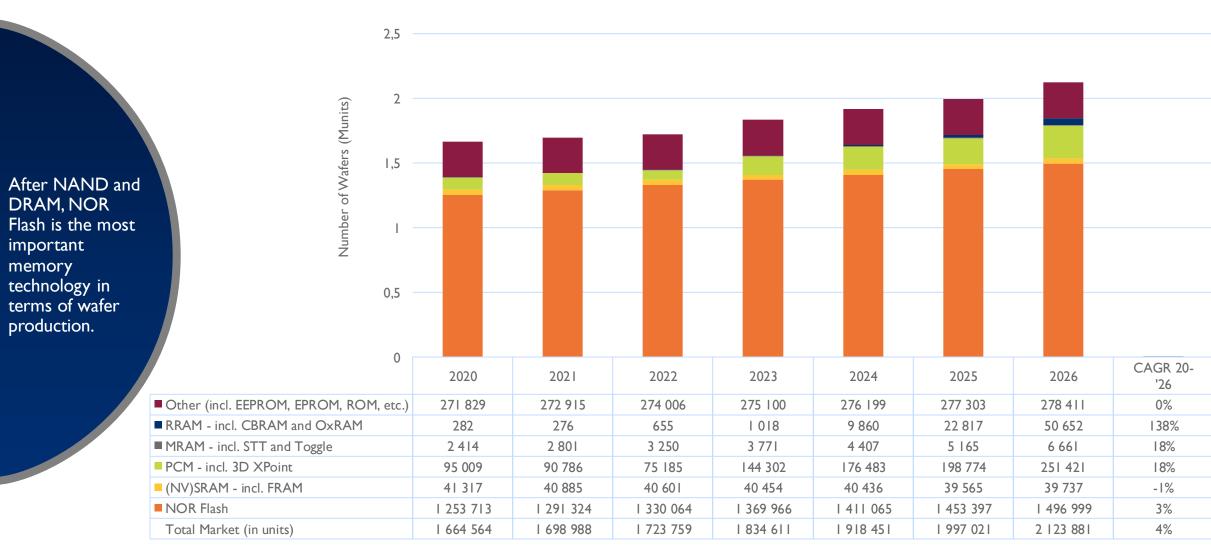

- Market trends for DRAM, NAND, NOR, (NV)SRAM, emerging NVM and other stand-alone memory technologies.

- Provide an understanding of memory packaging technologies and markets:

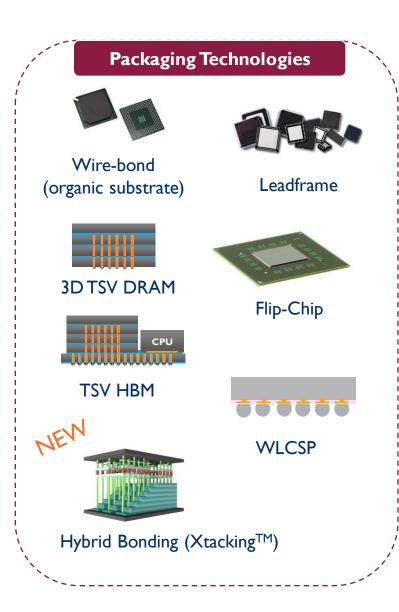

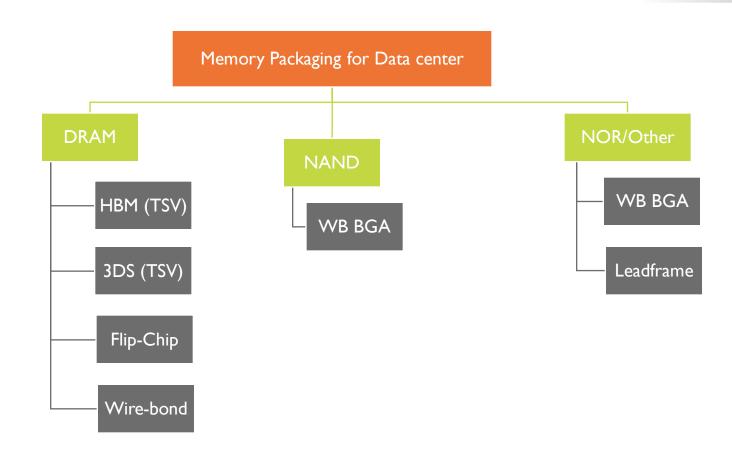

- Technical characteristics, manufacturing methods, advantages/limitations, development status for a variety of packaging approaches, among which leadframe, wire-bond, WLCSP, flip-chip, TSV-based stacking (HBM and 3DS) and hybrid bonding (YMTC's 3D NAND).

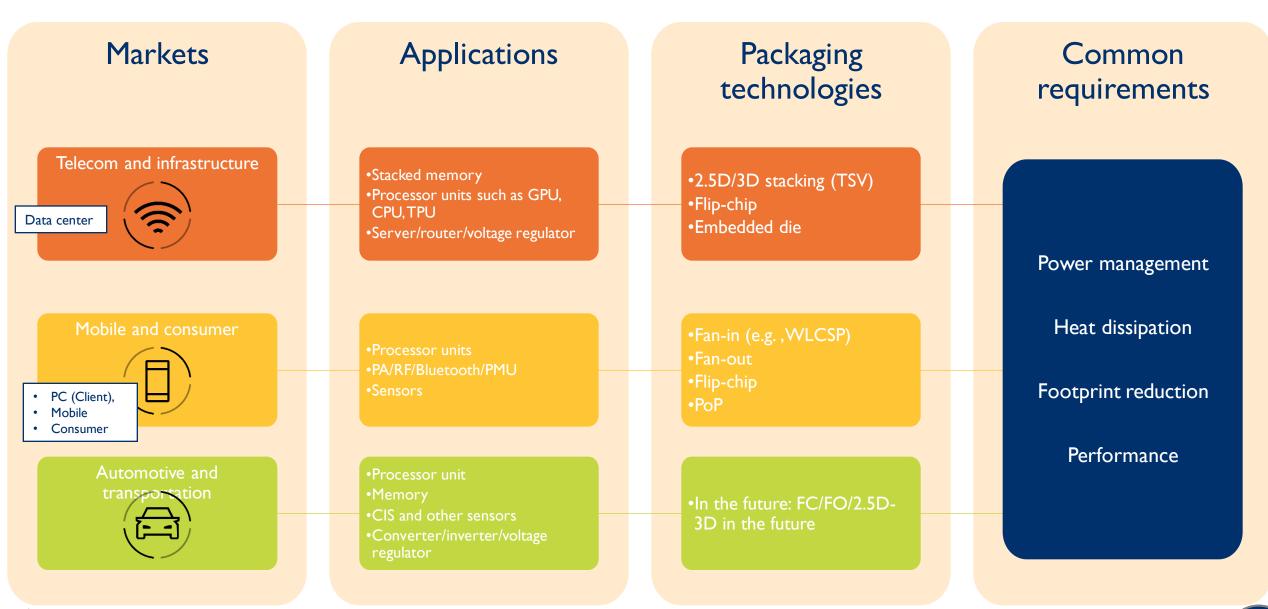

- Packaging trends for 5 different end-markets: data center, PC, mobile, consumer and automotive.

- Packaging trends for DRAM, NAND and other stand-alone technologies, including NOR Flash, MRAM, PCM, ReRAM, and more.

- Offer market forecasts for memory packaging:

- 2020-2026 market forecast: revenue (US\$), volume (number of packages) and wafer shipments with breakdown by type of package, type of memory technology, as well as end-market.

- Evolution of ASP by type of package, type of memory technology and end-market.

- Describe the memory packaging business:

- Market drivers, challenges, opportunities and technology requirements for 5 end-markets, roadmaps and players.

- Analysis of the memory packaging supply chain and players' dynamics with a focus on OSATs and memory IDMs.

- Detail and analyze the competitive landscape:

- Recent acquisitions and funding, latest company news, key players by technology and application.

## SCOPE OF THE REPORT — MARKET ANALYSIS WITH BREAKDOWN BY:

Your needs are out of scope of this report?

Contact us for a custom study:

Notes: (1) Multiple package-on-board / PCB in module format (e.g., DIMM) is not included in the market forecast. (2) Packaging revenues (substrate, assembly, stacking, TSV formation, bumping, etc.) are included in the market forecast but not testing.

## **METHODOLOGIES & DEFINITIONS**

### Yole's market forecast model is based on the matching of several sources:

Comparison with existing data Monitoring of corporate communication Using other market research data

Yole's analysis (consensus or not)

#### Comparison with prior Yole reports

Recursive improvement of dataset

Customer feedback

Preexisting information

#### Top-down approach

Aggregate of market forecasts

@ System level

#### **Market**

Volume (Munits) ASP (in \$)

Revenue (\$M)

#### Bottom-up approach

Ecosystem analysis

Aggregate of all players' revenues

@ System level

#### Primary data

- Reverse costing

- Patent analysis

- Annual reports

Secondary data

Press releases

Conferences

Direct interviews

#### Top-down approach

Aggregate of market forecasts

@ Semiconductor device level

#### **B**ottom-up approach

Ecosystem analysis

Aggregate of key players' revenues

@ Semiconductor device level

#### levice level

Information Aggregation

Industry organization reports

## Semiconductor foundry activity

Capacity investments and equipment needs

## **ABOUT THE AUTHORS**

## Biographies & contacts

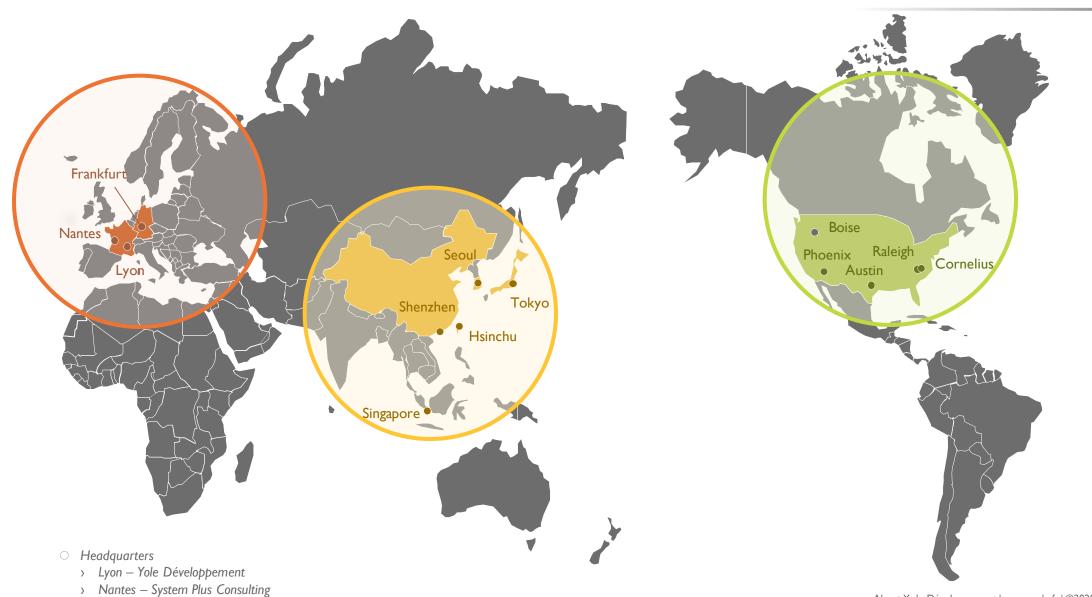

Simone is a Senior Technology & Market analyst at Yole Développement (Yole), working with the Semiconductor & Software division. He is a member of Yole's memory team and contributes on a day-to-day basis to the analysis of memory markets and technologies, their related materials, and fabrication processes. Previously, Simone carried out experimental research in the field of nanoscience and nanotechnology, focusing on emerging semiconducting materials and their device applications. He (co-) authored more than 15 papers in high-impact scientific journals and was awarded the prestigious Marie Curie Intra-European Fellowship. Simone obtained a Ph.D. in physics in 2015 from École Polytechnique Fédérale de Lausanne (Switzerland), where he developed novel flash memory cells based on heterostructures of 2D materials and high-κ dielectrics. Simone earned a double M.A. Sc. degree from Polytechnique de Montréal (Canada) and Politecnico di Milano (Italy), graduating cum laude.

Email: <a href="mailto:simone.bertolazzi@yole.fr">simone.bertolazzi@yole.fr</a>

#### **Thomas Illner**

As a Technology and Market Analyst Intern, Thomas Illner is a member of the Semiconductor, Memory & Computing at Yole Développement (Yole), part of Yole Group of Companies. Thomas collaborates with his team to perform strategic and technical analyses of memory packaging and materials related to the packaging. Prior to Yole, Thomas worked as an intern at Sartorius Stedim Biotech on the irradiation of biomedical films materials. Thomas holds a Physics and Chemical engineering degree specializing in polymer sciences at the European School of Chemistry of Strasbourg, France. He is preparing for an MBA as a complementary degree at the EM Strasbourg.

Email: thomas.illner@yole.fr

## COMPANIES CITED IN THIS REPORT

Amkor, Applied Materials, Ardentec, ASE, ASML, Avalanche, Canon, Carsem, Centon, Chipbond Technology, ChipMOS Technologies, CXMT, Dialog Semiconductor, Dosilicon, ESMT, Etron, Everspin, Formosa Advanced Technologies, Fujitsu, GigaDevice, GlobalFoundries, Greatek Elec, Hana Micron, H-Grace, Hitachi, HLMC, IBM, IDT, Inari Berhad, Infineon-Cypress, Intel, ISSI, Jiangsu Silicon Integrity Semiconductor Technology, JCET Group, JHICC, King Yuan Electronics, Kingston, Kioxia, KLA Tencor, Lam Research, Lapis, LB Semicon, Lingsen Precision Industries, Liteon, Longsys, Macronix, Marvell, Maxim, Maxio, MediaTek, Microchip, Micron, Montage, Nanya, NEC, Nepes Corporation, NetApp, NetList, Nuvoton-Panasonic, Orient Semiconductor Electronics, Phison, Powerchip, Powertech Technology, Rambus, Realtek, Renesas, Samsung, Seagate, SFA Semicon, Signetics, Sigurd Microelectronics, Silicon Motion, SJ Semi, SK Hynix, Smart Modular, SMIC, Sony, STMicroelectronics, Swissbit, TEL, Texas Instruments, Tianshui Huatian Microelectronics, Tong Hsing, Tongfu Microelectronics, Transcend, TSMC, UMC, Unisem Berhad, UTAC, Viking, Violin Memory, Walton Advanced Engineering, Weebit, Winbond, WLCSP, XMC, YMTC, and many more.

## COMPARISON WITH THE PREVIOUS EDITION OF THE REPORT (2017)

#### What we saw:

#### o Market:

What we saw, what we missed

• The total stand-alone memory wafer production was correctly predicted to rise to ~35M wafers (12") in 2020.

#### Players

• The rising Chinese memory IDMs are indeed fueling a strong business opportunity for OSATs in China. YMTC (Wuhan, NAND) and CXMT (Hefei, DRAM) do not have fully-developed assembly/testing divisions, so they need to outsource all their memory packaging to OSATs. This is a strong tailwind for JCET, HT-Tech and Tongfu.

#### Technologies

• The growing penetration of flip-chip packages for PC and server DRAM was anticipated correctly. As forecast, TSV-based stacking of NAND devices – introduced by Toshiba (Kioxia) in 2017 – had a negligible market penetration.

#### What we missed:

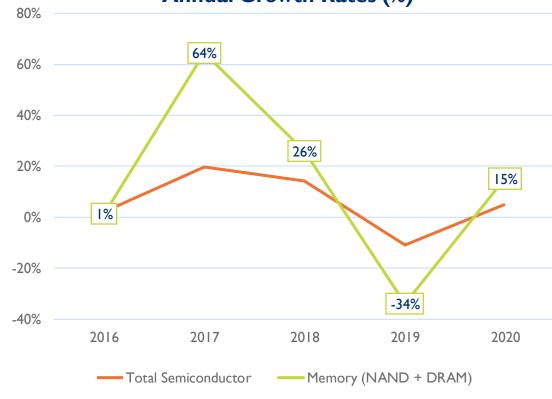

#### Market

- In the last 4 years, the memory market went through a rapid growth and subsequent decline. After hitting record high revenues in 2017 and 2018, the memory industry entered an oversupply condition. 2019 was a year of deep decline (revenues down 34%).

- Note: the overall memory packaging market reported in 2017 included the ASP contribution from testing. In the current edition, we disentangle the different contributions to provide only the packaging-related revenues.

#### Technologies

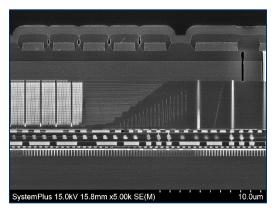

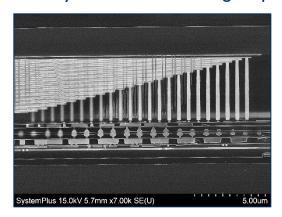

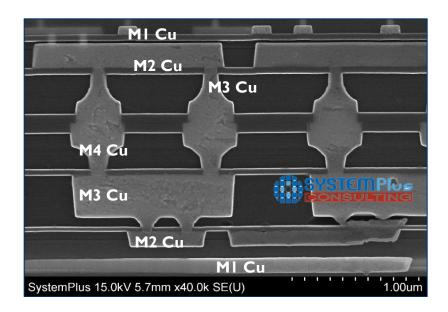

• In 2017, we underestimated the evolution of the average number of dies per package for NAND and DRAM, and consequently we overestimated the package volume. We have revised this data through the analysis of a large number of devices and systems in collaboration with our reverse-engineering partner System Plus Consulting.

## WHO SHOULD BE INTERESTED IN THIS REPORT?

### OSATs, IDMs and foundries:

- Understand stand-alone memory markets and technology trends.

- Understand the market potential of future technologies and products for new applicative markets

- Screen potential new suppliers to introduce new disruptive technologies

- Position your company in the future of memory technology

- Monitor and benchmark your competitors' advancements

## R&D players

- Understand the latest industrial developments in the field of memory packaging

- Gain an insight into the memory-packaging technology landscape and understand the trends/requirements by application

### Financial & strategic investors:

- See the potential of new memory devices and related packaging technologies

- Understand the memory business and learn about tailwinds and headwinds in the memory supply chain

- Know the key players involved in memory manufacturing, including assembly and packaging

### Equipment & material manufacturers:

- Understand the memory packaging business and the dynamics of OSATs and IDMs

- Discern the differentiated value of manufacturing tools and materials for memory packaging

- Understand technology requirements and manufacturing trends for memory packages

- Identify new business opportunities and prospects

## YOLE GROUP OF COMPANIES RELATED PRODUCTS – MEMORY

## Yole Développement

## DRAM & NAND Quarterly Market Monitors

# Status of the Memory Industry 2021

# Emerging Non-Volatile Memory 2021

# Equipment and Materials for 3D-NAND Manufacturing 2020

# Status of the Advanced Packaging Industry 2021

# Advanced Packaging Quarterly Market Monitor

## YOLE GROUP OF COMPANIES RELATED REPORTS

## System Plus Consulting

## Samsung LPDDR5 12GB Mobile Memory

# Micron LPDDR5 12GB Mobile Memory

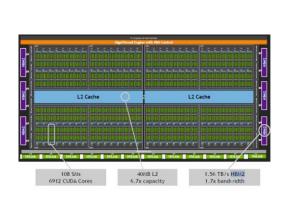

## NVIDIA A 100 Ampere GPU

## YMTC 3D NAND Flash Memory

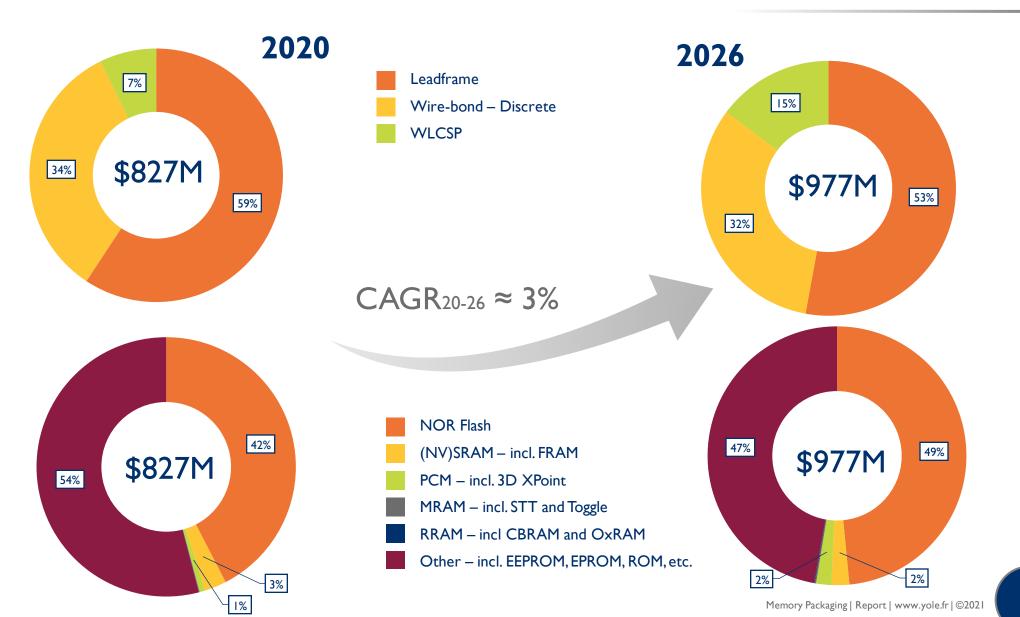

## MEMORY PACKAGING BUSINESS – OVERVIEW

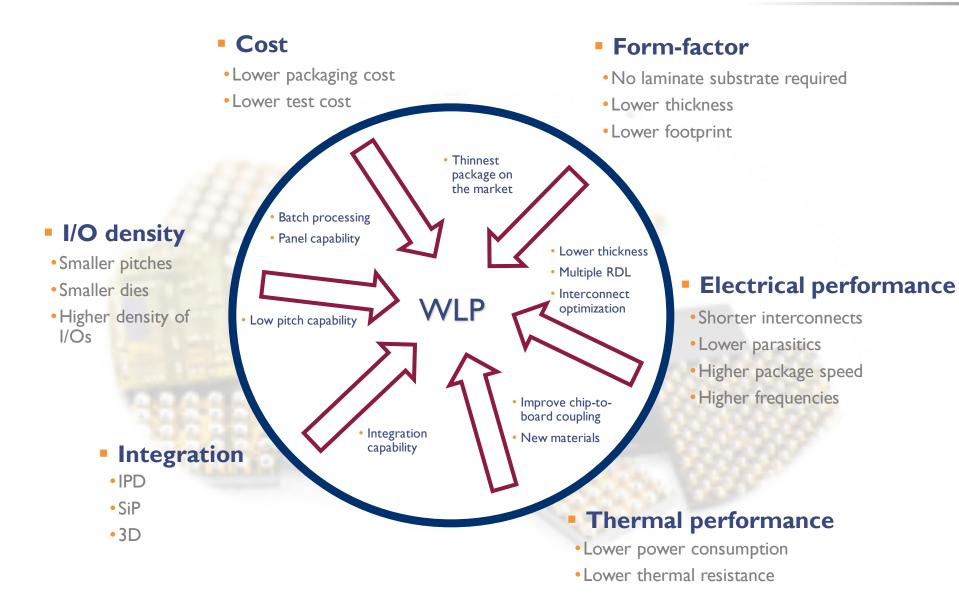

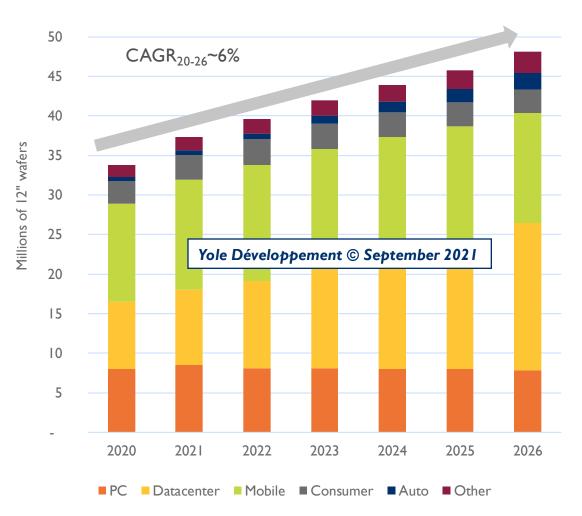

- Semiconductor memory is a critical market in modern data-centric societies, fueled by important megatrends, such as mobility, cloud computing, artificial intelligence (AI), and the internet of things (IoT). All these are propelling the so-called "data-generation explosion" and are shaping robust growth in memory demand for the next several years.

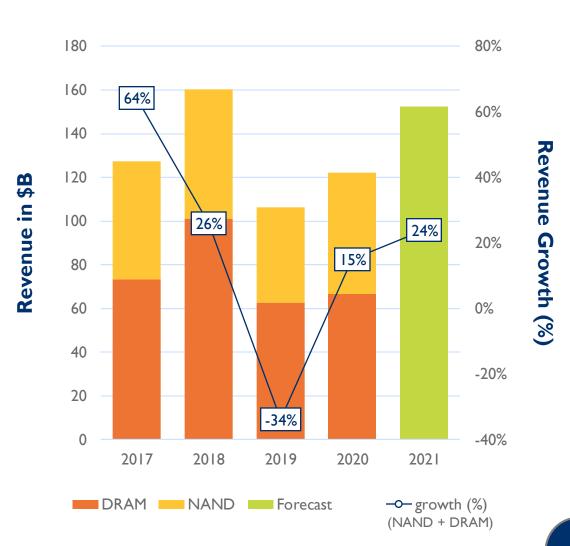

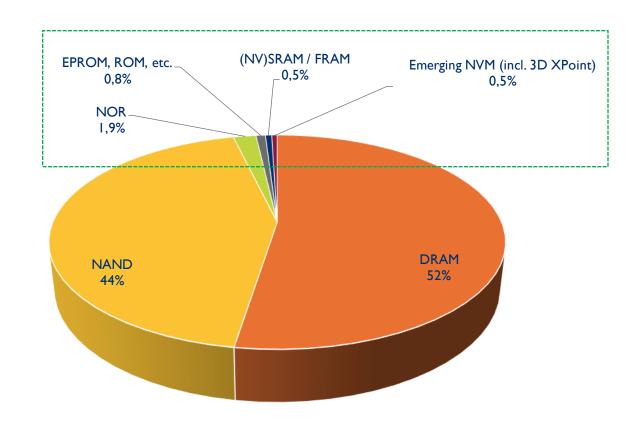

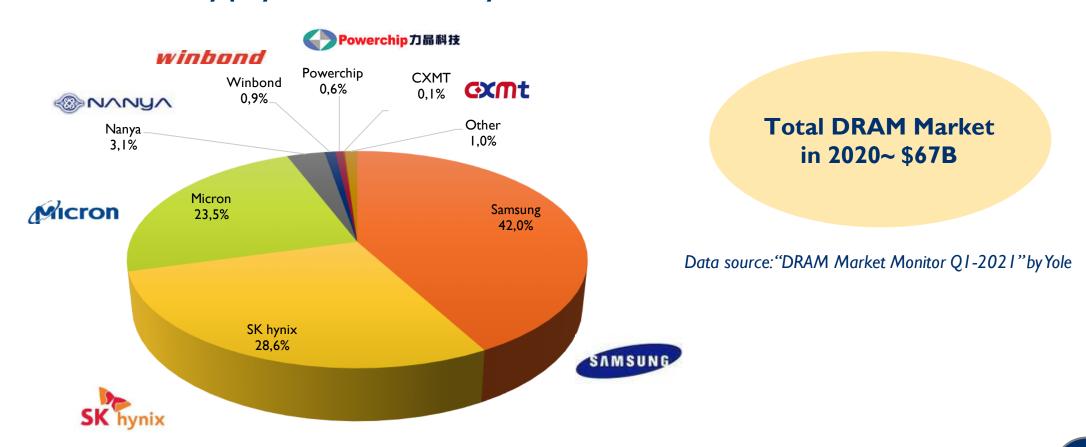

- NAND and DRAM are the workhorse memory technologies and account together for ~96% of the overall stand-alone memory market revenue. Combined DRAM and NAND revenues were ~\$122B in 2020, up 15% from 2019. In the long term, NAND and DRAM revenues are expected to grow to \$93B (NAND) and \$155B (DRAM) in 2026 with CAGR<sub>20-26</sub> of ~9% and ~15%, respectively.

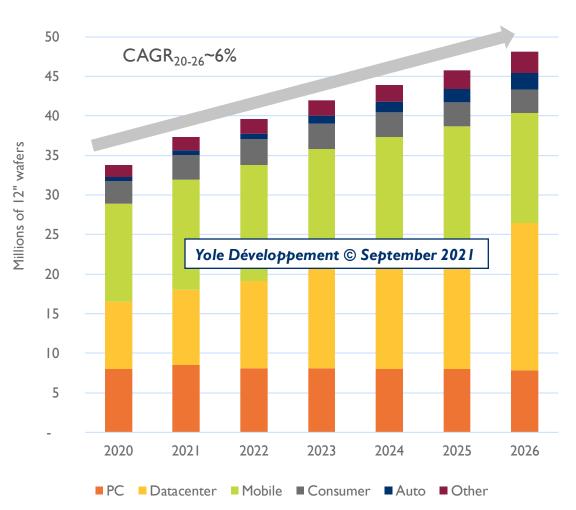

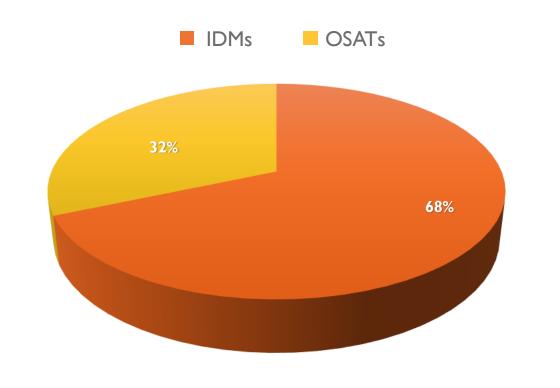

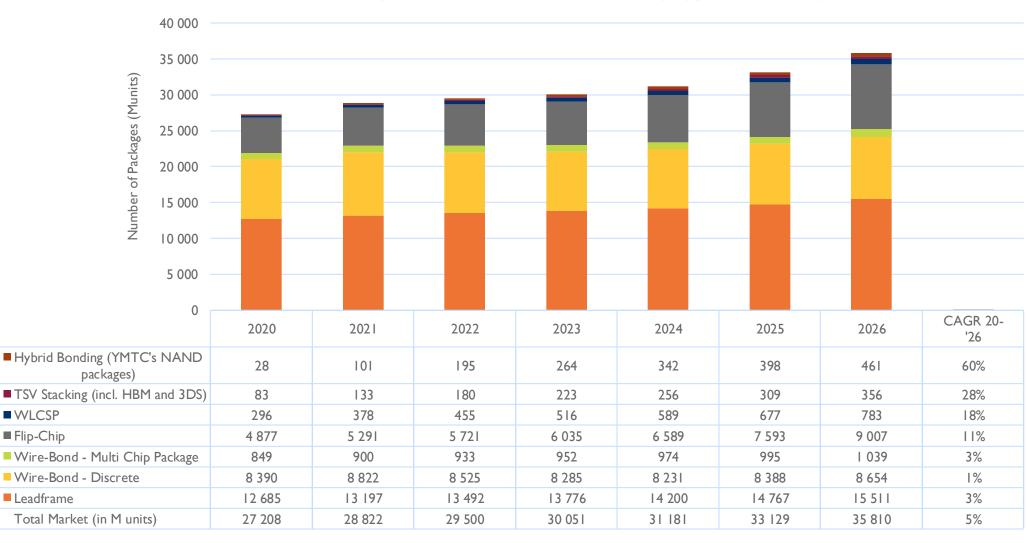

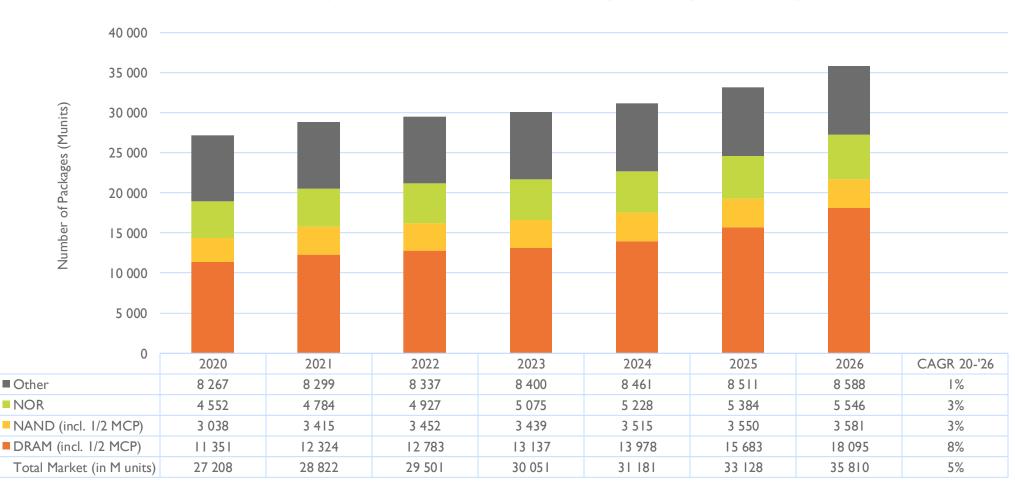

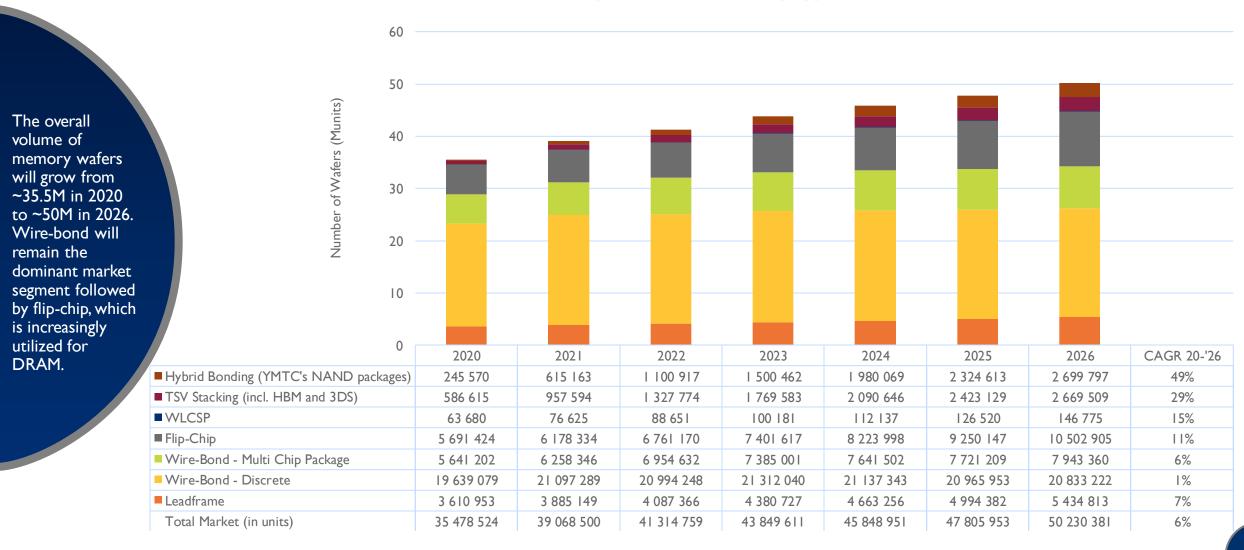

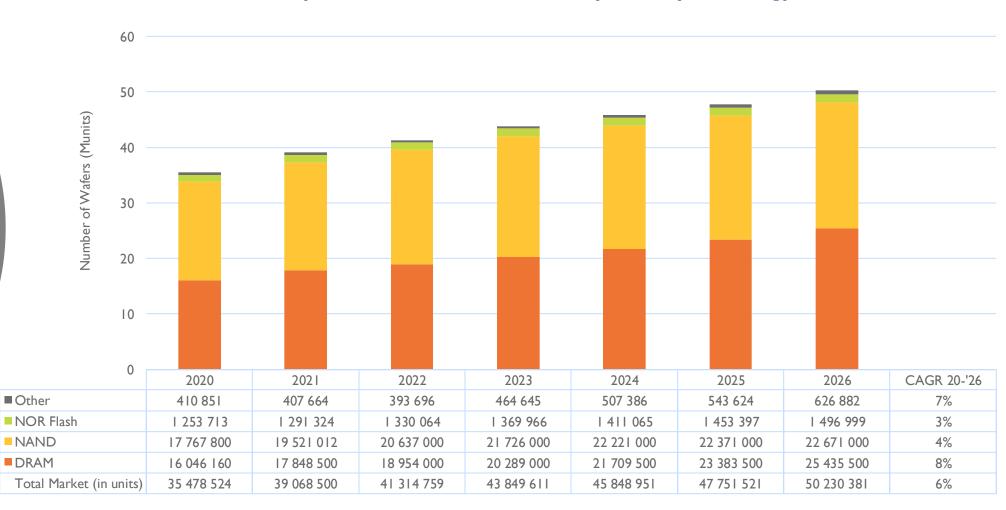

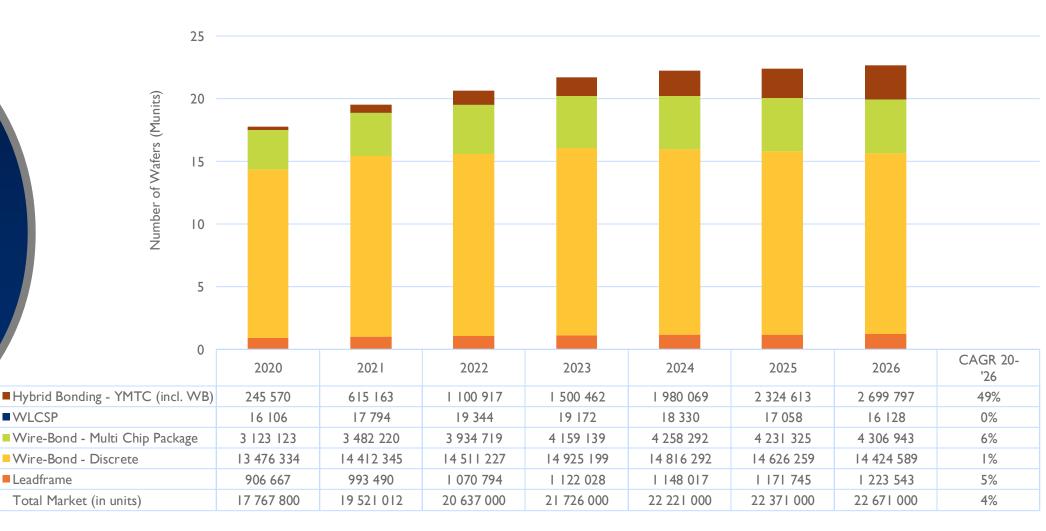

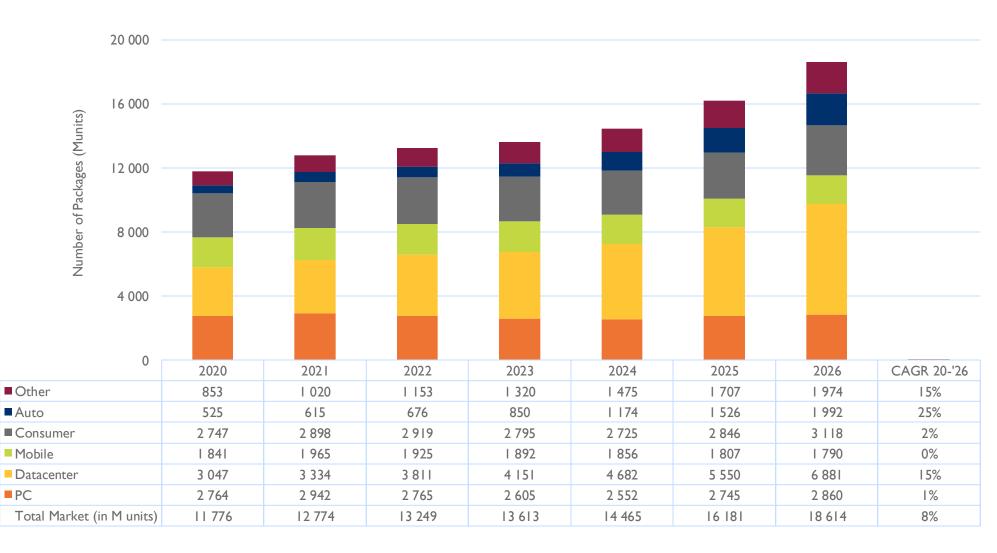

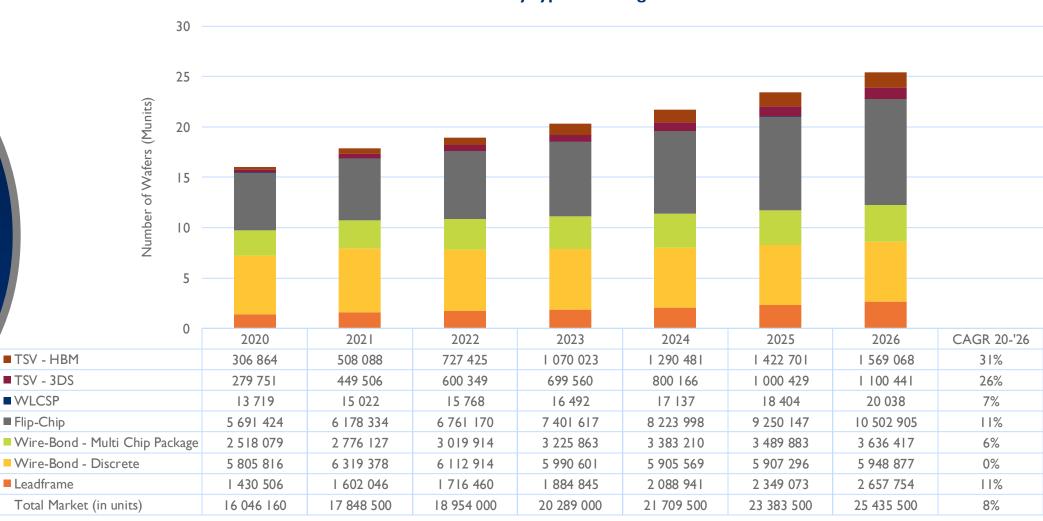

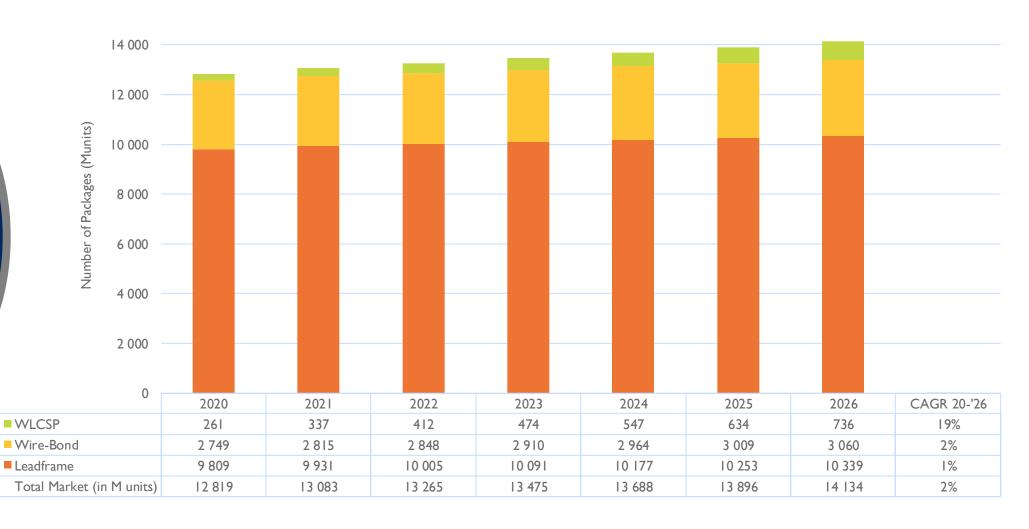

- The memory packaging market follows the same trends that rule the stand-alone memory market and thus will benefit from the robust long-term growth of memory demand, as well as from the ongoing fab capacity expansion. We forecast that the overall volume of memory wafers will grow from ~35.5M in 2020 to ~50M in 2026 with a CAGR<sub>20-26</sub>~6%, while the volume of memory packages will rise with a CAGR<sub>20-26</sub> of ~5% in the same years.

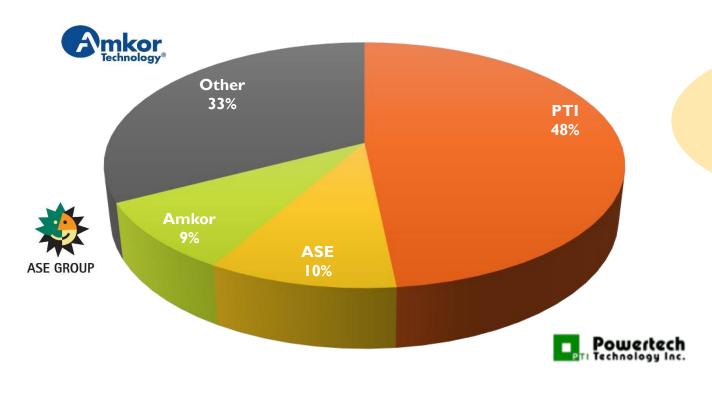

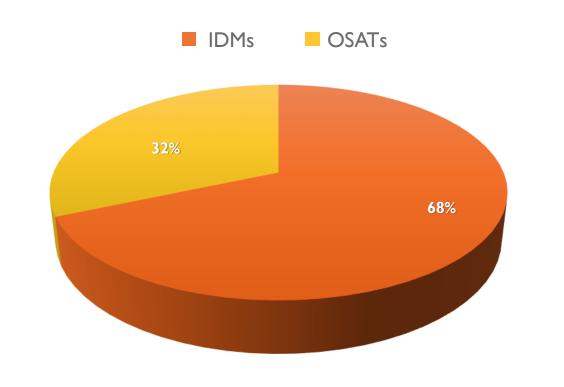

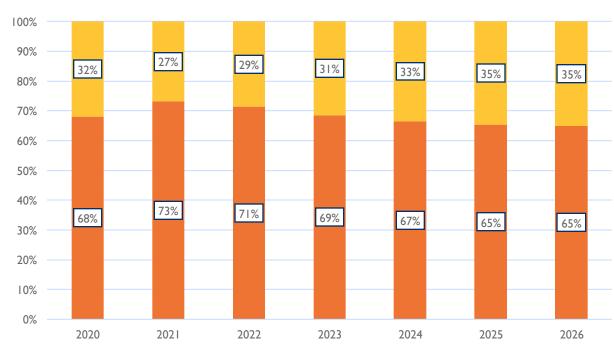

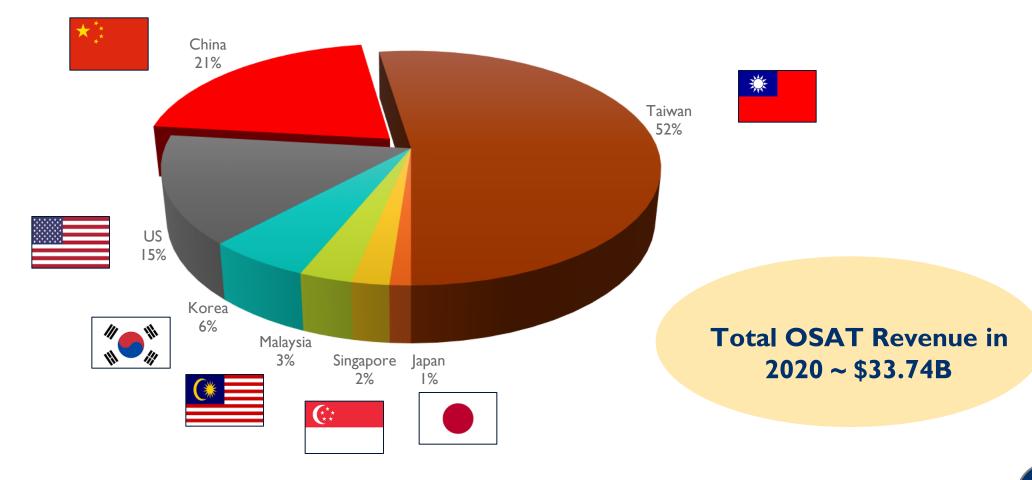

- However, unlike the stand-alone memory market that is characterized by high price volatility, the memory packaging market is more stable since most of the business is carried out internally by memory IDMs. We estimate that approximately 68% of the memory packaging revenue in 2020 was generated by IDMs and the remaining 32% by OSATs.

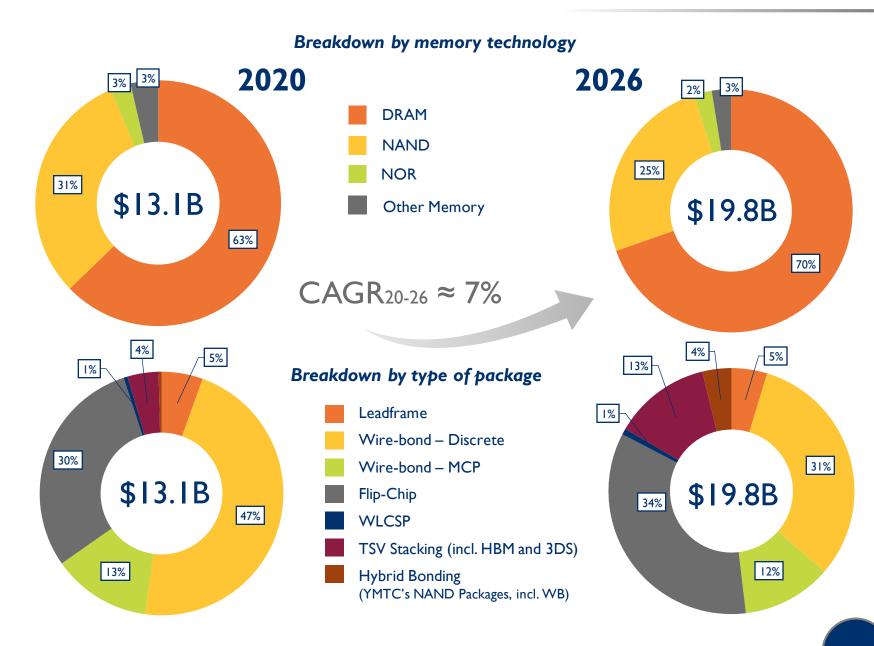

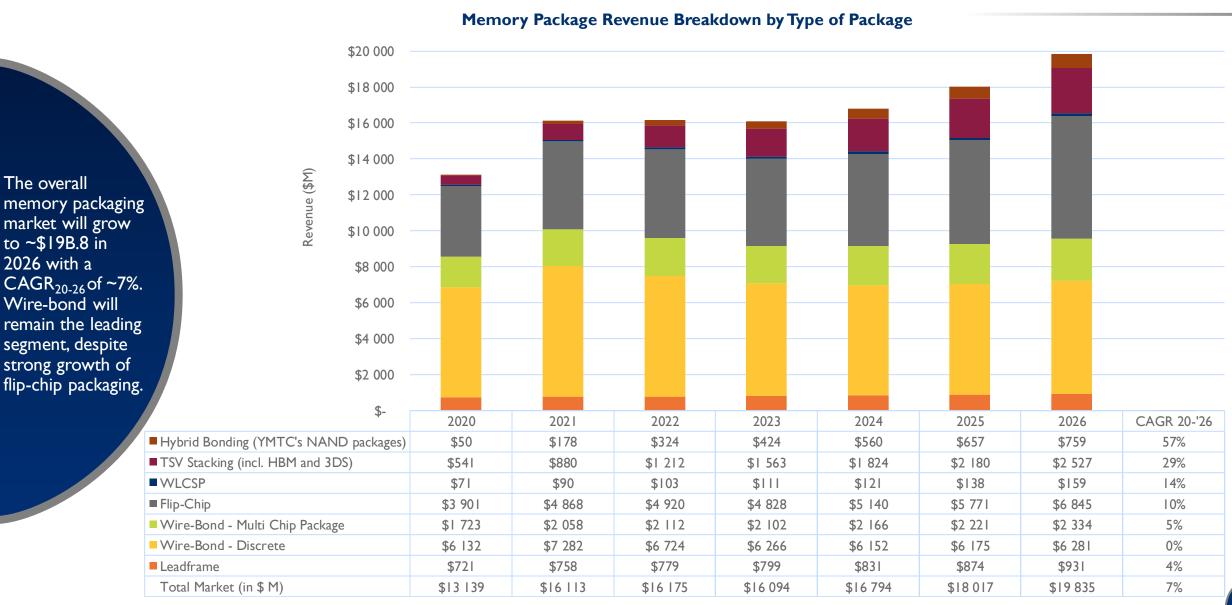

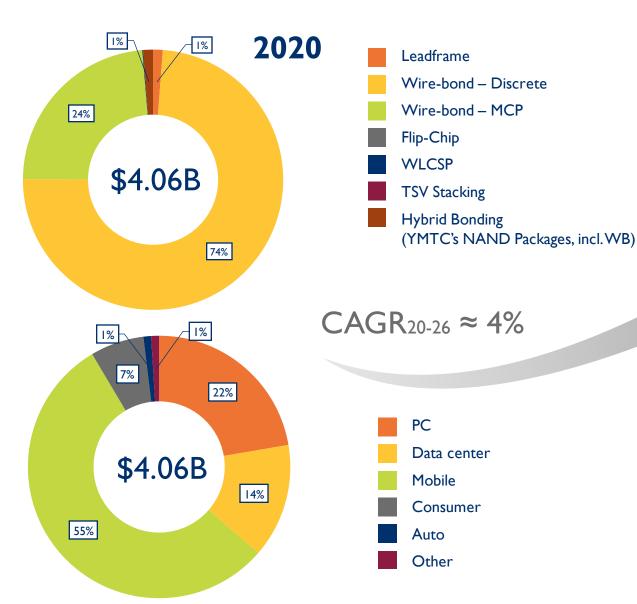

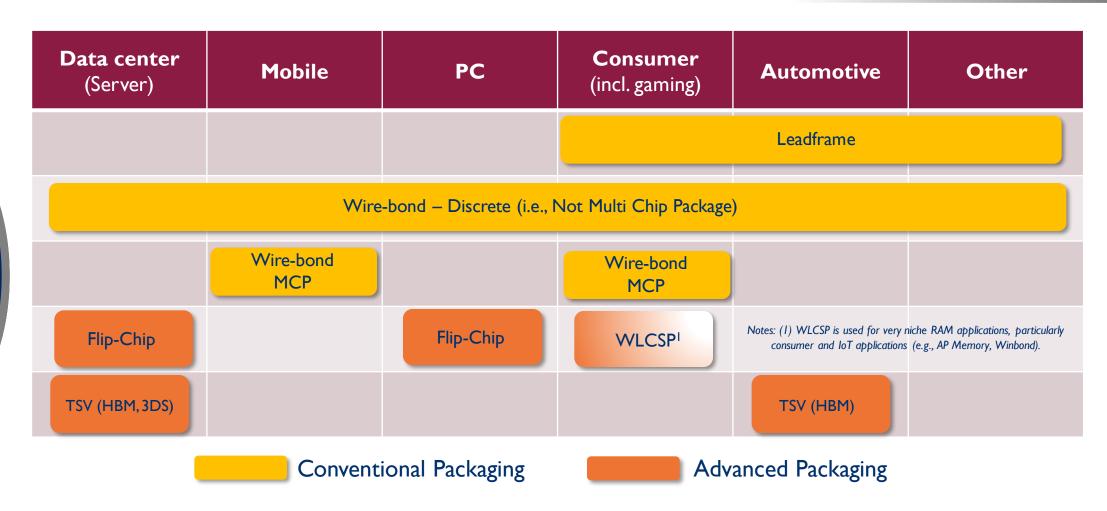

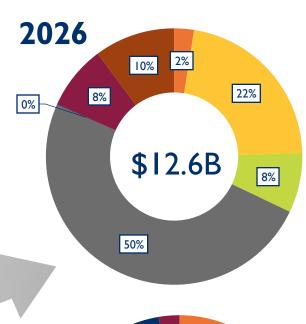

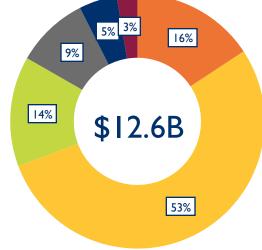

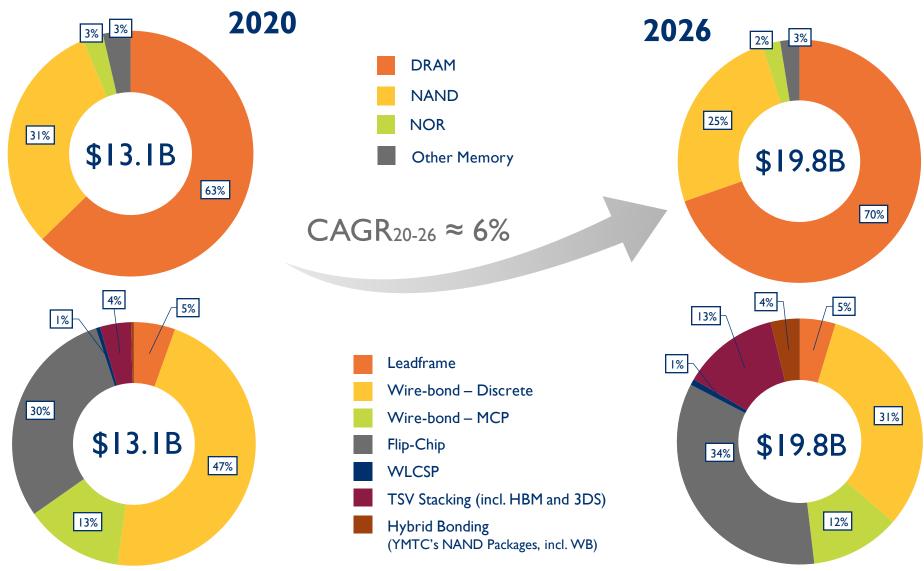

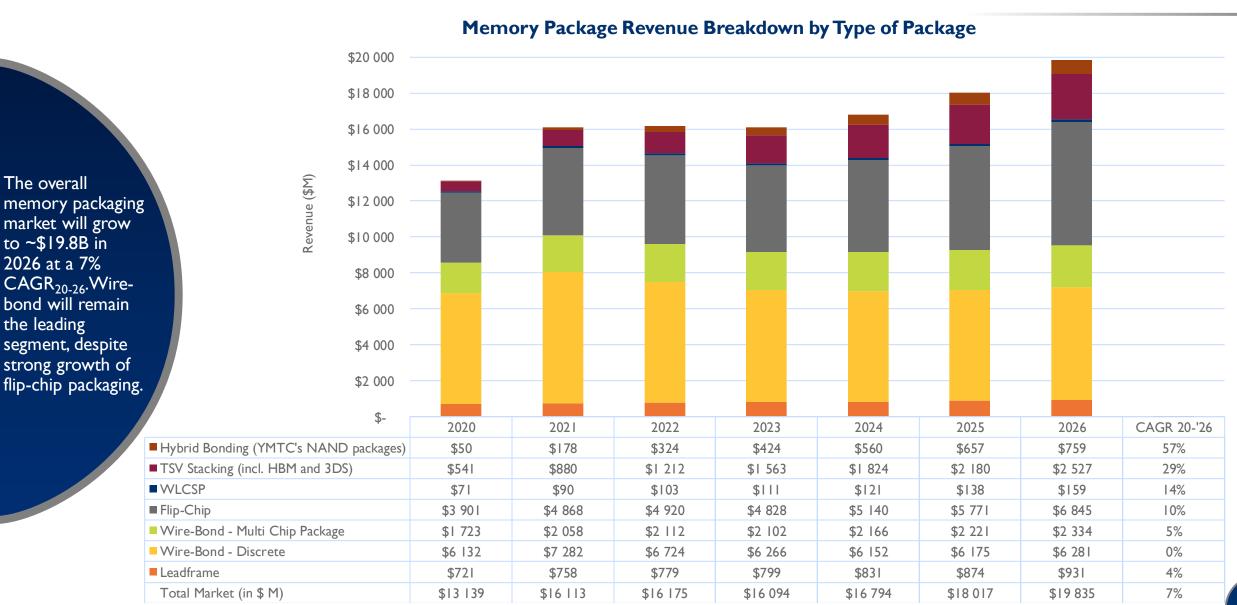

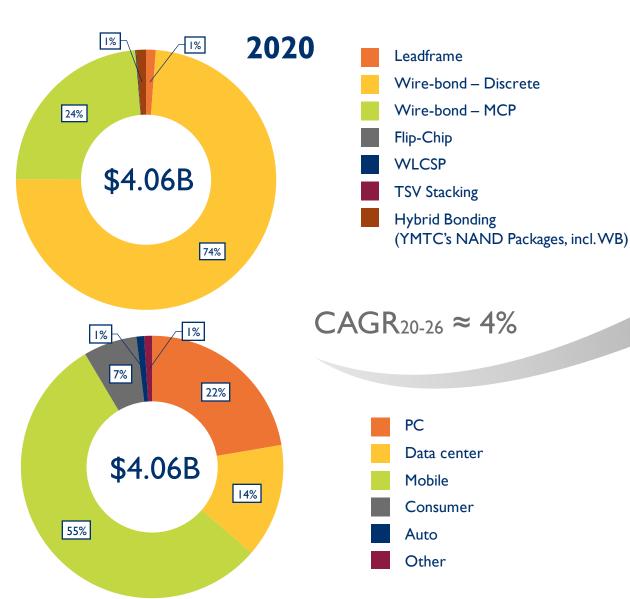

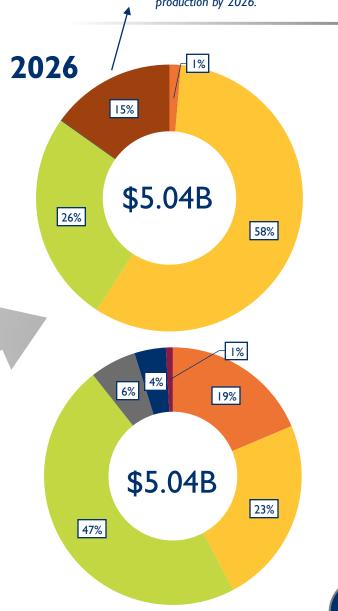

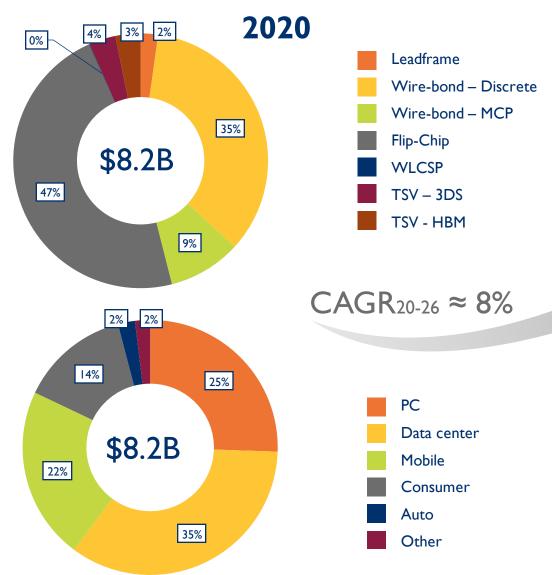

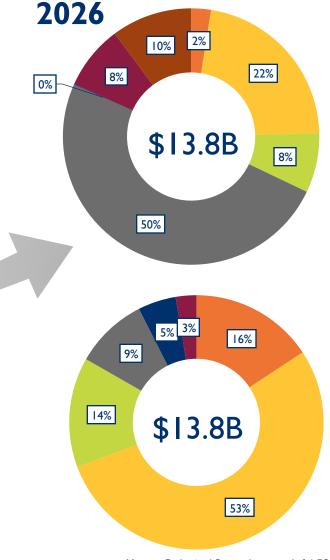

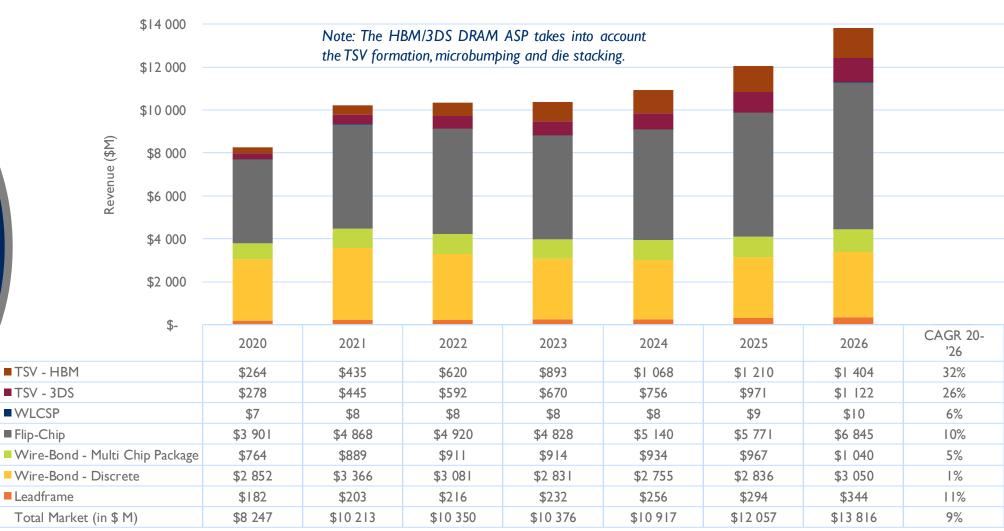

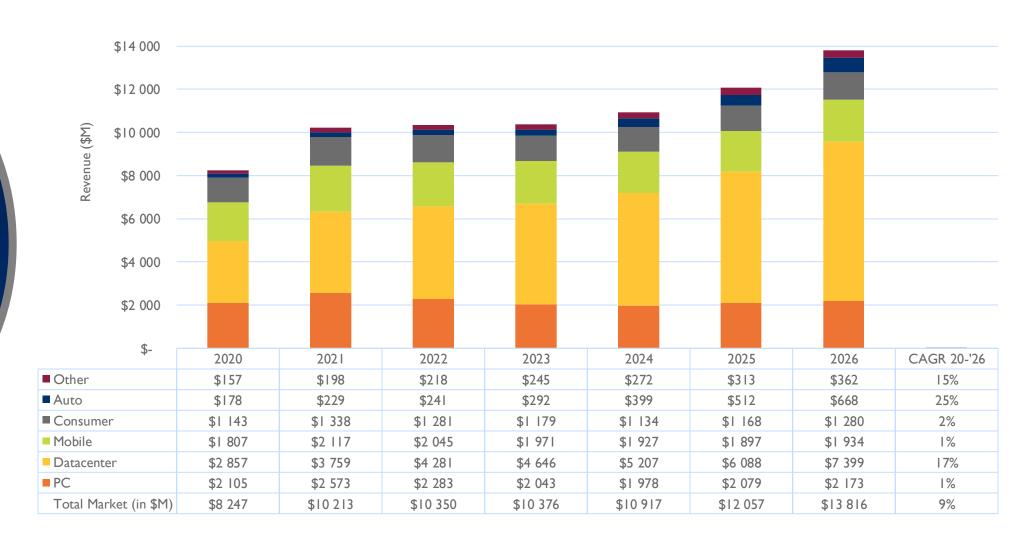

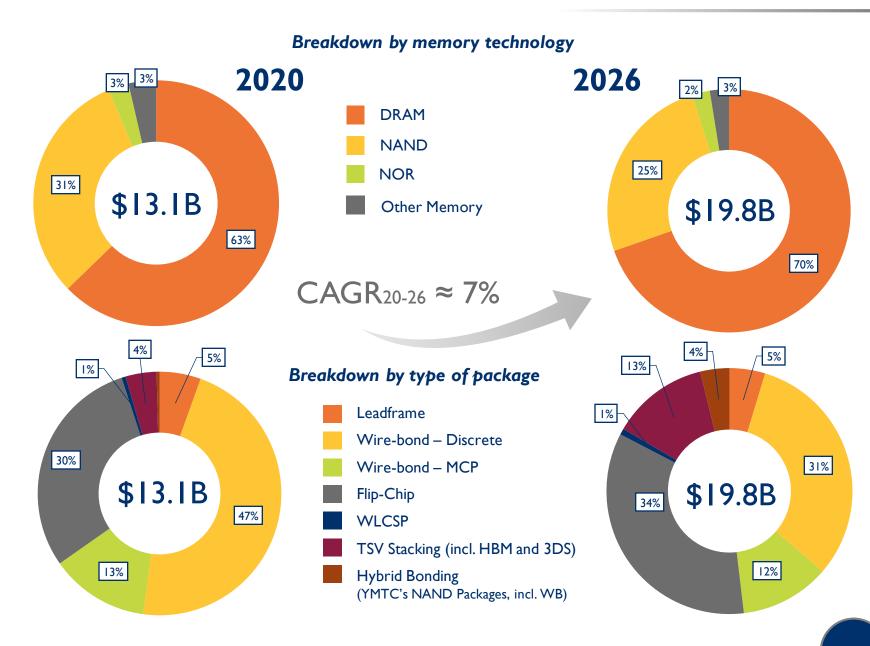

- The overall memory packaging market\* is worth  $\sim$ \$13.1B in 2020 which corresponds to  $\sim$ 10.3% of the stand-alone memory market and will grow to  $\sim$ \$19.8B in 2026 (CAGR<sub>20-26</sub> $\sim$ 7%). DRAM is the leading memory technology in 2020 with a 63% share, while wire-bond is the dominant packaging approach, widely used for mobile memory and storage applications.

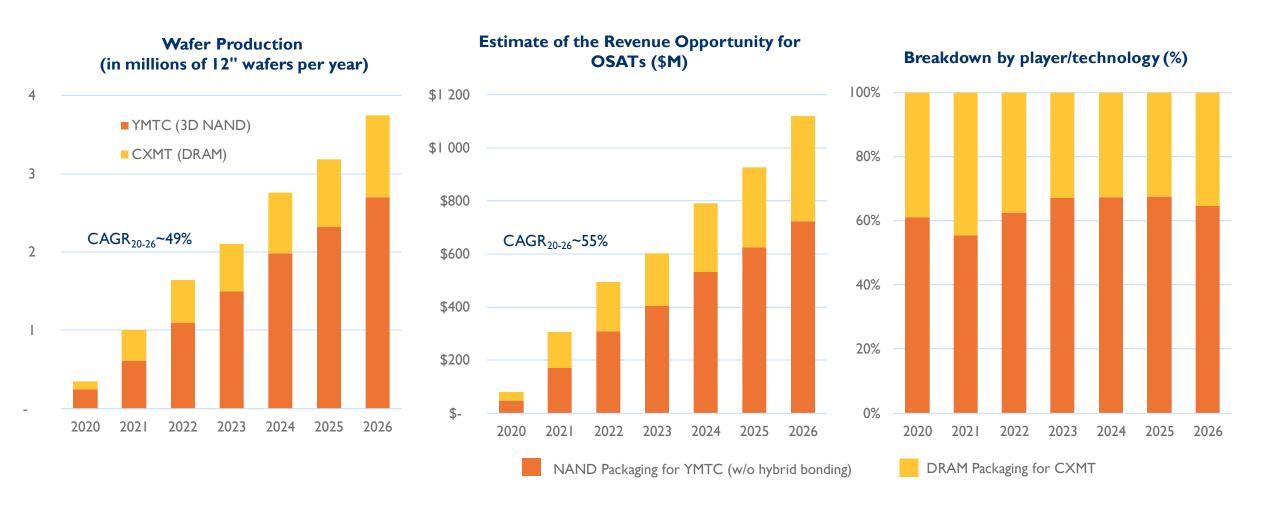

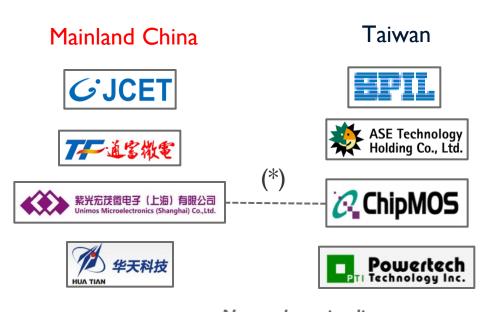

- Memory packaging in China is a key business opportunity for OSATs: The two rising memory players in China YMTC (NAND) and CXMT (DRAM) do not have experience in assembly/packaging and must outsource all their packaging to OSATs. We estimate that the OSATs' business opportunity related to the two Chinese memory IDMs can grow from <\$100M in 2020 to  $\sim$ \$1.1B in 2026 (CAGR<sub>20-26</sub>  $\sim$ 55%).

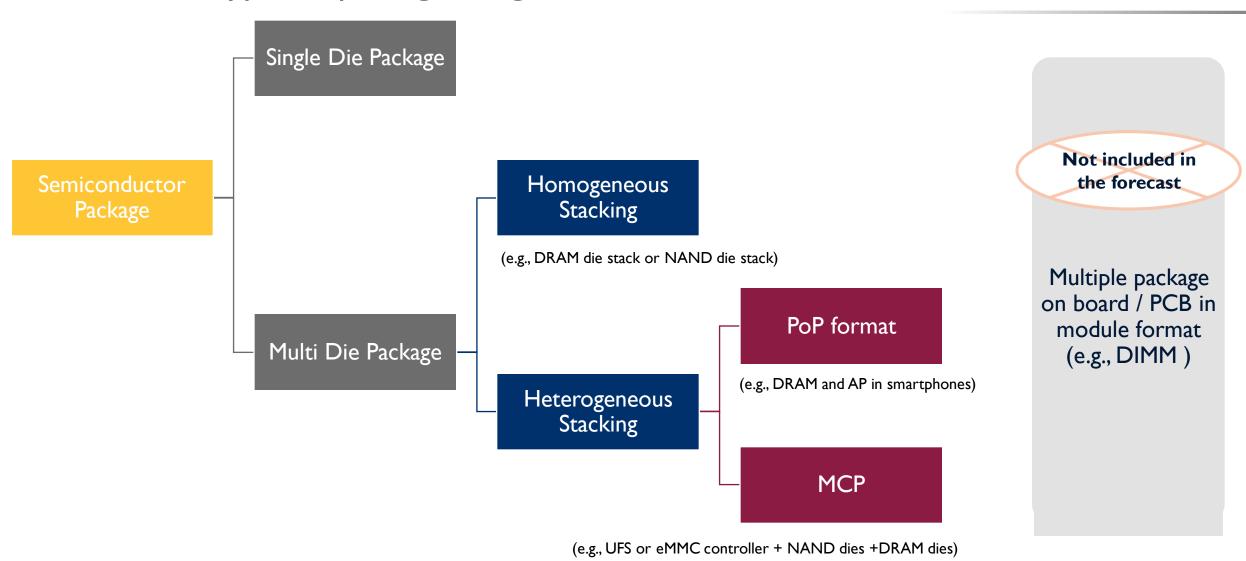

## MEMORY PACKAGING TECHNOLOGY - OVERVIEW

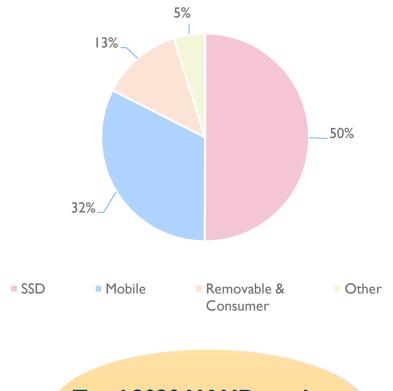

- Wire-bond is the most common packaging technology for NAND (~98% of NAND packaging revenues) and mobile DRAM (i.e., LPDDR); it will remain the dominant type of package followed by flip-chip, which is continuing its expansion in the DRAM business.

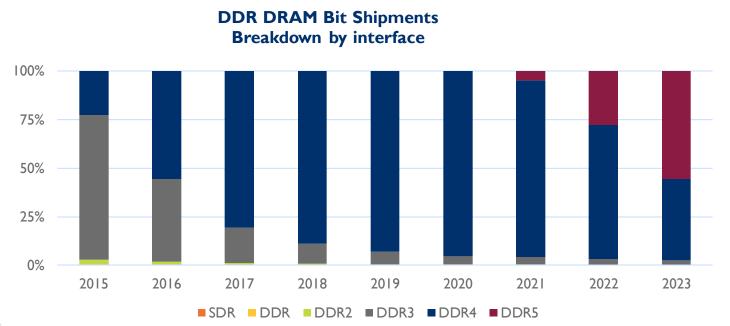

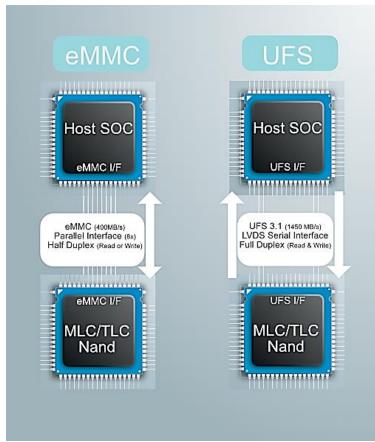

- In the last five years, **PC** and server **DRAM** packaging has been progressively migrating from wire-bond to flip-chip. Samsung and SK hynix have converted most of their DRAM packaging lines into flip-chip; Micron did not initiate the conversion process as early as its Korean competitors but has also been readying its own flip-chip packaging lines and will attempt to reduce its dependence on OSATs (e.g., PTI, ChipMOS) for flip-chip packaging. Note: The adoption of flip-chip packaging with short interconnects will be essential to fully exploit the potential of DDR5 and subsequent DRAM generations.

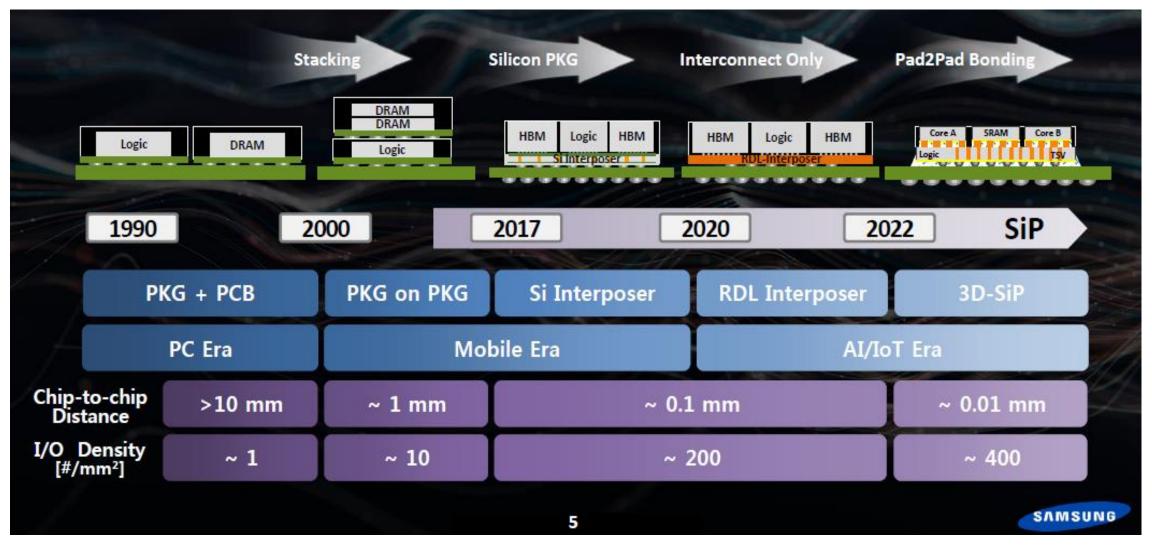

- With the ongoing slowdown of Moore's Law and the rise of new advanced packaging techniques, back-end processing has gained increasing importance, and several semiconductor companies are now leveraging it rather than the front-end to improve the performance, the compactness, and the number of functionalities of their IC products. Heterogeneous integration techniques and chiplet architectures enabled by novel stacking/bonding solutions have become essential to increase the performance of computing systems via a tight integration of logic and memory building blocks.

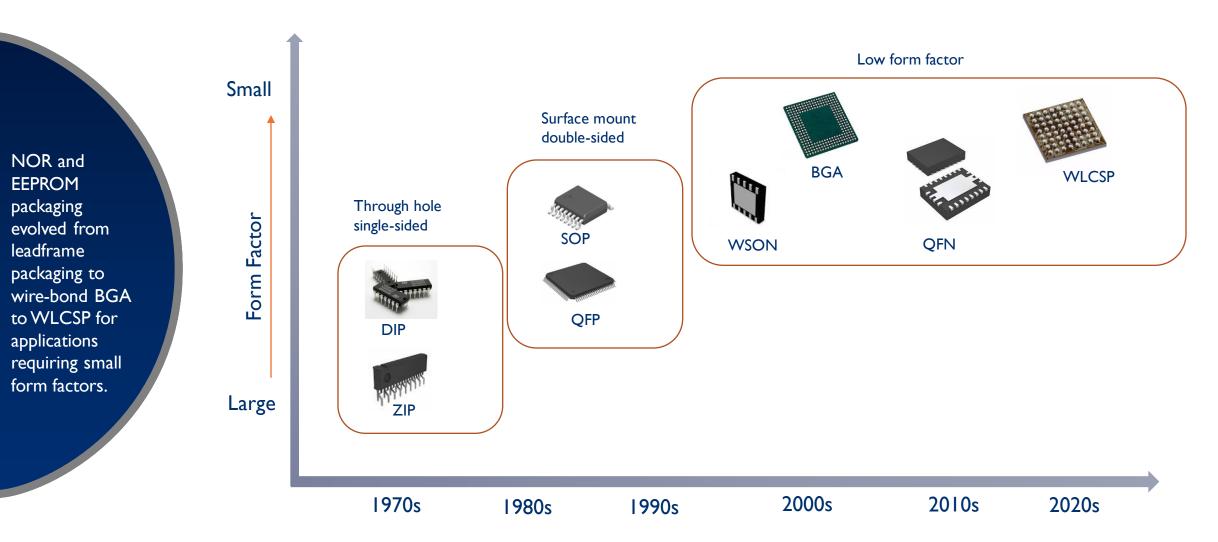

- WLCSP a form of advanced packaging is being increasingly adopted for consumer/wearable applications requiring a small form-factor (e.g., TWS earbuds). It is found in a variety of low-density memory devices, among which are NOR Flash, EEPROM, and SLC NAND.

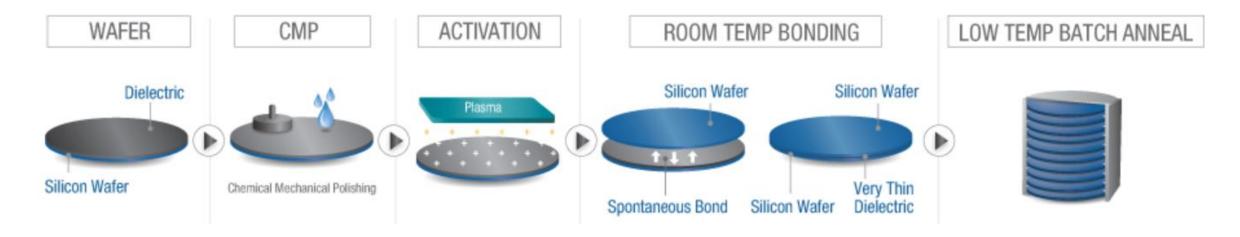

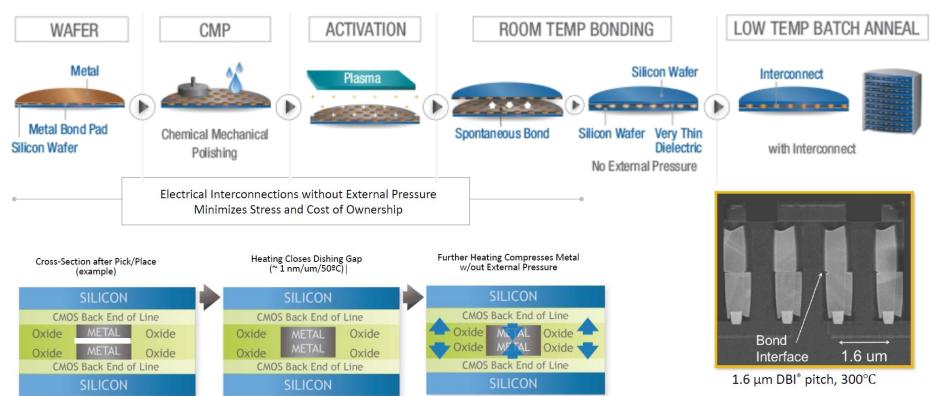

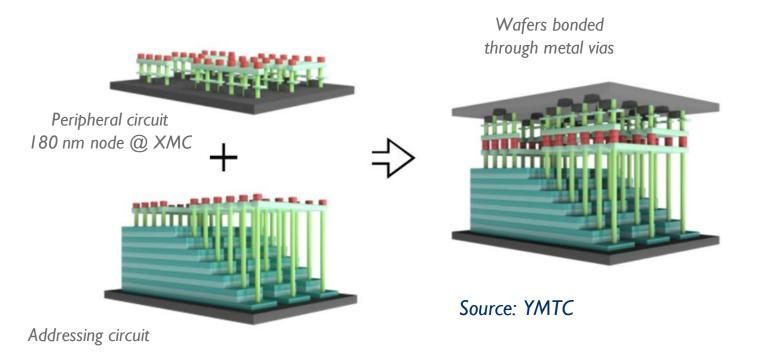

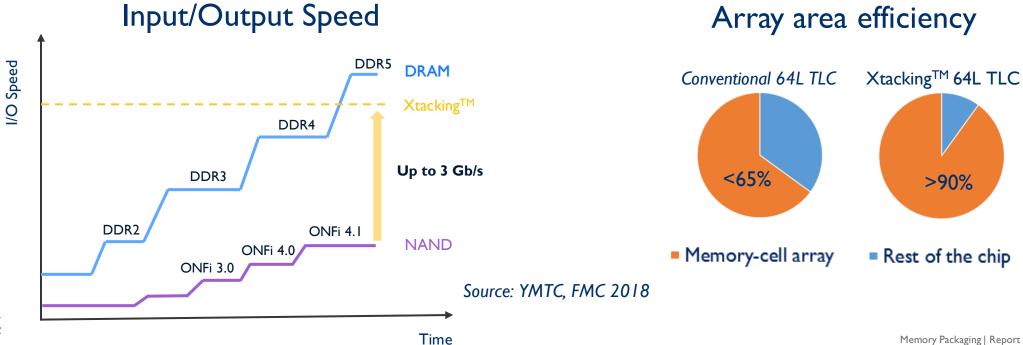

- All memory manufacturers are carrying out R&D activities on hybrid bonding. YMTC was the first player in the NAND business to adopt wafer-to-wafer hybrid bonding for its Xtacking<sup>TM</sup> 3D NAND technology. However, adopting a wafer-to-wafer stacking approach would require a massive conversion of production lines which is not feasible for companies that already have large production capacity. Therefore, we expect that incumbent players will continue with their monolithic 3D NAND solutions (e.g., CuA, PuC) for at least the next 4-5 years, until the current deck-stacking approach runs out of steam.

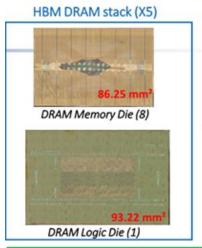

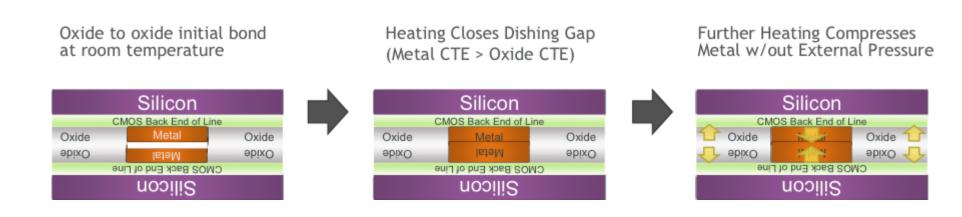

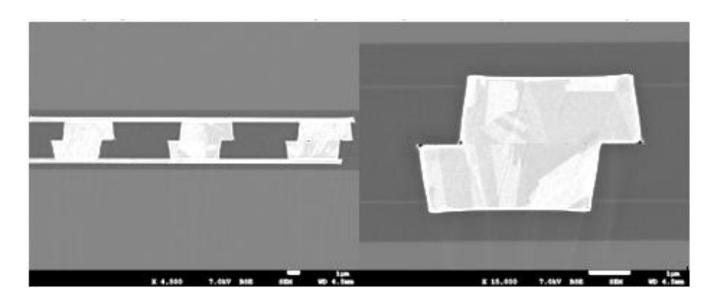

- Die-to-die or die-to-wafer hybrid bonding is widely being explored for next-generation HBM devices, and we believe it could make its first entry into the market within the next five years. However, significant technological challenges still need to be addressed to achieve the high yields suitable for high-volume manufacturing. The operating characteristics of DRAM (e.g., refresh time) are highly sensitive to temperature, so suitable low-temperature bonding procedures need to be implemented.

## MEMORY PACKAGING MARKET – OVERVIEW

- In terms of packaging revenues, **DRAM** will be the leading memory technology. It will generate up to \$13.8B in 2026, which corresponds to 70% of the overall memory packaging market. In the same year, the share of NAND is estimated to be ~25%.

- Flip-chip packaging continues to penetrate the server and PC DRAM markets at the expense of wire-bond. DRAM flip-chip revenue will grow from ~\$3.9B in 2020 to ~\$6.9B in 2026 with a CAGR<sub>20-26</sub>~10%.

- WLCSP is expected to grow in revenue at a CAGR<sub>20-26</sub>~I4%, but in terms of value will remain only ~I% of the market by 2026.

- TSV stacking for DRAM (HBM/3DS) and hybrid bonding promise to enable new progress in memory. Together, these advanced packaging technologies represent ~5% of the memory packaging revenue in 2020, and they are poised to grow to ~17% by 2026 (~\$3.2B).

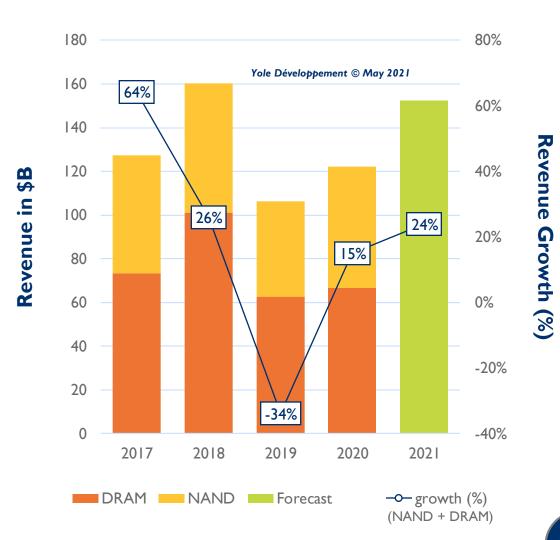

## STAND-ALONE MEMORY MARKET DYNAMICS

- Memory is a critical market in modern data-centric societies, and is driven by important megatrends, including mobility, cloud computing, artificial intelligence (AI), and the internet of things (IoT).

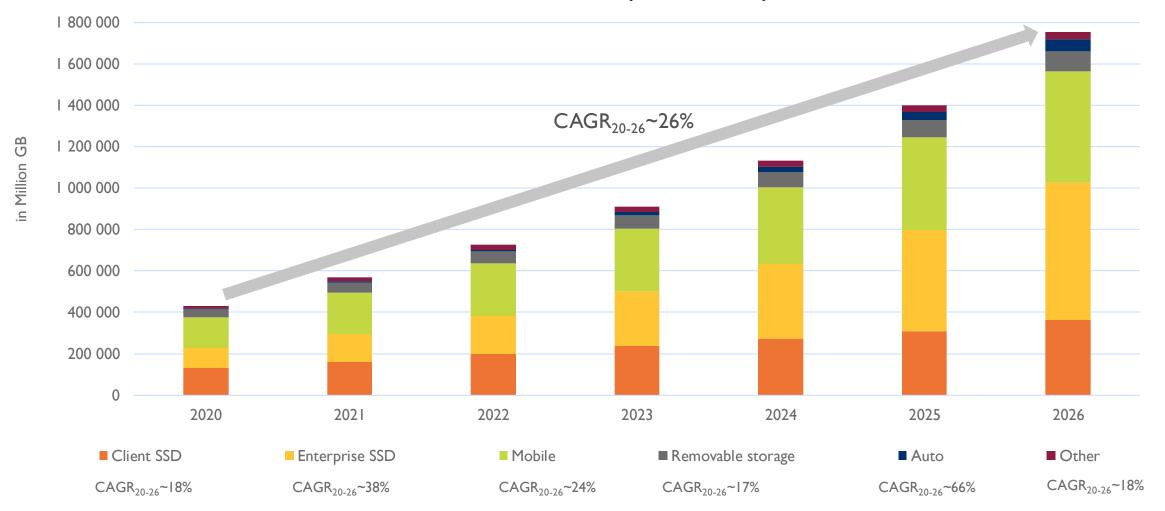

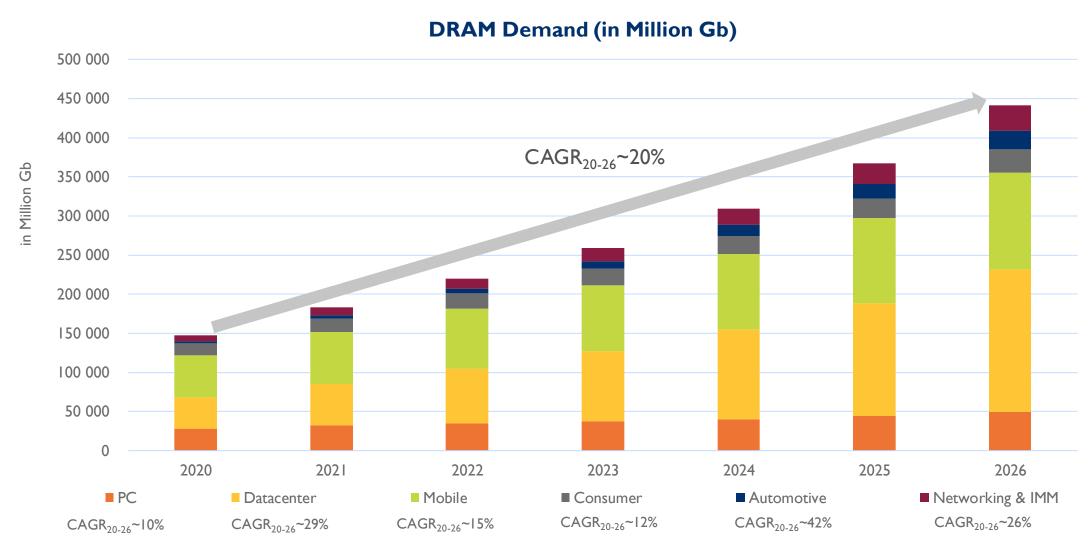

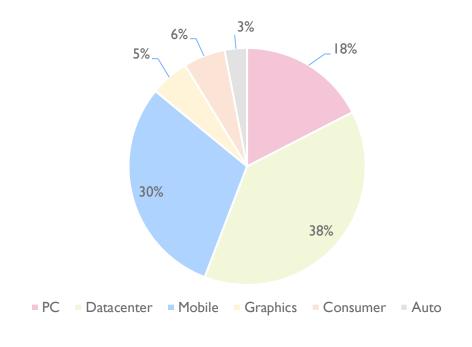

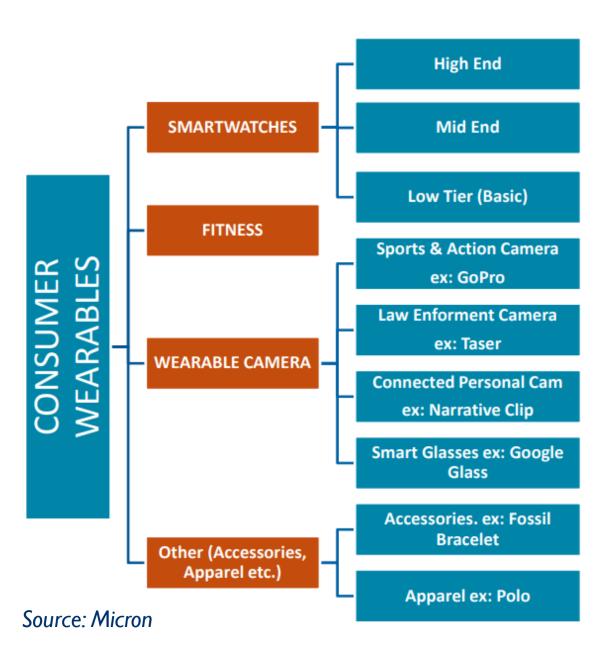

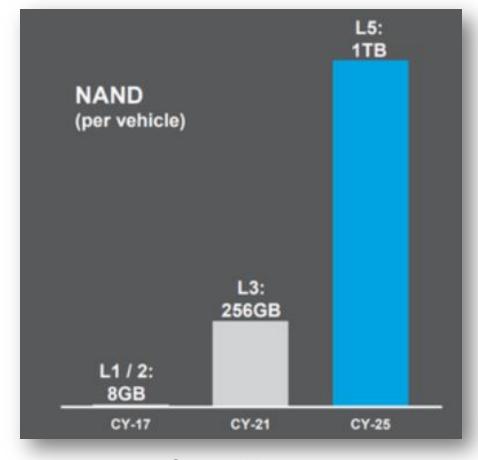

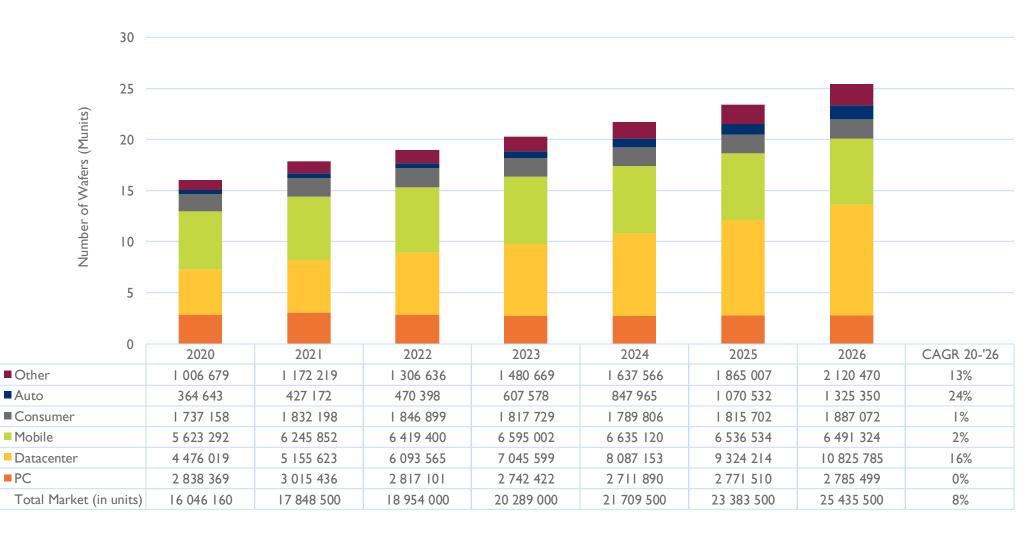

- The largest segments for memory demand are **mobile** and **data centers**. The latter, in particular, is the fastest growing segment, as new applications and systems will rely intensively on data center resources. The ongoing deployment of the 5G network in multiple countries, as well as the increasing penetration of autonomous vehicles will boost memory demand significantly.

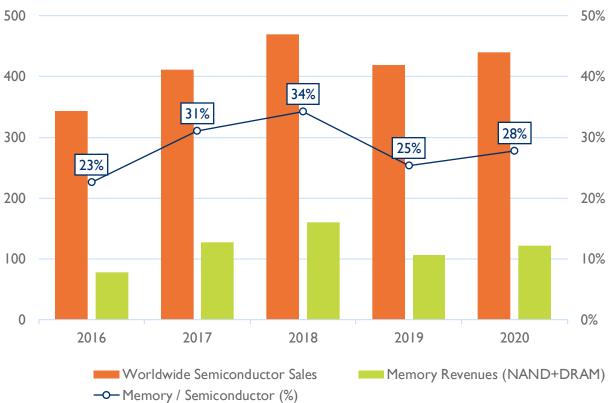

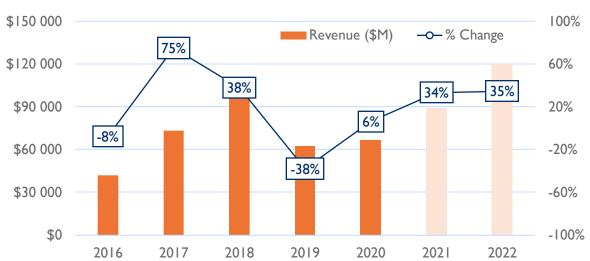

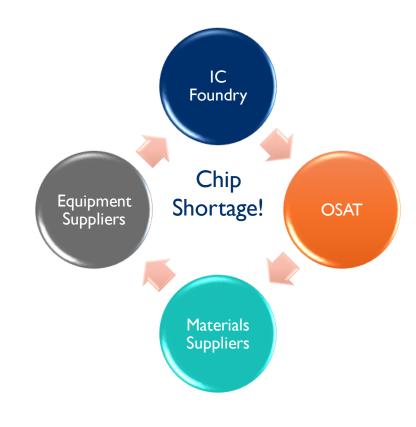

- The stand-alone memory is characterized by periods of shortages and oversupply that give rise to strong price variations and revenue volatility. NAND and DRAM account together for ~28% of the overall semiconductor market (~\$440B n 2020).

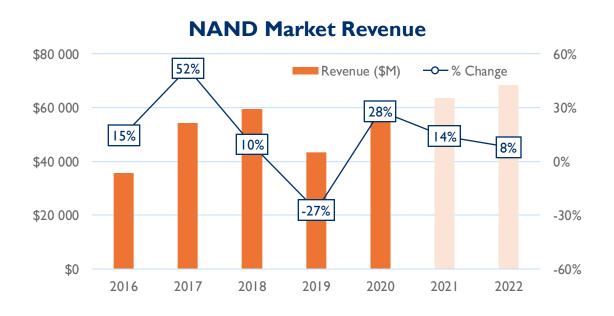

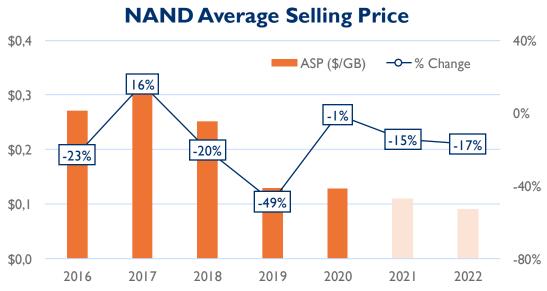

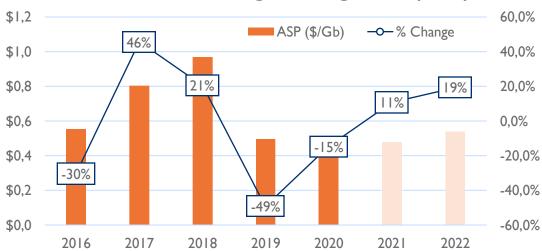

- The memory market entered a new phase of oversupply in Q4-2018, and the year 2019 witnessed a terrible collapse with combined DRAM and NAND revenue down 34% from 2018 and ASP down 49% for both NAND and DRAM. To achieve market equilibrium, memory suppliers have significantly underinvested in new production capability (CAPEX down 18% in 2019).

- Inventory levels started decreasing and market conditions began improving since early 2020 despite trade-war tensions and the outbreak of the Covid-19 pandemic. Supply-chain disruptions that occurred in the first half of 2020 were largely cleared by the beginning of 2H-2020.

- The pandemic had a mixed impact on the memory industry: data center and laptop demand grew, automotive and smartphones faced a slowdown. The net result has been a relatively balanced memory demand. Revenues could grow despite ASP still declined year-over-year.

- Combined DRAM and NAND revenue in 2020 was ~\$122B, up 15% from 2019.

- ASPs in 2020 were 0.42 \$/Gb (DRAM) and 0.128 \$/GB (NAND), down 15% (DRAM) and down 1% (NAND) from 2019.

- Thanks to a combination of CapEx cuts from suppliers in recent years and flourishing demand, the future is looking bright, particularly for DRAM.

- Revenues are expected to grow 47% for DRAM and 26% for NAND up to \$98B and \$70B, respectively. They will peak again in 2022 reaching record-high values of \$128B (DRAM) and \$80B (NAND).

- In the long term, the NAND and DRAM revenues are expected to grow to \$93B (NAND) and \$155B (DRAM) in 2026 with CAGR<sub>20-26</sub> of ~9% and ~15%, respectively. In the same period, the ASP is expected to decrease by ~5% (DRAM) and ~16% (NAND), driven by cost-per-bit reductions enabled by technology scaling.

## STAND-ALONE MEMORY MARKET – OVERVIEW

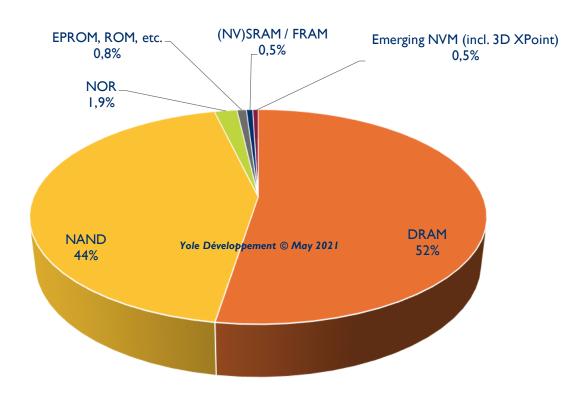

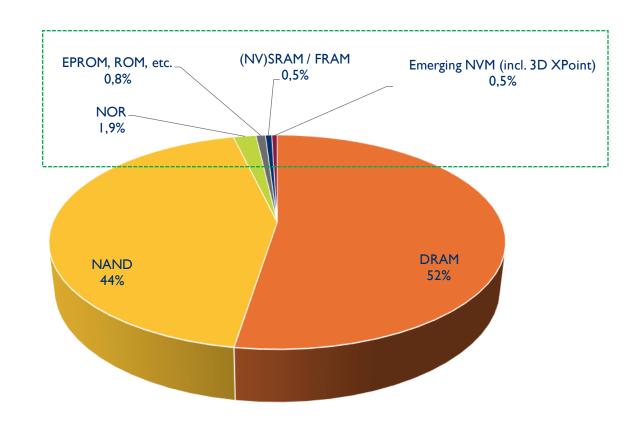

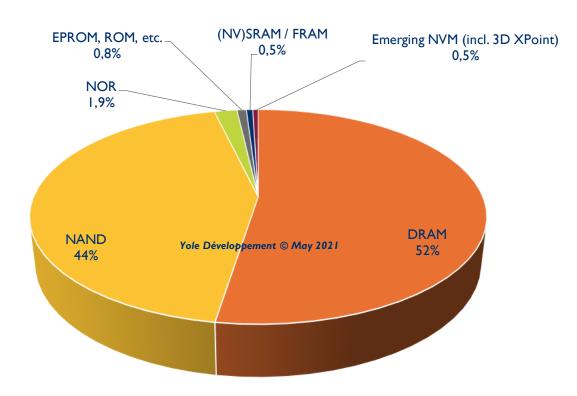

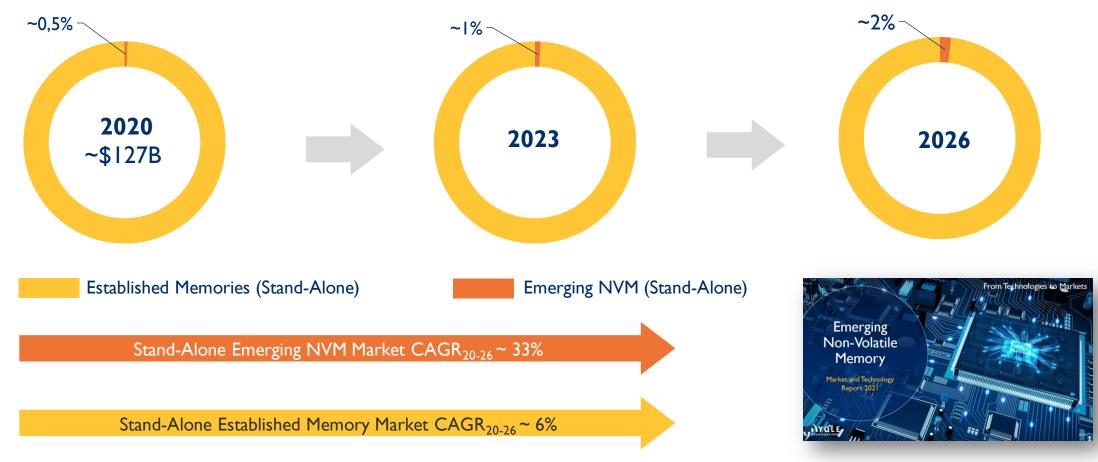

- NAND and DRAM account for ≈96% of the overall stand-alone memory market.

- Combined NAND and DRAM revenue is estimated to be ≈ \$122B in 2020, up 15% from 2019.

### 2020 Memory Market - Breakdown by Technology

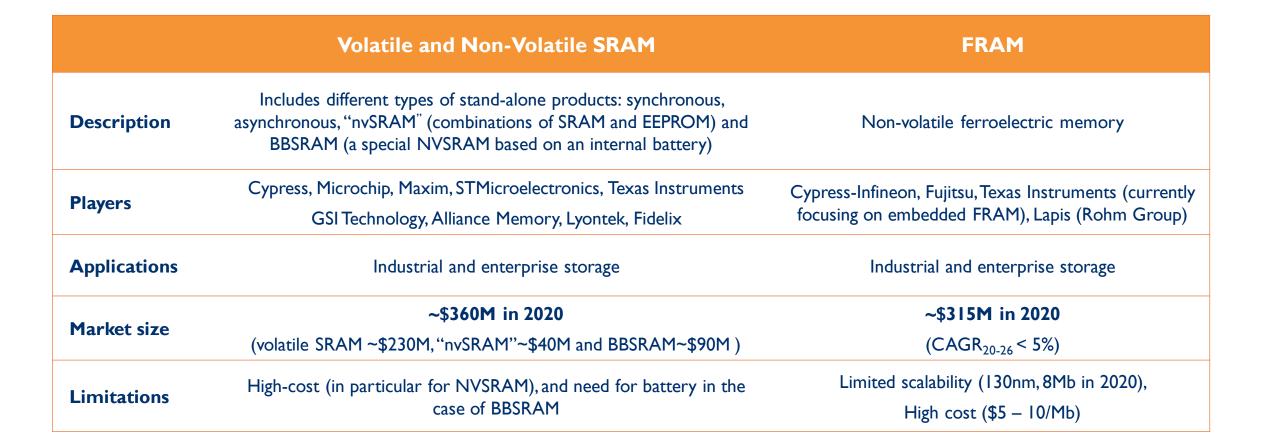

## STAND-ALONE MEMORY TECHNOLOGIES AND MARKETS

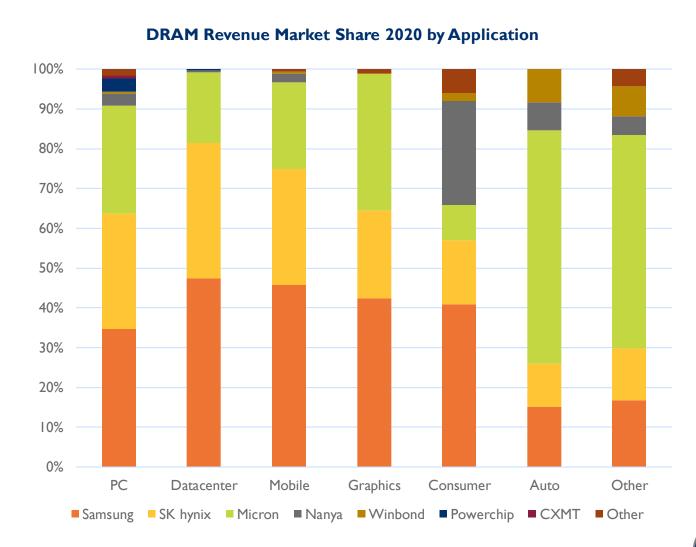

- DRAM and NAND together represent ~96% of the stand-alone memory market.

- The remaining ~4% of the market (~\$4.7B) consists of:

- Flash NOR (~\$2.4B)

- EEPROM, EPROM, Mask PROM/ROM, etc. (~\$1B)

- Volatile RAM (~\$230M)

- Asynchronous SRAM

- Synchronous SRAM

- Non-Volatile RAM (~\$450M)

- nvSRAM

- BBSRAM

- FRAM

- Stand-alone emerging NVMs (~\$600M)

- Compared to NAND and DRAM, these markets are relatively more stable.

**Total Stand-Alone Market in 2020 ~ \$127 billion**

## **KEY MEMORY END MARKETS**

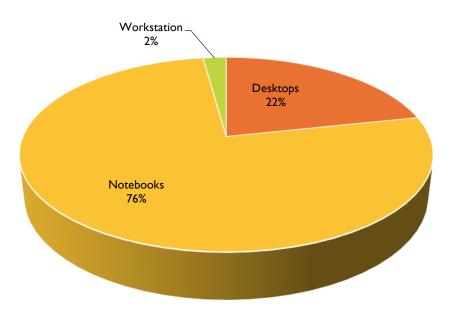

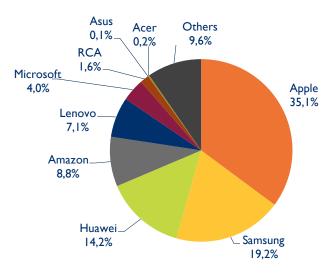

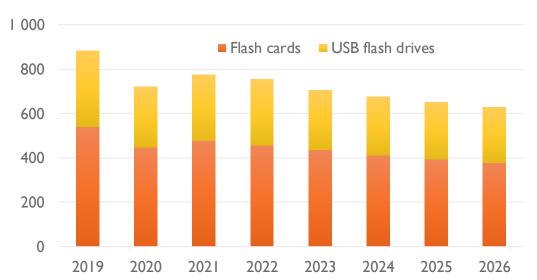

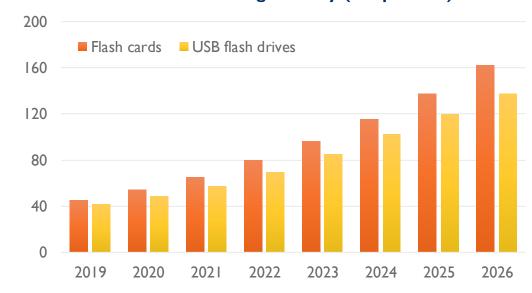

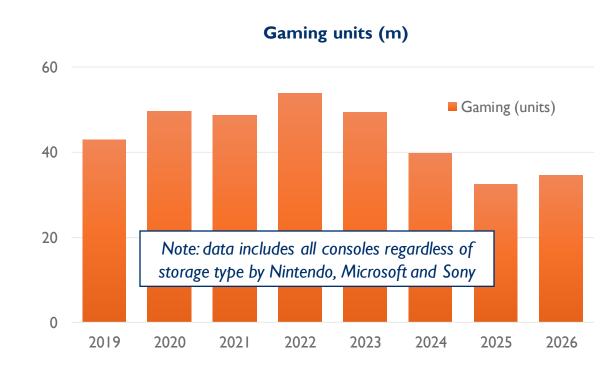

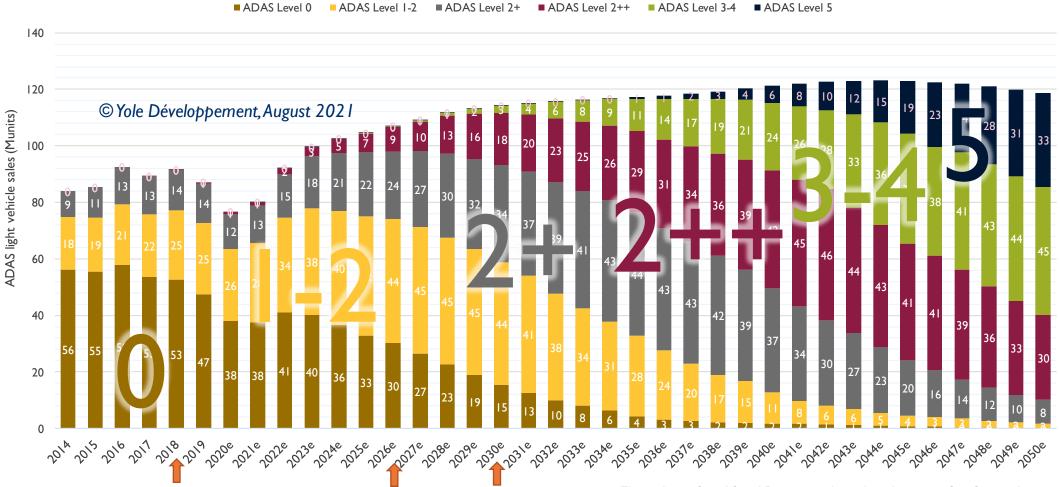

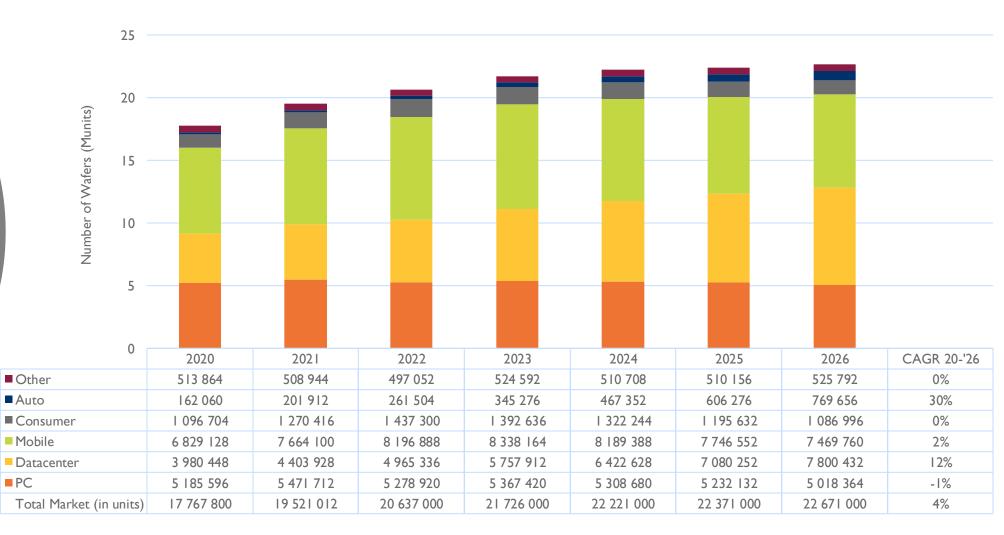

Data center and mobile are the largest market segments. Automotive is the fastest growing.

#### **NAND** and **DRAM** Wafer Demand

Data center CAGR<sub>20-26</sub> ~ I4%

Automotive CAGR<sub>20-26</sub> ~ 26%

PC/Client CAGR<sub>20-26</sub> ~ 0%

Mobile CAGR<sub>20-26</sub> ~ 2%

Consumer CAGR<sub>20-26</sub> ~ 1%

Other CAGR<sub>20-26</sub> ~ 10%

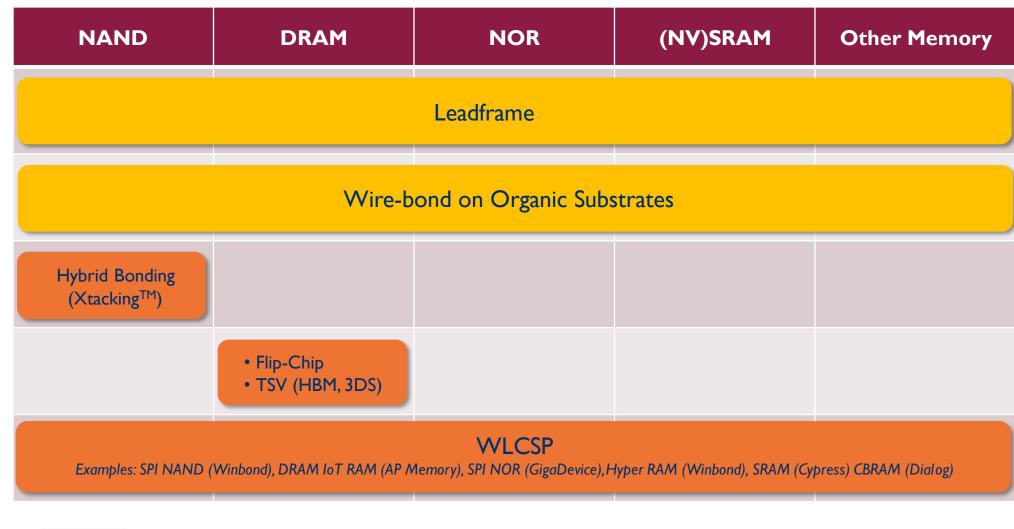

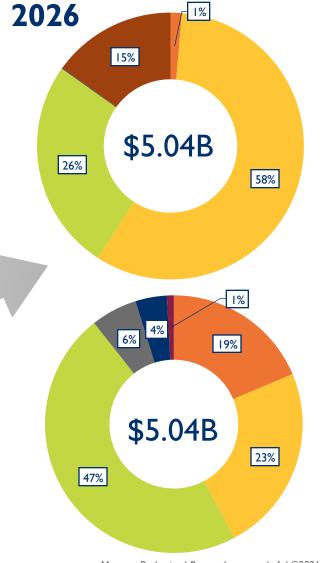

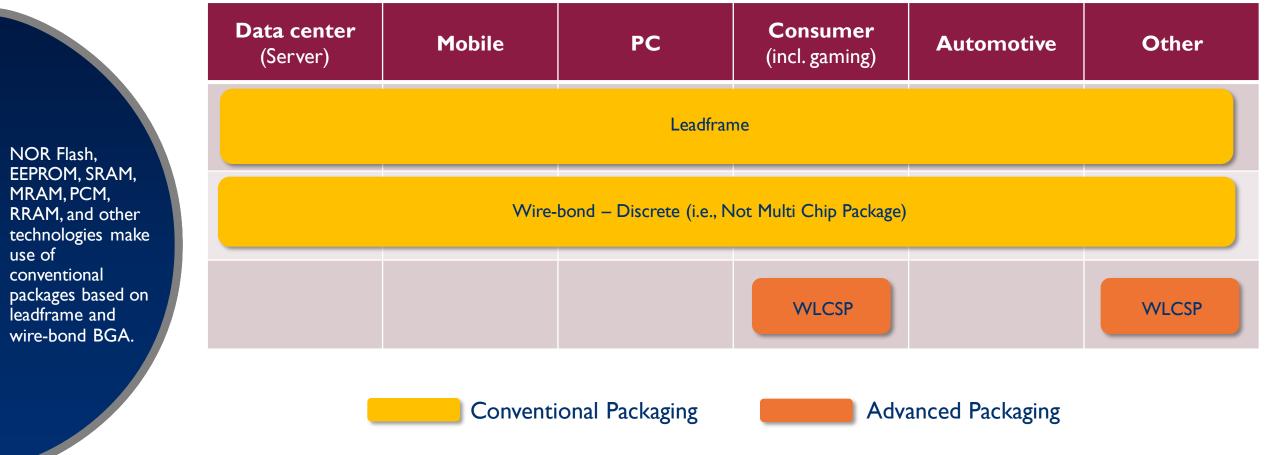

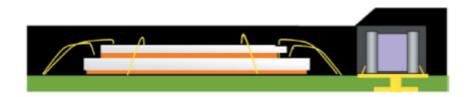

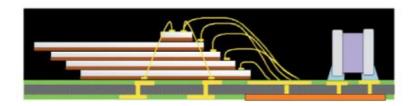

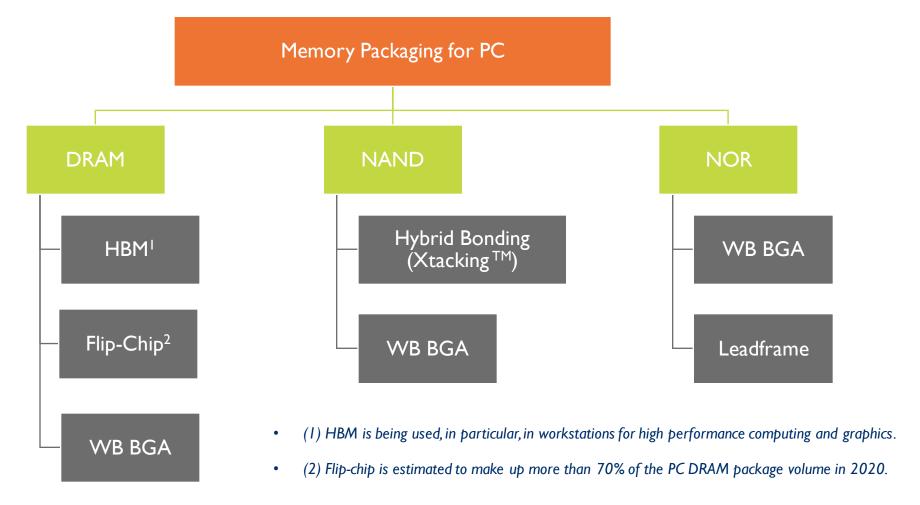

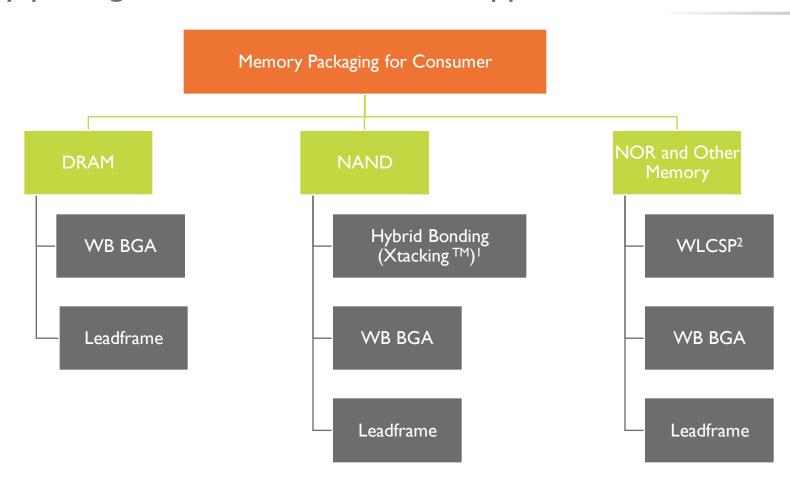

## MAIN MEMORY PACKAGING PLATFORMS

Memory devices use a wide varieties of packages

TSOP-SD2 (2+0) staircase

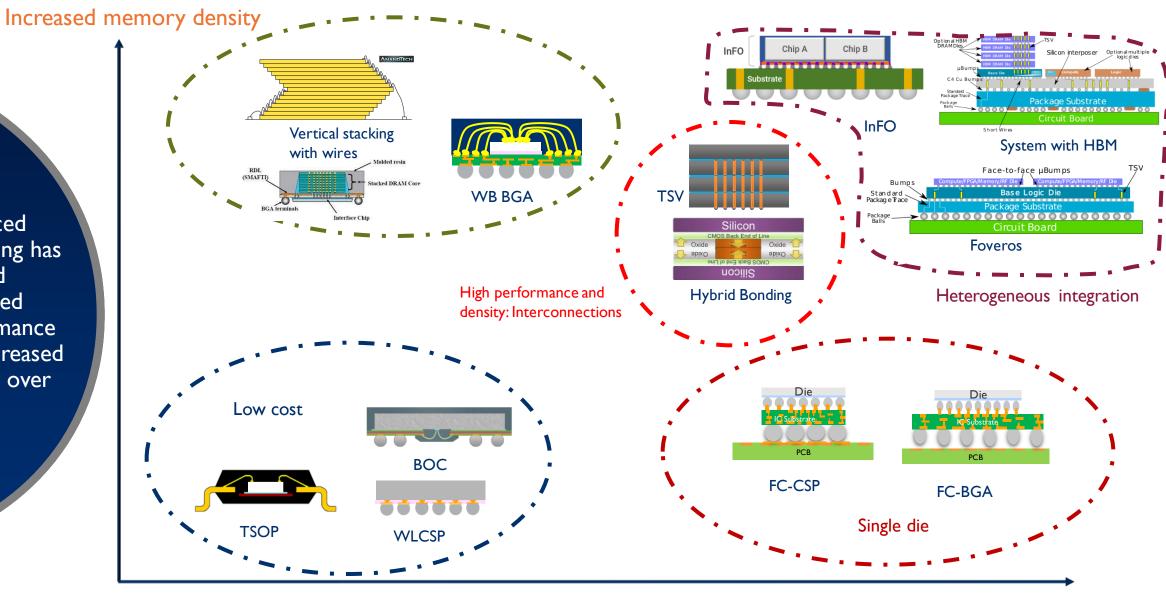

## PACKAGING LANDSCAPE

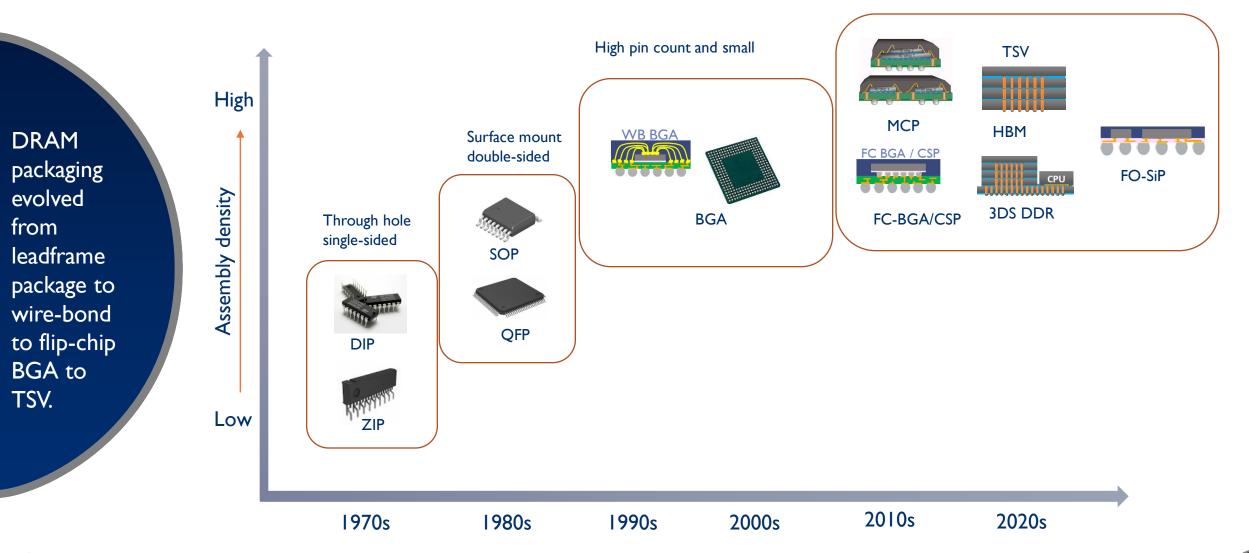

Advanced packaging has enabled improved performance and increased density over time.

## STAND-ALONE MEMORY PACKAGING

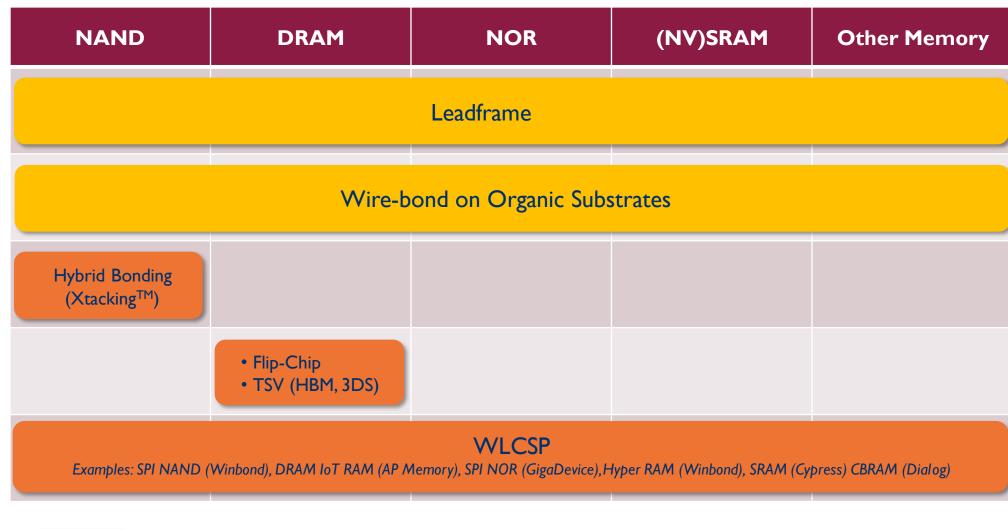

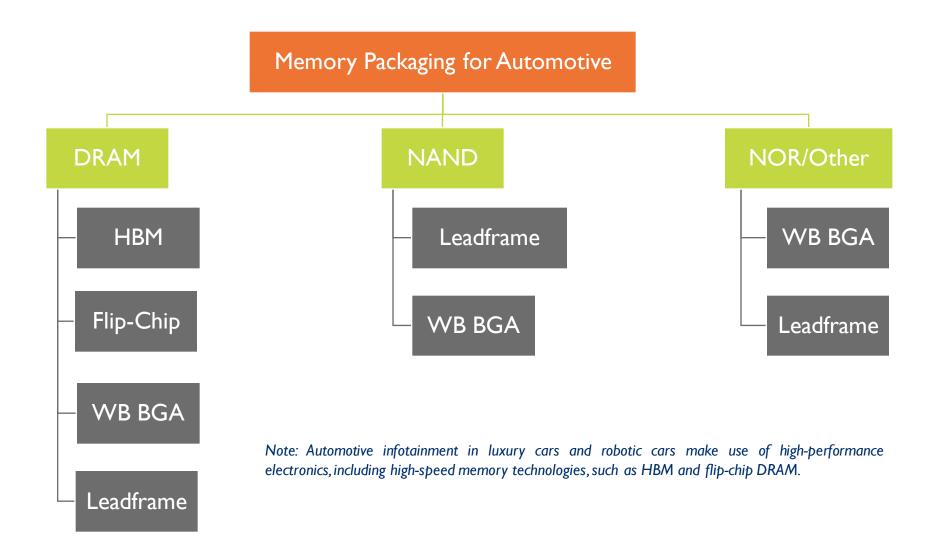

## Packaging Approaches for Stand-Alone Memory Technologies

Leadframe and wire-bond packaging technologies are used for all types of memory. WLCSP is making inroads in consumer/loT applications.

## STAND-ALONE MEMORY PACKAGING MARKET – OVERVIEW

from the ongoing memory-wafer capacity expansion.

- The memory packaging market follows the trends that rule the stand-alone memory market, given that packages are fundamental building blocks of all memory devices. Hence, the memory packaging market will benefit from the strong growth of memory-bit demand which is driven by important megatrends (AI, IoT, big data, autonomous driving, and more) as well as

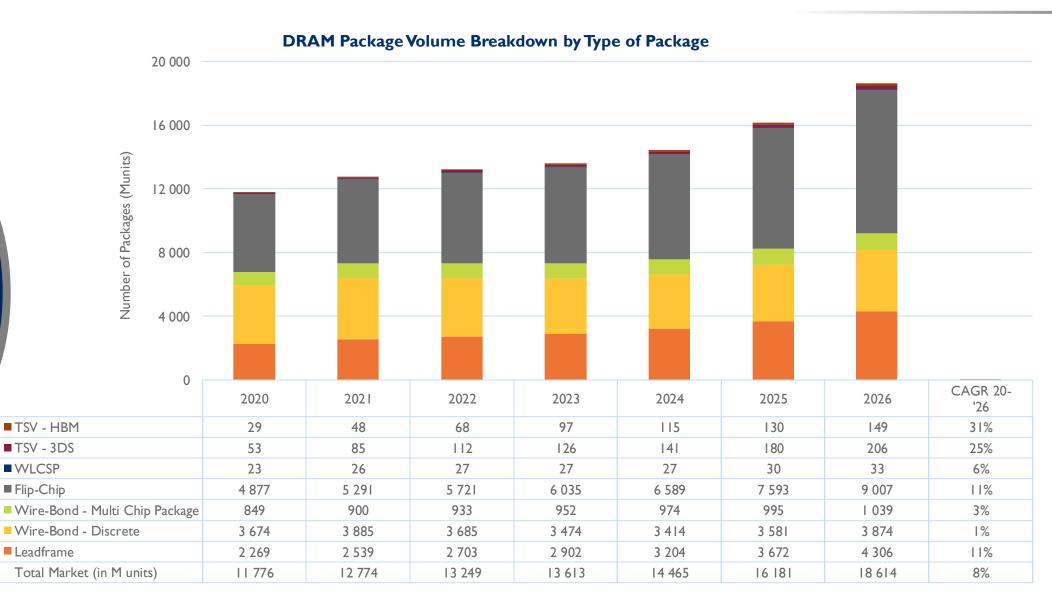

- We estimate that the overall volume of memory wafers will grow from ~35.5M in 2020 to ~50M in 2026 with a CAGR<sub>20-26</sub> of ~6%, whereas **the volume of memory packages will rise from ~27B in 2020 to ~36B in 2026 with a CAGR<sub>20-26</sub> of ~5%.** DRAM is the largest market segment by volume due to the continuous growth of flip-chip packages containing a single die.

- In contrast to the stand-alone memory market which is characterized by high price volatility, the memory packaging market is more stable since most of the business is carried out internally by memory IDMs (note: internal margins are assumed to be stable over time). We estimate that in 2020 approximately 68% of the memory packaging revenue was generated by IDMs. The remaining 32% was generated by OSATs, which need to offer competitive pricing to motivate IDMs to outsource a larger portion of their memory packaging.

- The **overall memory packaging market** is worth **~\$13.1B** in **2020** (note: testing is not included) and will grow to **~\$19.8B** in 2026 (CAGR<sub>20-26</sub>~7%).

- Wire-bond is the most common packaging technology for NAND (~98% of NAND packaging revenues in 2020) and for mobile memory; it will remain the dominant type of package, followed by flip-chip, which is continuing its expansion in the server amd PC DRAM business.

- Micron did not initiate the conversion process as early as its Korean competitors but has also been readying its own flip-chip packaging lines and will attempt to reduce its dependence on OSATs (e.g., PTI, ChipMOS) for flip-chip packaging. Note: The adoption of flip-chip packaging with short interconnects will be essential to fully exploit the potential of DDR5 and subsequent DRAM generations.

- In terms of packaging revenues, DRAM will be the key memory technology driving growth. It will generate revenue of \$13.8B in 2026, which corresponds to 70% of the overall packaging market. In the same year, the share of NAND is estimated to be ~25%.

The memory packaging market will benefit from the robust demand for DRAM and stand-alone Flash memory technologies.

## MEMORY PACKAGING MARKET REVENUE FORECAST (2020-2026)

Breakdown by memory technology

In terms of packaging revenue, DRAM will be the key memory technology driving growth. It alone will generate revenue of \$13.8B in 2026.

#### Memory Package Revenue Breakdown by Memory Technology

Note: Revenue for MCP memory is split between the NAND and DRAM market segments with weightings that depend primarily on the average number of NAND/DRAM dies per package.

## MEMORY PACKAGING MARKET REVENUE FORECAST (2020-2026)

## Breakdown by type of package

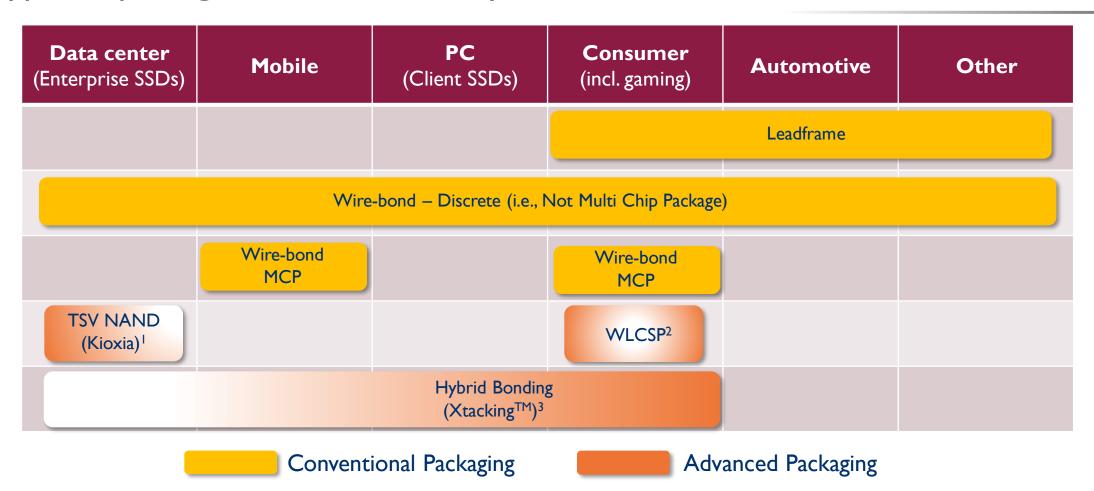

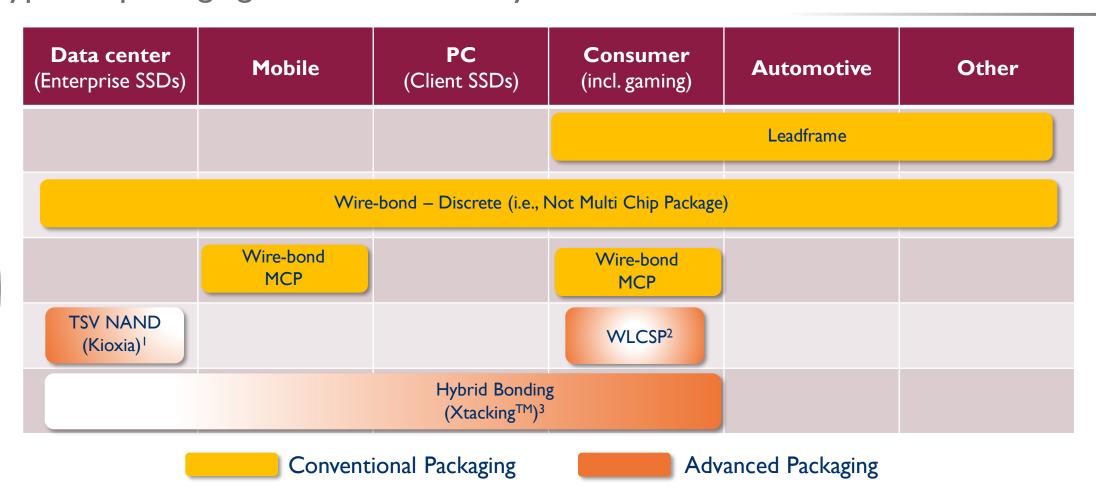

## STAND-ALONE MEMORY PACKAGING – FOCUS ON NAND

## Main types of package for NAND flash by end-markets

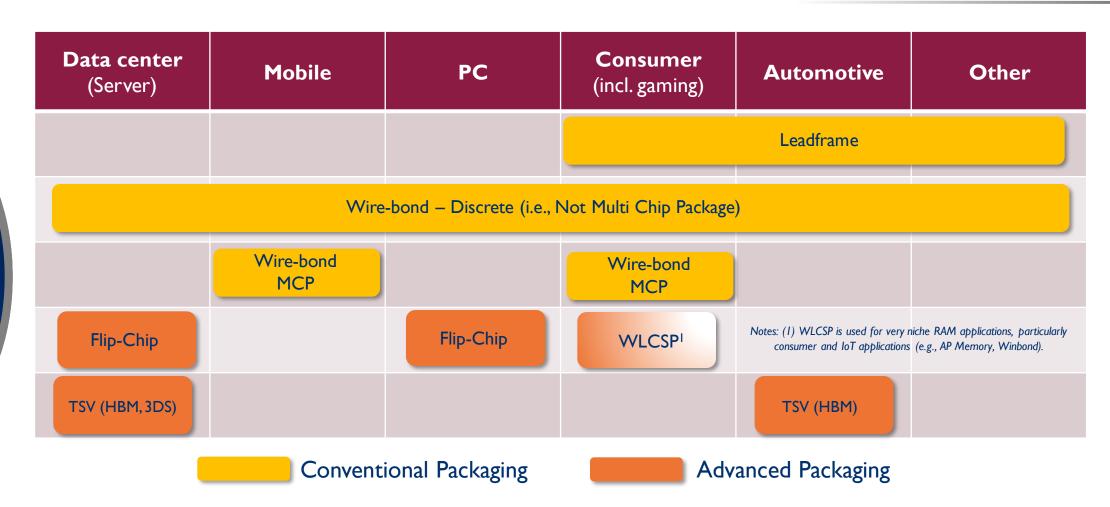

At this stage, advanced packaging (AP) techniques are not necessary. NAND is a relatively "slow" technology, so there is no motivation to use AP to boost the performance.

Notes: (1) Toshiba (Kioxia) introduced TSV NAND for high-end storage applications in data centers (<u>link to news</u>), but it has not had a significant market penetration to date. (2) WLCSP is used for niche SPI NAND consumer applications (e.g., Winbond). (3) YMTC currently targets the consumer and the PC markets (client SSD), with plans to tackle the smartphone market in the short term and data center applications in the long term (requirement: filling the technology gap with other memory suppliers).

NAND PACKAGING - MARKET EVOLUTION

By type of package and by application

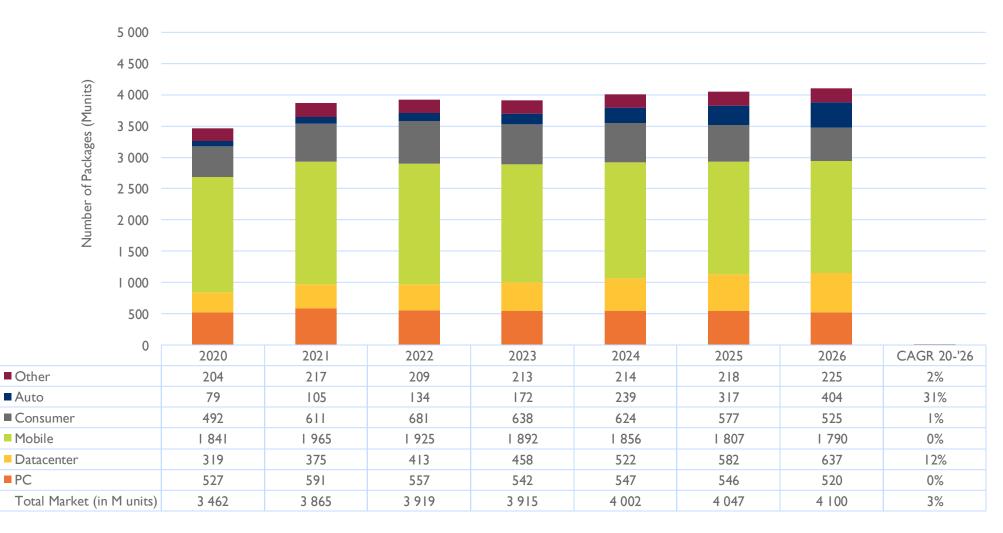

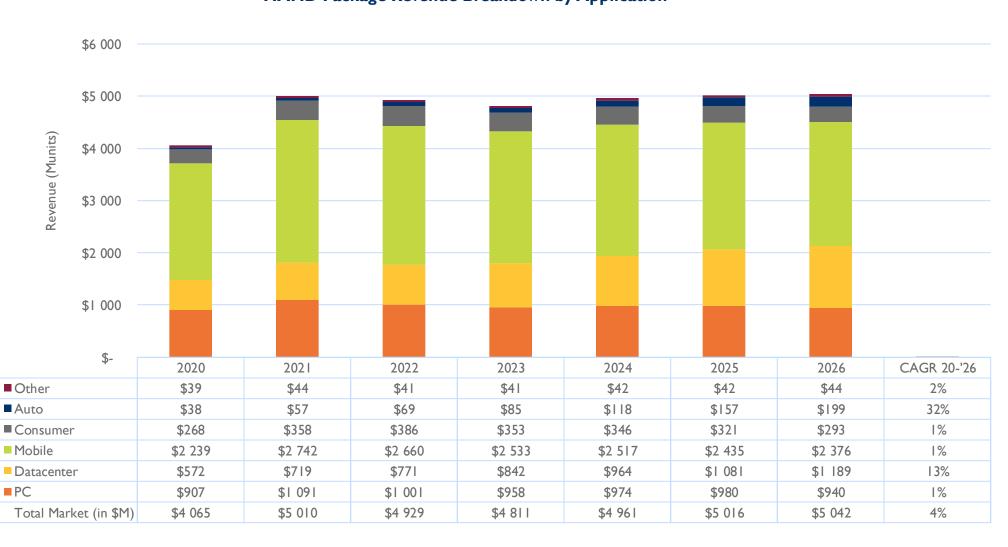

Wire-bond packaging on organic substrates represents more than 98% of NAND packaging. Mobile is the largest market segment followed by SSDs (client or enterprise). Auto and data center are the fastest growing segments.

### STAND-ALONE MEMORY PACKAGING

## Focus on NAND packaging evolution & roadmap

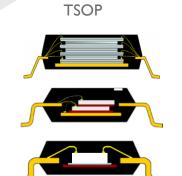

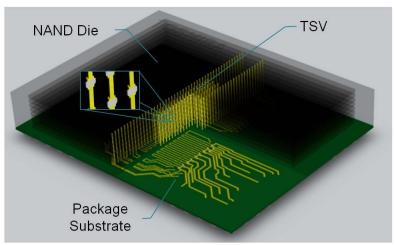

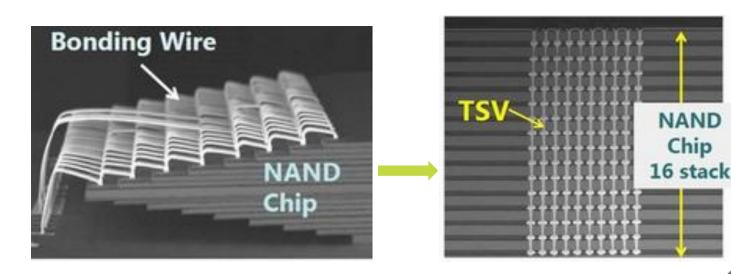

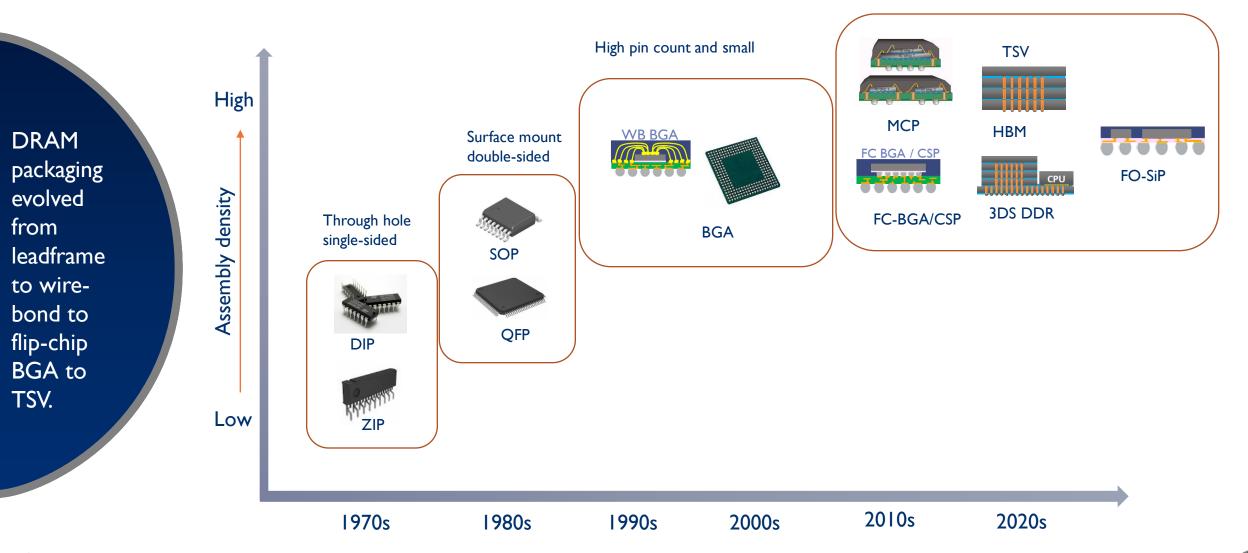

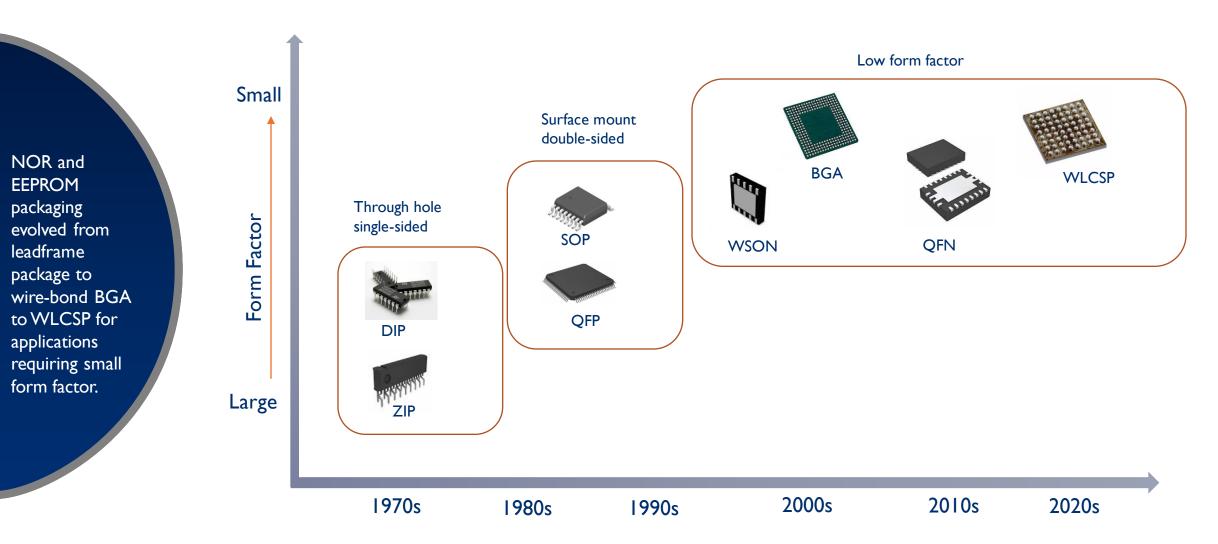

Multi die High pin count and small High MCP NAND Surface mount packaging double-sided Hybrid **BGA** evolved **Bonding Assembly density** from Through hole leadframe single-sided SOP package to wire-bond BGA to **QFP** DIP TSV. Low 2020s 2010s 2000s 1970s 1980s 1990s

#### STAND-ALONE MEMORY PACKAGING – FOCUS ON DRAM

## Main types of package for DRAM by end-markets

Flip-chip has penetrated the server/PC DRAM packaging market, driven by Samsung and SK hynix.

Wire-bond will remain the leading packaging technology for mobile DRAM.

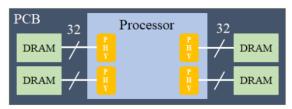

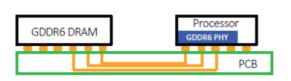

• The memory packaging technology for PC/server DRAM applications has been migrating from wire-bond to flip-chip. Flip-chip packaging is used for GDDR (graphics). For mobile DRAM (LPDDR), wire-bond will continue to be the packaging choice.

#### DRAM PACKAGING – MARKET EVOLUTION

By type of package and by application

Flip-chip is the leading type of package for DRAM, having already being adopted by Samsung and SK hynix for DRAM in PCs and data centers (i.e., the largest markets segments). Micron will also adopt flip-chip, propelling further growth.

#### STAND-ALONE MEMORY PACKAGING

## A

## Focus on DRAM packaging evolution & roadmap

#### FLIP-CHIP PACKAGING FOR SERVER AND PC DRAM

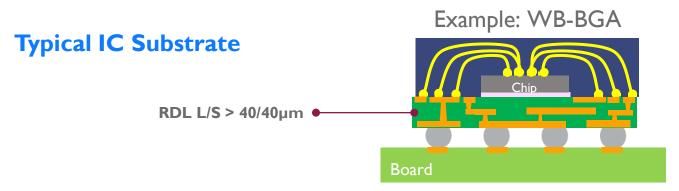

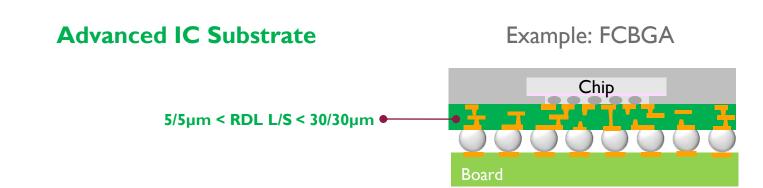

- In the last five years, the packaging for **PC and server DRAM** has been progressively migrating from wire-bond to flip-chip. Although, wire-bond packaging enables sufficient bandwidth to cope with DDR4/DDR5 data rates, Samsung and SK hynix have converted most of their DRAM packaging lines into flip-chip.

- At the start of such changes, there was probably a strategic decision by Korean players particularly Samsung to exploit the full capacity of their flip-chip packaging lines, while at the same time getting ready for new high-speed DDR generations. Note: DDR5 and DDR6 deliver high bandwidth for which wirebond is probably not the best choice (note: wires introduce a latency penalty). The adoption of flip-chip (FC) for server and PC DRAM by Korean players is estimated to be >50% for DDR3 and >95% for DDR4 and DDR5.

- Micron did not initiate the wire-bond-to-FC conversion process as early as its Korean competitors. However, industry sources report that Micron is currently optimizing the yields of its own flip-chip packaging lines, which will be used for packaging DDR5 DRAM and beyond.

- Notes: (I) The adoption of flip-chip packaging with short interconnects suitable for low latency will be essential to fully exploit the potential of DDR5 and subsequent DRAM generations. (2) Micron will attempt to reduce its dependence on OSATs (e.g., PTI, ChipMOS) for flip-chip packaging, leading to loss of memory-packaging revenue on the OSATs' side.

#### Flip-Chip Packaging – Technical Characteristics and Roadmap

| Typical    |        | Metrics                  | <2017            | 2019                | 2022       | 2025         |

|------------|--------|--------------------------|------------------|---------------------|------------|--------------|

| Substrate) | FC BGA | Substrate RDL L/S        | 30/30 to 10/10μm | 10/10 to            | o 5/5μm    | 8/8 to 5/5μm |

|            |        | Substrate I/O pitch      | 1200 to 350μm    |                     |            | 300μm        |

|            |        | Substrate I/O ball       | 500 to           | 500 to 3000 >> 3000 |            | 3000         |

| 5          |        | Max package size         | > 65x65mm        |                     | >> 80x80mm |              |

| Flip-chip  | FC CSP | Max no. of dies/passives | < 15             | < 35                | >> 35      |              |

|            |        | Max no. of RDLs          | 10 to 16x RDL    |                     | >> 10x RDL |              |

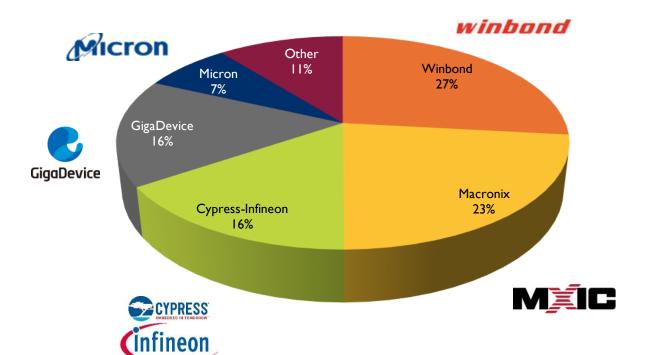

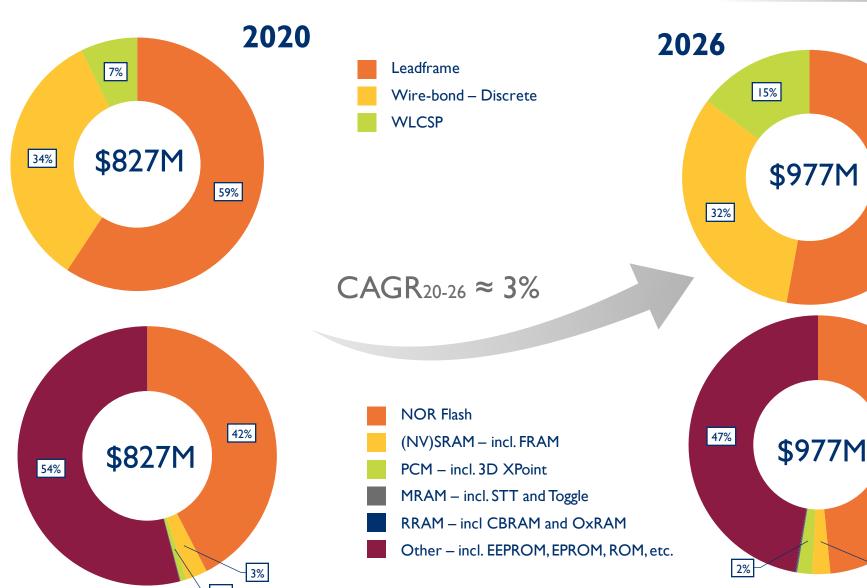

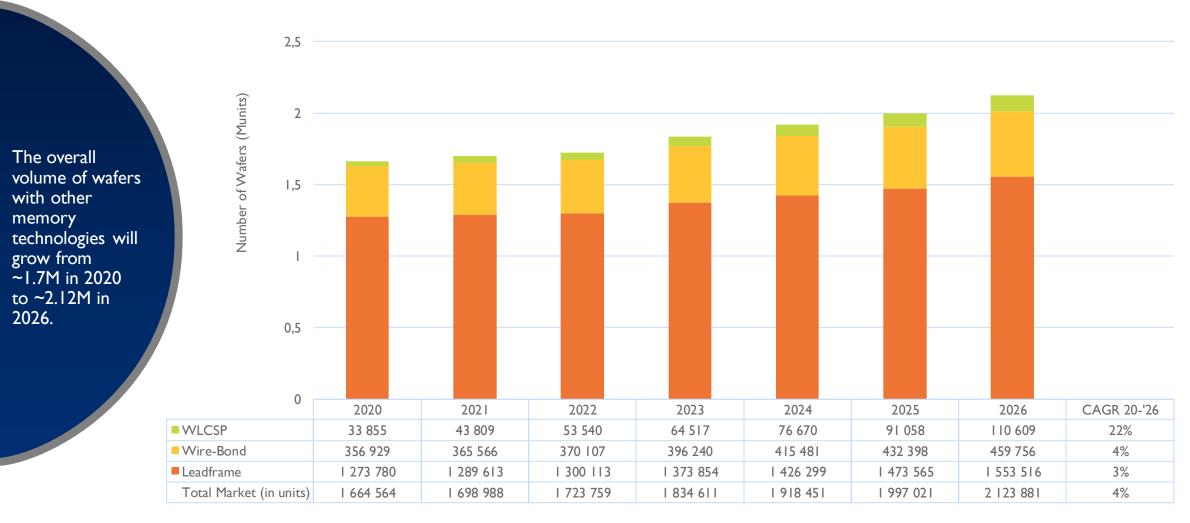

#### STAND-ALONE MEMORY PACKAGING – FOCUS ON OTHER MEMORY

Main types of package for other memory by end-markets

• WLCSP has started penetrating the NOR/EEPROM flash market for consumer and other wearable applications requiring small form factors. (Key suppliers: Winbond, Macronix, Cypress-Infineon, GigaDevice).

#### OTHER MEMORY PACKAGING - MARKET EVOLUTION

By type of package and by memory technology

Other memory technologies mainly use conventional packages that contain a single die.WLCSP is here the only advanced packaging, and its increasing adoption is driven by small formfactor consumer applications.

## STAND-ALONE MEMORY PACKAGING

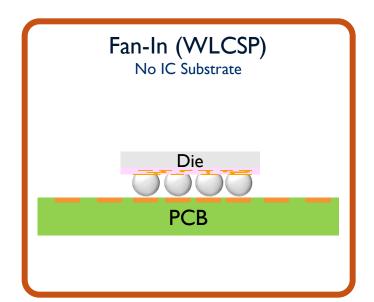

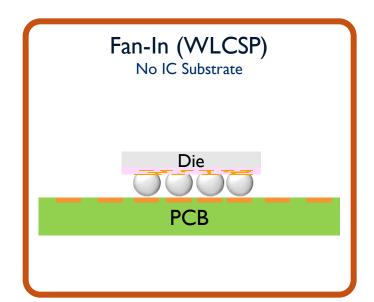

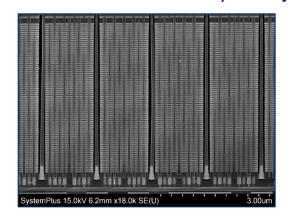

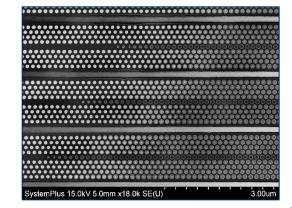

## WAFER LEVEL CHIP SCALE PACKAGING (WLCSP)

## A growing fan-in packaging approach for memory in consumer devices

Examples of consumer products containing NOR/EEPROM serial memory with WLCSP:

- Huawei Watch GT 2 (46mm)

- Jabra Elite 75t

- Huawei M-Pen 2

- Amazon Echo Frames

- Amazon Echo Buds

- Garmin International Vivoactive 4

- Amazon Halo band

- Fitbit Charge 3

Source: System Plus Consulting <a href="https://www.reverse-costing.com">https://www.reverse-costing.com</a>

Example: WLCSP NOR Flash and SLC NAND by GigaDevice

- Why WLCSP? It is not expensive, it has a small form factor, good thermal conduction, and it reduces the die/PCB inductance.

- **Main markets**: mobile, consumer (wearables, TWS...)

- Fan-in WLCSP has earned a large market share in the past five years due to its advantages (low cost, thin package). It is a substrate-less approach but faces inherent limitations due to available die area for re-routing.

#### 兆易创新NOR Flash

- 容量 4Mb~512Mb

- 1.8V供电

#### 兆易创新NAND Flash

- 容量 1Gb~2Gb

- 1.8V和3.3V供电

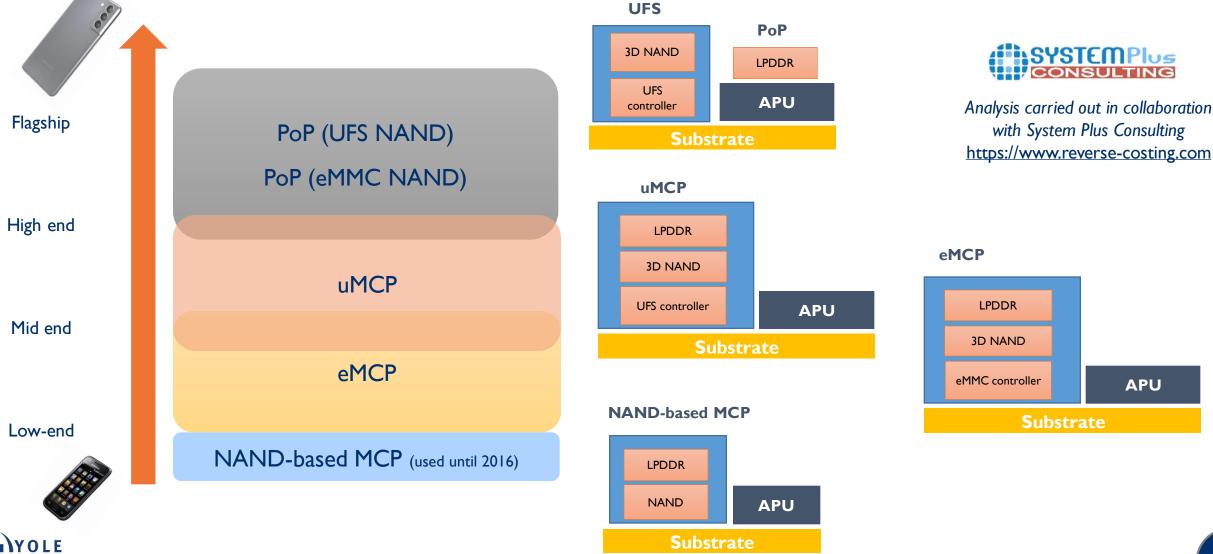

#### MEMORY PACKAGING FOR MOBILE

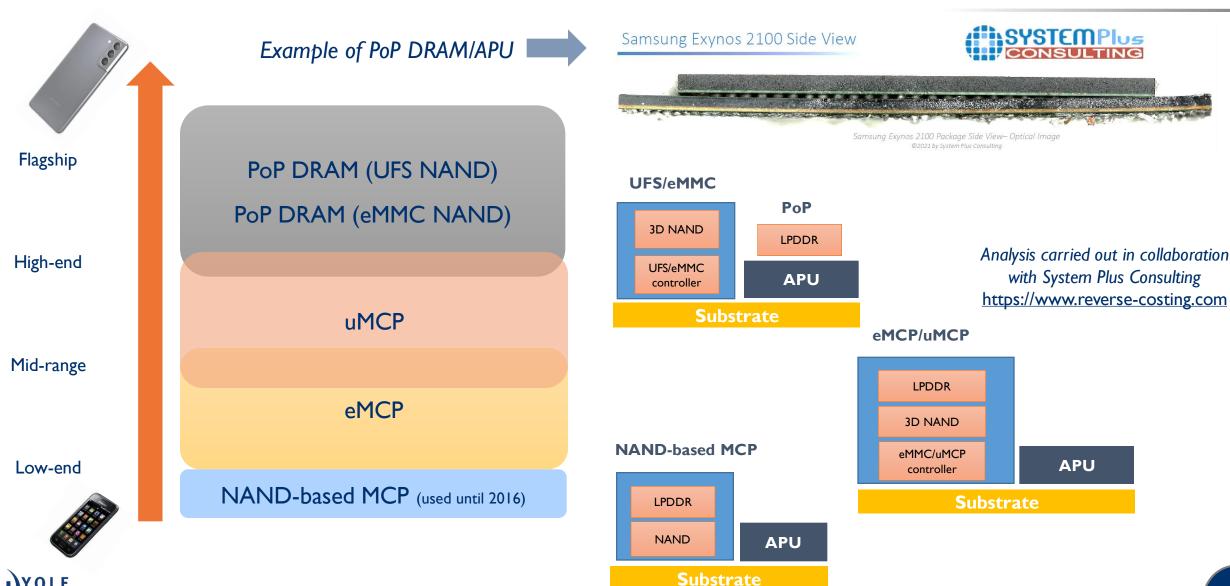

# DRAM configurations (MCP or PoP) by smartphone class

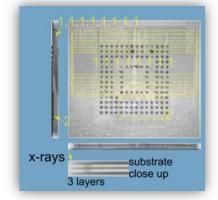

#### SMARTPHONE TEARDOWNS BY SYSTEM PLUS CONSULTING

Memory configurations in mobile & consumer electronics were assessed through teardown analyses carried out by System Plus Consulting

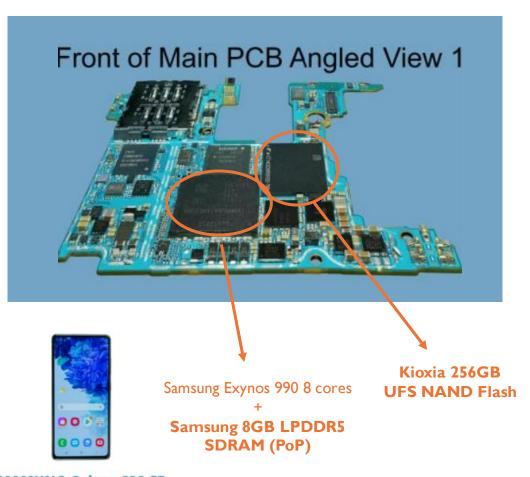

#### **Example: Samsung Galaxy S20 FE Teardown**

#### **DRAM** package

| Characteristic     | Value                   |

|--------------------|-------------------------|

| Packaging size (L) | I4mm                    |

| Packaging size (W) | I2.4mm                  |

| Packaging size (H) | 0.6mm                   |

| Dies/package       | 8                       |

| Type of package    | PoP Top                 |

| Balls/Pins         | 496                     |

| Pitch              | 0.4mm                   |

| Substrate material | FR4 3Layers<br>0.07mm H |

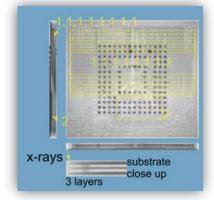

# x-rays substrate close up

#### **NAND** package

| Characteristic     | Value                   |

|--------------------|-------------------------|

| Packaging size (L) | 13mm                    |

| Packaging size (W) | 11.5mm                  |

| Packaging size (H) | 0.7mm                   |

| Dies/package       | 8 + I ctrl.             |

| Type of package    | BGA                     |

| Balls/Pins         | 153                     |

| Pitch              | 0.4mm                   |

| Substrate material | FR4 3Layers<br>0.11mm H |

Source: System Plus Consulting <a href="https://www.reverse-costing.com">https://www.reverse-costing.com</a>

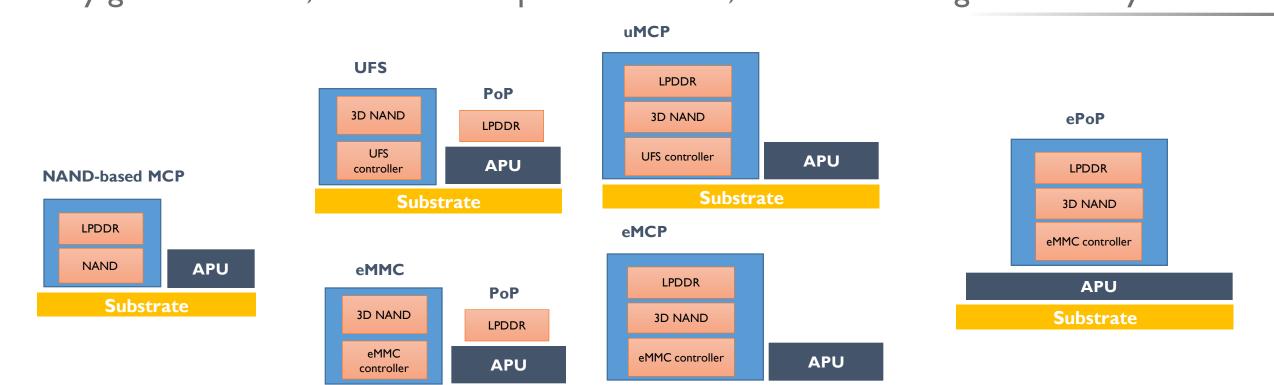

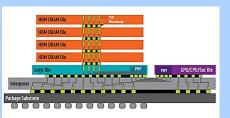

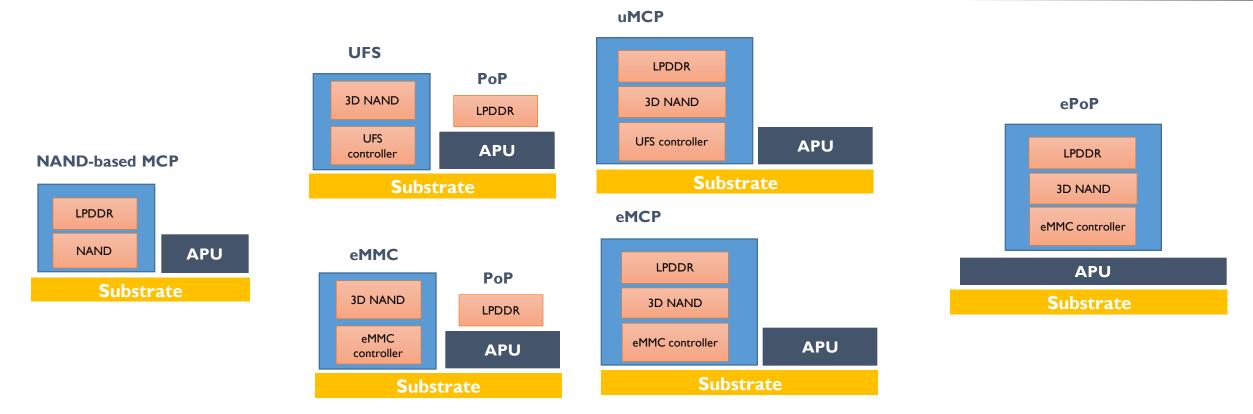

#### MEMORY PACKAGING FOR MOBILE: SYSTEM-IN-PACKAGE SOLUTIONS

Key goals: thinness, minimum footprint-on-board, low cost and high bit density

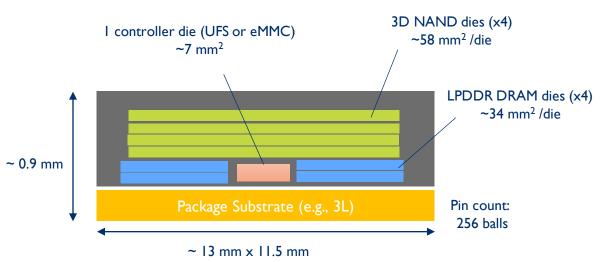

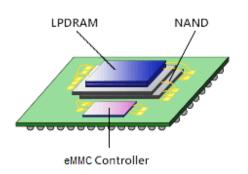

• In the early smartphones, the mainstream storage solution was NAND-based MCP that includes SLC NAND and LPDDR DRAM packaged together, which had the advantages of low production costs.

**Substrate**

• eMCP is eMMC (NAND flash + control chip) and low-power DRAM package. It is widely used in low-end and middle-end mobile phones.

**Substrate**

• Compared with the traditional MCP, eMCP can not only increase the storage capacity and meet the requirement of large capacity for mobile phones, but the embedded control chip can also reduce the burden on the main CPU, thereby simplifying and better managing large-capacity NAND flash chips and save space on the phone's motherboard.

#### MULTICHIP PACKAGING FOR SMARTPHONE DEVICES

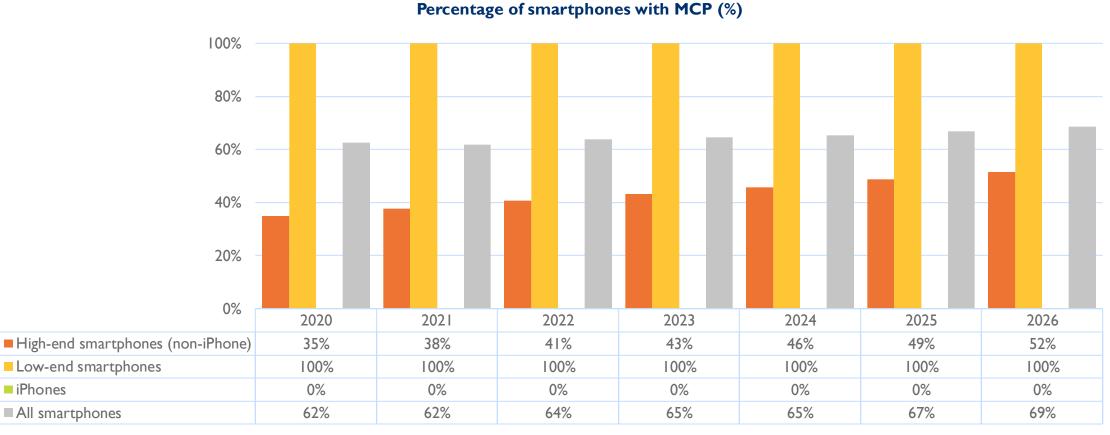

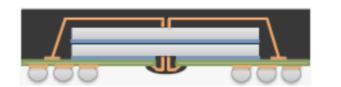

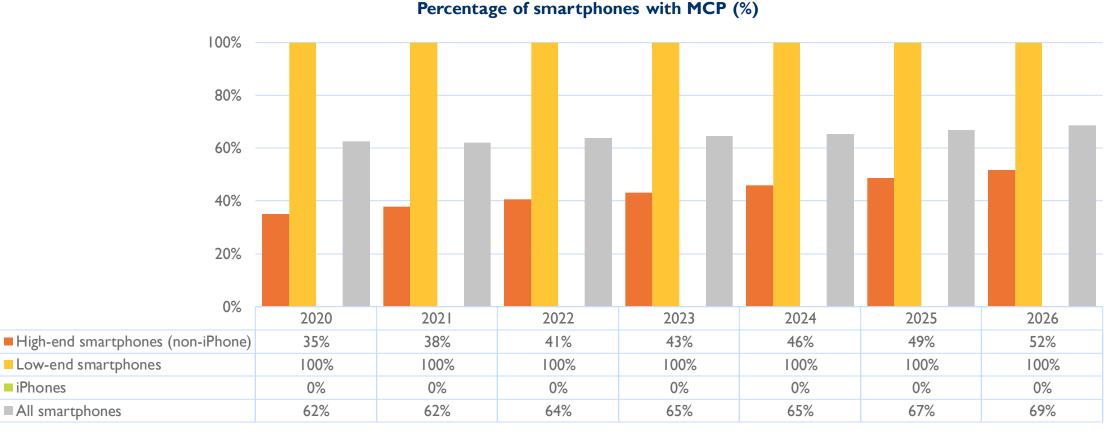

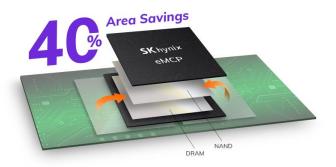

- Multi Chip Packaging (MCP) where NAND and DRAM dies are included in the same package allow optimization of the ratio between the memory-bit capacity and the overall size of packages to be mounted on the smartphone PCB.

- MCP has been used for more than 6 years in mobile applications and is expected to grow in the future. MCP is already used in all the low-end smartphones and will be adopted by 50% of the high-end smartphones by 2026.

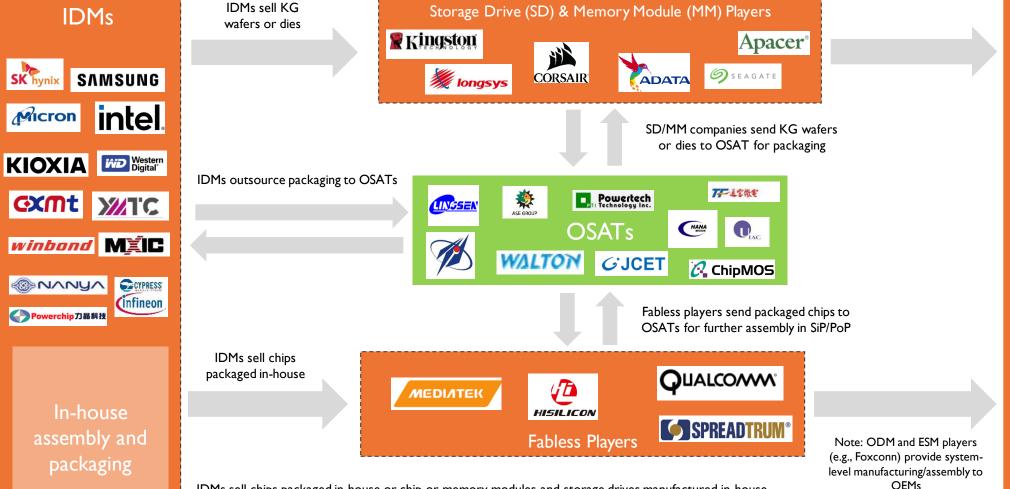

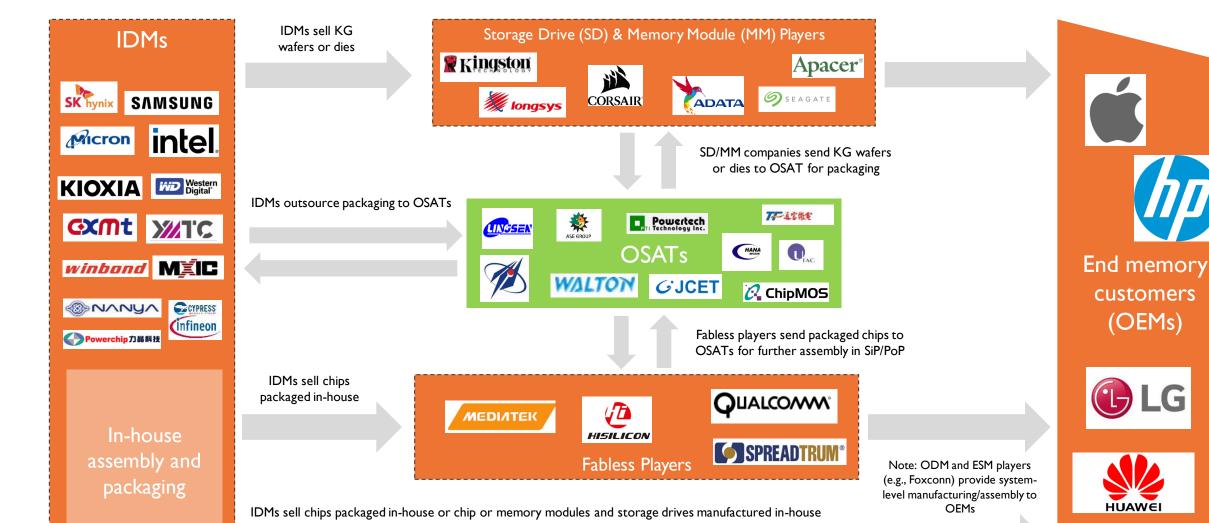

## SUPPLY CHAIN - BUSINESS MODEL OF MEMORY OSATs

IDMs sell chips packaged in-house or chip or memory modules and storage drives manufactured in-house

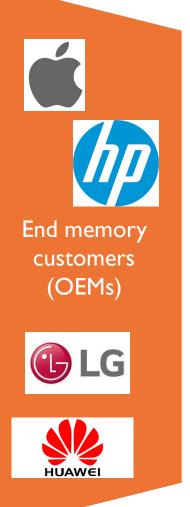

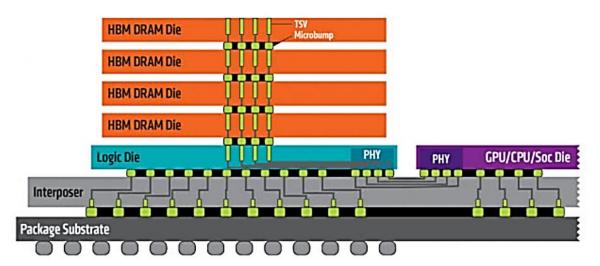

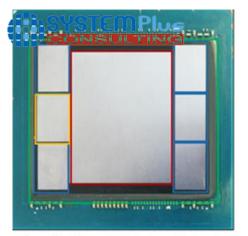

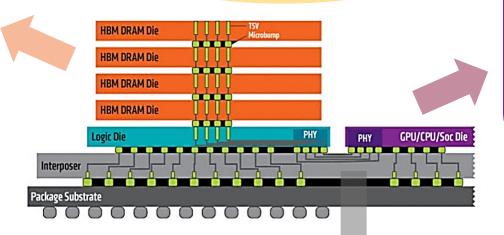

## MANUFACTURING OF (x)PUs WITH HBM – SUPPLY CHAIN

## SAMSUNG

Including TSV formation, wafer bumping and stacking of the DRAM dies and the logic die

#### Focus of this report

The ASP of HBM includes the DRAM/logic wafer middle-end manufacturing (TVS and microbumping)

**GPU/CPU Suppliers**

Assembly of HBM stack and CPU/GPU on interposer and final packaging

#### MEMORY PACKAGING PLAYERS – IDMs AND OSATs

#### IDMs with in-house packaging

Rising IDMs with no in-house packaging

intel

**SAMSUNG**

Non-exhaustive list

#### **Partial Outsourcing**

IDMs have their own internal packaging capability, but they can also outsource packaging to optimize their productivity or to comply with specific customers' requirements.

#### **Full Outsourcing**

Chinese memory IDMs do not have inhouse packaging capability → Huge business opportunity for Chinese OSATs.

#### **OSATs**

Non-exhaustive list

#### Chinese OSATs

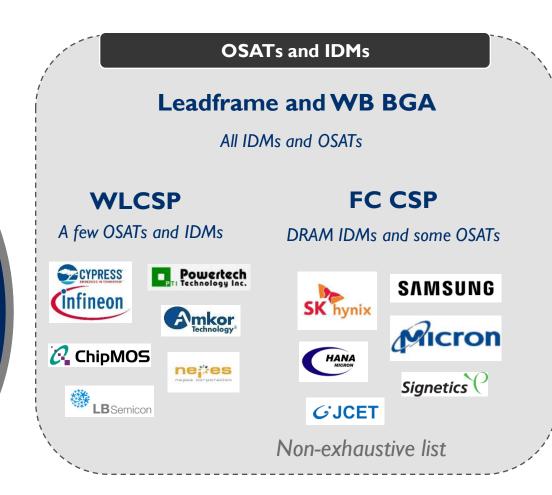

## MEMORY PACKAGING PLAYERS – OSATS BY TYPE OF PACKAGE

| J |   |   |

|---|---|---|

|   | ٦ | ľ |

|   |   |   |

|   |   |   |

| OSAT                                | (Country) | Flip-Chip | WB BGA   | WLCSP    | eMMC / MCP | Leadframe |

|-------------------------------------|-----------|-----------|----------|----------|------------|-----------|

| ASE GROUP                           | (Taiwan)  | ✓         | ✓        | ✓        | ✓          | ✓         |

| Emkor<br>Technology®                | (USA)     | ✓         | ✓        | <b>✓</b> | ✓          | ✓         |

| <b> ⊘</b> JCET                      | (China)   | ✓         | ✓        | ✓        |            | ✓         |

| Powertech                           | (Taiwan)  | ✓         | <b>✓</b> | ✓        | ✓          | <b>✓</b>  |

| 74-道宫檄電                             | (China)   | ✓         | ✓        |          | ✓          | ✓         |

| 华天科技                                | (China)   | ✓         | ✓        |          | ✓          | ✓         |

| KYEC The Testing Industry Benchmark | (Taiwan)  |           | ✓        |          | ✓          | ✓         |

| 🤼 ChipMOS                           | (Taiwan)  |           | ✓        | ✓        | ✓          | ✓         |

| <b>W</b> 聯測科技                       | (Taiwan)  | ✓         | ✓        |          |            | ✓         |

| HANA                                | (Taiwan)  | ✓         | ✓        |          | ✓          | <b>✓</b>  |

#### KEY PARTNERSHIPS BETWEEN OSATS AND MEMORY CHIP MANUFACTURERS

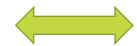

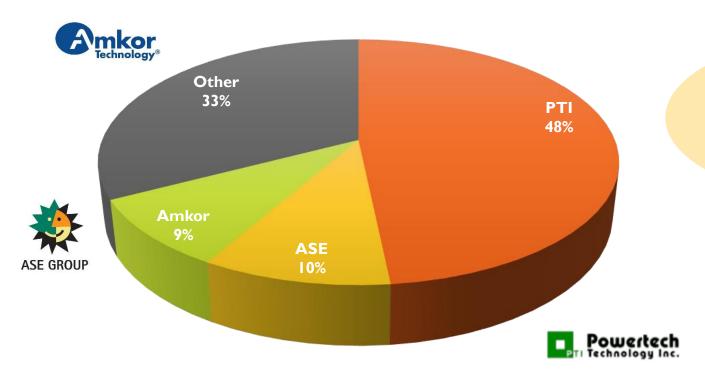

**Powertech Technology (PTI)** is the largest memory chip packaging and testing service provider, with over 60% of its revenue generated from the memory chip sector.

- Micron is PTI's main commercial partner, particularly for DRAM chips. We estimate that ~50% of PTI's production came from Micron.

- Micron transferred part of its packaging production to its Taiwanese facilities and has initiated new packaging activities for leading edge technologies such as HMC/HBM, based on die-to-die and TSVs.

- Micron and PTI have been working together for a long time. In 2016, they started a joint fab in Xi'an (China) for testing and assembling memory chips that enter volume production. In April 2017, Micron and PTI signed an agreement for the acquisition of Micron Akita, a test/assembly company based in Japan.

- **Amkor Technology** and **Kioxia** are commercial partners for packaging of 3D NAND memory chips.

- The partnership between the two companies has a long history. In 2015, Amkor acquired J-Devices, which is the largest OSAT in Japan and is now operating as an Amkor subsidiary. J-Devices was formed back in 2009 as a joint venture between Toshiba Corp., Nakaya Microdevices (NMD) and Amkor → 60% owned by NMD, 30% by Amkor and 10% by Toshiba (Kioxia).

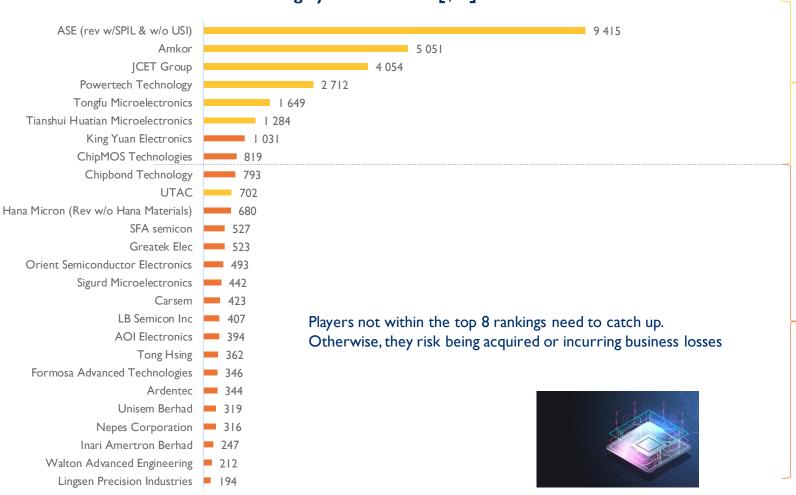

#### MEMORY PACKAGING PLAYERS – OSATS

Powertech (PTI) is the market leader in memory

PTI's main business is DRAM packaging for Micron.

packaging.

# Memory Packaging Market for OSATs Market Shares (%)

Total Memory Packaging Market for OSATs in 2020 ~ \$4.2B

#### MEMORY PACKAGING PLAYERS – IDMs AND OSATs

## IDMs' vs OSATs' memory packaging revenue in 2020

IDMs are doing most of their memory packaging inhouse. We estimate that less than 1/4 of the memory packaging market is currently generated by OSATS.

Total Memory Packaging Market in 2020~ \$13.1B

OSATs' packaging business (without testing) ~\$4.2B

- Korean IDMs (Samsung and SK hynix) are doing more than 70% of their packaging in-house.

- American IDMs (Intel, Micron, WD, Cypress-Infineon) are outsourcing around 50-60% of their packaging to OSATs.

- Chinese IDMs (CXMT and YMTC) are outsourcing all their packaging because they didn't have in-house packaging.

## IDMs' RATIONALES FOR (NOT) OUTSOURCING MEMORY PACKAGING

#### Why memory IDMs prefer to carry out memory packaging internally?

- There are multiple reasons why IDMs prefer to be independent and not rely on third parties for memory packaging:

- The price/cost of memory packaging is under control

- The risks of supply-chain constraints and time delays are lower

- Supply chain management and logistics are easier (no need for shipping back and forth memory wafers, dies or packages)

- Quality controls are carried out in-situ based on internal standards

- Electrical testing procedures are carried out according to specific internal protocols

- OSATs do not have extensive know-how and experience on advanced memory, which is necessary for efficient packaging/testing

of devices such as flip-chip DRAM, HBM and 3DS DRAM

#### Why memory IDMs outsource memory packaging?

- The main reason why IDMs decide to outsource memory packaging is to reduce pressure on their back-end manufacturing lines and

overcome their capacity limitations. Note: Certain IDMs could give priority to the internal packaging of non-memory IC products.

- A large fraction of the memory packaging volume relies on conventional approaches such as wirebond or leadframe that are well mastered by OSATs with good yields and high throughputs.

- OSATs are often located in countries where the manufacturing cost is low, so their pricing can be competitive.

#### MEMORY PACKAGING REVENUE – IDMs VERSUS OSATs

## Estimated evolution of revenues by OSAT and IDM

Two opposing trends are influencing the memory-packaging business carried out by OSATs:

OSAT \$ 1

Chinese players – YMTC and CXMT – are ramping up their memory capacity boosting memory outsourcing demands at OSATs.

OSAT \$↓

Following Samsung and SK hynix, Micron has started the conversion of DRAM packaging from wire-bond to flip-chip increasing its internal back-end capacity. This implies less outsourcing to OSATs, particularly to its major packaging partner PTI.

#### Memory Packaging Market - IDM vs OSAT Breakdown

Note: testing is not included. See Market Forecast Chapter for more details on the overall memory-packaging market evolution.

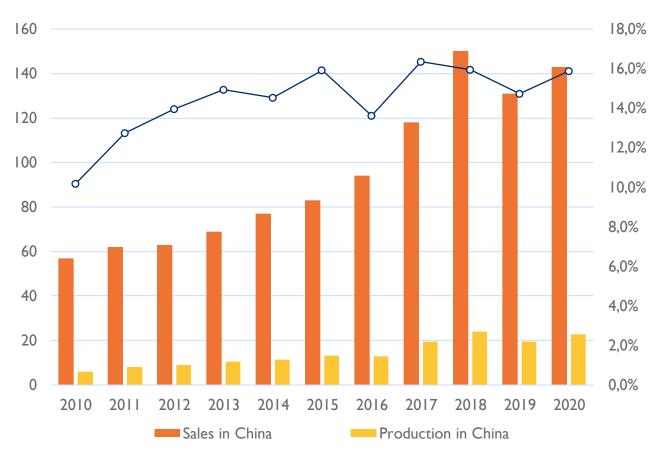

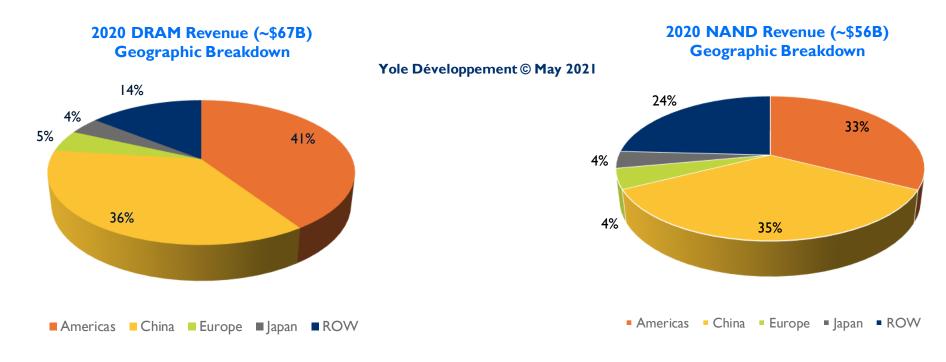

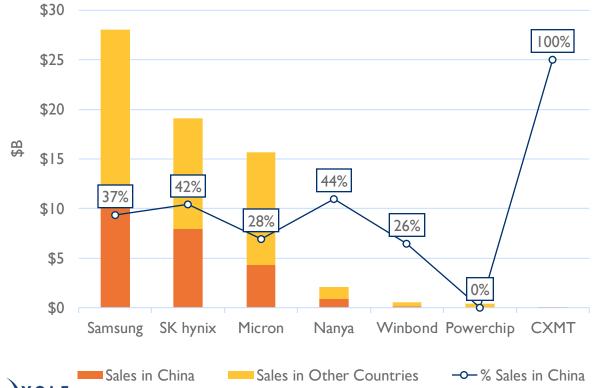

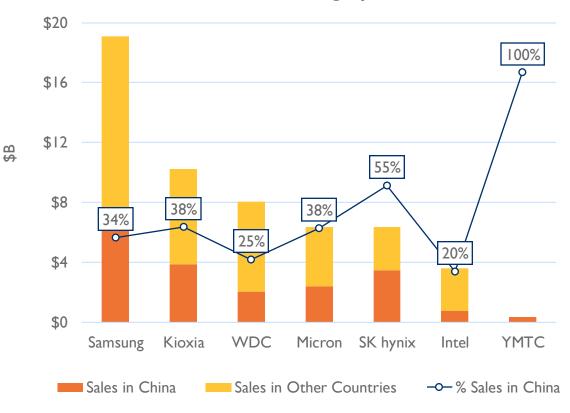

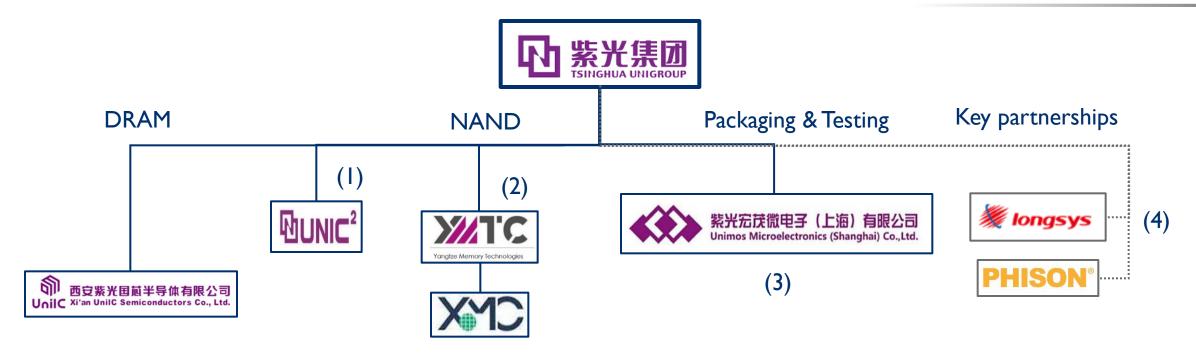

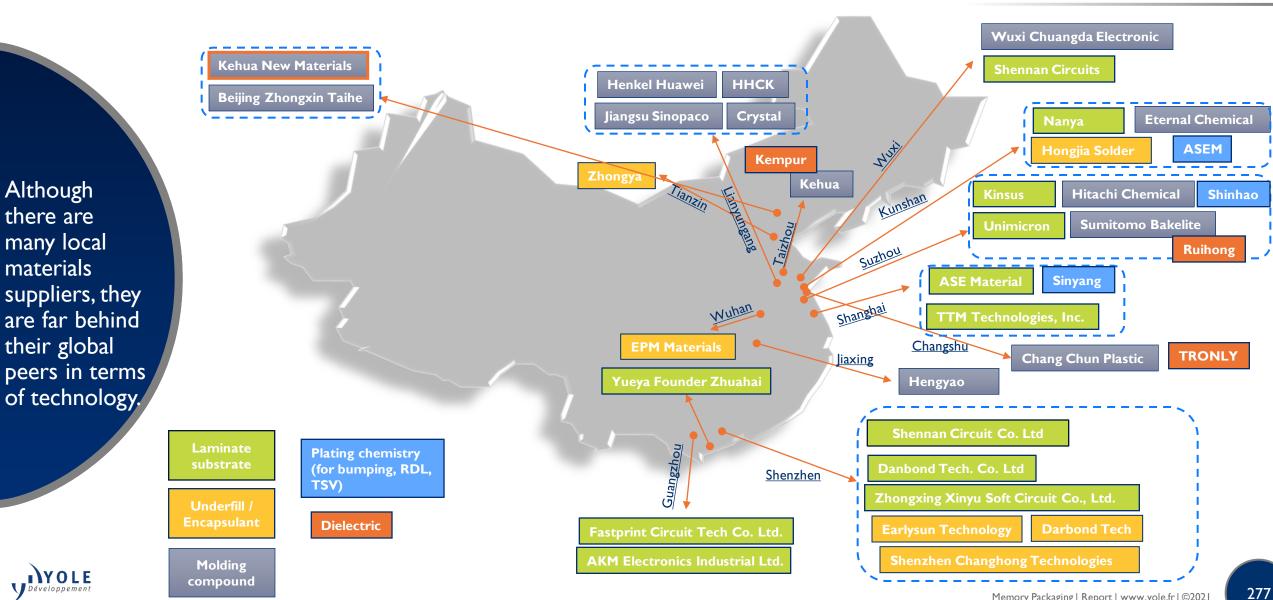

## CHINA'S MEMORY BUSINESS – SUMMARY

- The DRAM and NAND flash memory markets together accounted for more than 30% of China's total IC market. The high level of memory consumption in China is helping fuel the country's burning desire to increase the domestic production of both DRAM and NAND flash devices.

- NAND: YMTC is the leading memory maker in China (NAND). The company is currently shipping 64L NAND in low volumes domestically (including SSDs), with 128L production under development (shipments expected in 2021). YMTC's 2020 ramp-up has been hampered by Covid-19, with delays in equipment deliveries/installations at its Wuhan manufacturing site.

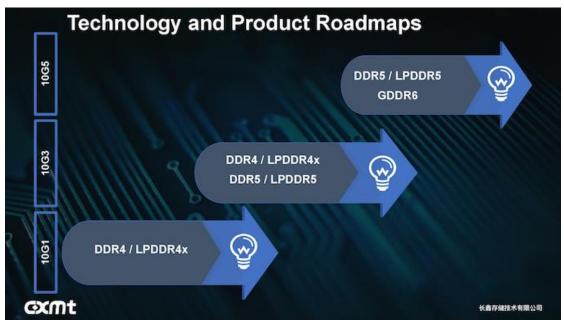

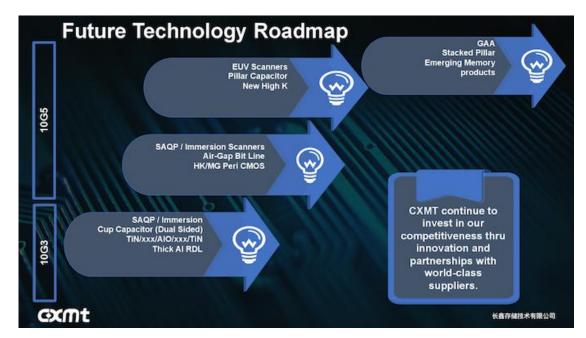

- DRAM: CXMT is currently the leading DRAM maker in China. Initial production won't be broadly available in the market. Broad commercialization is planned with Gen 3 products after skipping Gen 2. Jinhua IC was significantly handicapped by the US sanctions and faces significant/insurmountable challenges. Tsinghua Unigroup follows behind CXMT and continues to be a contender.

- Semiconductor packaging: China's IC packaging & testing industry maintained its strong growth, growing at 7% YoY to ~ \$38B (250.95 billion Yuan) in 2020. In 2H 2021, it grew by 7.6% YoY, with sales of ~\$18B (116.47 billion Yuan).

- Memory Packaging in China is a key business opportunity for OSATs: The two rising memory players in China YMTC and CXMT do not have experience in assembly/packaging and must outsource all their packaging to OSATs.

- YMTC and CXMT are rapidly ramping up their wafer production. We assume that by 2026 YMTC could achieve ~12% of the overall NAND industry wafer production, while CXMT could achieve ~4% of the DRAM industry production. Based on this assumption, we estimate that OSATs' business opportunity related to Chinese memory players can grow from <\$100M in 2020 to ~\$1.1B in 2026 (CAGR<sub>20-26</sub> ~55%)

- Chinese OSATs will be the first to take this opportunity. The three major players in China (JCET, Tongfu and HT Tech) have already started developing memory packaging for the two Chinese memory leaders. Note: MCPs for Chinese-brand smartphones (low-to-mid range) are being regarded by Chinese OSATs as a key application driving the growth.

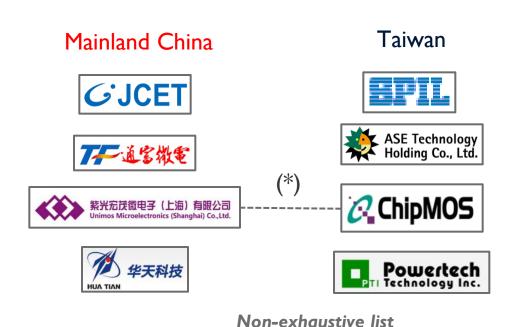

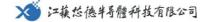

#### CHINA'S MEMORY PACKAGING LANDSCAPE

## IDMs and OSATs involved in Memory Packaging

#### CHINA'S MEMORY PACKAGING BUSINESS

The Chinese memory market is a good opportunity for OSATs

The overall memory packaging market is dominated by IDMs, with more than \(^3\)4 of the business. Global memory IDMs have huge experience in packaging and have their own large internal capacity. However, the new memory players in China do not have much experience in assembly/packaging and must outsource packaging to OSATs.

#### Where is the opportunity?

Many new players entering the Chinese memory business and looking for OSATs

(\*) Unimos Microelectronics was renamed in July 2018 from ChipMOS (Shanghai), originally a wholly-owned subsidiary of Taiwan's ChipMOS Technologies, after Tsinghua Unigroup acquired a 48% stake to become its largest shareholder. The company started construction of brand-new 3D NAND back-end service lines in April 2018.

Compared to other semiconductor sectors, China's OSAT technology has a much narrower technology gap vis-a-vis the leading countries. Chinese OSATs can support nearly all the common packages.

## ESTIMATE OF THE MEMORY PACKAGING OPPORTUNITY IN CHINA

YMTC and CXMT will be generating a >\$1B opportunity for OSATS by 2026

Note: Yole estimates that by 2026 YMTC could supply ~12% of the NAND wafers globally, while CXMT could supply ~4% of the DRAMs.

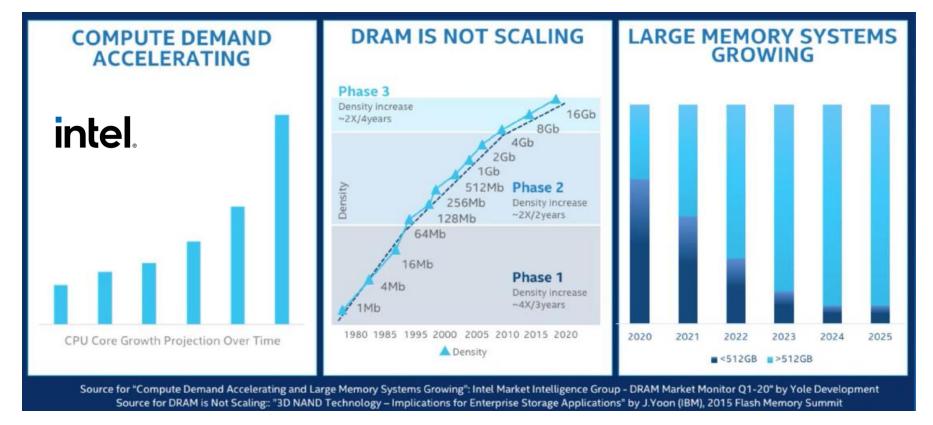

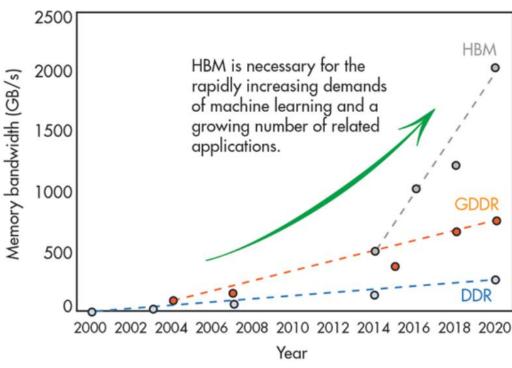

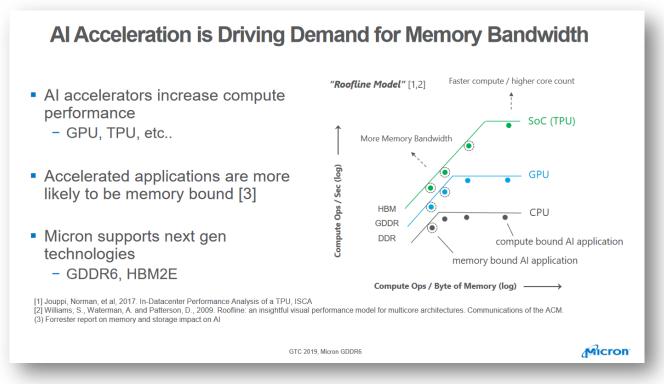

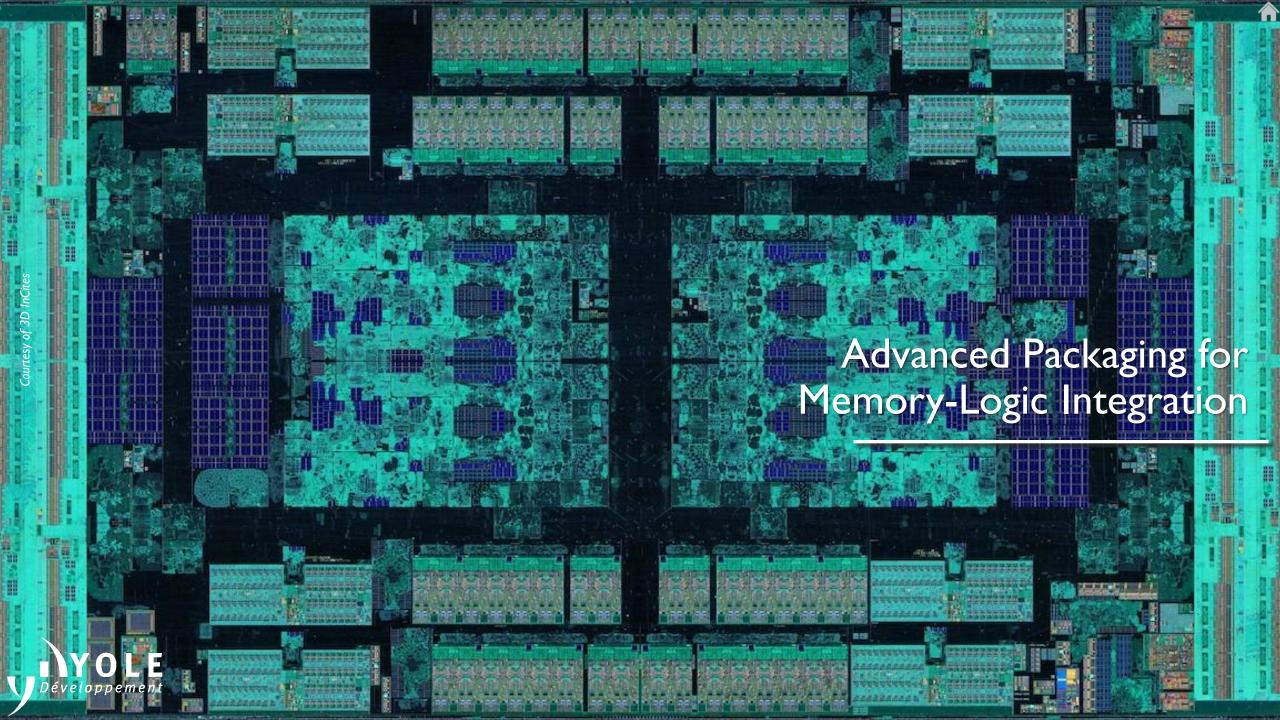

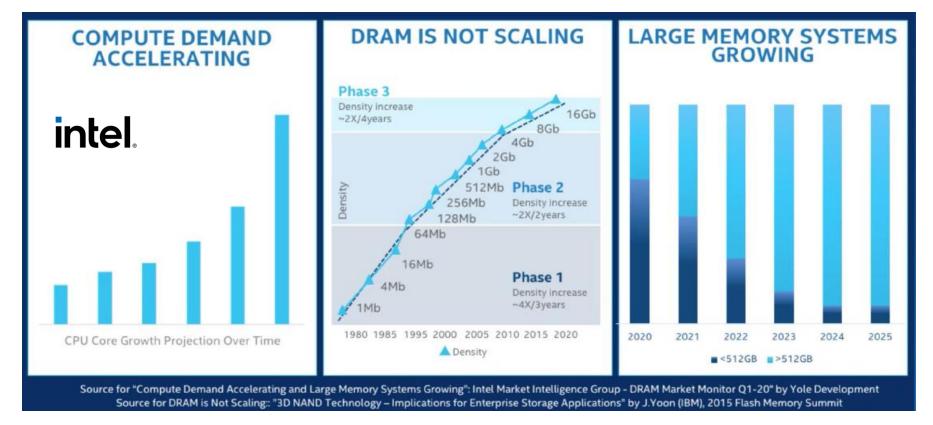

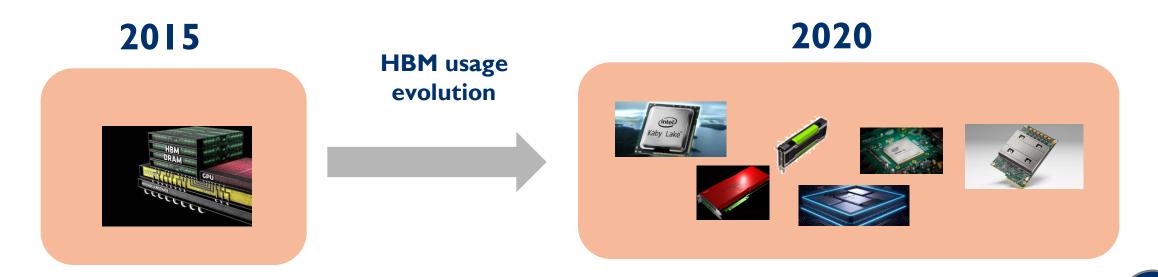

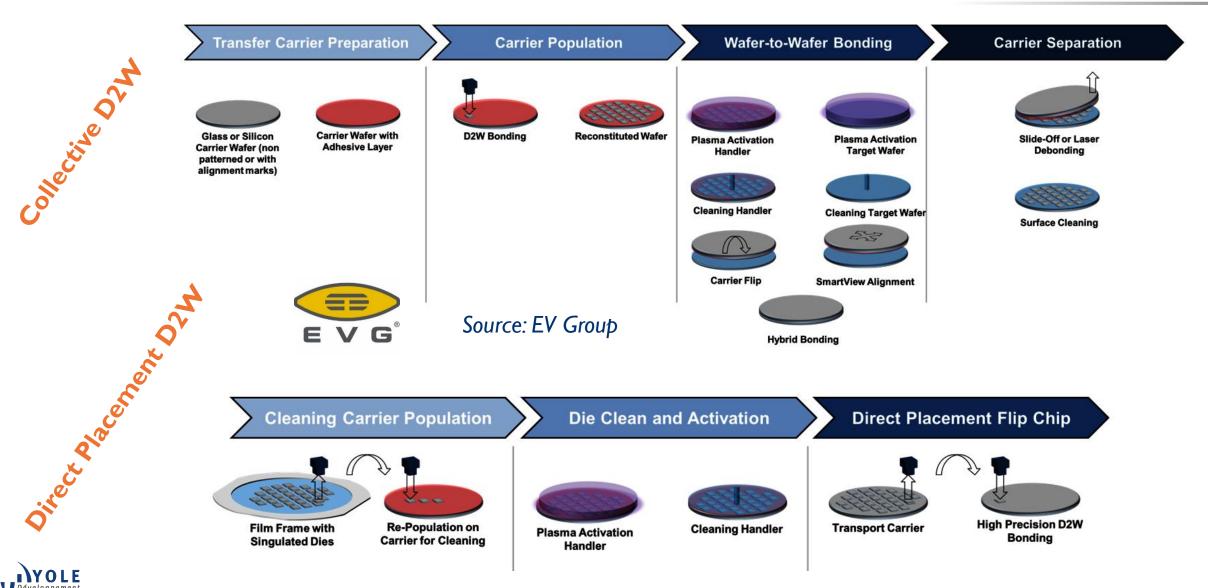

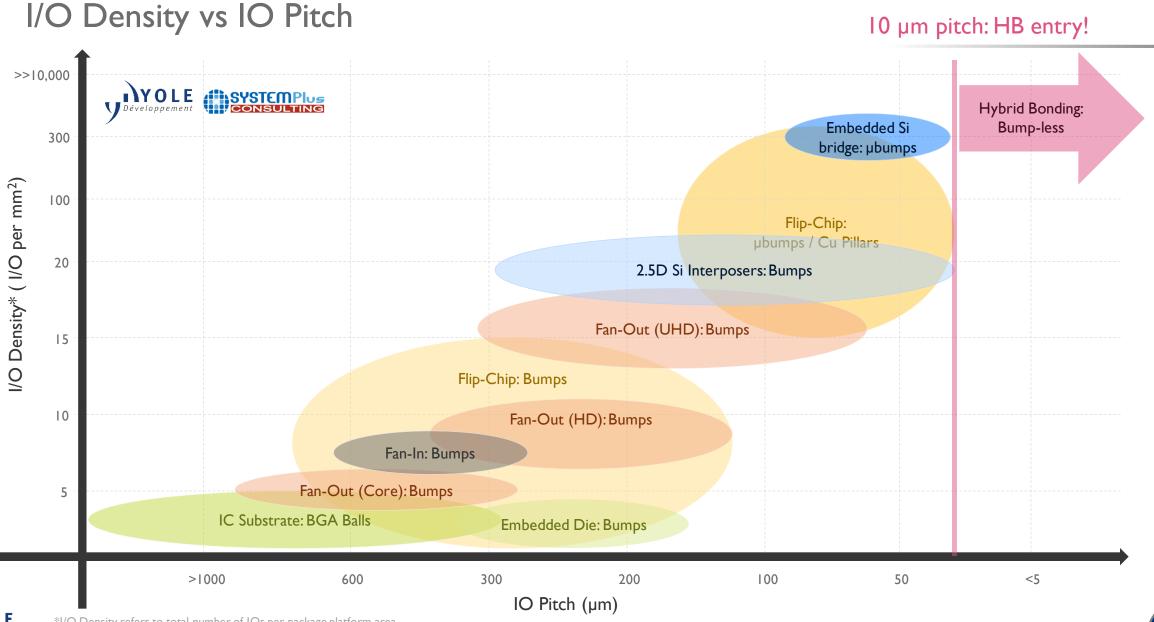

#### THE TECHNOLOGY LANDSCAPE IS CHANGING

## Memory struggles to keep pace with the fast-growing data generation and computing demand

- System performance is often limited by the data transfer rate between processors and memory ("Memory Bottleneck"). New devices and system architectures are needed to deal with ever growing amounts of data.

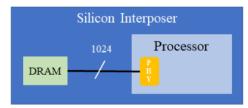

- In this context, advanced packaging techniques such as TSV stacking (HBM) and hybrid bonding (chiplets) are becoming the preferred solutions to continue boosting system performance.

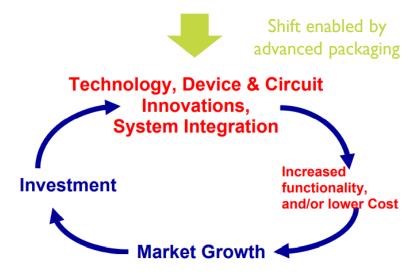

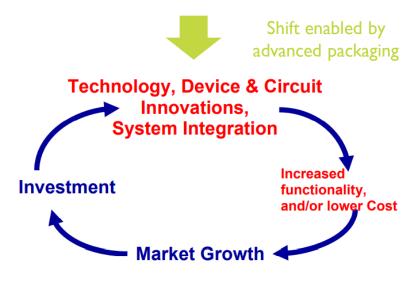

## A PARADIGM SHIFT IN THE ROLE OF SEMICONDUCTOR PACKAGING

Back-end processing has become a primary focus area for improving the performance of computing systems

- Since the first days of Moore's Law in the 1960s, continuous progress in semiconductor devices was made possible by shrinking the size of transistors to augment their operating frequency and their density per unit area. Therefore, front-end manufacturing has always been regarded as the key area to work on to increase the performance of computing systems.

- On the other hand, back-end processing has for long been considered an "afterthought", serving only to protect the die and connect it to the outside world. However, since the last decade, the perception of the role of packaging has dramatically changed.

- With the <u>slowdown of Moore's Law</u> and <u>the rise of new advanced packaging techniques</u> such as flip-chip, TSV stacking, hybrid bonding, fan-out, and more (see Yole's 2021 report on the "Status of the Advanced Packaging Industry" for a detailed overview) back-end processing has gained more and more importance. Therefore, several semiconductor companies are now leveraging it to improve the performance, compactness, and number of functionalities of their IC products.

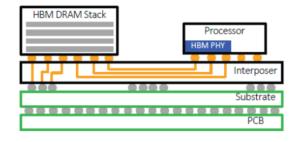

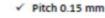

- This paradigm shift is happening in multiple semiconductor areas, spanning from imaging to memory and computing devices. Heterogeneous integration techniques are used today to address the "memory wall" problem by bringing memory and computing units close to each other *via* 3D stacking approaches (e.g., TSV for HBM and hybrid bonding for chiplets).

- For instance, the move from conventional packaging to flip-chip or TSV stacking in memory enabled improved performance of DRAM devices, achieving higher bandwidth with shorter interconnections and higher I/O density.

Semiconductor economic cycle based on front-end scaling

Semiconductor economic cycle based on new integration approaches

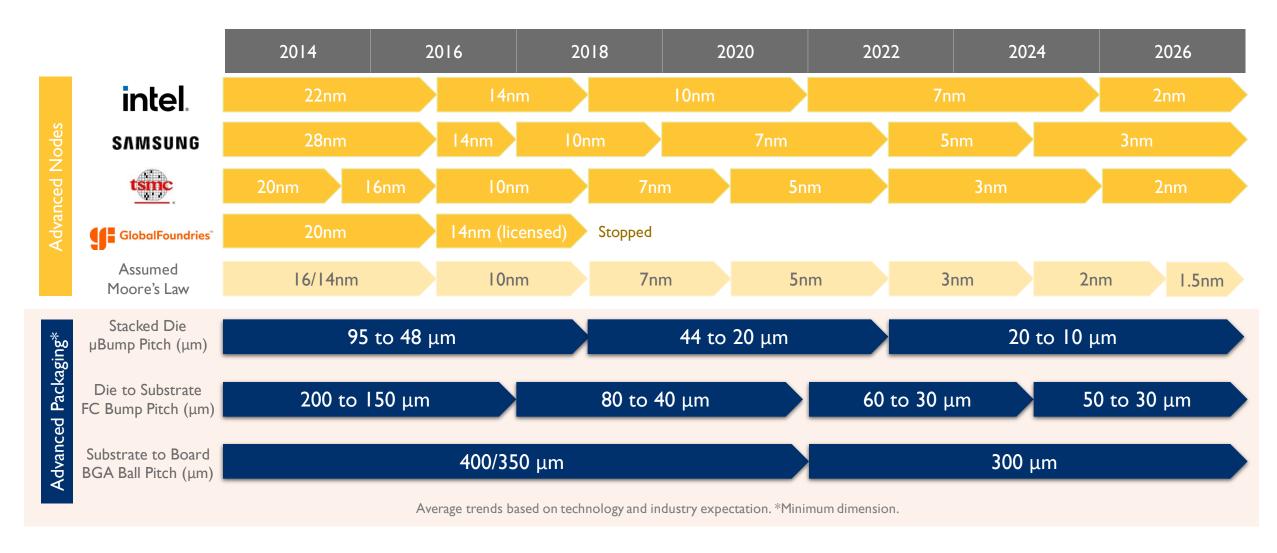

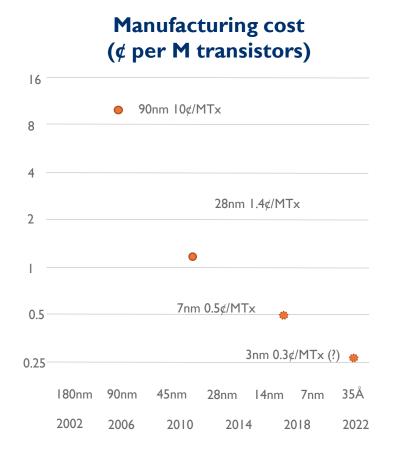

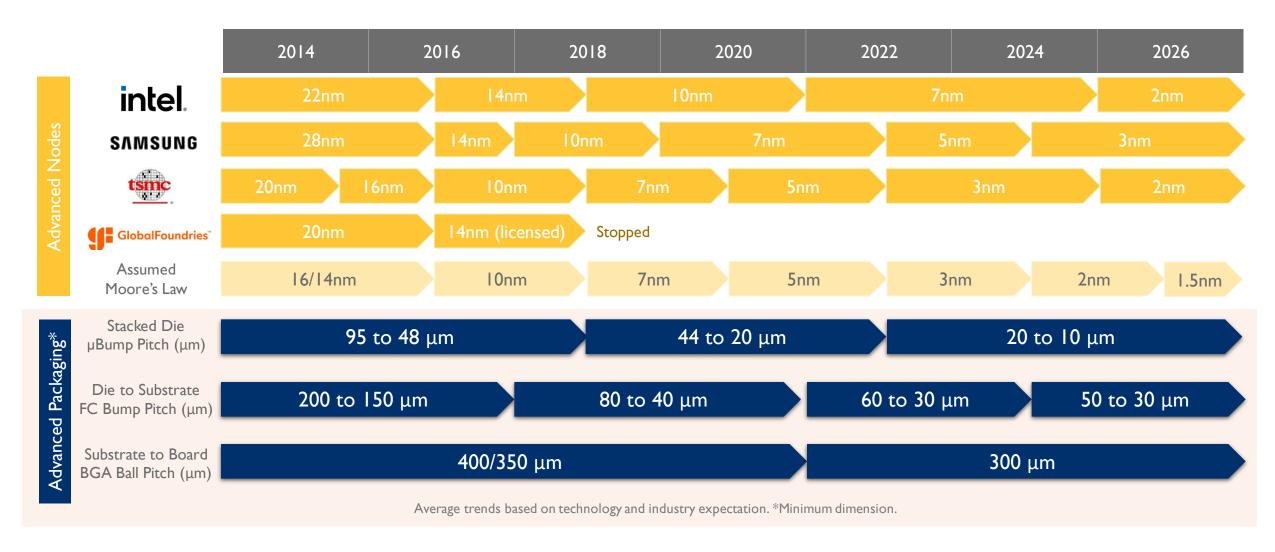

## TECHNOLOGY ROADMAP — FRONT-END MANUFACTURING VS ADVANCED PACKAGING

- In the coming years, technology scaling in the field of advanced packaging (AP) can continue at a faster pace compared to front-end (FE) manufacturing.

- AP enables continuous performance growth in computing systems through the tighter integration of memory and logic. Examples: high-bandwidth memory mounted over GPUs/CPUs and 3D heterogeneous integration techniques for chiplets.

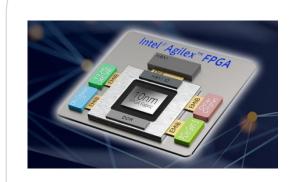

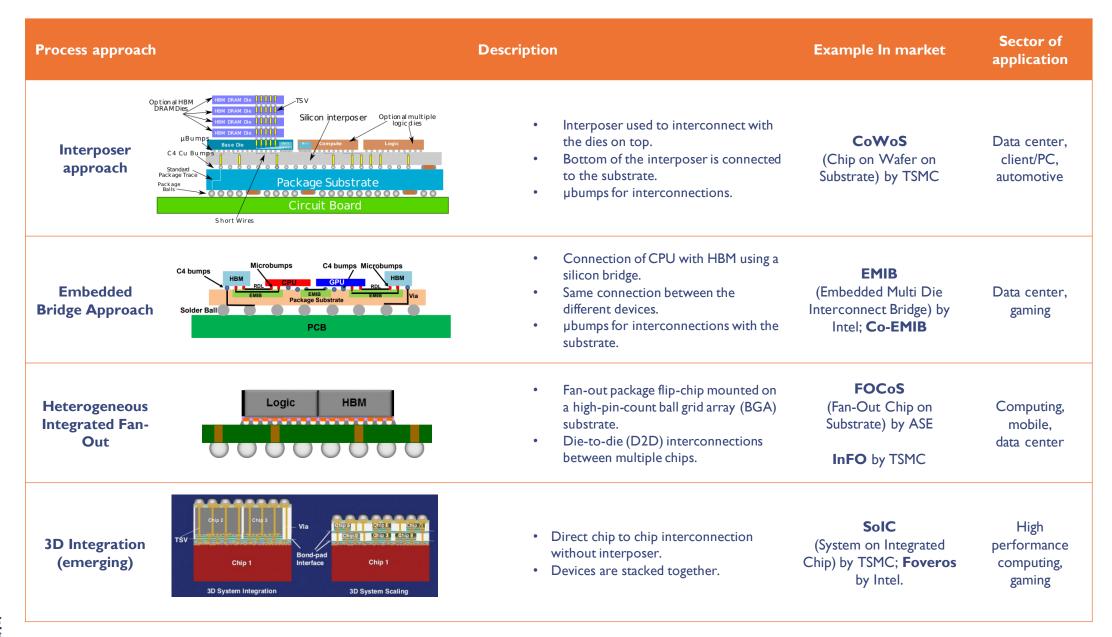

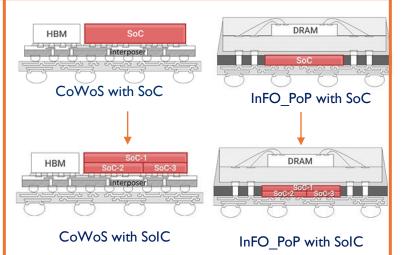

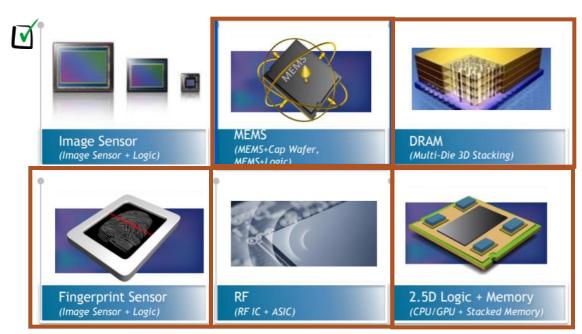

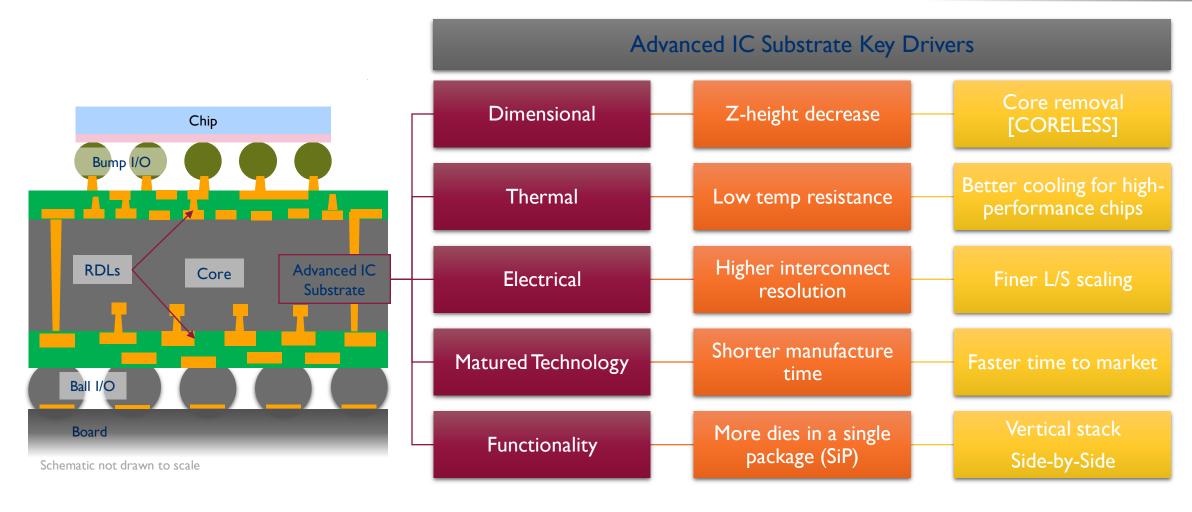

## ADVANCED PACKAGING FOR MEMORY-LOGIC INTEGRATION

| Process approach                    | Desc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Example                                                                                                                                                                                 | Applications                                                    |                                          |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------|

| Interposer<br>approach              | Optional HBM DRAM DIS Silicon interposer Optional multiple logic dies HBM DRAM DIS Silicon interposer Optional multiple logic dies HBM DRAM DIS SIlicon interposer Optional multiple logic dies HBM DRAM DIS SIlicon interposer Optional multiple logic dies HBM DRAM DIS SIlicon interposer Optional multiple logic dies HBM DRAM DIS SILICON INTERPOSE OPTIONAL DIS SILICON INTERP | <ul> <li>Interposer used to interconnect with the dies on top.</li> <li>Bottom of the interposer is connected to the substrate.</li> <li>µbumps for interconnections.</li> </ul>        | CoWoS<br>(Chip on Wafer on<br>Substrate) by TSMC                | Data center,<br>client/PC,<br>automotive |

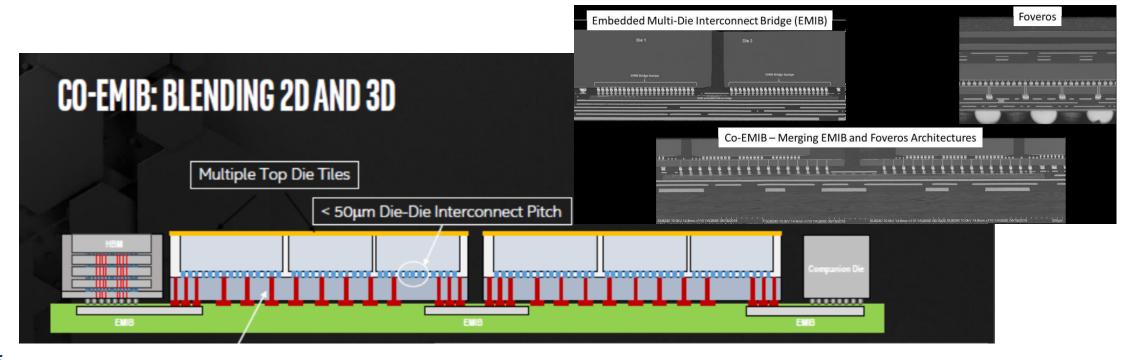

| Embedded Bridge<br>approach         | C4 bumps Microbumps C4 bumps Microbumps HBM RDL CPU G2U RDL HBM Package Substrate  PCB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>Connection of CPU with HBM using a silicon bridge.</li> <li>Same connection between the different devices.</li> <li>µbumps for interconnections with the substrate.</li> </ul> | EMIB (Embedded Multi Die Interconnect Bridge) by Intel; Co-EMIB | Data center,<br>gaming                   |

| Heterogeneous<br>Integrated Fan-out | Logic HBM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>Fan-out package flip-chip mounted on a high pin count ball grid array (BGA) substrate.</li> <li>Die-to-die (D2D) interconnections between multiple chips.</li> </ul>           | FOCoS (Fan-Out Chip on Substrate) by ASE InFO by TSMC           | Computing,<br>mobile,<br>data center     |

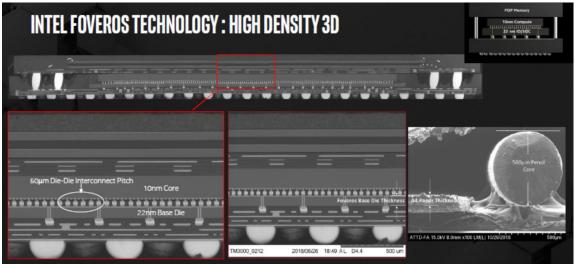

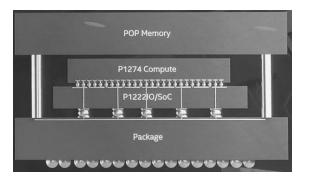

| 3D Integration<br>(emerging)        | Chip 2 Chip 3 Via Chip 2 Chip 2 Chip 2 Chip 2 Chip 2 Chip 3 Chip  | <ul> <li>Direct chip to chip interconnection without interposer.</li> <li>Devices are stacked together.</li> </ul>                                                                      | SolC (System on Integrated Chip) by TSMC; Foveros by Intel.     | High performance computing, gaming       |

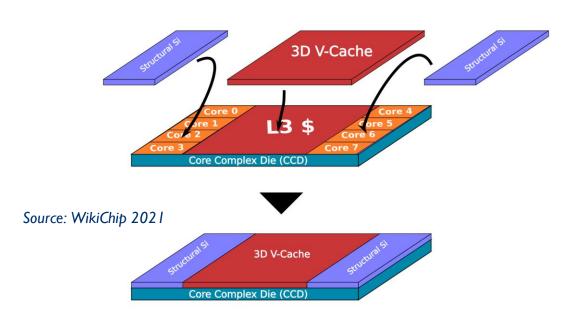

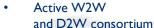

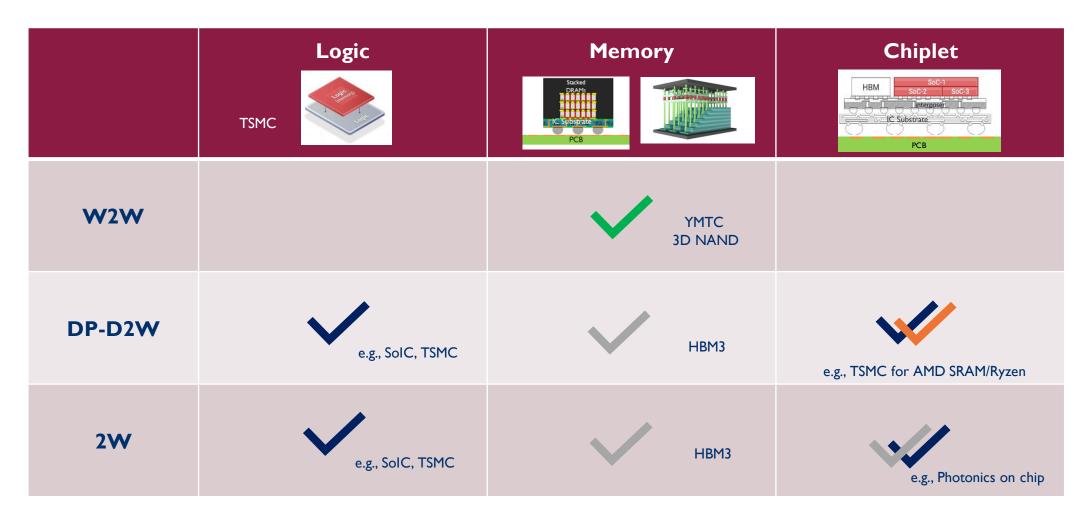

#### HYBRID BONDING – LOGIC & MEMORY APPLICATIONS

## Technology Roadmap

Logic

D2W with die attach **SRAM** on Ryzen

D<sub>2</sub>W used in SoIC  Foveros Omni: 35-40 µm pitch

Foveros Direct: <10 um</li>

Note: (2) The use of hybrid bonding for HBM is challenging. DRAM is particularly sensitive to temperature.

We expect that at least 4 more years of R&D by major players will be needed.

2026

2020

Memory

W2W

2022

Note: (1) Besides YMTC, we do not expect other NAND players to adopt Xtacking-like solutions before 2025, as they can compete with their CuA/CoP/PuC approaches.

2024

3DS<sub>o</sub>C **Memory D2W**

≥ HBM3 (50µm-thick die)

**D2W, D2D**

2020 2024 2026 2022

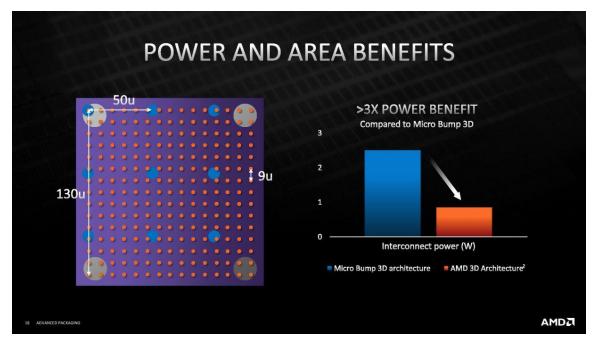

## HYBRID BONDING FOR HIGH-BANDWIDTH MEMORY (HBM)

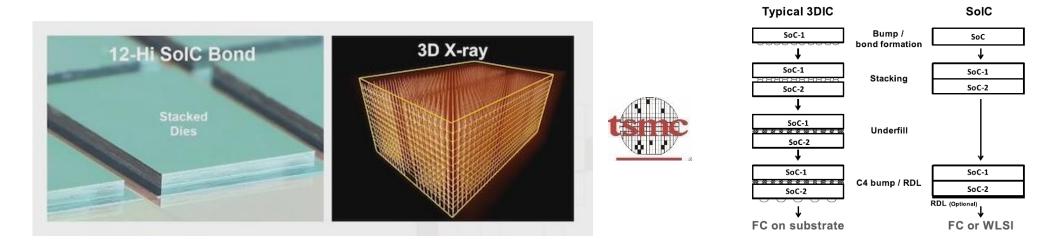

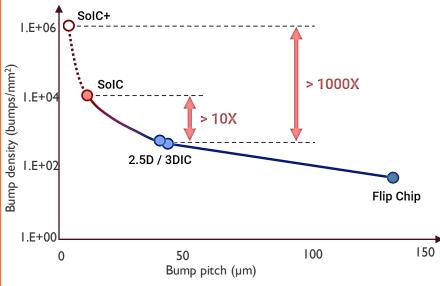

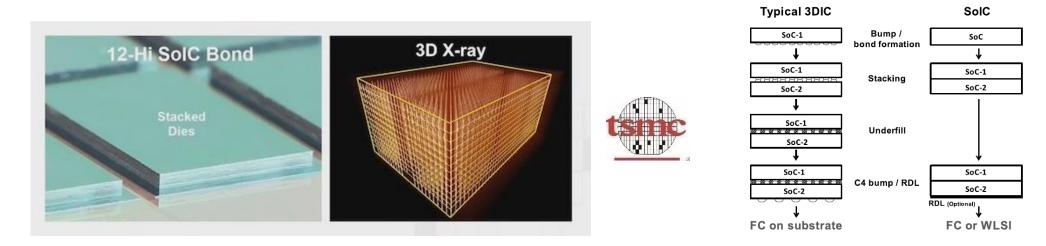

- Hybrid bonding is being considered as a potential approach for next-generation HBM, thanks to the higher bandwidth enabled by bumpless dieto-die contacts and smaller inter-die spacing.

- TSMC has developed a set of technologies called SoIC (System on Integrated Chip) that allows stacking silicon through direct bonding of metal layers (note: SoIC is TSMC's implementation of hybrid bonding).

- In the last few years, TSMC has been carrying out R&D activities on HBM devices based on different configurations of SolC, such as 12-Hi (i.e., stacks of 12 dies). The stack has a thickness <600µm, meaning that each die is <50µm thick.

- The hybrid-bond pitch is on the scale of 9µm for N7/N6 chips and 6µm for N5 chips. With this work, TSMC demonstrated it has wafer thinning, linear manufacturing, and alignment technologies suitable for building this next-generation of HBM devices.

- Although this is a truly promising demonstration, we believe that <u>hybrid bonding for HBM is not likely to appear before 2024</u>. Critical technical challenges such as thermal-budget management during manufacturing need to be further addressed to achieve yields suitable for high-volume manufacturing environments (note: DRAM's performance is easily degraded by heating).

Source: TSMCTechnology Symposium 2020. TSMC demonstrated 12 stacked dies with  $< 600 \mu m$  total thickness

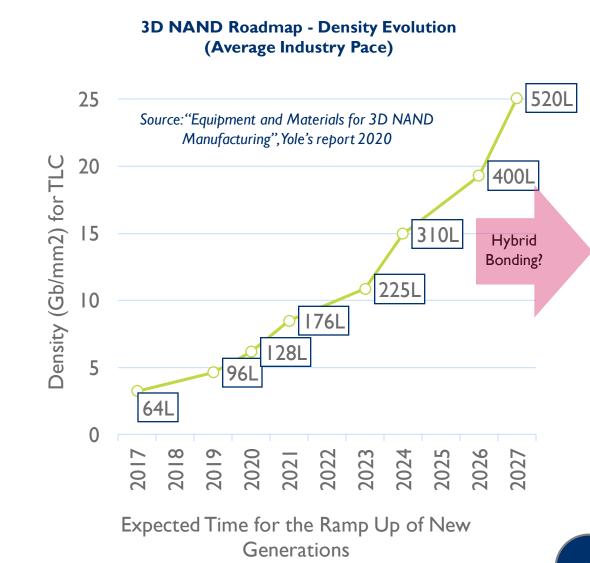

#### 3D NAND – WHICH OPPORTUNITY FOR HYBRID BONDING?

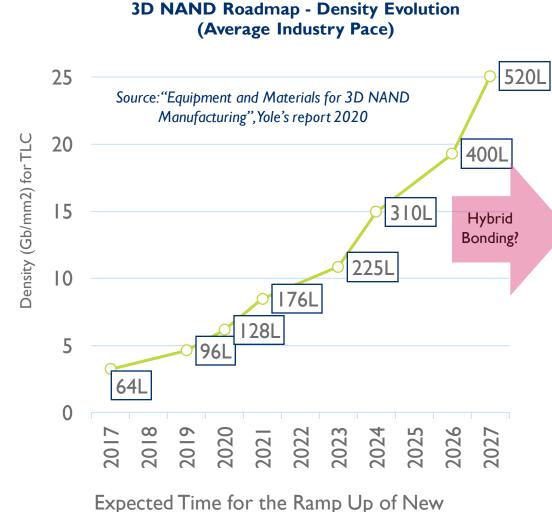

#### String-stacking and CuA/CoP/PuC approaches will enable continuous scaling at least until 400L

- In the next 5 years, 3D NAND players will continue to increase the layer count by leveraging high-aspect-ratio (HAR) etching tools and the string-stacking approach.

- From 2021, all the manufacturers will introduce in the market 3D-NAND technologies that rely on specific strategies for optimizing the logic circuit area and position, such as Periphery Under Cell (PUC, SK hynix), Core Over Periphery (COP, Samsung) or CMOS/Circuit Under Array (CUA, Micron and Intel, Kioxia and Western Digital), as well as Xtacking based on hybrid bonding (YMTC).

- The adoption of hybrid bonding by other players besides YMTC will not happen in the short term. We expect that NAND players will remain with their CUA/COP/PUC solutions for the next 4-5 years. Those solutions, in combination with string stacking, will enable continuous technology advancements until at least the 4xxL generation. Note: adopting a wafer-to-wafer logic-memory stacking approach implies a major conversion of the production lines (not straightforward for players that already have a large production capacity).

- Industry sources report that all memory manufacturers are doing R&D with hybrid bonding tools. Yole believes that hybrid bonding could have an opportunity for wafer-to-wafer stacking once string-stacking runs out of steam (likely after 4xxL) mainly due to cost/complexity barriers. In that case, hybrid bonding will be used for stacking multiple wafers containing NAND arrays, and possibly also the logic circuit.

#### STAND-ALONE MEMORY MARKET – OVERVIEW

- The stand-alone memory market is cyclical in nature, as it is characterized by periods of shortages and oversupply that give rise to strong price variations and revenue volatility.

- Memory is one of the primary market segments for semiconductor products. In 2020, combined NAND and DRAM revenues represented about 28% of the overall semiconductor market.

#### **Semiconductor and Memory Revenues (\$B)**

## Semiconductor and Memory Market Annual Growth Rates (%)

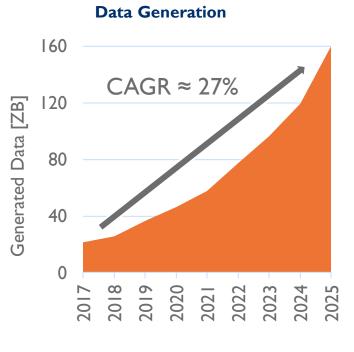

#### SEMICONDUCTOR MEMORY MARKET – DRIVERS AND MEGATRENDS

A variety of applications and trends are driving the "explosion of data"

Courtesy of Marvell Technology Group

- In today's data-centric societies, humans and machines are generating an impressive amount of data: by 2025, the number of bytes generated each year is expected to reach ~160 ZB (1 ZB =  $10^{21}$  B, or one trillion GB). The contribution of machines to data generation is expected to soon overtake that of humans and is expected to exceed 90% of all data generated by 2022.

- Memory is a critical market segment in modern data-centric societies and is driven by important megatrends, including mobility, cloud computing, artificial intelligence (AI), and the internet of things (IoT). The long-term demand, driven by these megatrends, will result in memory continuing to increase its share of the overall semiconductor market.

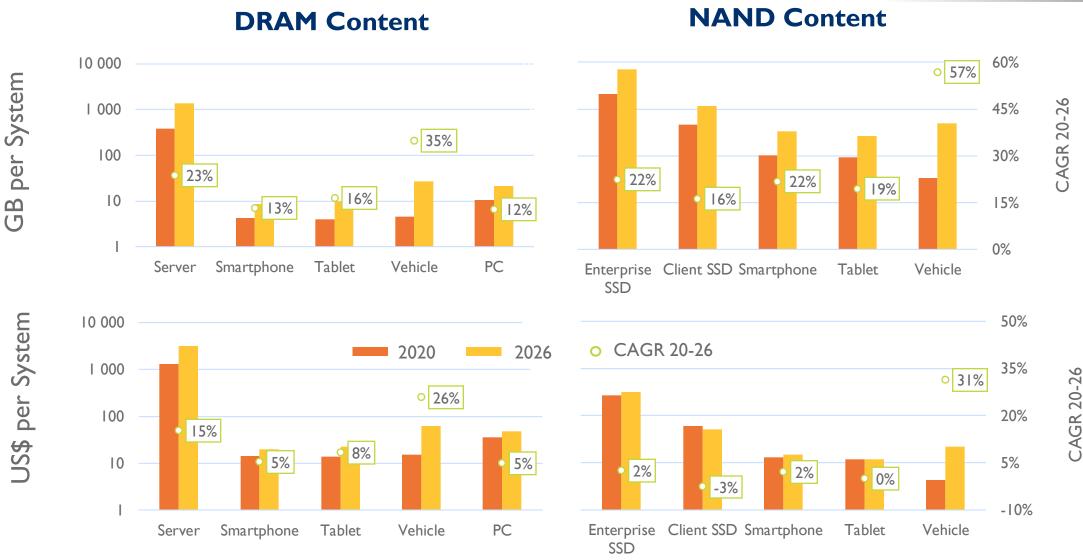

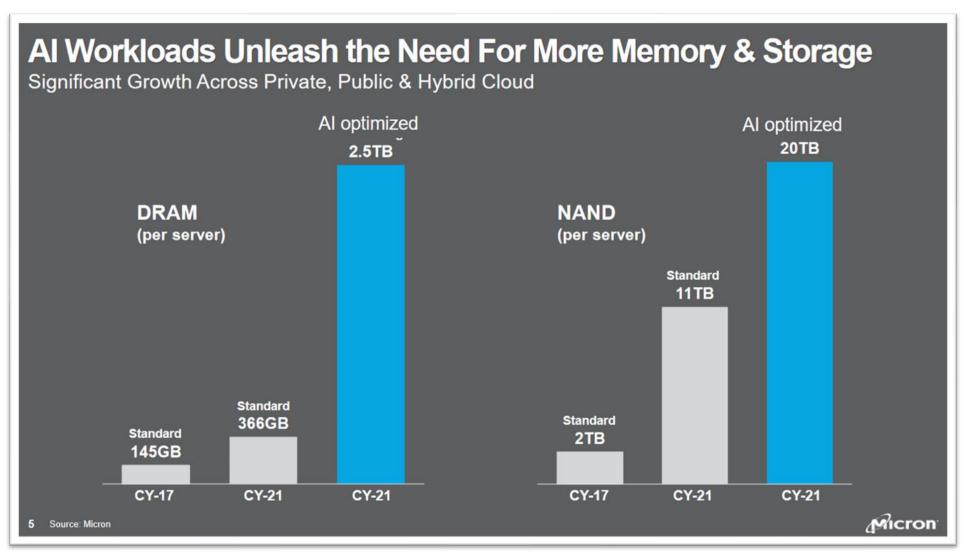

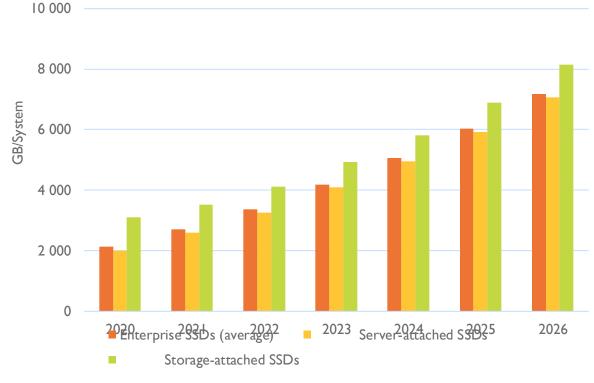

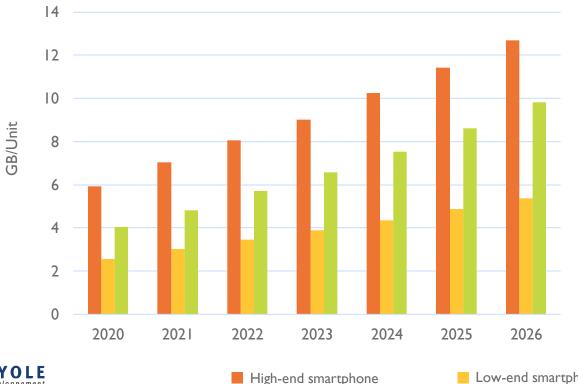

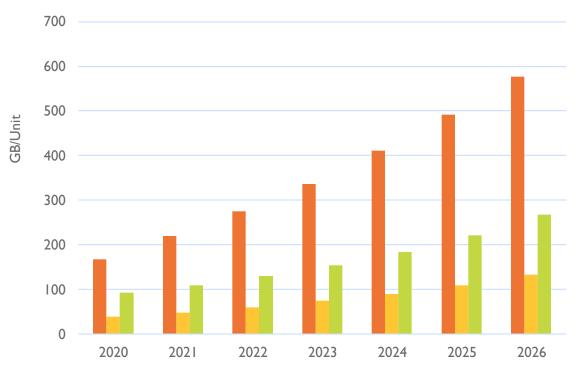

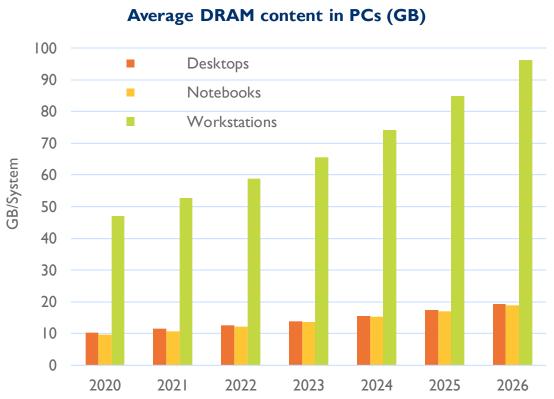

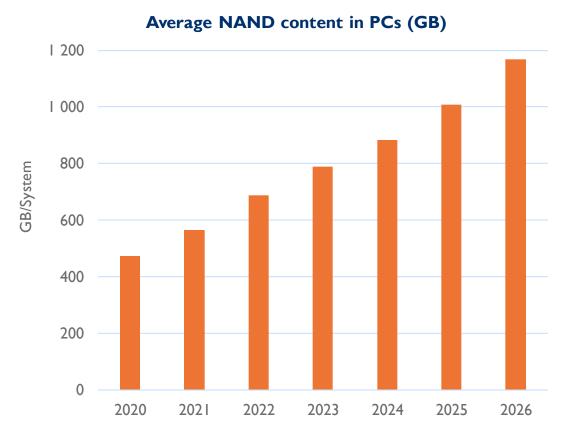

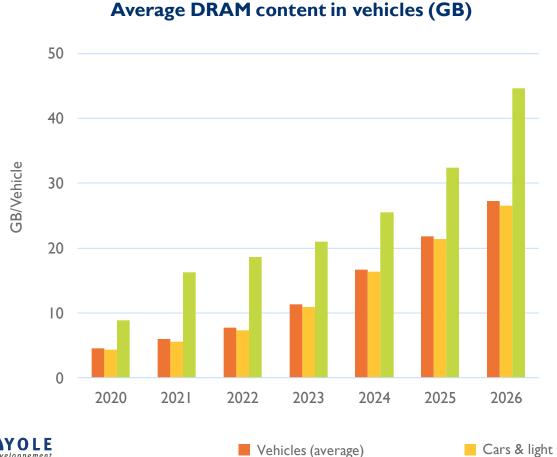

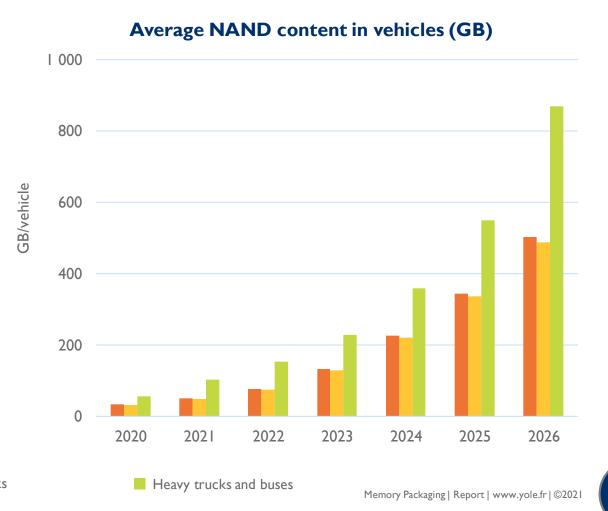

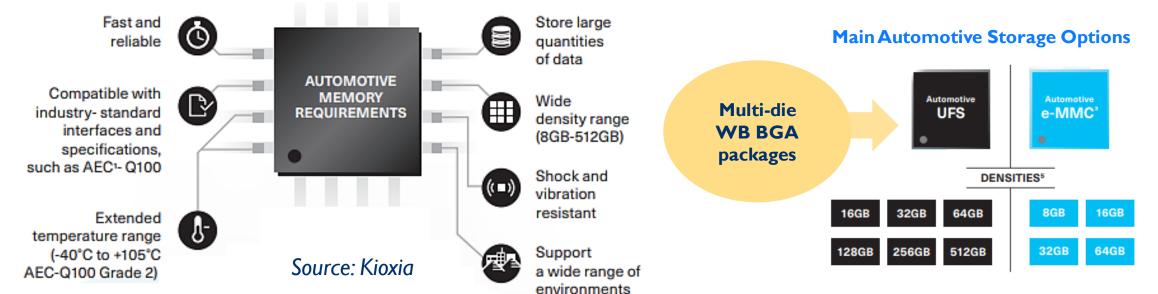

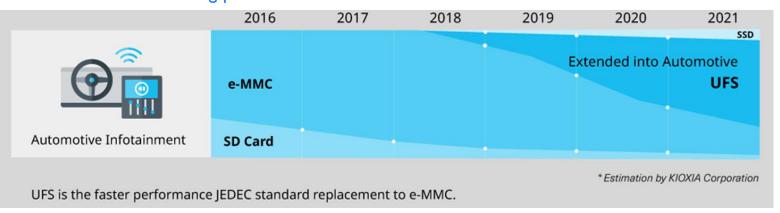

## MEMORY GROWTH FORECAST - A SYSTEMS POINT OF VIEW

Evolution of the average memory content for key end-systems from 2020 to 2026

## SEMICONDUCTOR MEMORY MARKET

## Main Market Trends

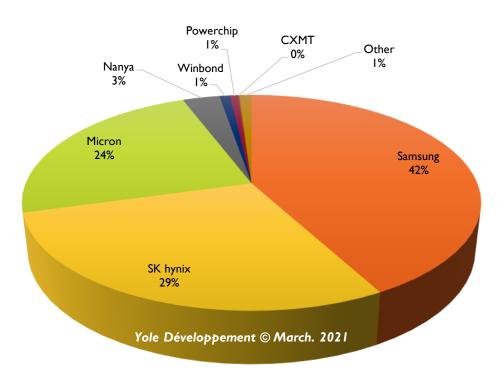

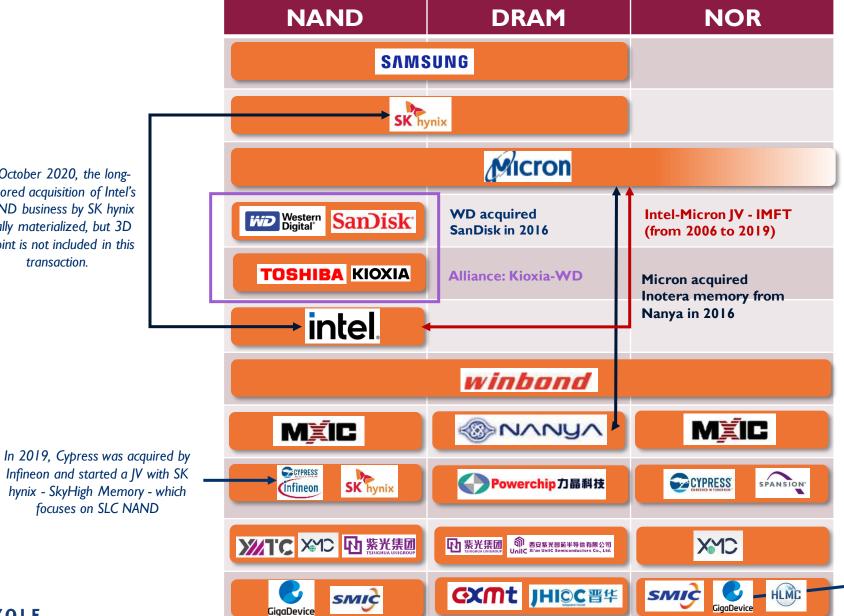

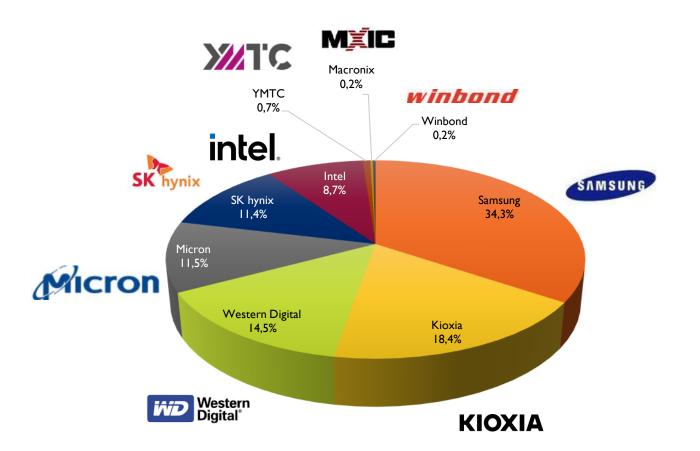

#### The stand-alone memory market is dominated by NAND and DRAM:

- NAND and DRAM markets are fueled by the growing need for memory in mobile devices (smartphone and tablet) and data centers (enterprise storage and server memory).

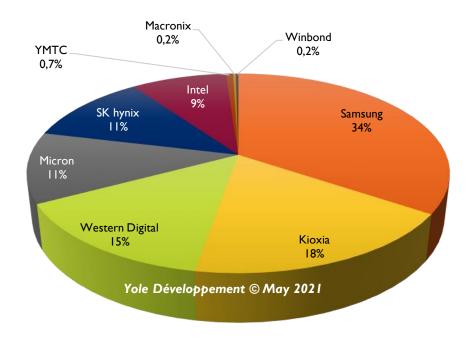

- Market concentration has accelerated in the last decade and is now very high, with six dominant players Samsung, Micron,

SK hynix (DRAM and NAND), Kioxia, Western Digital and Intel (NAND) holding a combined 96% of the market.

Chinese players could become a threat in the long-term.

- NAND and DRAM scalability was supposed to stop, but engineers have found new solutions just like in the past to exceed this limit through the introduction of new materials and new device architectures (e.g., 3D NAND).

- o 3D NAND, with up to 128 memory-cell layers, was introduced into the market in 2020; the next generation with 176 layers has been announced by Micron and SK hynix. For DRAM, new chips manufactured on 1z node have hit the market in 2020.

- Huge annual R&D investments (several \$B) are still being made in existing DRAM and NAND technologies!

#### The embedded business is dependent on the end-market (MCU, SoC, ASIC, etc.):

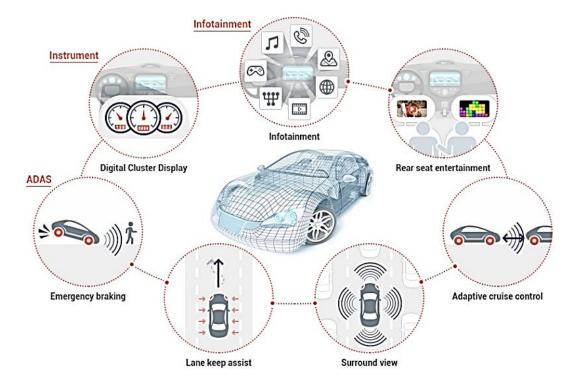

- Due to the proliferation of IoT and the advent of autonomous vehicles, the MCU market will grow in the coming years. Embedded Flash (eFlash) will become cost-prohibitive for nodes ≤28nm and foundries are working on new NVM solutions.

- Application processors use leading-edge nodes (<10nm) for logic and SRAM, a high-performance volatile technology. Thus, it

will take longer for SRAM to be replaced by emerging NVM (> 2 years).

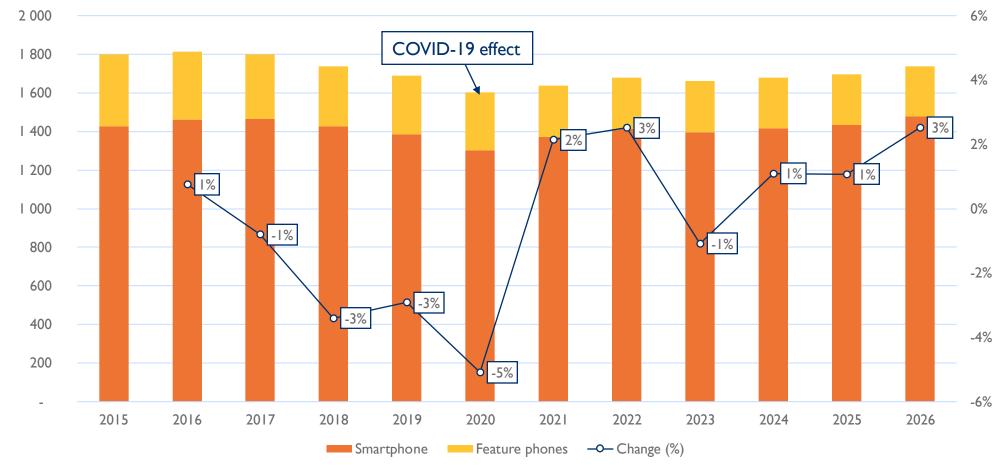

## IMPACT OF COVID-19 ON THE MEMORY MARKET

# The Covid-19 pandemic had a mixed impact on the memory market

- Data center and laptop demand grew, automotive and smartphones faced a slowdown. The net result has been a relatively balanced memory demand.

- Despite Covid-19, 2020 has been a year of recovery for the memory industry. In 2020, revenues have been growing modestly (5%) for DRAM and more appreciably (26%) for NAND, to \$67B and \$56B, respectively.

- Major cloud service providers are expanding construction of data centers to better serve global users, so the server industry has received a significant boost.

- Due to the lockdown restrictions, smartphone and vehicle sales have experienced a slowdown mainly in the first part of the year. For the full year 2020, unit shipments are expected to decrease with respect to 2019 by -3% for smartphones and -20% for vehicles.