# **LLC DRAM Updates**

Mar. 2022 | DRAM Product Planning Team, Memory Division

Confidential

### **Caution for Document License**

THIS DOCUMENT AND ALL INFORMATION PROVIDED THIS DOCUMENT AND ALL INFORMATION PROVIDED HEREIN (COLLECTIVELY, "INFORMATION") IS PROVIDED ON AN "AS IS" BASIS AND REMAINS THE SOLE AND EXCLUSIVE PROPERTY OF SAMSUNG ELECTRONICS CO., LTD. CUSTOMER MUST KEEP ALL INFORMATION IN STRICT CONFIDENCE AND TRUST, AND MUST NOT, DIRECTLY OR INDIRECTLY, IN ANY WAY, DISCLOSE, MAKE ACCESSIBALE, POST ON A WEBSITE, REVEAL, REPORT, PUBLISH, DISSEMINATE OR TRANSFER ANY INFORMATION TO ANY THIRD PARTY. CUSTOMER MUST NOT REPRODUCE OR COPY INFORMATION, WITHOUT SPECIFIC WRITTEN CONSENT FROM SAMSUNG. CUSTOMER MUST NOT USE, OR ALLOW USE OF, ANY INFORMATION IN ANY MANNER WHATSOEVER, EXCEPT FOR CUSTOMER'S INTERNAL EVALUATION PURPOSE. CUSTOMER MUST RESTRICT ACCESS TO INFORMATION TO THOSE OF ITS EMPLOYEES WHO HAVE A BONA FIDE NEED-TO-KNOW FOR SUCH PURPOSE AND ARE BOUND BY OBLIGATIONS AT LEAST AS RESTRICTIVE AS THIS CLAUSE. BY RECEIVING THIS DOCUMENT, IT IS UNDERSTOOD THAT CUSTOMER AGREES TO THE FOREGOING AND TO INDEMNIFY SAMSUNG FOR ANY FAILURE TO STRICTLY COMPLY THEREWITH. IF YOU DO NOT AGREE TO ANY PORTION OF THIS CLAUSE, PLEASE RETURN ALL INFORMATION AND ALL COPIES (IF ANY) WITHIN 24 HOURS OF RECEIPT THEREOF.

Confidential

## **Updates on Footprint**

1. Die size: 10 x 5 mm

#### 2. Footprint study of LLC DRAM includes

1) The same OD-ECC scheme as HBM3

□ OD-ECC: 256b (data) + 16b (meta data for system) + 32b (ECC check bits)

2) The repair and check scheme: PPR, Line Repair and Boundary Scan

#### 3. Footprint study of LLC DRAM does not include

1) DFT scheme, e.g. DA or MBIST: Die size increases if DFT scheme is implemented

#### Channel

| Cell      | Cell      | Cell      | Cell      |

|-----------|-----------|-----------|-----------|

| Pad(Peri) | Pad(Peri) | Pad(Peri) | Pad(Peri) |

| Pad(Peri) | Pad(Peri) | Pad(Peri) | Pad(Peri) |

| Cell      | Cell      | Cell      | Cell      |

| Cell      | Cell      | Cell      | Cell      |

| Pad(Peri) | Pad(Peri) | Pad(Peri) | Pad(Peri) |

| Pad(Peri) | Pad(Peri) | Pad(Peri) | Pad(Peri) |

| Cell      | Cell      | Cell      | Cell      |

| Key Features | Value       |

|--------------|-------------|

| Cache line   | 64B         |

| Organization | x1024       |

| Density      | 8Gb         |

| Ch.          | 16          |

| Bank/Ch.     | 4 (2 BGs,   |

| Dalik/Cii.   | 2 Banks/BG) |

| BL           | 8           |

| Bandwidth    | 0.8~1TB/s   |

| Pin speed    | 6.4~8Gbps   |

| tRC          | 40ns        |

| RL (tRCD+RL) | 32ns Con    |

# **Further Study Results**

#### 1. Power Rail

- 1) If Intel shares power measurement conditions, Samsung team can estimate the power of LLC DRAM

- □ For example, 3 channels are operated and the remaining channels are in precharge standby (IDD2N)

| Power Supply | Typical |

|--------------|---------|

| VDDP         | 1.8V    |

| VDDC / VDDQ  | 1.1V    |

| VDDQL        | 0.4V    |

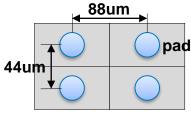

#### 2. Pad pitch: 88 x 44 um

1) Does Intel consider HCB (hybrid copper bonding)?

3. Operating temperature: 105C (t<sub>i</sub>) w/ 4x refresh rate

# **Product and Stacking Type**

#### 1. Product type: Wafer or Die w/ ubump

#### 2. Stacking type: 2.5D and/or 3D

1) For 3D stacking, we need to discuss about how to build DA path (for the purpose of test and/or failure analysis)

| 2 ED Stocking                                | 3D Stacking           |                                                          |  |

|----------------------------------------------|-----------------------|----------------------------------------------------------|--|

| 2.5D Stacking                                | DA path as TSV in CPU | DA path as additional connection                         |  |

| (Logic)<br>Interposer  CPU  LLC  PCB  DA pin | CPU TSV in CPU        | CPU  TBD  Wire bonding?  - Additional Interposer?  - etc |  |

### **Discussion about DFT**

#### 1. Need to discuss about DFT scheme for HF (high frequency)

- 1) LF test is done at wafer level

- ☐ HF test at wafer level needs further study about feasibility (currently at conceptual stage)

- 2) Die overhead of DFT for HF depends on test coverage (function)

|              | Option 1 –<br>Design guarantee                                            | Option 2 –<br>DA                  | Option 3 –<br>MBIST (+ DA)                 |

|--------------|---------------------------------------------------------------------------|-----------------------------------|--------------------------------------------|

| How to test  | HF yield is measured as SiP or proxy PKG (Yield level needs to be agreed) | Test patterns are injected via DA | Test is initiated by simple command via DA |

| Die overhead | None                                                                      | Mid                               | High                                       |

### **Requests for Intel**

#### 1. Proposal on separate meeting for standardization milestone

1) To align Standardization schedule btw Intel & Samsung

#### 2. Requirements for DFT coverage

- 1) Test coverage (functions)

- ☐ For example, the same level as HBM

- □ # of DA pads

#### 3. Quick question for Intel Market rough estimate

- 1) 02/22 "For a iGFX attach to client PCs" → Market for iGPU frame buffer memory?

- 2) 03/17 − "Graphics Volume 10-20Mu" → Market for dGPU memory + Accelerator (next PVC) memory?

# **END**

# **Comparison between LLC and HBM3**

|                        | Item            | HBM3                                                               | LLC DRAM                          |

|------------------------|-----------------|--------------------------------------------------------------------|-----------------------------------|

| Architecture           | Die composition | Stack, 8H                                                          | Mono                              |

|                        | Cache line      | 32B                                                                | 64B                               |

|                        | Footprint       | 115.56mm²<br>10.75(X) * 10.75(Y)                                   | 50mm <sup>2</sup><br>10(X) * 5(Y) |

|                        | Density         | 16Gb                                                               | 8Gb                               |

|                        | Organization    | x1024                                                              | x1024                             |

|                        | CH per die      | 4                                                                  | 16                                |

|                        | PCH per die     | 2                                                                  | 1                                 |

|                        | Bank per die    | 128                                                                | 64 (32BG, 2Banks/BG)              |

|                        | BL              | 8                                                                  | 8                                 |

|                        | Interface       | DRAM type                                                          | ←                                 |

|                        | PHY pitch       | 110um x 48um                                                       | 88um x 44um                       |

|                        | Bandwidth       | 0.8TB/s                                                            | 0.8~1TB/s                         |

|                        | Power/bit       | 4pj/bit                                                            | 0.8pJ/bit                         |

| _                      | Pin speed       | 6.4Gbps                                                            | 6.4~8Gbps                         |

| Features               | tRC             | 52ns                                                               | 40ns                              |

|                        | RL (tRCD+RL)    | 35ns                                                               | 30ns                              |

|                        | WL (tRCD+WL)    | 20ns                                                               | 16ns                              |

| Operating<br>Condition | VDD1 / VDD2     | 1.8V / 1.1V                                                        | <b>←</b>                          |

|                        | VDDQ            | 0.4V                                                               | <b>←</b>                          |

|                        | Operating Temp  | 0~95°C                                                             | -25~105°C                         |

|                        | RAS             | OD-ECC                                                             | <b>←</b>                          |

| Special<br>Feature     | TEST            | Boundary Scan, Lane Repair, PPR,<br>Direct Access, BIST, IEEE 1500 | Boundary Scan, Lane Repair, PPR   |

# ARs continued

# AR: Intel to provide update on Size and Timing of Market to help Samsung with Motivation for TCM.

- Rough Estimate

- For 50mm2 die with 2026/27 Server intercept. Multiple GB per socket

- Low market penetration. 6M unit, High Market Penetration. 60M unit

- For a iGFx attach to client PCs. ~5M unit

Any deeper discussion would be with Business Teams (Raja K) as Intel team on call is engineering team

# Graphics feedback

- Capacity

- varies across product lines from 2GB to 32GB

- BW/capacity ratio

- Ideal BW/capacity ratio varies across product lines from .5 to 1 to 2 TB/s/GB

1 TB/s/GB is good except for high end

- 2 TB/s/GB for high end OAM form factor with limited footprint for memory

- Aspect ratio

- For 50mm2 aspect ratio of 10x5mm is good. 10x10mm is too large

- Volume

- 10-20Mu

- Timeline

- 2026

## **LLC DRAM Feature Alignment**

#### 1. Need to confirm the LLC DRAM key requirement

- 1) To fix the starting point for the design optimization

- □ For server/client CPU, 1GB, 0.8TB/s and 50mm2, is agreed as starting point for further discussion. And How about AI/ML Accelerator?

#### 2. Next step: To investigate the detailed architecture

1) Power rail, on top of concrete high-level DRAM architecture

|                            | Server / Client CPU                   | AI/ML Accelerator        | Remarks                                         |  |

|----------------------------|---------------------------------------|--------------------------|-------------------------------------------------|--|

| Die composition            | Mono-die                              | Mono-die                 | -                                               |  |

| Cache line                 |                                       | 64B                      | Need to discuss about Cache line of Accelerator |  |

| Footprint                  | 50mm²                                 |                          | Need to discuss about Range                     |  |

| Density                    | 1GB                                   |                          | Under 1GB is OK?                                |  |

| Latency                    | tRC: 40-45ns / tRCD: 17ns / tAA: 15ns |                          | Need to update AI/ML Accelerator requirement    |  |

| Bandwidth<br>(6.4Gbps/pin) | 1TB/s                                 |                          |                                                 |  |

| Ю                          | Distributed, 1K                       | Distributed, 4K          |                                                 |  |

| Channel                    | TBD                                   | TBD                      |                                                 |  |

| Bank                       | based on Cache line size              | based on Cache line size | TBU after Key Architecture fixed                |  |

| BL                         | Any preference? BL8 vs BL16           | Any preference?          | The after key Architecture fixed                |  |

| Address                    | TBD                                   | TBD                      |                                                 |  |

| Power rail/Pin map         | TBD                                   | TBD                      |                                                 |  |

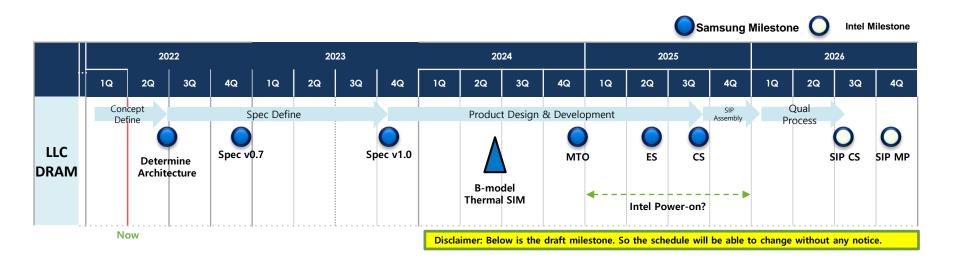

## **LLC DRAM Milestone Update**

#### 1. Spec v0.7 & MTO draft milestone are updated → Need to align with Intel

1) Power-on : 2025 → Any quarter based schedule?

13 Confidential