WW40'2022

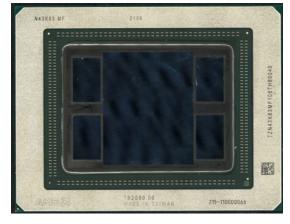

AMD MI210 (SPIL FOEB) and MI100 (TSMC CoWoS-S)

Jose Perez, Tom DeBonis, Ivan Garcia

Ack: Derek Heatherington, KC Liu, Georg Seideman

# AMD Instinct MI100 & MI210 Accelerators

### AMD MI100 AMD MI210

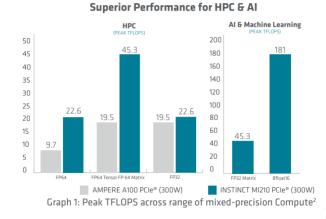

# Superior Performance for HPC & AI (Peak TFLOPS) HPC Workloads 50 AI Workloads 40 15 10 50 FP64 FP32 M100 (400W) Graph 1: Peak TFLOPS across range of mixed-precision Comute¹

### **Key Features**

### **PERFORMANCE**

120 **Compute Units** Stream Processors 7.680 Peak BFLOAT16 Up to 92.3 TFLOPS Peak INT4 | INT8 Up to 184.6 TOPS Peak FP16 Up to 184.6 TFLOPS Peak FP32 Matrix Up to 46.1 TFLOPS Peak FP32 Up to 23.1 TFLOPS Peak FP64 Up to 11.5 TFLOPS **Bus Interface** PCIe® Gen 3 and Gen 4 Support³

### MEMORY

Memory Size32GB HBM2Memory Interface4,096BitsMemory Clock1.2 GHzMemory BandwidthUp to 1.2 TB/s

### RELIABILITY

ECC (Full-chip) Yes<sup>4</sup> RAS Support Yes<sup>5</sup>

### **SCALABILITY**

Infinity Fabric™ Links 3

OS Support Linux® 64-bit

AMD ROCm™ Compatible Yes

### **BOARD DESIGN**

Warranty

Board Form Factor Full-Height, Dual Slot Length 10.5" Long Thermal Passively Cooled Max Power 300W TDP

·

Three Year Limited<sup>6</sup>

Memory Interface Memory Clock Memory Bandwidth

**Key Features**

**PERFORMANCE**

Stream Processors

Peak FP64/FP32 Vector

Peak FP64/FP32 Matrix

**Compute Units**

Peak FP16/BF16

Peak INT4/INT8

**MEMORY**

Memory Size

Matrix Cores

MI210

416

104 CU 🖶

6,656

22.6 TF 👚

45.3 TF 👚

181.0 TF -

181.0 TOPS -

| RELIABILITY            | MI210                                |

|------------------------|--------------------------------------|

| ECC (Full-chip)        | Yes                                  |

| RAS Support            | Yes                                  |

| SCALABILITY            |                                      |

| Infinity Fabric™ Links | up to 3                              |

| Coherency Enabled      | Yes (Dual   Quad Hives)              |

| OS Support             | Linux™ 64 Bit                        |

| AMD ROCm™ Compatible   | Yes                                  |

| BOARD DESIGN           |                                      |

| Board Form Factor      | Full-Height, Full-Length (Dual Slot) |

| Length                 | 4.5" x 10.5" (11.43 CM x 26.67 CM)   |

| Bus Interface          | PCIe® Gen4   Gen3 Support            |

| SR-IOV Support         | Yes (Passthrough Only)               |

Thermal

Max Power

Warranty

**Passively Cooled**

300W TDP (EPS12V, 8-pin)

Three Year Limited<sup>5</sup>

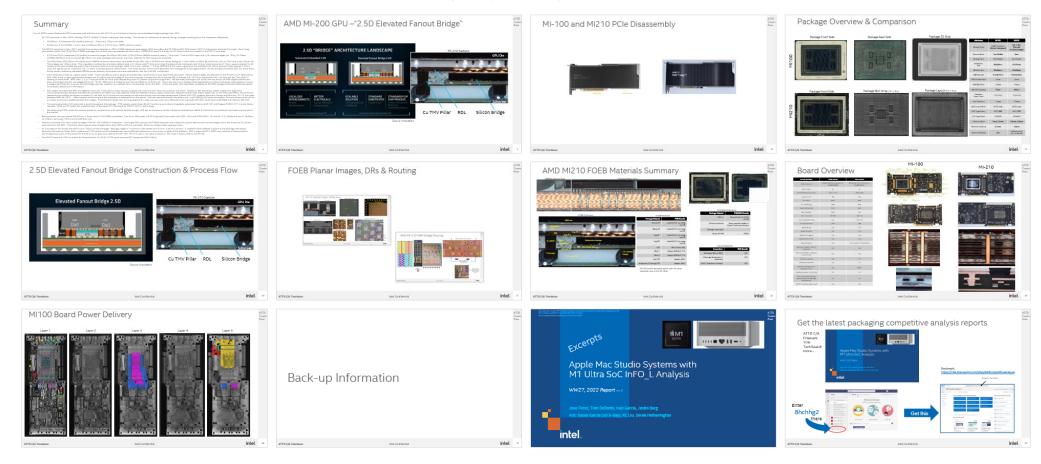

# Summary Zoom

### Click slide images to jump to key sections

# Summary

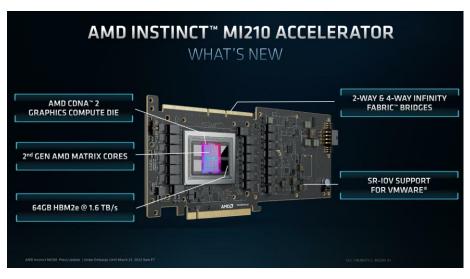

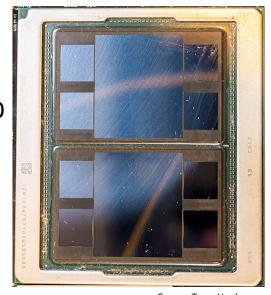

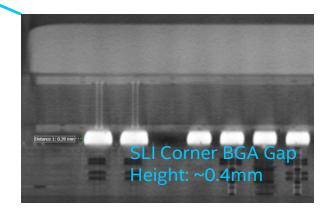

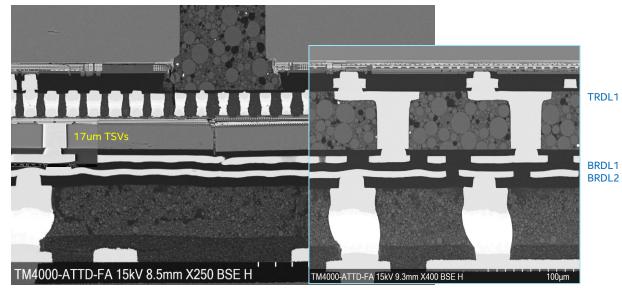

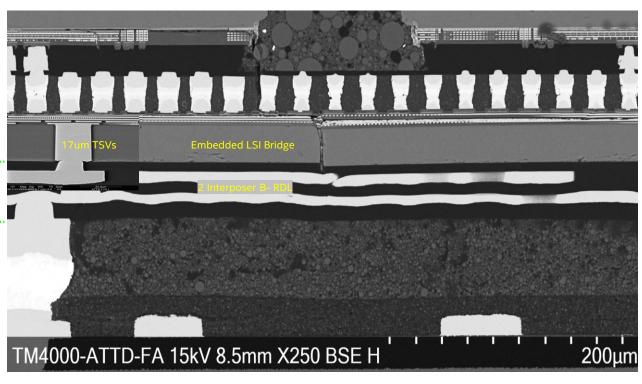

Two of AMD's recent datacenter GPUs are examined with focus on the MI-210, our first look at the fan out embedded bridge package from SPIL:

- MI-100, launched in Nov. 2020, utilizing TSMC's CoWoS-S silicon interposer technology. This serves as a reference to identify design changes resulting from the interposer differences.

- 40x29mm Si Interposer (44 i/wafer) stackup?, Chip-Last, 140um min pitch

- 65x50 mm 5-2-5 FCBGA 1.2mm core, 22x28mm GPU, 4 6.7x10.7mm HBM2 memory stacks

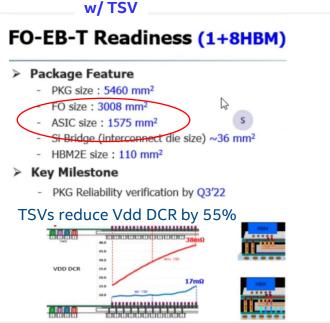

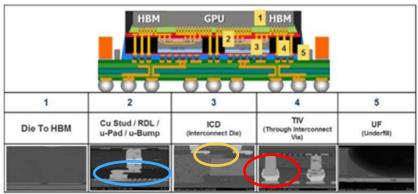

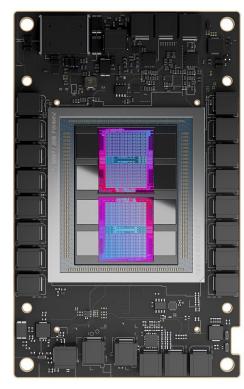

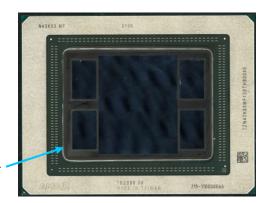

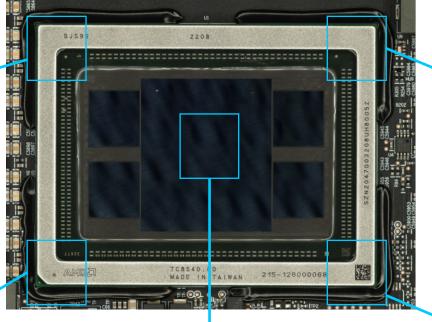

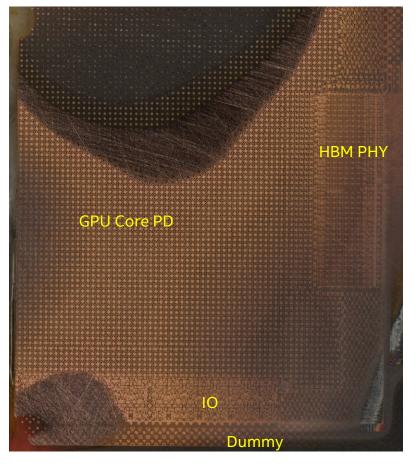

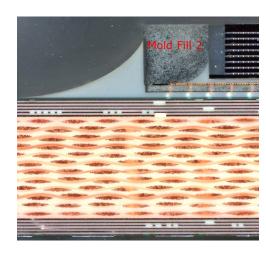

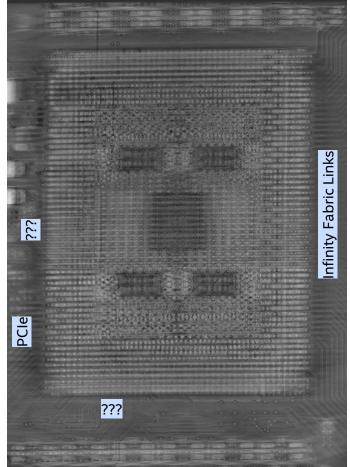

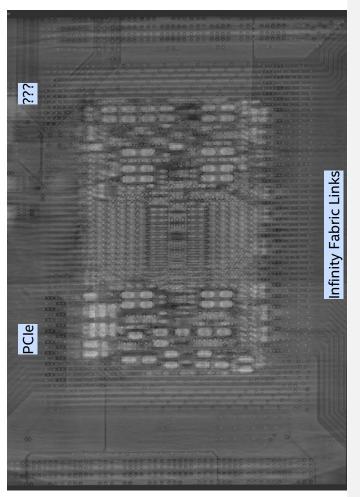

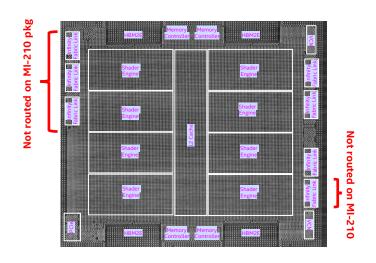

- The MI210, launched in Nov. 2021 and the first product shipping on SPIL's FOEB interposer technology. AMD also offers the MI-200 and MI-250 where 2 MI210 interposers are linked through ~6mm long connections within the 79.5x70mm FCBGA package; this version was not available for tear down. MI200/250 specific Infinity Link IO blocks were not routed on the MI210 substrate.

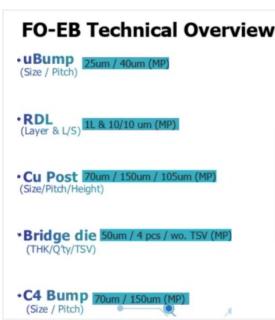

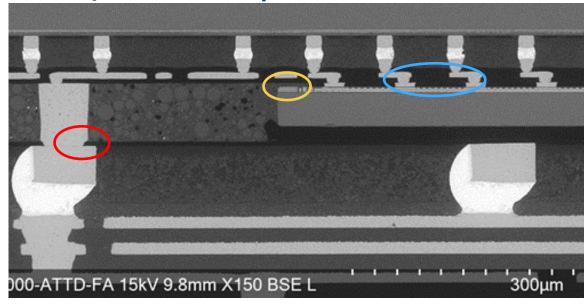

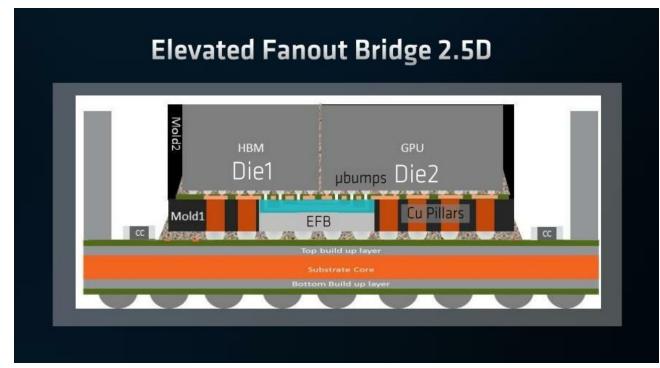

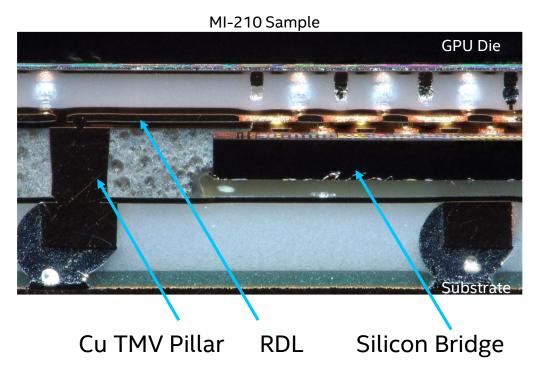

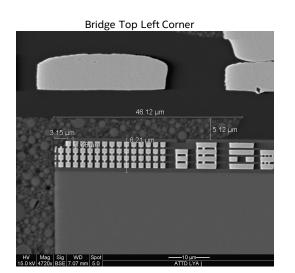

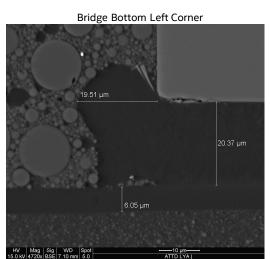

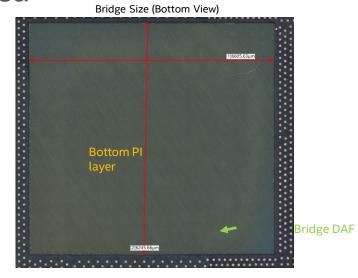

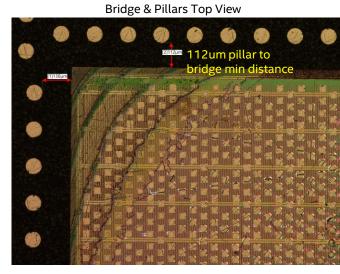

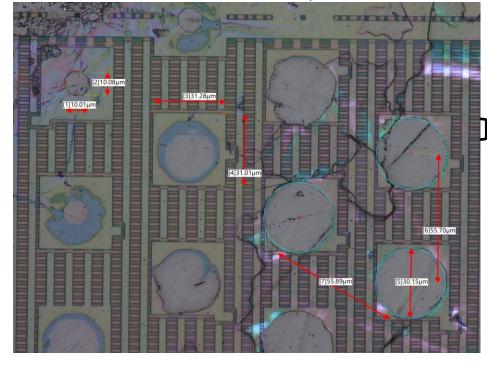

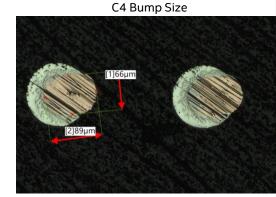

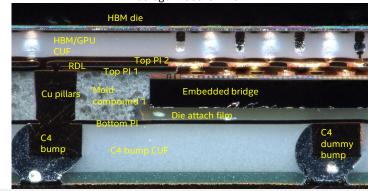

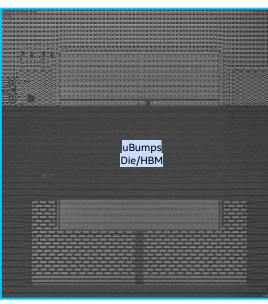

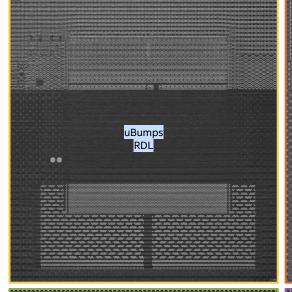

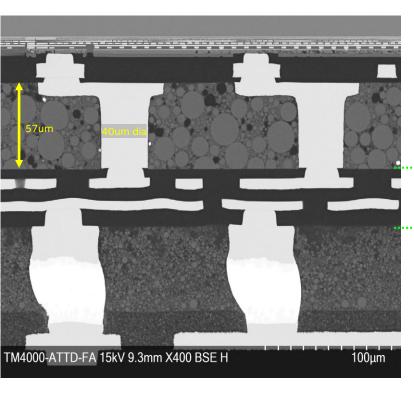

- 47x31mm PI/Cu Interposer (33 i/wafer) connect the larger 25x29mm GPU and 4 9.5x10.5mm HBM2e memory stacks, Chip-Last, 1 Fan-out RDL layer with 4 4L silicon bridges (no TSVs), Cu Pillars (1/PSB), 89x66um oval Cu bumps @148um min pitch package side bumps are mass reflowed to SAC bumps on substrate.

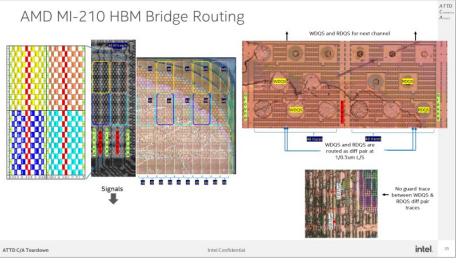

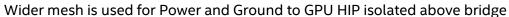

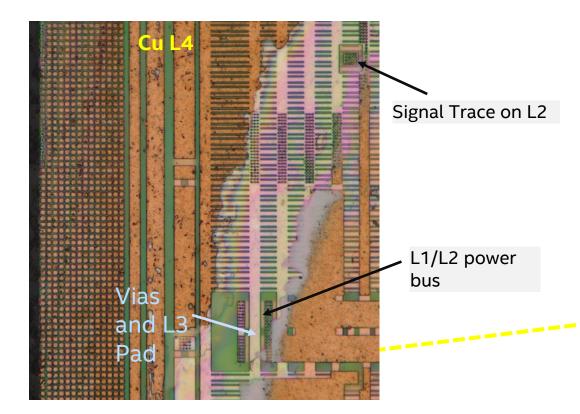

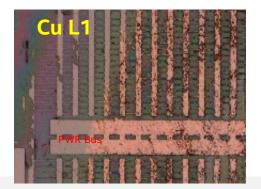

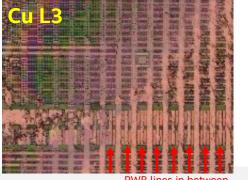

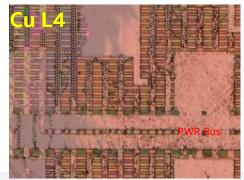

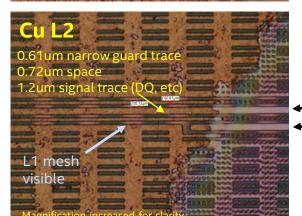

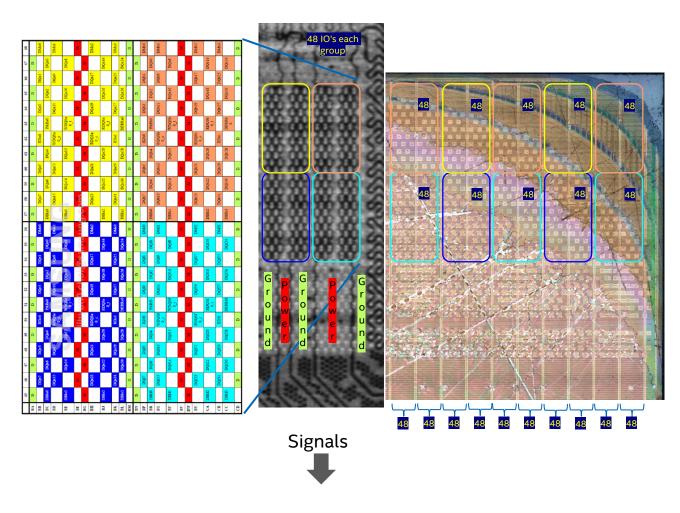

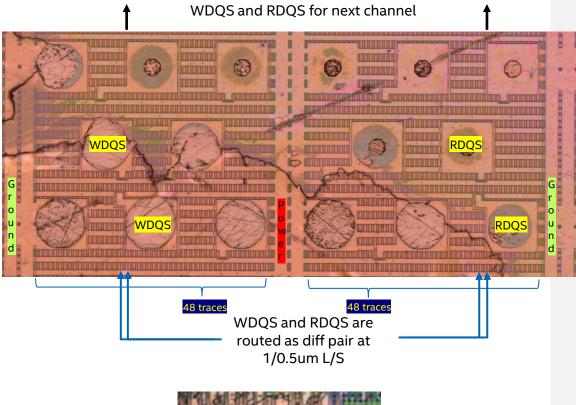

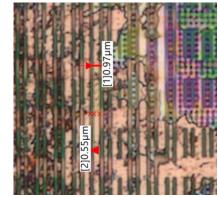

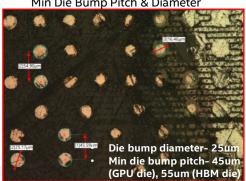

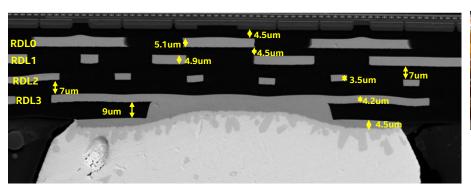

- The 25x29mm GPU (45um min pitch) and 4 HBM2e memory stacks each connected to the GPU with a 6.25x6.4mm silicon bridge (4 1.14um thick Cu RDLs @ 3.3/5.3um L/S, no TSVs with a thin 0.5um ILD. The bridges are ~58um thick. The singulation method has not been determined; a 41-46um wide PI-free zone rings the edge of the interposer and <0.5um wide remnants of 1.5um square stacked Cu fill shapes in the kerf outside the guard ring are present with minimal damage noted in the cross section. 1.25um HBM2e DQ and other signal lines are shielded with 0.6um ground traces spaced 0.72um away, DP signals are at 1.0/0.5um L/S. L1 and L3 are also ground shield mesh. The wider portion of the mesh generally runs orthogonal to the signal traces. Power and ground traces also run every third bump column following standard HBM2e power delivery conventions and are replicated in the Fan Out RDL metal layer.

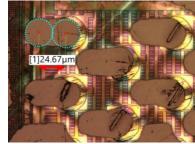

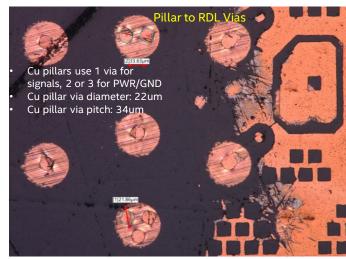

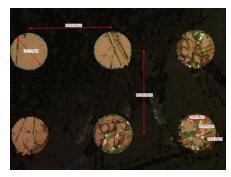

- The interposer is built on a glass carrier wafer. 70um dia./85um tall Cu pillars are plated atop vias formed in 6um polyimide base layer. ~60um thick bridges are attached to the PI with 21um Nitto Denko DAF. After mold, a slight grind/polish reveals the Cu pillars and the bridge PI and micro-bumps. A single 8um thick topside RDL is formed with 22/14um top/bottom dia. vias through the 7um thick PI landing on each pillar. AMD uses 1, 2, or 3 vias per pillar at 34um pitch depending upon IO, power or ground assignment. SIB (die side) power/ground bump vias are always at least slightly offset from pillar and bridge vias; IOs are staggered by 40 97um. SIB bump to bridge bump vias are offset by 24.67um ctc. 20um dia vias (14um bottom opening) landing on 30um interposer pads; approx. 5.34um misalignment between a corner via and bridge pad was noted on our sample. 8um of polyimide covers the RDL. A few test pads were identified, probably to test RDL-bridge continuity before die attach. Full process details are in the report.

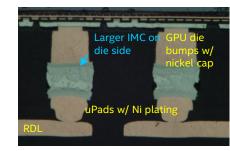

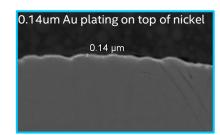

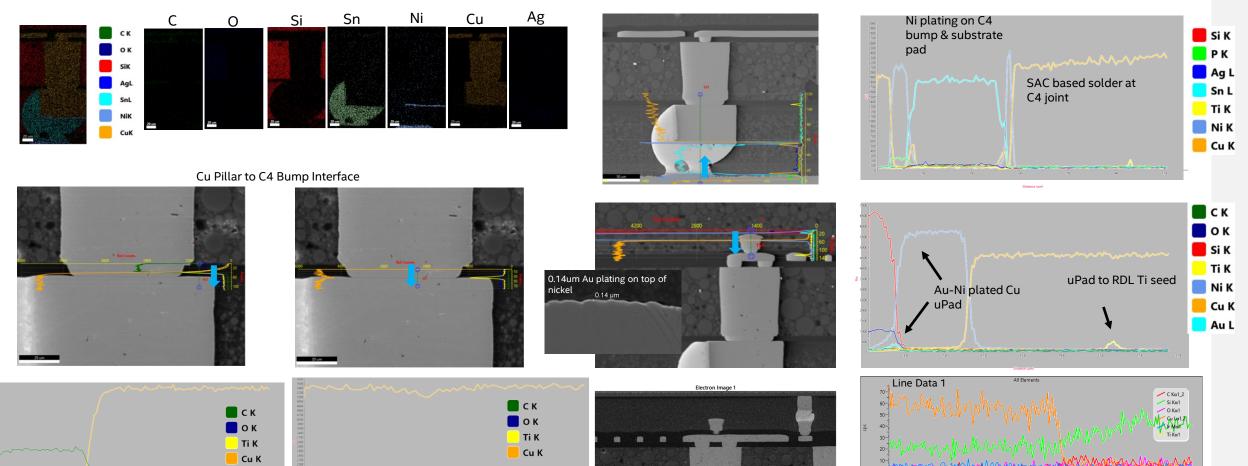

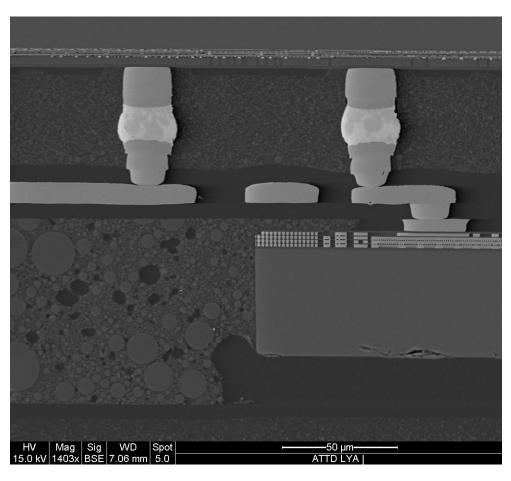

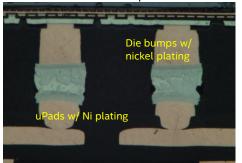

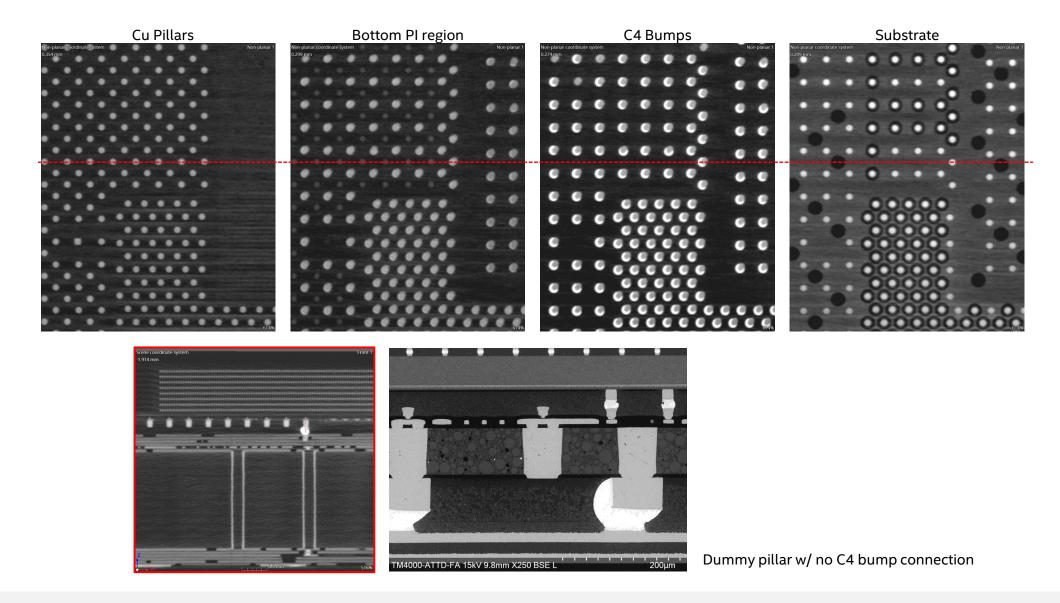

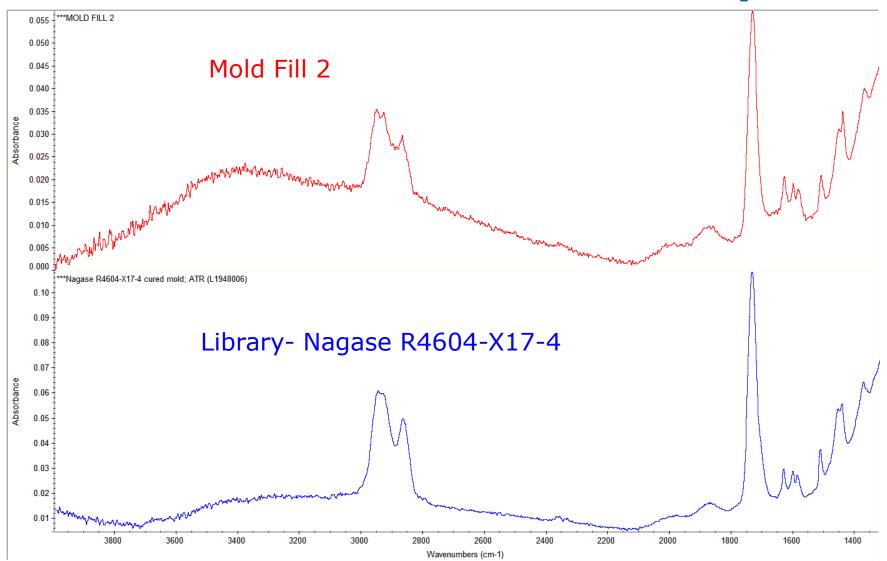

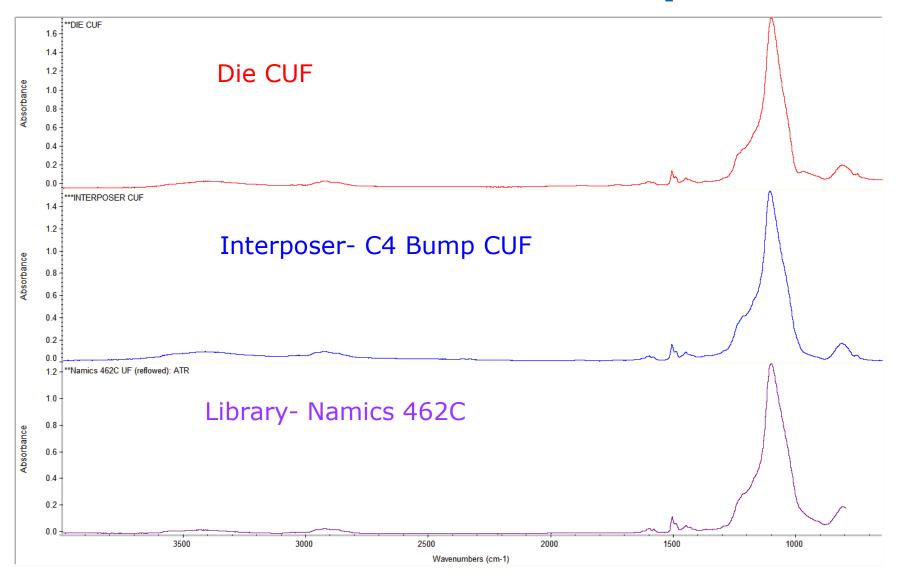

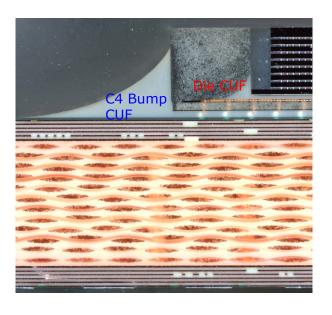

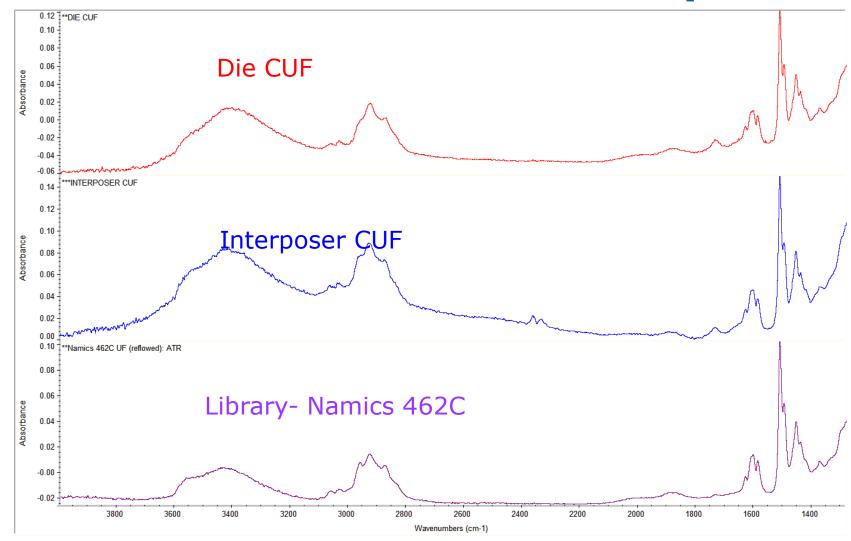

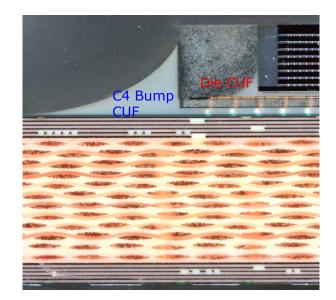

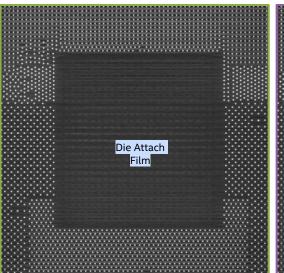

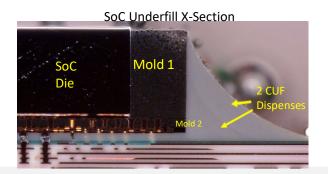

- SAC solder connects the GPU and HBM to 24um dia. 15um tall Cu micro-bumps capped with 7um Ni and 0.14um Au at 40um min pitch. Based on IMC thickness, solder shapes and data from unconnected bumps beneath the HBM2Es we believe the GPU was TCB attached while the HBM2E memory stacks were mass reflowed and all chip attach solder was on the GPU and HBMs. The intent of several dummy pillars anchored in bottom PI vias with no C4 bump nor connection to the micro-bump has not been determined. Namics 462 CUF protects the micro-bumps and fills the 124-131um gaps between HBM and GPU. After topside mold and grind the interposer is released from the carrier. Vias are opened beneath the pillars and oval Cu/Ni/(Au?) bumps are plated. Dummy bumps (with no via or visible anchor) are plated beneath the bridges. The finished interposers are singulated with a step-cut saw, and mass reflowed onto substrate with SAC solder and underfilled with Namics 462 CUF.

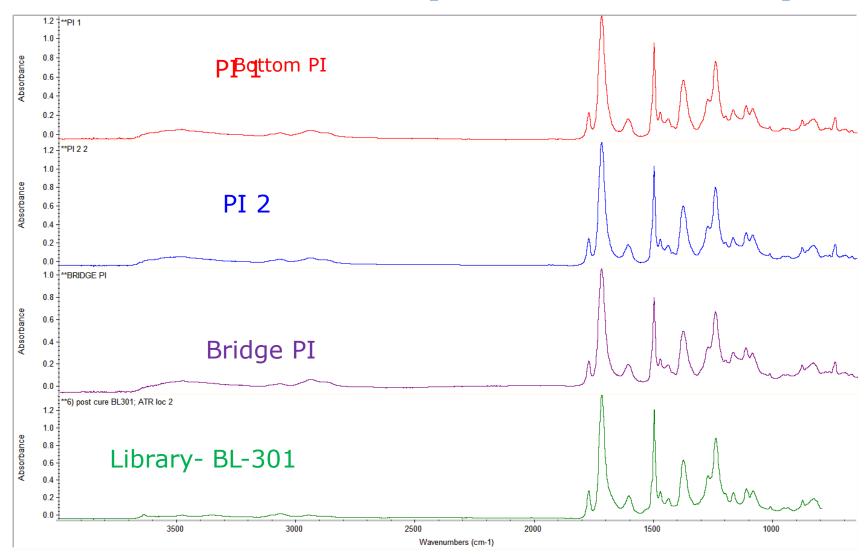

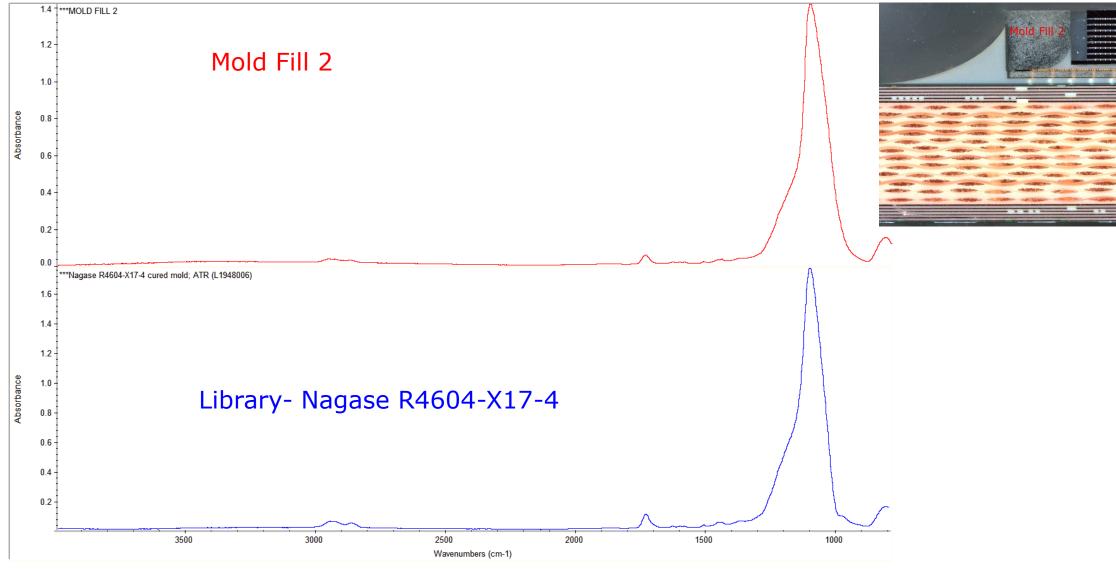

- The same polyimide, CUF and mold is used throughout the package. FTIR spectra match Asahi BL301 low temp cure photo-imageable polyimide, Namics 462 CUF and Nagase R4604-X17-4 mold library samples. Mold and PI match the materials seen in the Apple M1 Ultra built on TSMC's InFO-L technology.

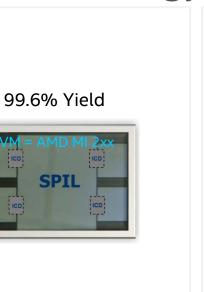

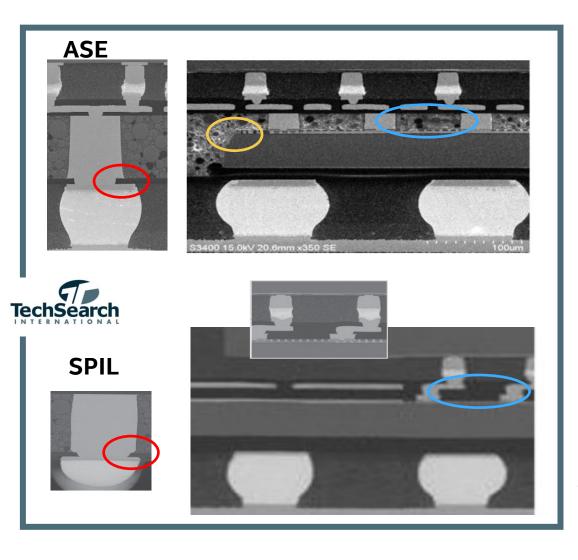

- We determined SPIL made this sample based on comparisons with their published images; ASE has announced a similar interposer architecture called Si-FoCoS but no products have been announced in the market.

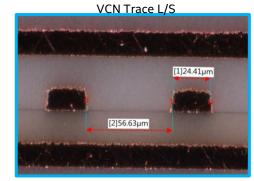

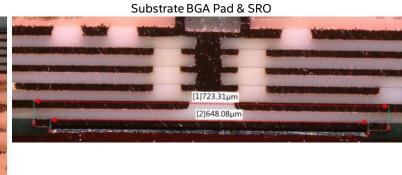

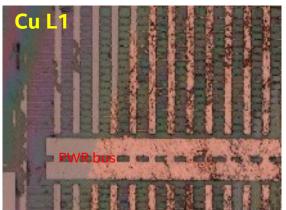

- Both products use very similar 65x50 mm 1.2mm core 5-2-5 FCBGA substrates, 7um Ni on BGA pads, 2,878 SnAg balls/1mm pitch with 0201 LSCs and 0204 DSCs. On the MI-210, Infinity link are 21.5/48um LS (136um pair-pair); VCN is at 24.4/56.6um L/S.

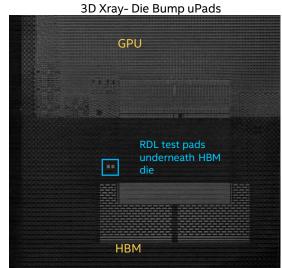

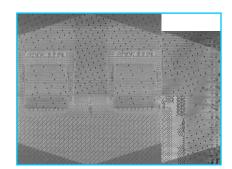

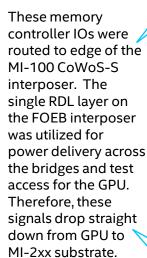

- Memory controller IOs were routed to edge of the MI-100 CoWoS-S interposer. The single RDL layer on the FOEB interposer was utilized for power delivery across the bridges and a few dozen 9/12 L/S test port traces for the GPU. Therefore, these signals drop straight down from GPU to MI-2xx substrate. Minimum shape-shape spacing is 9um.

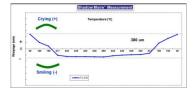

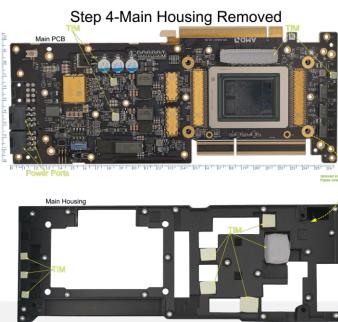

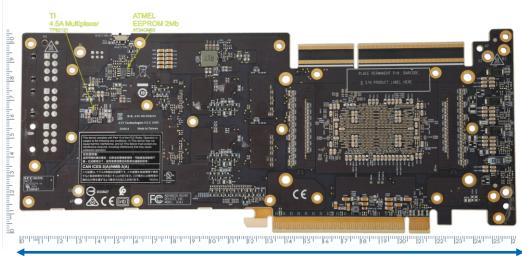

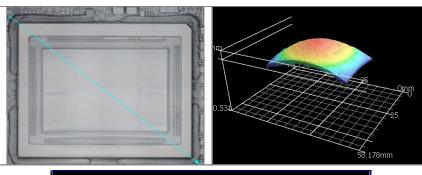

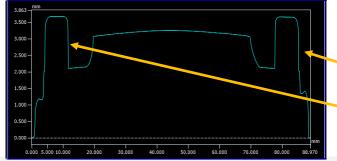

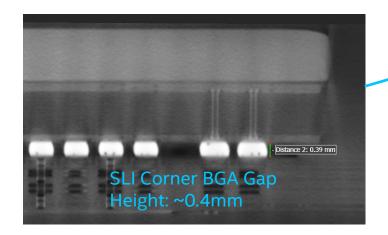

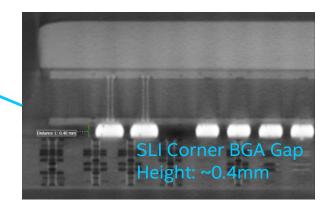

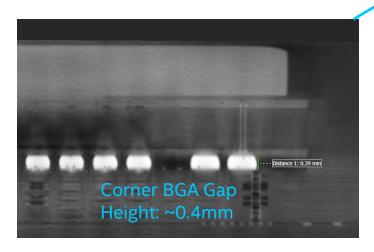

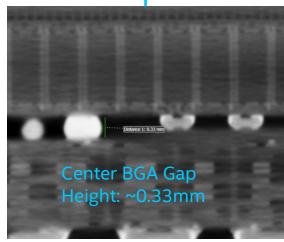

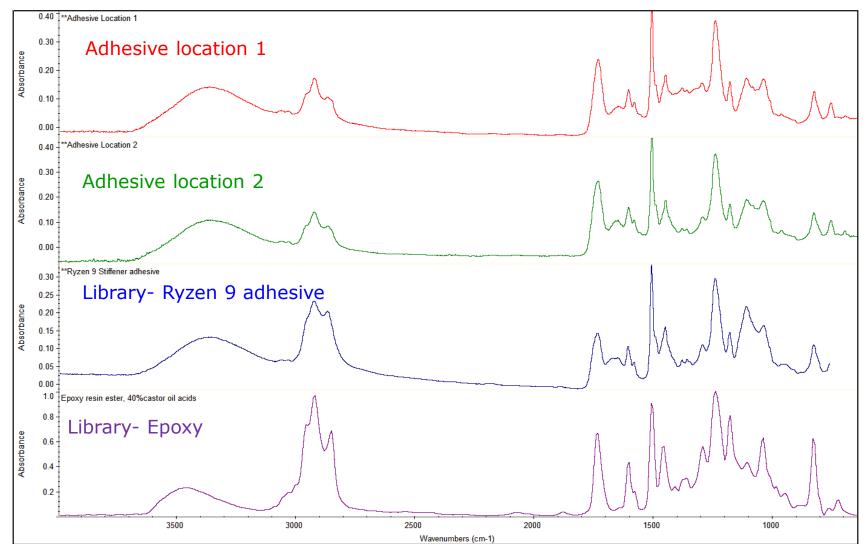

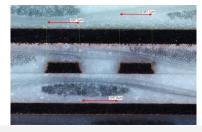

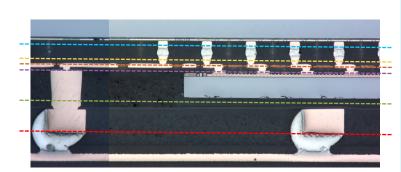

- As mounted on the board, the MI210 has ~70um convex warpage. BGA gap height is ~0.33mm in the center and 0.4mm in all four corners. A stainless-steel stiffener is glued to the package with epoxy adhesive like used on Ryzen BGAs. optical and FTIR results could not detect the use of different adhesives in the corner vs sides of the stiffener; SPIL's paper at ECTC 2022 may relate to a future product. Corner glue was used on the board for the MI-210, no glue was used on the MI-100. MI-210 uses a 14L Type 4 board vs. 16L Type 3 board used on the MI100.

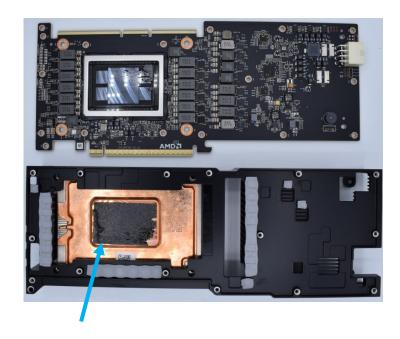

- The MI210 heat sink TIM is a match for Showa Denko YV-001H VCTIM; post removal BLT measured 330-345um.

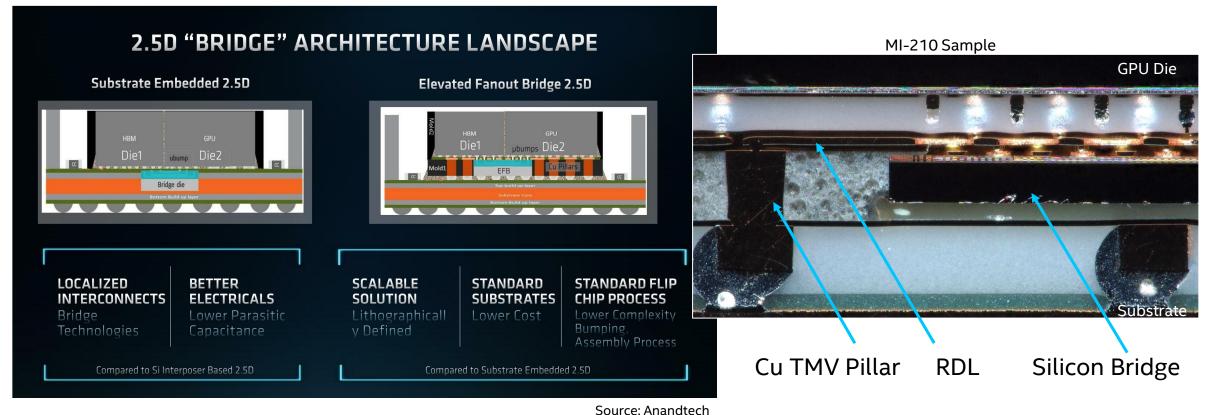

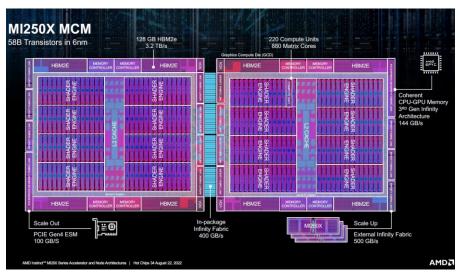

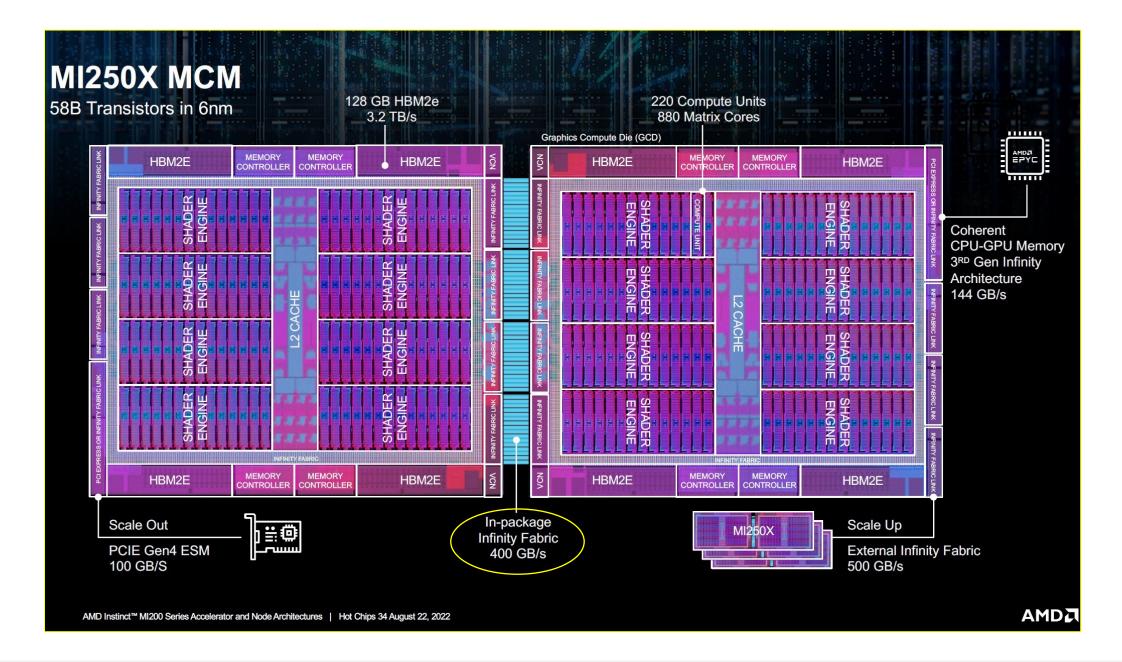

# AMD MI-200 GPU - "2.5D Elevated Fanout Bridge"

intel Intel Confidential ATTD C/A Teardown

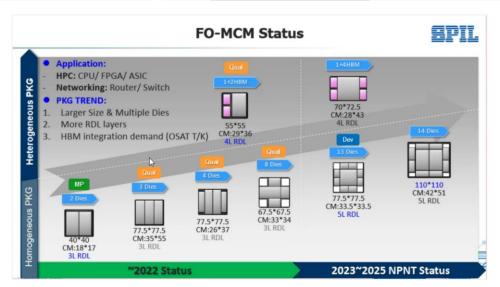

SPIL's FOEB Technology

### **Customer Inquiries > Readiness**

### FO-EB-T

- 2xR ASIC

- 8 HBM2E

- 3.7xR Interposer

- ~75x75 substrate

### **FO MCM**

- 14 die

- 2.6xR Interposer

- 5 RDL 2/2 L/S

- 110x110mm substrate

### Chiplets Integrated Solution with FO-EB Package in HPC and Networking Application

Po Yuan (James) Su\*, David Ho, Jacy Pu, Yu Po Wang Siliconware Precision Industries Co. Ltd. (SPIL)

|        |   |                                         |                          |                | Result   |

|--------|---|-----------------------------------------|--------------------------|----------------|----------|

|        | 1 | Time Zero                               | то                       | 0/99 pcs       | All Pass |

|        | 2 | MSL4<br>(30 °C, 60% RH, 96hrs)          | Pre-cond.                | 0/99 pcs       | All Pass |

|        | 3 | TCT (J)<br>(0 ~ 100 °C)                 | 625, 2000,3000<br>Cycles | 0/33 pcs       | All Pass |

|        | 4 | u-HAST (B)<br>(110 °C,85%RH, 17.7 Psia) | 132, 264<br>Hours        | 0/33 pcs       | All Pass |

| 150 25 | 5 | HTSL (B)<br>(150 °C, Need Pre-cond.)    | 500, 1000<br>Hours       | 0/33 pcs       | All Pass |

|        |   | Table 6. Reliabili                      | ity and Verific          | cation Test Re | esult    |

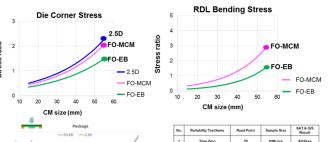

Figure 5. FO-EB versus 2.5D Warpage

| PK                             | G Electric Perform | mance for HBM2E |         |

|--------------------------------|--------------------|-----------------|---------|

| Item                           | FO-EB              | FO-MCM          | 2.5D    |

| W(um)/S(um)                    | 0.5/1.5            | 2/3             | 0.5/0.5 |

| HBM2E (3.2Gbps)<br>Eye Diagram | XX                 | XX              | XX      |

| HBM2E Request(mV)              |                    | 480             |         |

| Height (mV)                    | 662                | 1013            | 600     |

| Width (ps)                     | 294                | 301             | 288     |

| Result                         | Accept             | Accept          | Accept  |

Table 2. PKG Electric Performance for HBM Demand

Table 7. Structure Cross-section Result

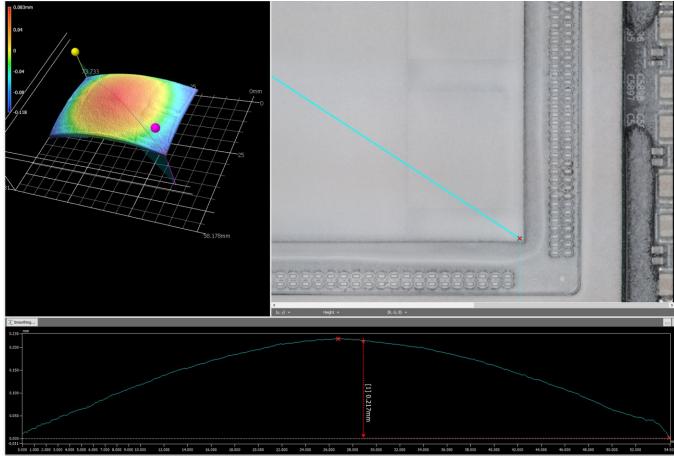

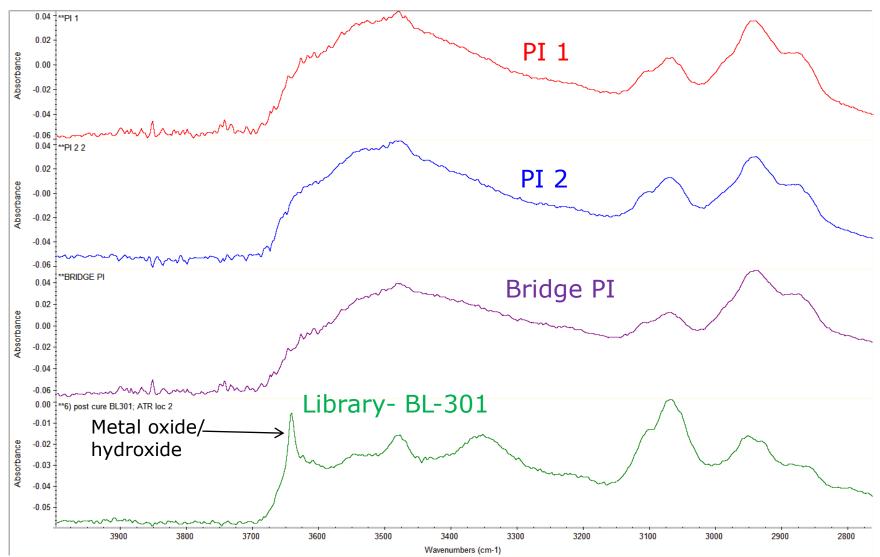

# **OSAT Identification: SPIL**

### **ATTD C/A MI-210 Sample:**

### **SPIL**

2020 IEEE 70th Electronic Components and Technology Conference (ECTO

Scalable Chiplet package using Fan-Out Embedde Bridge

Joe Lin, C. Key Chung, C. F. Lin, Ally Liso, Ving Ju Lu, Jia Shuang Chen,

Copporate R & D.

Silicomoure Precision Industries Cu., Ltd

Taichung, Taiwan, R.O.C.

joetin-323/jippl.com.ps. recedung@jppl.com.ps

Table 7. Structure Cross-section Result

Bridge bump • gap fill (PI), • bridge singulation and •TMV Cu pillar and • via shape match images published by SPIL. Both OSATs changed to Cu pillar PSB at some point during development.

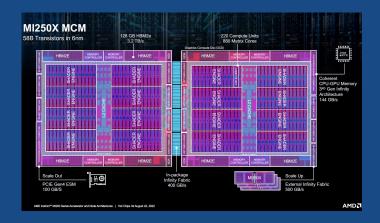

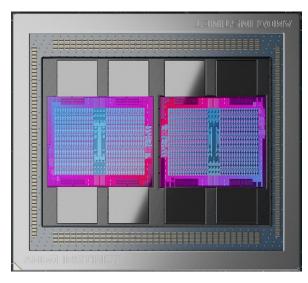

# AMD MI200 Series GPU Accelerators

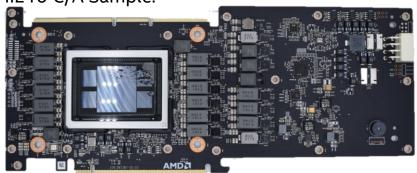

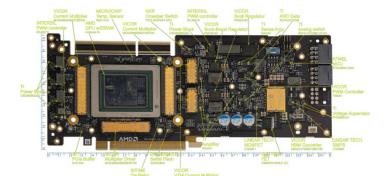

### MI210 in PCIe Card Form Factor

### MI210 C/A Sample:

### MI250 in OAM Form Factor

https://www.hpcwire.com/off-the-wire/amd-instinct-mi200-adopted-for-large-scale-ai-training-in-microsoft-azure/

Artist rendering. Real unit has 2 interposers connected though substrate.

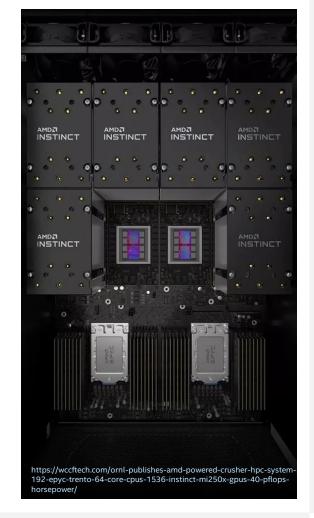

### MI250X in 'Crusher" HPC System

- 40 PFLOPs @ Oak Ridge National Labs

- 192 EPYC Trento 64c CPUs

- 1536 Instinct MI250X GPUs

# AMD MI-200 GPU - "2.5D Elevated Fanout Bridge"

### MI-200/250 Dual GPU

Est: 79.5x70mm

GPU:GPU connection is through ~6mm traces in FCBGA.

Source: Toms Hardware

Source: Anandtech

MI-210 C/A Sample

MI-210, Nov. 2021 Launch 47 x 31mm SPIL FOEB interposer 33 glpw, ~\$45-55/int @\$1.5-1.8k/w

> MI-100, Nov. 2020 Launch 40x29mm TSMC CoWoS-S Interposer 44 glpw, ~\$45-55/int @\$2-2.5k/w

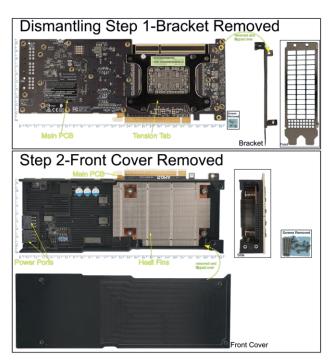

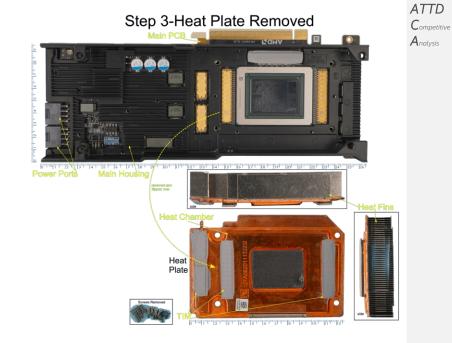

# MI-100 and MI210 PCIe Disassembly

# MI100 System Disassembly

### Front & Side Views

### **Back View of Device**

\*Images from SystemPlus Consulting Teardown Report

Intel Confidential

intel

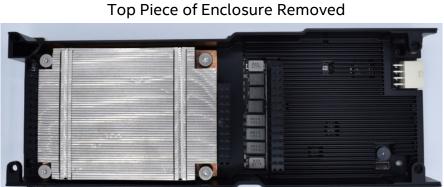

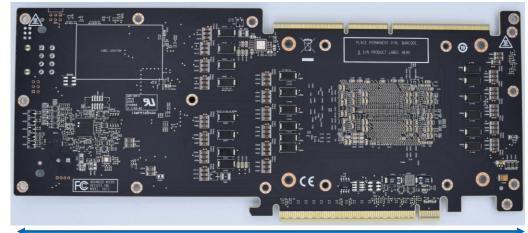

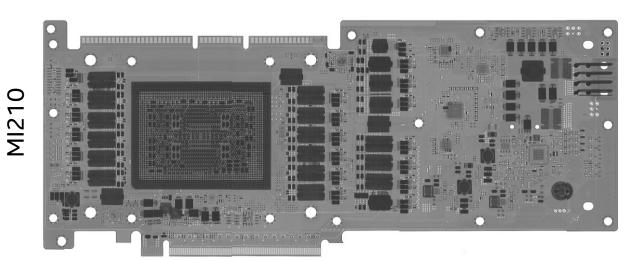

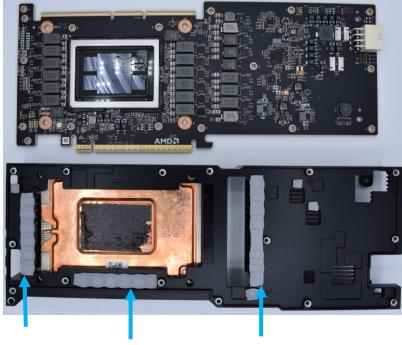

# MI210 System Disassembly

Heat Sink Removed

**Board Enclosure Bottom View**

**Bottom Piece of Enclosure Removed**

Heatsink Backplate Removed

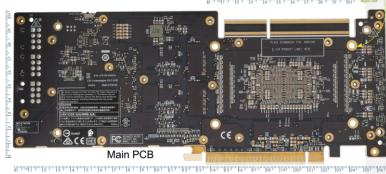

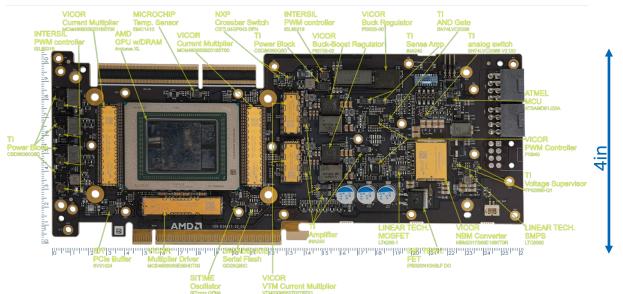

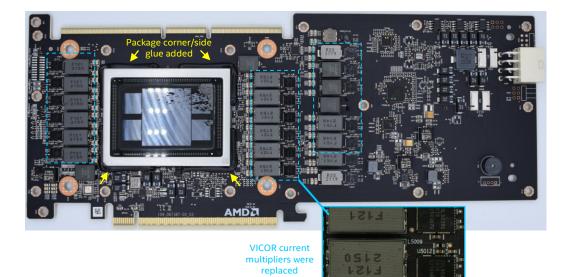

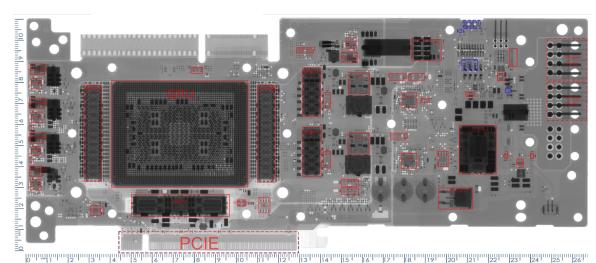

# MI100 & MI210 Board Images

10.3in

10.5in

intel

4.5in

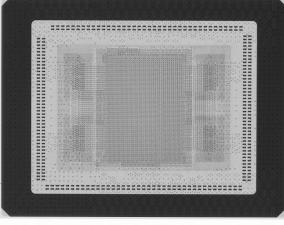

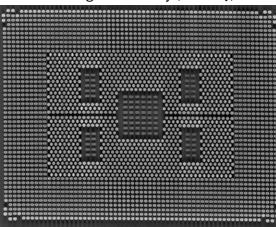

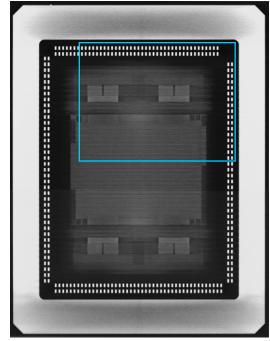

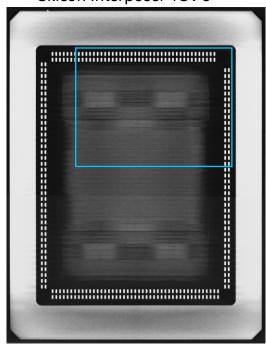

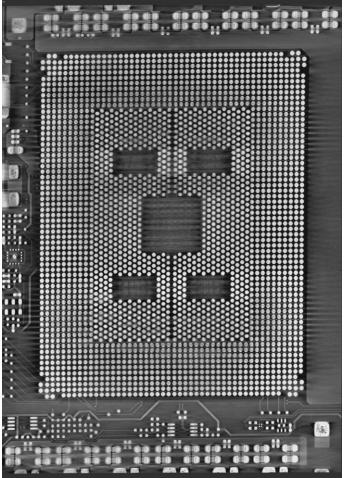

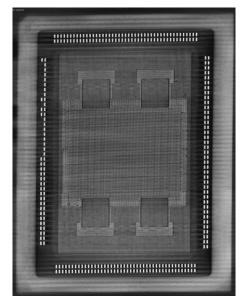

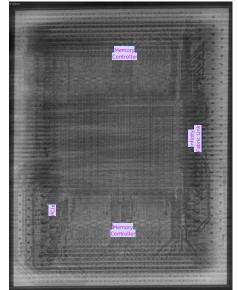

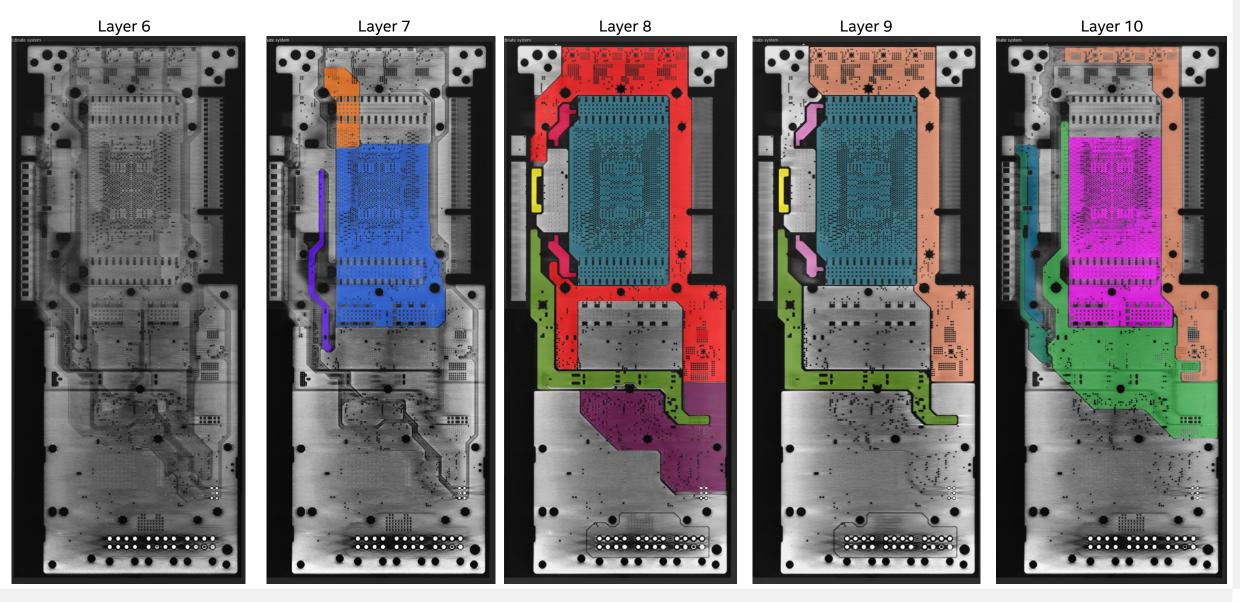

# PCB & Package 2D-Xray

Side Cross Section 16 layers (not to scale)

Front of PCB

Back of PCB

\* = saw/^duplexer

65mm

65mm

intel

M1100

ATTD Competitive

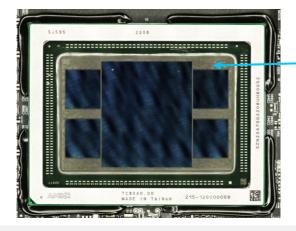

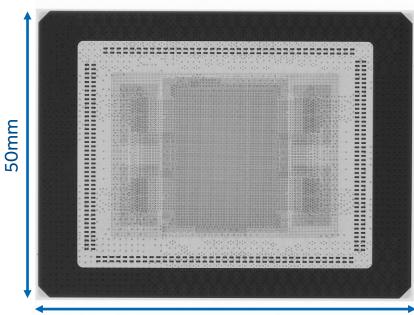

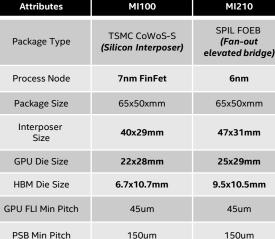

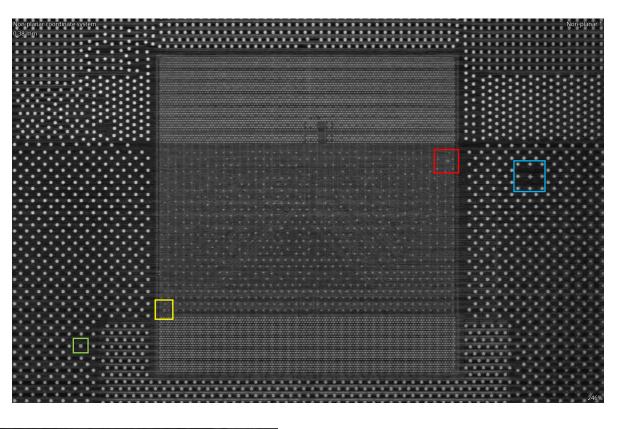

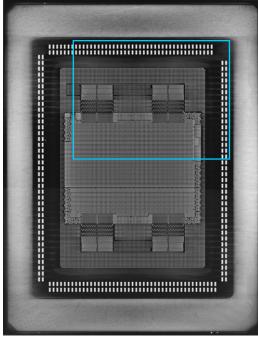

# Package Overview & Comparison

MI210

SPIL FOEB

(Fan-out

6nm

65x50xmm

47x31mm

MI100

Package Front Side

Package Back Side

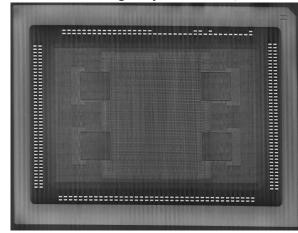

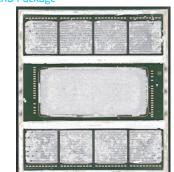

Package 2D Xray

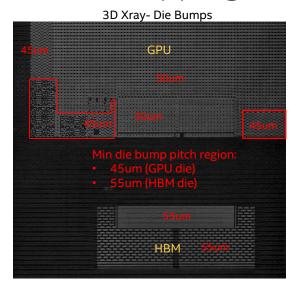

Package Front Side

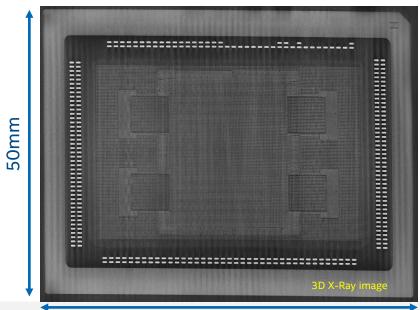

Package BGA Array (3D X-Ray)

Intel Confidential

Package Layout (3D X-Ray)

| Size                     |                  |                                     |

|--------------------------|------------------|-------------------------------------|

| GPU Die Size             | 22x28mm          | 25x29mm                             |

| HBM Die Size             | 6.7x10.7mm       | 9.5x10.5mm                          |

| GPU FLI Min Pitch        | 45um             | 45um                                |

| PSB Min Pitch            | 150um            | 150um                               |

| Min D2D Spacing          | 75um             | 125um                               |

| Substrate<br>Layer Count | 12 (5-2-5)       | 12 (5-2-5)                          |

| Core Thickness           | 1.2mm            | 1.25mm                              |

| BGA Count/ Pitch         | 2878/1mm         | 2878/1mm                            |

| DSC Type/Count           | 0201/ <b>332</b> | 0201/ <b>316</b>                    |

| LSC Type/Count           | 0204/88          | 0204/88                             |

| Stiffener Width          | 7mm, 5.2mm       | 3.6mm, 4.5mm                        |

| Stiffener thickness      | 0.7mm            | 1.5mm                               |

| Stiffener Material       | TBD              | Stainless steel<br>(Fe, Cr, Mn, Ni) |

|                          |                  |                                     |

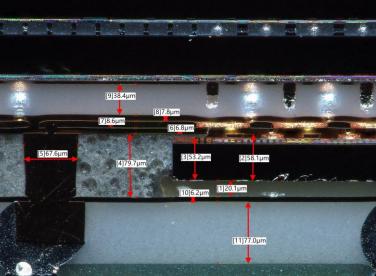

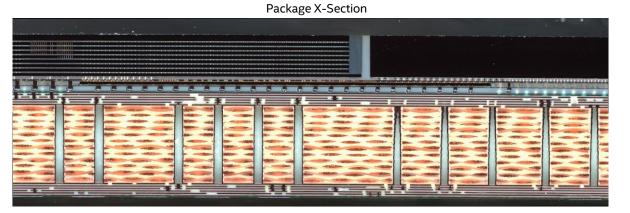

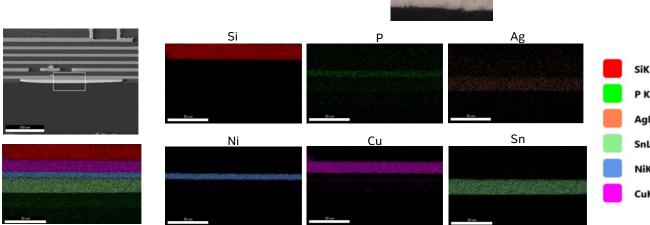

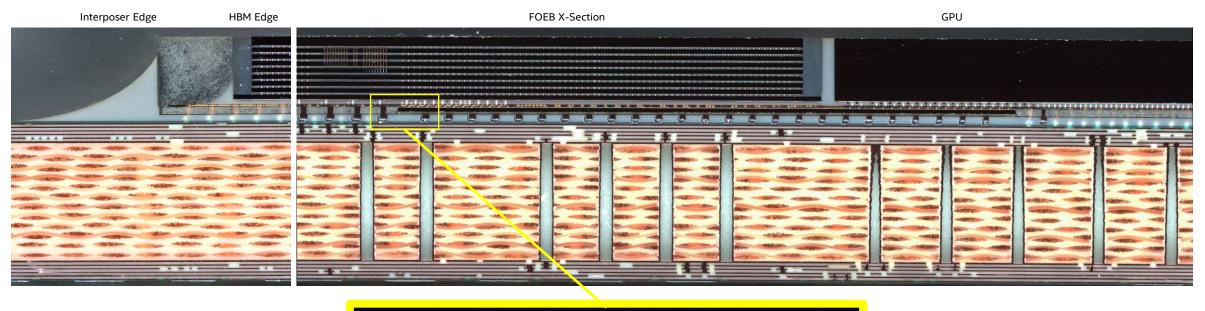

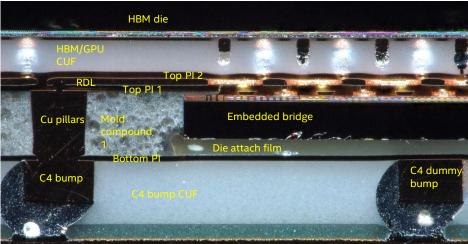

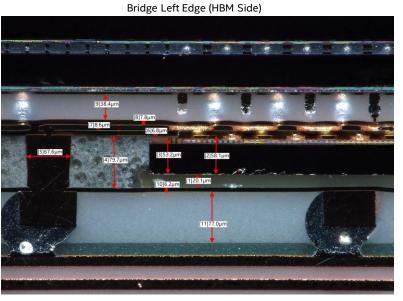

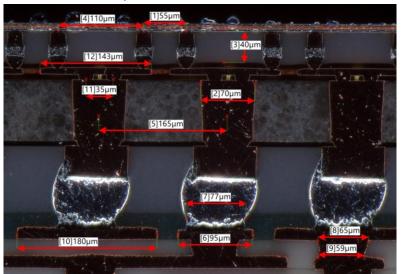

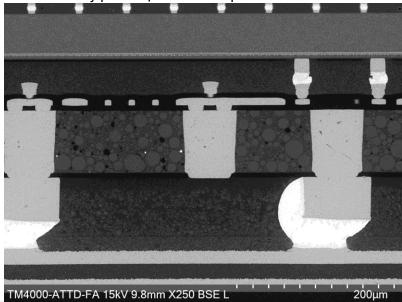

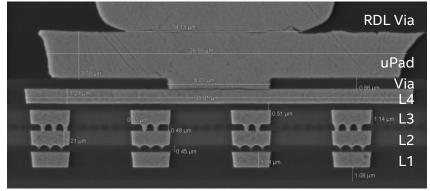

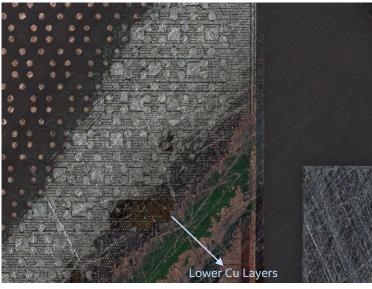

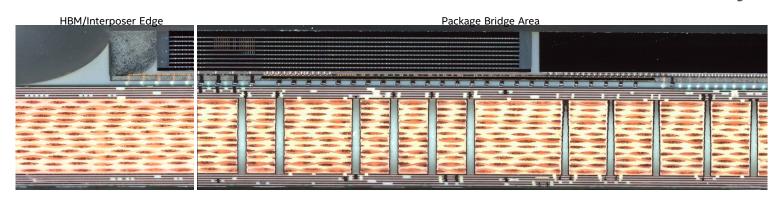

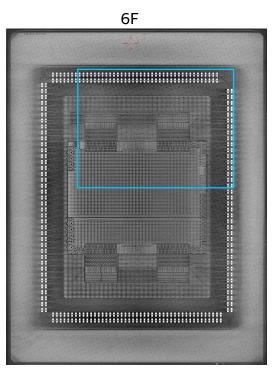

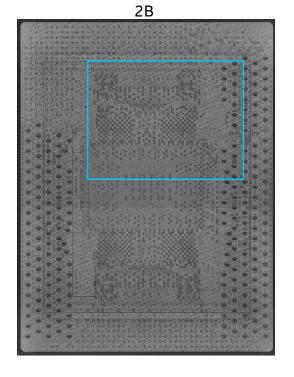

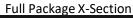

# MI210 Package X-Sections- Package Stackup

HBM/Interposer Edge

D2D Region

Interposer, Pillar & Bridge

- GPU & HBM thickness: 685um

- Die to interposer gap height: 38um

- Interposer 2P1M thickness: 24um

- Bridge Thickness: 60um

- DAF Thickness: 21um

- Bottom PI thickness: 6um

- PSB CGH: 77-84um

- Substrate Thickness: 1.7mm (1.2mm core)

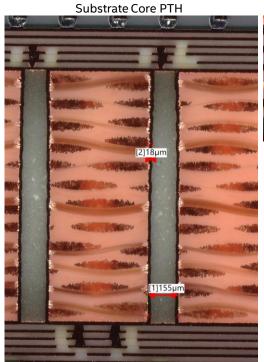

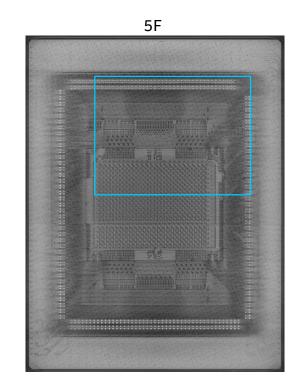

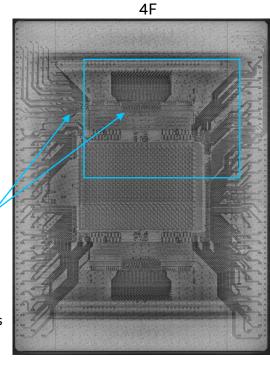

## 12-layer substrate

|            | 5-2-5)    |

|------------|-----------|

| Layer      | Thickness |

| FSR        | 19.3      |

| 6F         | 16.5      |

| Dielectric | 19.3      |

| 5F         | 17.1      |

| Dielectric | 24.8      |

| 4F         | 15.4      |

| Dielectric | 22.0      |

| 3F         | 16.5      |

| Dielectric | 24.3      |

| 2F         | 16.5      |

| Dielectric | 22.6      |

| 1FC        | 22.0      |

| Core       | 1250      |

| 1BC        | 22.8      |

| Dielectric | 22.8      |

| 2B         | 16.2      |

| Dielectric | 22.8      |

| 3B         | 15.2      |

| Dielectric | 22.8      |

| 4B         | 15.5      |

| Dielectric | 21.2      |

| 5B         | 18.5      |

| Dielectric | 22.2      |

| 6B         | 16.5      |

| BSR        | 19.8      |

|            |           |

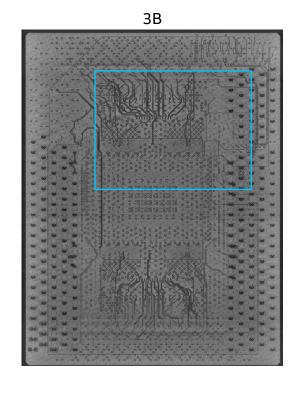

# MI210 Package X-sections- Substrate DRs

Substrate BGA Pad Ni

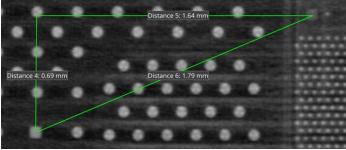

# MI210 Package Warpage

All warpage measurements were done with package mounted on the board

Thick corner glue was added for MI210 package mechanical support vs the MI100 that did not use any corner glue.

- Convex Package Shape

- Warpage= ~217um

### ATTD Competitive Analysis

# MI210 Package Warpage

# 2.5D Elevated Fanout Bridge Construction & Process Flow

Source: Anandtech

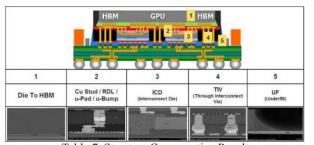

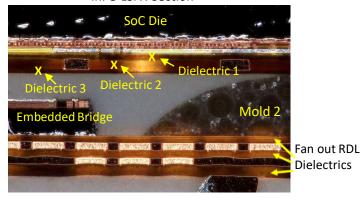

# FOEB Cross Section / Key Elements

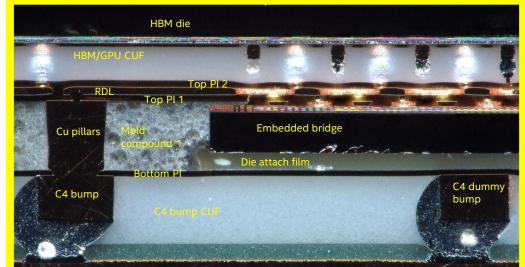

# AMD MI-210 Silicon Bridge Process Flow

Step 7: Litho PR/Pattern TV (terminal via) opening

Step 9:

PR removal

Step 8: RIE TV Opening

Step 10: PVD seed laver

(TiCu)

- Silicon wafer with >2.32um SiO<sub>2</sub>

- 1.24um thick Cu RDL (Damascene)

- 1.66um oxide, 0.41um dia via, 1.21um Cu (Dual Damascene)

- 4. 1.62um oxide, 0.41um dia via, 1.14um Cu (Dual Damascene)

- 5. 1.72um oxide, 0.41um dia via, 1.21um Cu (Dual Damascene)

- 6. 0.86um SiON, 8.25um via opening ———

|       | Step 11:   |

|-------|------------|

| Litho | PR/pattern |

|       | for Cu pad |

| этер | deposition on top of 4th Cu metal layer                               |  |

|------|-----------------------------------------------------------------------|--|

| 7    | Litho PR/Pattern TV (terminal via) opening                            |  |

| 8    | RIE TV opening (8.25um dia )                                          |  |

| 9    | Photo Resist removal                                                  |  |

| 10   | PVD seed layer (TiCu (standard) older TiWCu )                         |  |

| 11   | Litho PR/Pattern for Cu pad                                           |  |

| 12   | Cu plating ———                                                        |  |

| 12   | PR removal                                                            |  |

| 14   | Seedlayer removal (-> undercut)                                       |  |

| 15   | Asahi Low temp Cure Photo-Imageable PI → >45um scribe street openings |  |

| 16   | Bridge singulation                                                    |  |

| 17   | Pick and place bridge on carrier                                      |  |

| 18   | Molding bridge                                                        |  |

| 19   | Grinding bridge ( opening of Cu Pad B) (option + CMP)                 |  |

| 19a  | Option: electrical measurement                                        |  |

| 20   | Continue with 1st dielectric of RDL process                           |  |

Cartoon process flow starting after passivation

Step 15: Asahi LT Cure Photo-Imageable

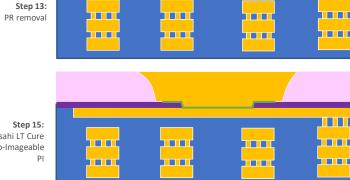

# Close-up look at bridge uPad and pasivation

Ejector pin needle mark

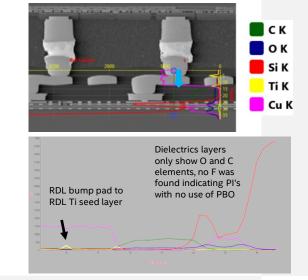

EDX did not detect Ti on sidewall, PI not present during plating

Ti seed etch undercut

SiON top dielectric Underlying DE areSiOx u

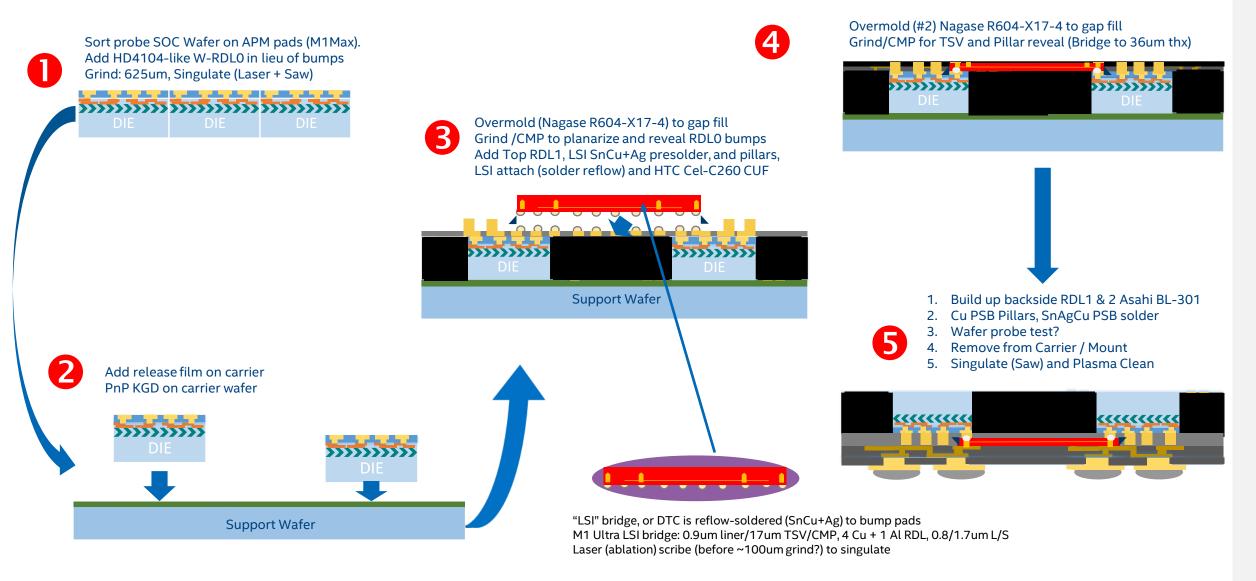

## MI210 FO-EB Process Flow Overview

Bridge die

(b) Organic interposer

(c) µPad and RDL2

(d) Logic and

(e) C4 bump

(f) Flip chip

Memory die

# ATTD Competitive Analysis

### Bridge fabrication flow

- 1. Silicon wafer with 2.32um SiO<sub>2</sub> 1.24um thick Cu RDL (Damascene)

- 2. 1.66um oxide, 0.41um dia via, 1.21um Cu (Dual Damascene)

- 3. 1.62um oxide. 0.41um dia via. 1.14um Cu (Dual Damascene)

- 4. 1.72um oxide, 0.41um dia via, 1.14um Cu (Dual Damascene)

- 5. 0.86um SiON, 8.25um via opening (and crack stop trench opening)

- 5. Deposit TiCu seed, PR/pattern/plate 4um Cu pad/ Strip PR and seed

- Spin/pattern ~4um Asahi Low temp cure photo-imageable PI

To pattern >45um scribe street openings after dicing

- 8. Flip / Mount on carrier tape

- 9. Thin wafer to 60um

- 10. Flip/Remount while attaching 21um Nitto Denko DAF, soft cure

- 11. Saw singulate

### Interposer process flow

a)-f) matched to SPIL publication

### a) Cu post and Bridge die

- Release film on glass carrier wafer

- 2. 6um Asahi Low temp cure photo-imageable Bottom PI

- 3. Pattern PSB via openings

- 4. Deposit TiCu seed/adhesion layer

- 5. Pattern/plate 70um dia/85um tall Cu pillars

- 6. Remove photoresist & seed layer

- Attach bridge with 21um Nitto Denko DAF and cure (3um misalignment noted on our sample)

### b) Organic interposer

- 1. Nagase R4604-17X-4 mold (likely exposed die mold style )

- 2. Grind/CMP Pillar & bridge pad reveal, mold and PI

- Possible bridge probing

### ) uPad and RDL2

- 1. Top PI 1/ pattern via and edge KOZ

- 2. TiCu seed layer, Pattern/plate Cu RDL Layer, PR & Seed layer removal

- Top PI 2/ pattern vias and edge KOZ

- 4. TiCu seed layer, Pattern/plate Cu uPads,

- 5. Plate Ni & Au caps on Cu uPads

- 6. PR & seed layer removal

### d) Logic and Memory Die

- GPU TCB chip attach (all solder on GPU)

- 2. HBM Mass Reflow chip attach (all solder on HBM)

- 3. Namics 462 CUF dispense/cure for HBM/GPU bumps and 125um gaps

- 4. Nagase R4604-17X-4 gap fill mold

### e) C4 bump

- Release from glass carrier

- 2. Flip wafer & remount onto ringframe (?)

- 3. Etch/clean release film

- 4. TiCu seed layer, Pattern/plate C4 Cu bumps

- 5. Plate Ni caps on C4 Cu bumps

- 6. PR & seed layer removal

### f) Flip chip

- 1. Remove from ringframe (?)

- Topside grind to target thickness

- 3 Wafer sort?

- 4. Flip wafer & mount onto ringframe (?)

- 5. Saw dice (step cut) from C4 bump side

- 6. PnP & reflow onto substrate, deflux

- 7. Namics 462 CUF dispense and cure

Flow and materials based upon ATTD teardown data

# Cross section through pillar and edge of bridge, HBM interconnect region (a) Cu post and Cu post (b) Cu post HBM die

Interposer – Die Bumps

C4, dummy die side uPad

Fig. 8. FO-EB Process Flow Out Embedded Bridge (FO-EB) Package Evaluation during the Process and Reliability Test

ECTC 2022 Paper: The Optimal Solution of Fan-

Molding compound

Molding compound

C4 Bump

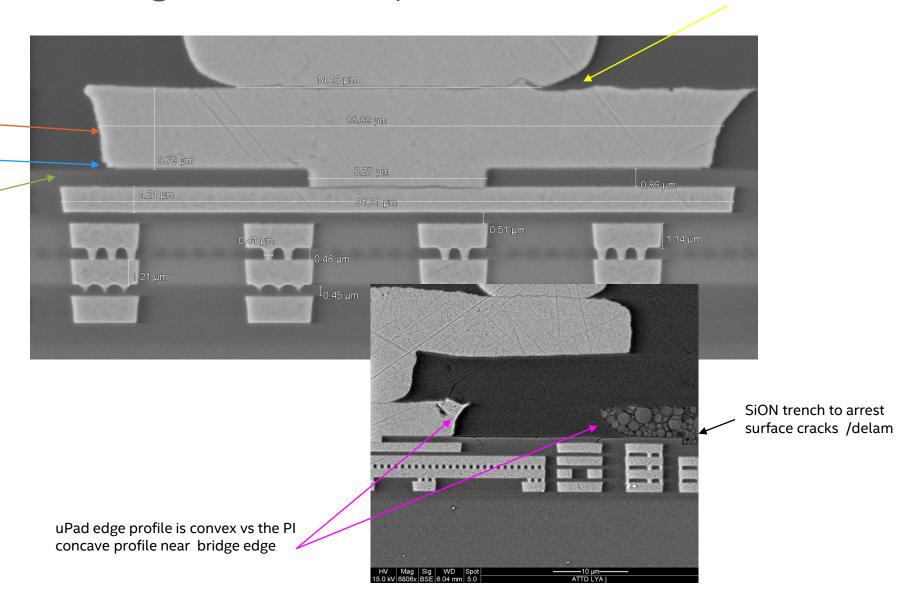

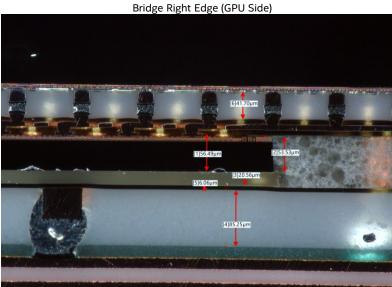

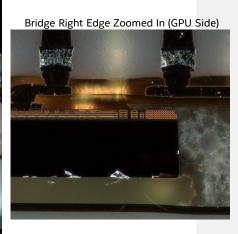

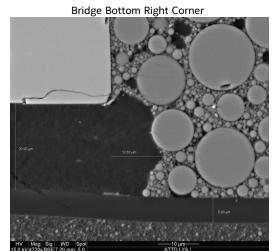

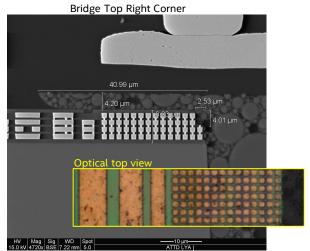

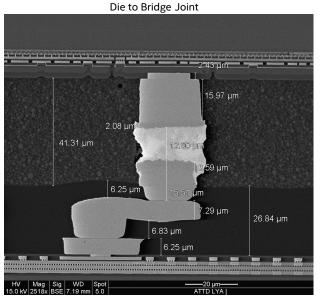

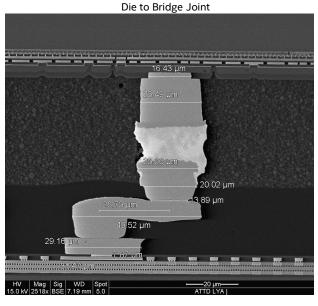

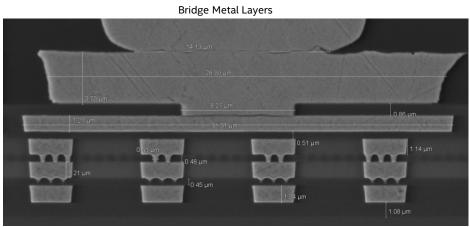

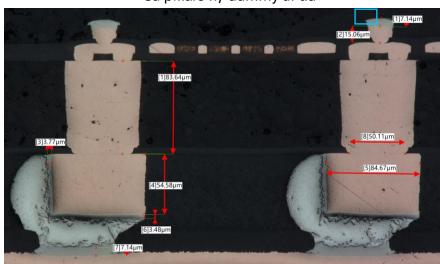

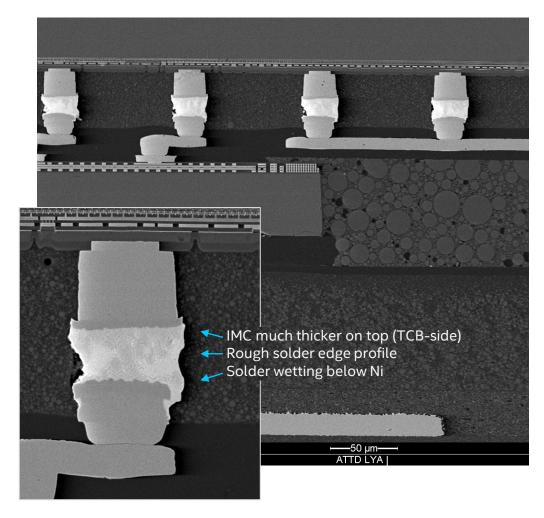

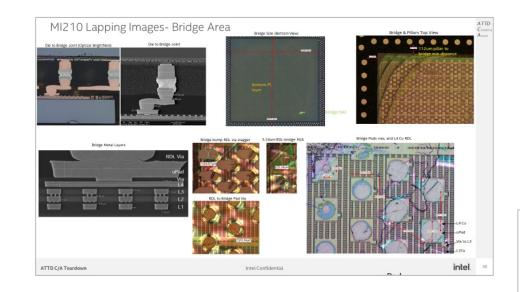

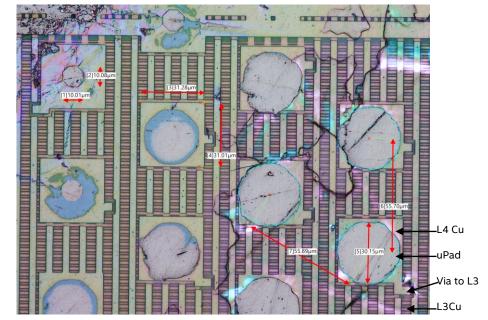

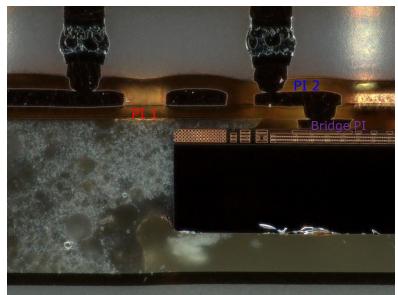

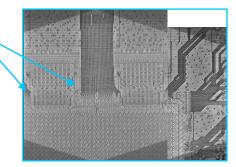

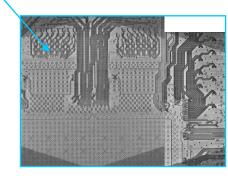

# MI210 FOEB X-Sections- Bridge Area

Bridge Left Edge Zoomed In (HBM Side)

# MI210 FOEB X-Sections- Bridge Area

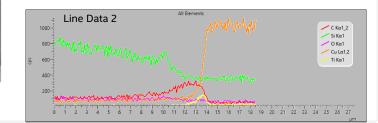

- HBM/GPU die bump height: 18um (16um Cu & 2um Ni)

- HBM/GPU die bump diameter: 25um

- Solder metallurgy: SAC based solder

- RDL side bump pad height: 15.5um (12um Cu & 3.5um Ni)

- RDL side bump pad dia: 24um

- Bridge area RDL via stagger: 25um

- RDL to bridge pad via dia: 23um

- Bridge pad dia: 30um

- Bridge pad to Cu layer 4 via:

- Bridge layer thicknesses: 1um Cu, 0.5um dielectrics

RDL to bridge pad Ti seed layer

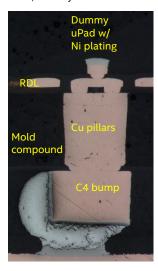

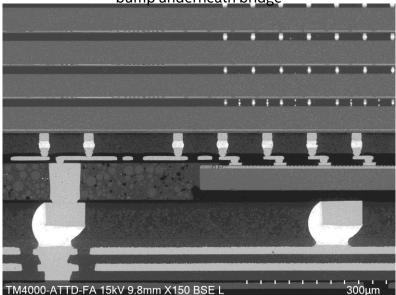

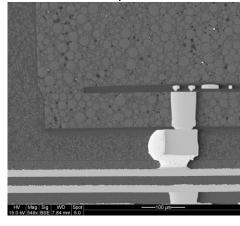

# MI210 FOEB X-Sections- Cu Pillars & C4 Bumps

ATTD

Competitiv

Analysis

27

Cu pillars w/ 2 vias & 2 uPads

Cu pillar w/ 1 via & 1 uPad/ Dummy C4 bump underneath bridge

Cu pillars w/ dummy uPad

Dummy pillar w/ no C4 bump connection

- RDL side uPads have 7um of Ni & 0.14um of Au plating

- Cu pillar diameter: 70um

- Cu pillar height: 83um

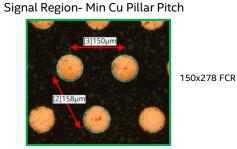

- Cu pillar min pitch: 150um (IO region)

- Cu pillars have 1 RDL via for signals, 2 or 3 RDL vias for PWR/GND

- C4 bump size- Oval shaped 89x66um

- Min C4 bump pitch- 150um

Step-cut saw final singulation with 100um top RDL KOZ

# MI210 FOEB X-sections- Cu Pillars & C4 Bumps

28

Ti seed layer peak is wider beneath pillar via vs outside of pillar region, indicating the first pillar seed layer was not removed as part of the carrier debond process

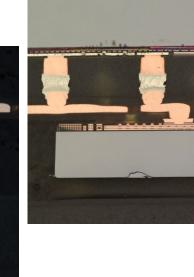

# Chip Attach: HBM=Mass Reflow vs GPU=TCB

HBM to FOEB

GPU to FOEB: characteristics of TCB

# SPIL FOEB vs TSMC InFO\_L

### ATTD Competitive Analysis

### **SPIL FOEB**

# SOC Chip uBumps/RDL0 TRDL Cu Pillars/ SI bridge C4 Bumps Substrate HV Mag Sig WD Spot — 100 µm— 15.0 kV 496x BSE 7.06 mm 5.0 ATTD LYA

# TSMC InFO\_L

Die are offset, x-section is thru center of bumps on left die only. Central crack is x-section artifact. TSV is from a different location, shown here for illustrative purposes

- SPIL embeds bridge between pillars and builds the interposer before active die TCB or mass reflow attach "Chip –Last".

- TSMC reconstitutes active die on a carrier wafer "Chips-first", builds an RDL and pillars, then reflows bridge before finishing interposer.

- C4 Bumps land directly on FOEB pillars; adding bridge TSVs would likely drive significant architectural changes. InFO\_L uses 2 bottom-side RDLs likely to provide stress relief for bridge TSVs.

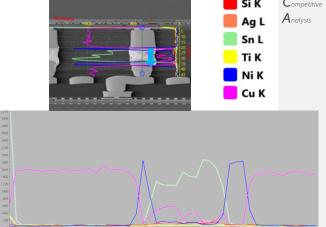

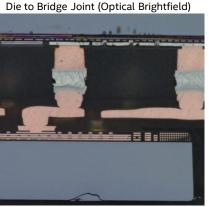

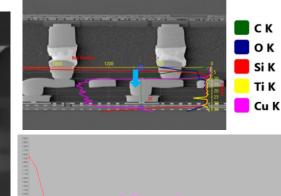

# FOEB Planar Images, DRs & Routing

Die to Bridge Joint (Optical Brightfield)

Die to Bridge Joint

6.43 µm

6.43 µm

20.02 µm

38.9 µm

29.16 µm

29.16 µm

29.16 µm

20.02 µm

38.9 µm

Bridge Metal Layers

Bridge bump RDL via stagger

RDL to Bridge Pad Via

5.34um RDL-bridge M/A

Bridge Pads vias, and L4 Cu RDL

# MI210 RDL Details- Lapping Images

3D Xray- RDL Layer

Mesh grid L/S- 10/20um

Shape-shape min L/S- 9um

Min "Power Bridge" L/S- 9/10um

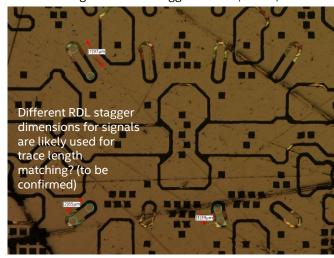

Signal RDL Via Staggers- 40um, 65um, 97um

Wider mesh is used for Power and Ground and a few 9um traces connect to GPU's HBM IO HIP directly to BGA pads, probably for test access.

# Bridge Power Delivery

## Power is primarily delivered by topside RDL

ATTD

$C_{\it ompetitive}$

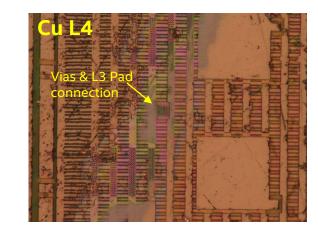

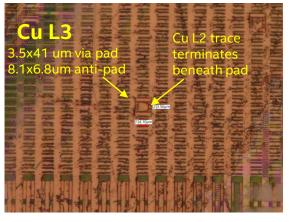

# HBM2E Signal Trace Details

ATTD Competitive Analysis

Diff pairs RDQS WDQS

1.2um HBM2e signal traces are shielded with 0.6um ground traces separated from the mesh

No vias above L2 traces

## AMD MI-210 HBM Bridge Routing

No guard trace

between WDQS &

RDQS diff pair

traces

## P/G shapes and Sort Pads

ATTD Competitive Analysis

PD Cu Pillars 164um pitch

PD uBumps 56um FCS

PD shapes 13.2um space

Sort pads and pillars are corresponding to uBump voids

GPU uPads and APM Layer

50x50um Sort pads on GPU APM

## ATTD

## AMD MI-210 Bridge Alignment Fiducials

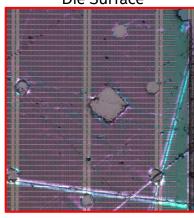

Die Surface

Interposer Surface

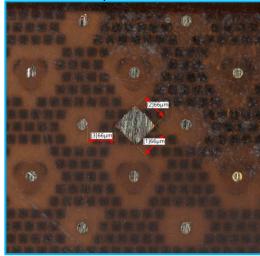

#### MI210 Lapping Images- Bump Size & Pitches

Die Bumps

RDL test pads- 200um diameter

RDL Test Pads at uPad level

Min Die Bump Pitch & Diameter

Package X-Section View

C4 bump size: Oval shaped 89x66um Min C4 Bump Pitch- 150um (GPU side), 170um (HBM side)

## Cu Pillars/C4 Dummy Bumps

#### AMD MI210 FOEB Materials Summary

#### FOEB X-Section

A-Section FOEB Materials

| HBM/GPU         | BM die   | 0       | The second secon | - D   | A. Florida |   | A. Carrier |

|-----------------|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|---|------------|

| CUF             | Top PI 2 |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -     | 124        |   |            |

| To              | p Pl 1   |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | -          |   | -          |

| Cu pillars Mold | und 1    | Eml     | bedded b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |            |   |            |

|                 |          | Die att | ach film                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19.17 |            |   |            |

| C4 bump         | om PI    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |            | A | C4 dummy   |

|                 |          |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |            |   | bump       |

| 15 /            |          |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |            |   |            |

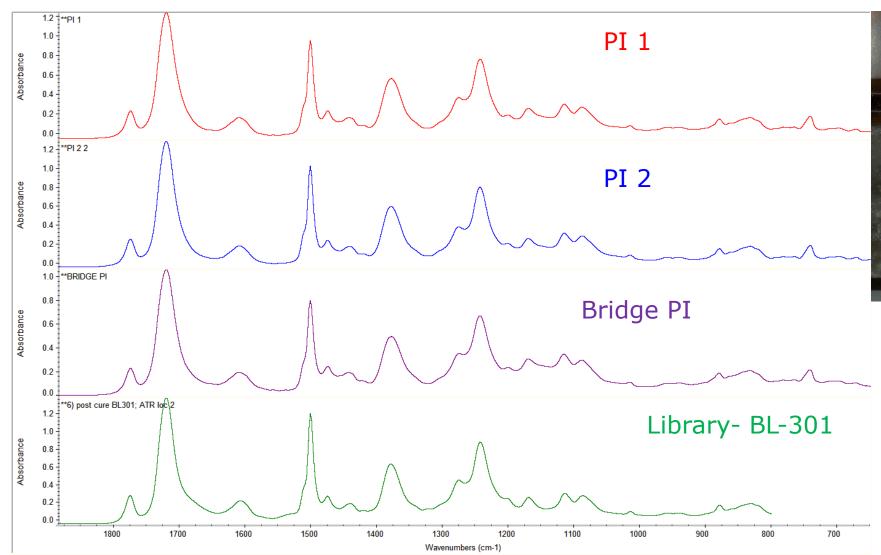

| FTIR Results                    | Package Material         |

|---------------------------------|--------------------------|

| Asahi BL301 low temp<br>cure PI | Bottom PI                |

| Asahi BL301 low temp<br>cure PI | Bridge PI                |

| Asahi BL301 low temp<br>cure PI | Top PI1                  |

| Asahi BL301 low temp<br>cure PI | Top PI2                  |

| Nitto Denko DAF                 | DAF                      |

| Nagase R4604-X17-4              | Mold 1                   |

| Nagase R4604-X17-4              | Mold 2                   |

| Namics 462C                     | Die CUF                  |

| Namics 462C                     | Interposer (C4 bump) CUF |

|                                 |                          |

The PI & mold materials match with the same materials seen in the M1 Ultra

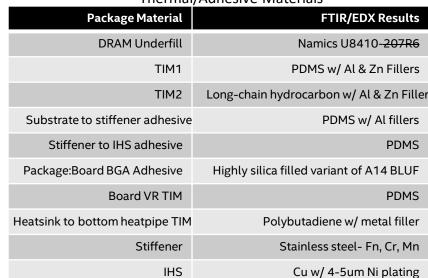

#### Thermals/Adhesives

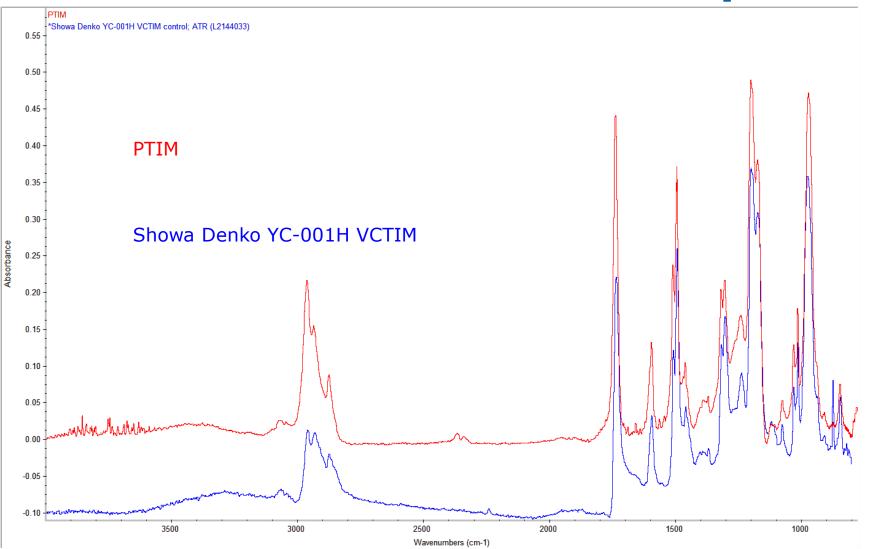

| Package Material    | FTIR/EDX Results                                        |

|---------------------|---------------------------------------------------------|

| TIM 1.5             | Showa Denko YC-001H<br>VCTIM                            |

| Stiffener adhesive  | Epoxy material similar to<br>Ryzen 9 stiffener adhesive |

| Package corner glue |                                                         |

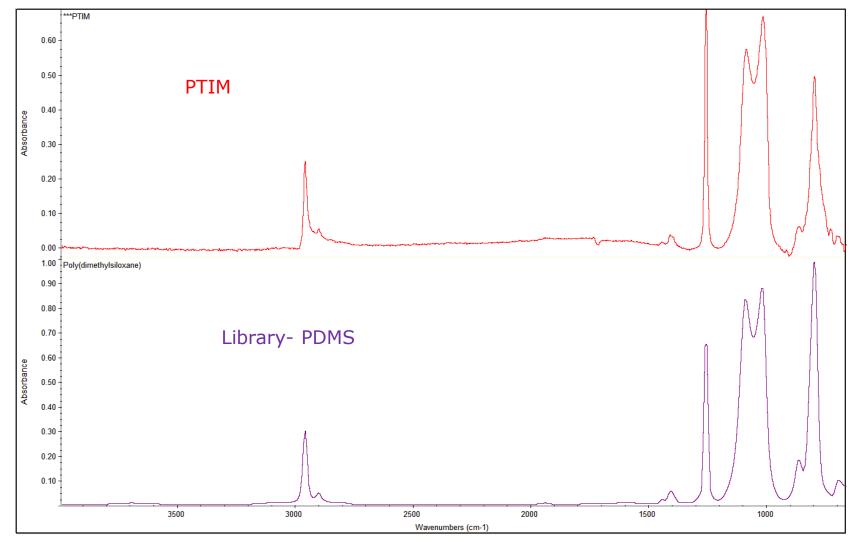

| Board VR TIM        | PDMS                                                    |

#### Solder Materials

| Connection                         | EDX Results |

|------------------------------------|-------------|

| Die bumps (Die to RDL)             | SAC         |

| C4 bumps (Interposer to substrate) | SAC         |

| BGA's (Substrate to board)         | SAC         |

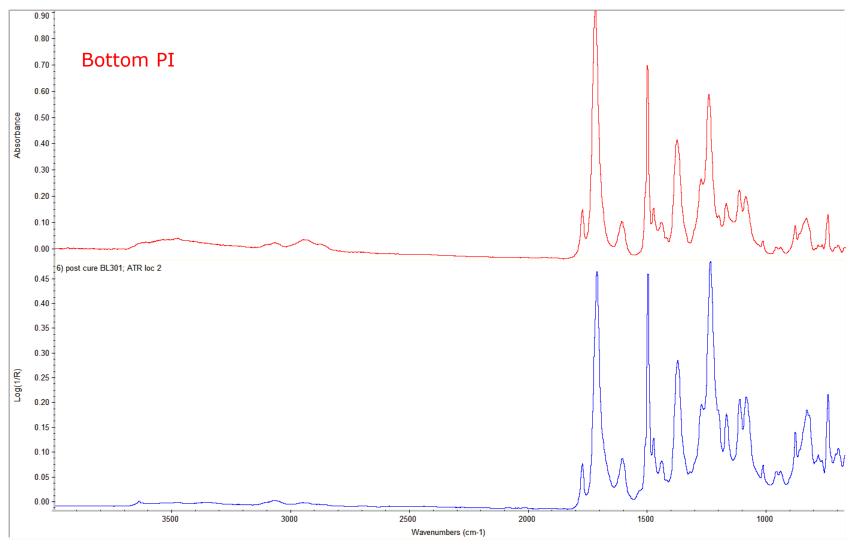

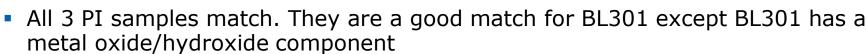

#### **Bottom PI**

- The bottom PI is a very good match for BL301.

#### **Polyimides FTIR spectra**

All 3 PI samples match. They are a good match for BL301 except BL301 has a metal oxide/hydroxide component

#### **Polyimides FTIR spectra**

#### **Polyimides FTIR spectra**

All 3 PI samples match. They are a good match for BL301 except BL301 has a metal oxide/hydroxide component

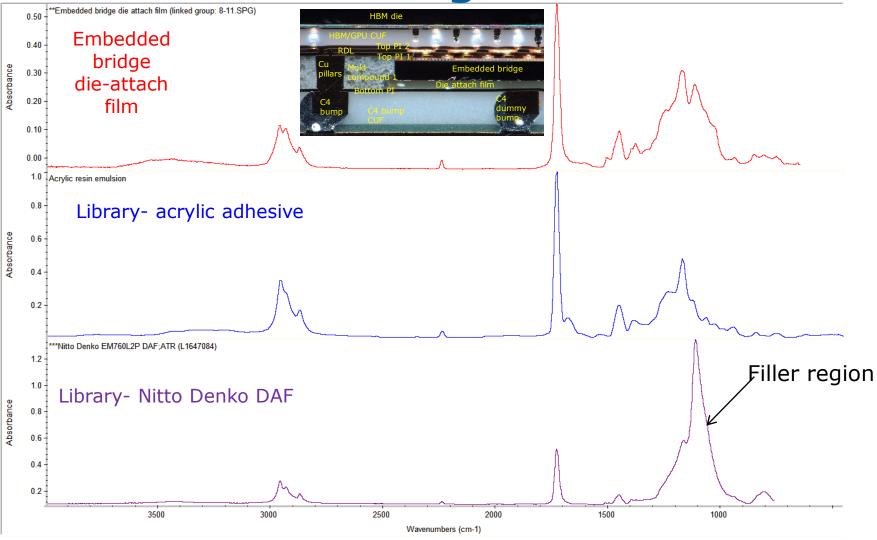

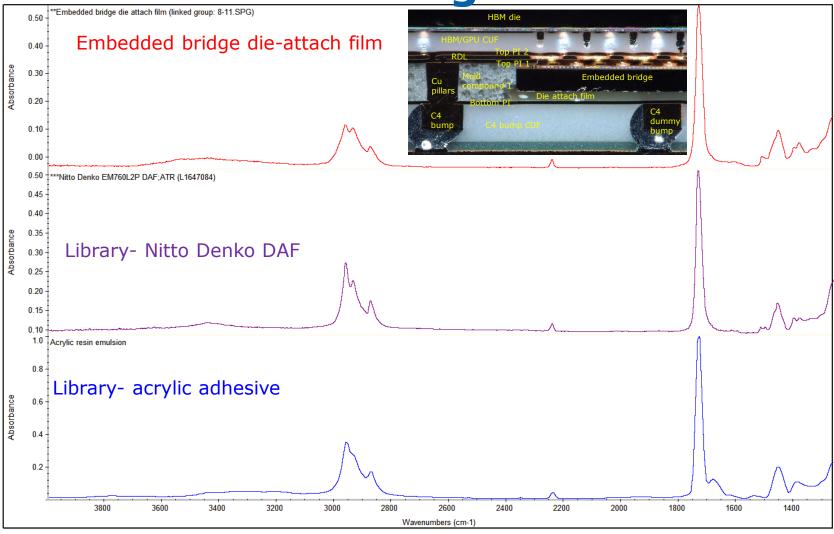

Embedded bridge die-attach film

The Embedded bridge die-attach film non-filler region is a very good match for a Nitto Denko DAF.

Embedded bridge die-attach film

The Embedded bridge die-attach film non-filler region is a very good match for a Nitto Denko DAF.

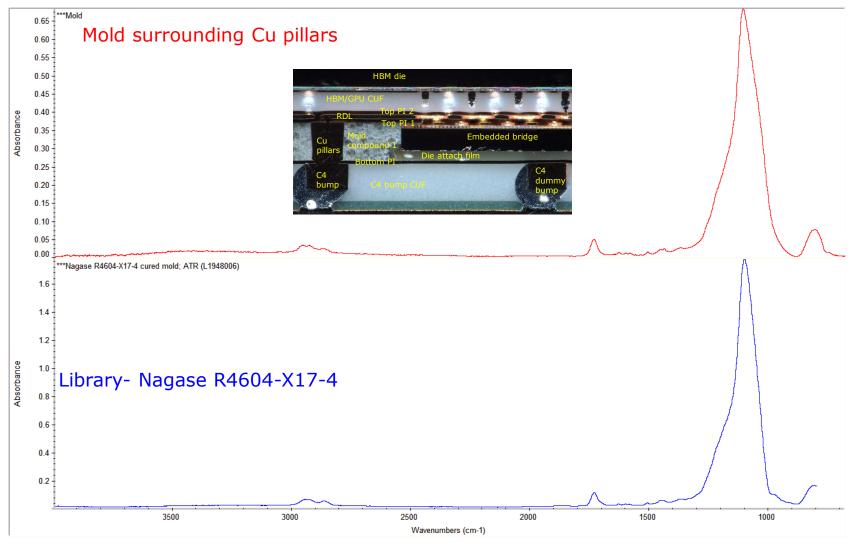

## **Mold Compound 1**

The mold is a very good match for Nagase R4604-X17-4.

#### **Mold Compound 1**

- The mold is a very good match for Nagase R4604-X17-4.

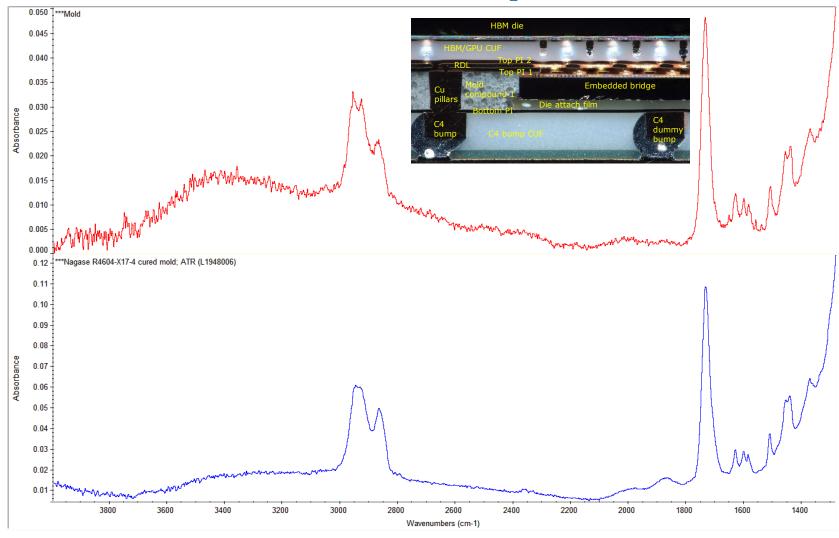

## Mold Fill 2 FTIR spectra

• The Mold Fill 2 is a very good match for Nagase R4604-X17-4

## Mold Fill 2 FTIR spectra

The Mold Fill 2 is a very good match for Nagase R4604-X17-4

#### **CUF FTIR spectra**

Both CUF samples are a very good match for Namics 462C

#### **CUF FTIR spectra**

Both CUF samples are a very good match for Namics 462C

#### **Stiffener Adhesive**

The 2 locations of the adhesive have the same material, an epoxy material, and is a good match for prior Ryzen 9 stiffener adhesive

2022 IEEE 72nd Electronic Components and Technology Conference (ECTC)

#### The Optimal Solution of Fan-Out Embedded Bridge (FO-EB) Package Evaluation during the Process and Reliability Test

Vito Lin, David Lai, Yu-Po Wang

Cooperate R & D, Siliconware Precision Industries Co. Ltd.

No. 153, Sec. 3, Chung-Shan Rd. Tantzu Taichung 427, Taiwan, R.O.C.

Email: chichshenglin@spil.com.tw

Tel: 886-4-25341525 ext 6708, Fax: 886-4-25325030

2022 ECTC paper showed they may have used 2 different stiffener adhesives & unique dispense patterns, but FTIR results & optical images showed no sign of this

Fig. 12. Adhesive Coverage and Adhesive Pattern Diagram

| Exp       | perimental D    | OE                           | Package warpage       | TCT results |

|-----------|-----------------|------------------------------|-----------------------|-------------|

|           | Type A          | 1.00X                        | EMC crack             |             |

|           | Material        | Type B                       | 1.31X<br>(Copl. Fail) | Pass        |

| Adhesive  | Coverage        | Less<br>*1pp A<br>Coverage I | 1.1 <b>2</b> X        | Pass        |

| Adilesive | Pattern         | #1;se A #1;se 8              | 1.11X                 | Pass        |

| Pattern   | #1;po A #1;po 8 | 1.16X                        | Pass                  |             |

Table V. Experimental Results

#### **Die TIM FTIR Spectra**

The PTIM is a very good match for Showa Denko YC-001H VCTIM

Post heatsink removal TIM BLT is 330-345um

#### **Current Multiplier Components PTIM FTIR Spectra**

The PTIM is a very good match for PDMS

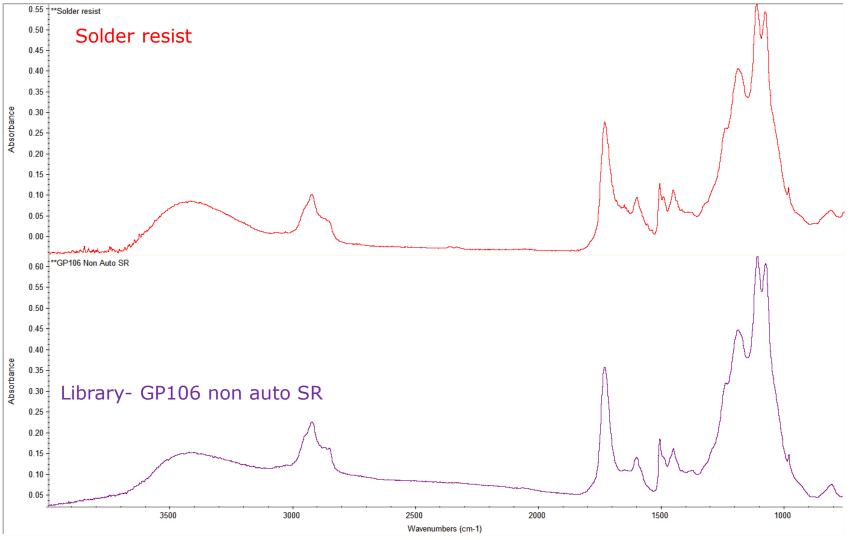

#### **Substrate solder resist**

- The Solder resist is a good match for prior GP106 non auto SR

#### **Board Overview**

| Board Attribute                                                     | AMD MI100                                  | AMD MI210                                  |

|---------------------------------------------------------------------|--------------------------------------------|--------------------------------------------|

| PCB Vendor ID                                                       | Advanced Micro Devices Inc.<br>Model: D343 | Advanced Micro Devices Inc.<br>Model: D673 |

| Board Type                                                          | 3                                          | 4                                          |

| Board Dimensions (mm)                                               | 261 x 110                                  | 264 x 96.5                                 |

| Layer Count                                                         | 16                                         | 14                                         |

| SLI Type                                                            | BGA                                        | BGA                                        |

| SLI metallurgy                                                      | TBD                                        | SAC                                        |

| BGA Pad Dia (um)                                                    | 530                                        | 695                                        |

| BGA Pad SRO                                                         | 690                                        | 795                                        |

| Min Trace L/S                                                       | 88/100                                     | 88/110                                     |

| uVia Top/Bottom Dia                                                 | n/a                                        | 135/115                                    |

| Primary Drill Dia                                                   | 260                                        | 260                                        |

| Backdrill Dia                                                       | n/a                                        | n/a                                        |

| Backdrill Depth                                                     | n/a                                        | n/a                                        |

| Backdrill Plugging                                                  | n/a                                        | n/a                                        |

| Backdrill Min Pitch                                                 | n/a                                        | n/a                                        |

| BGA Adhesive                                                        | n/a                                        | Corner Glue, FTIR pending                  |

| Adhesive Height >50% of substrate?                                  | n/a                                        | Yes                                        |

| Adhesive spread to adjacent components?                             | n/a                                        | Yes                                        |

| Adhesive spread                                                     | n/a                                        | ???                                        |

| Adhesive hardness                                                   | n/a                                        | ???                                        |

| Adhesive transparent or opaque? Color?                              | n/a                                        | Black                                      |

| Smallest passive component                                          | ???                                        | ???                                        |

| Min component spacing<br>(passive-passive, bga-bga,<br>bga-passive) | ???                                        | ???                                        |

| RF/EMI shielding types used                                         | n/a                                        | n/a                                        |

# II-100

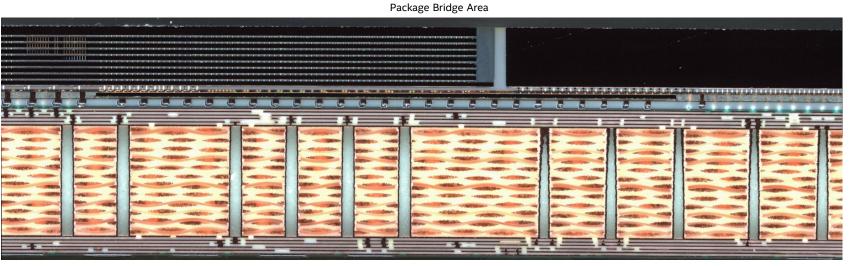

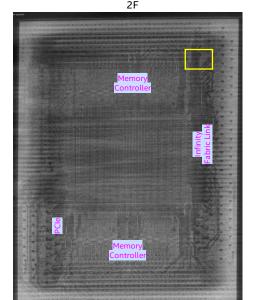

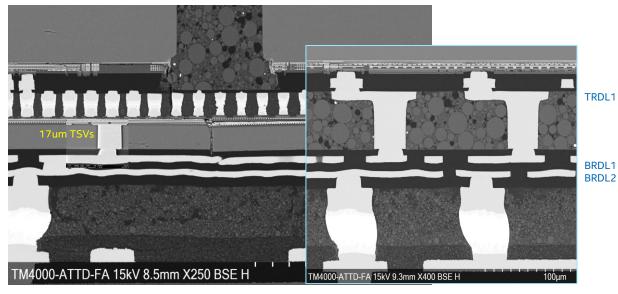

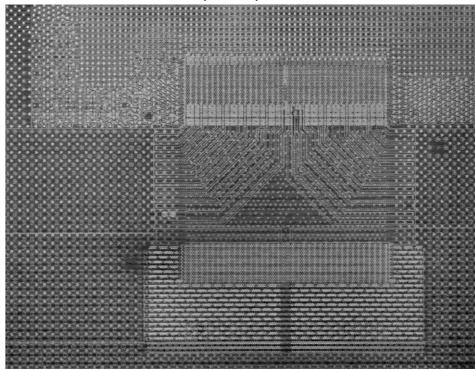

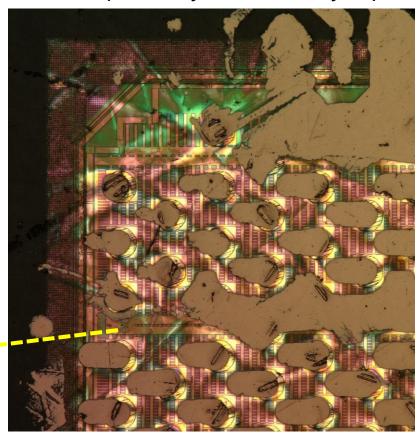

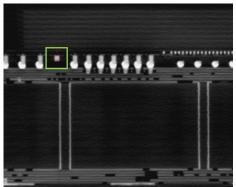

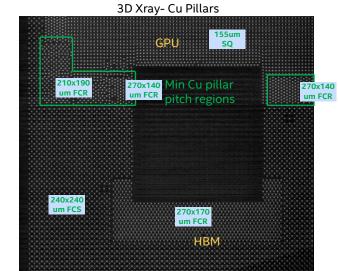

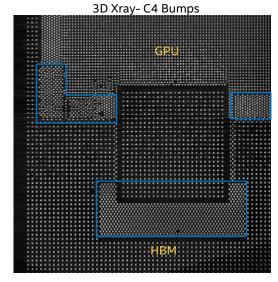

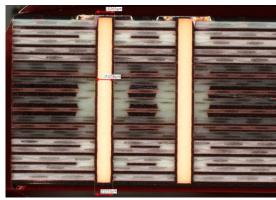

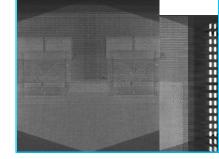

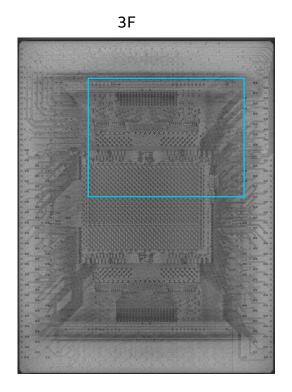

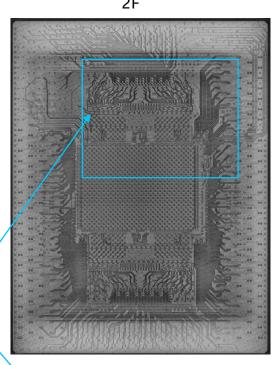

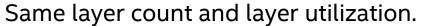

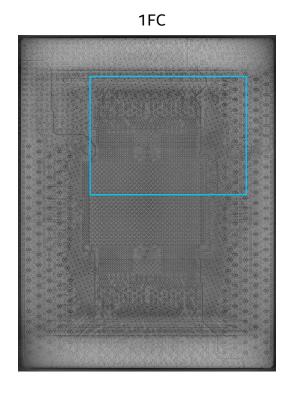

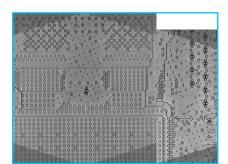

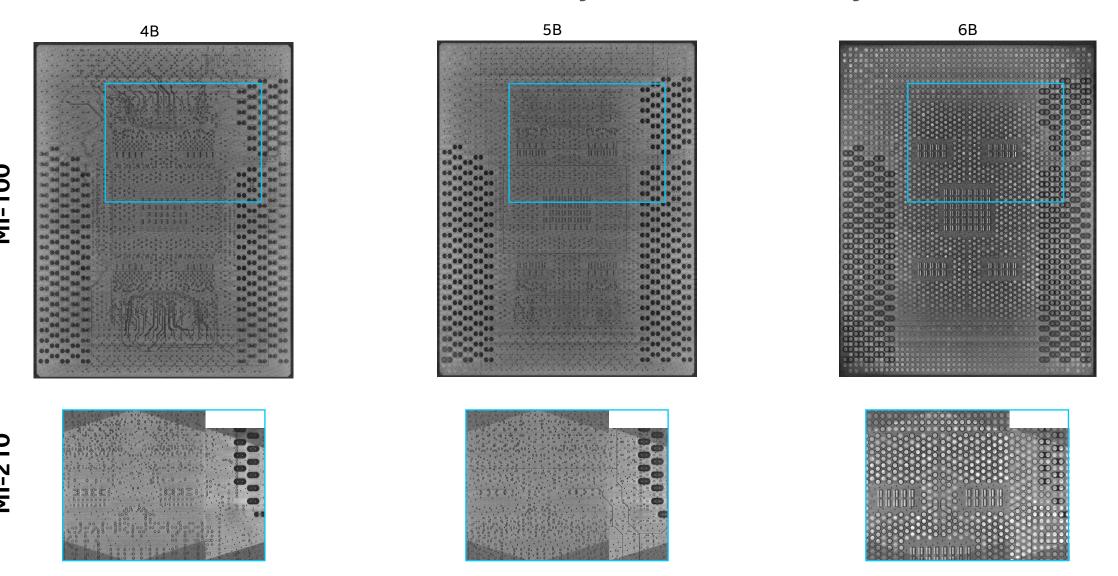

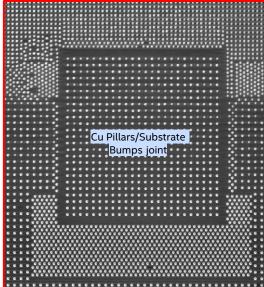

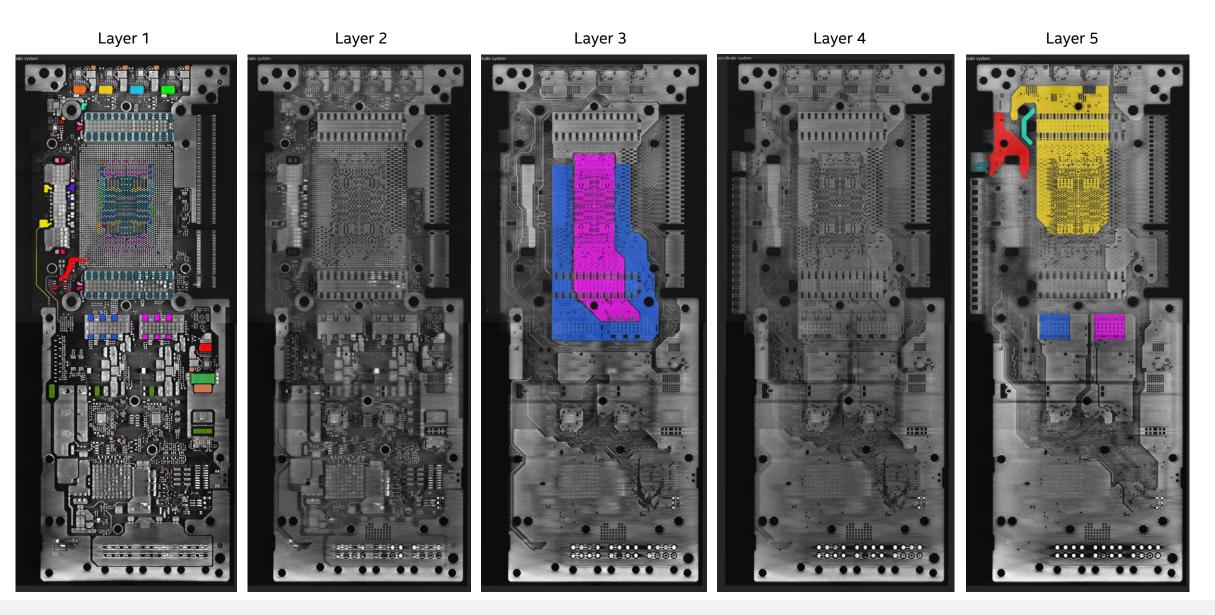

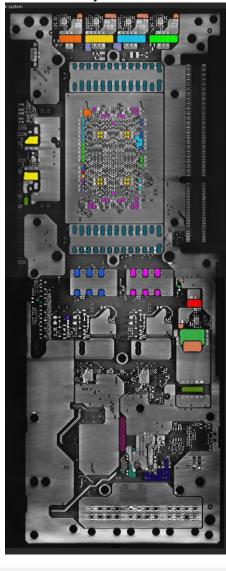

## MI100 vs MI-210 - Substrate Layers - 3D X-Ray

Silicon Interposer TSV's

**RDL** Layer

Cu Pillars/Substrate Bumps

Die attach Film

MI-100

Same layer count and layer utilization.

HBM2E DA drops straight down to substrate on both interposer technologies.

**4-100**

Same layer count and layer utilization.

Same layer count and layer utilization. Power planes have similar shapes.

## MI-210 – Die Bridge area – 3D X-Ray

## AMD MI-210 Board Routing

#### AMD MI-210 Package Routing

Cu Pillars/Substrate Bumps

2F

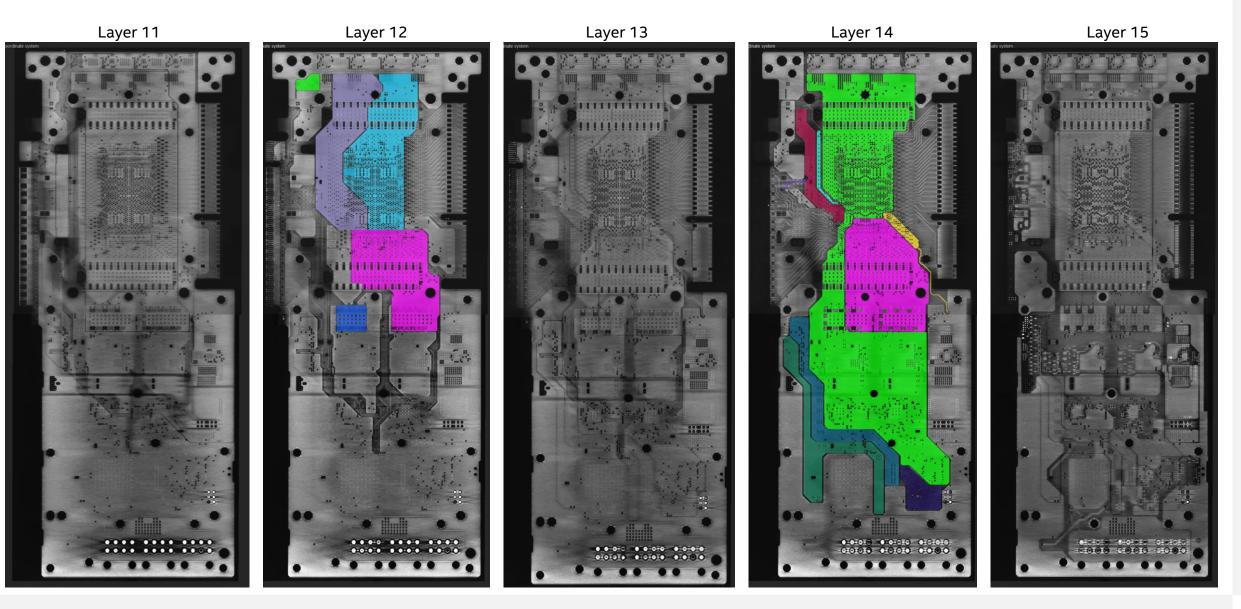

## MI100 Board Power Delivery

## MI100 Board Power Delivery

## MI100 Board Power Delivery

Layer 16

## Back-up Information

73

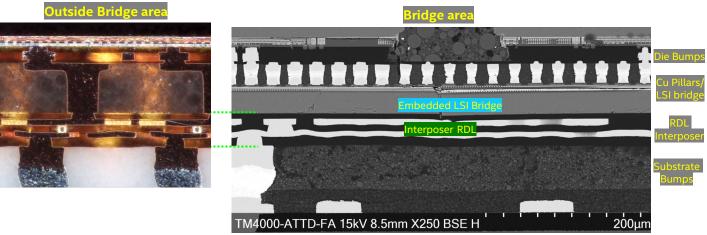

#### SPIL FOEB vs TSMC InFO\_L

#### ATTD Competitive Analysis

#### **SPIL FOEB**

# SOC Chip uBumps/RDLO TRDL Cu Pillars/ SI bridge C4 Bumps Substrate

#### TSMC InFO\_L

Die are offset, x-section is thru center of bumps on left die only. Central crack is x-section artifact. TSV is from a different location, shown here for illustrative purposes

- SPIL embeds bridge between pillars and builds the interposer before active die TCB or mass reflow attach "Chip –Last".

- TSMC reconstitutes active die on a carrier wafer "Chips-first", builds an RDL and pillars, then reflows bridge before finishing interposer.

- C4 Bumps land directly on FOEB pillars; adding bridge TSVs would likely drive significant architectural changes. InFO\_L uses 2 bottom-side RDLs likely to provide stress relief for bridge TSVs.

# Apple Mac Studio Systems with M1 Ultra SoC InFO\_L Analysis

WW27, 2022 Report rev D

Jose Perez, Tom DeBonis, Ivan Garcia, Justin Berg

Ack: Susan Garcia (3D X-Ray), KC Liu, Derek Hetherington

## Apple M1 Ultra

#### ATTD Competitive Analysis

#### Cu TMV Pillars Outside Bridge area

SOC Chip

RDL0 TRDL1

Cu Pillars/ LSI bridge

> BRDL1 BRDL2

Substrate Bumps

#### Bridge area

Die are offset, x-section is thru center of bumps on left die only. Central crack is x-section artifact. TSV is from a different location, shown here for illustrative purposes

#### InFO-LSI Process Flow Overview

Material identification from EDX, FTIR and NanoIR

#### InFO LSI, FCBGA & Thermal/Adhesive Package Materials Summary

#### ATTD Competitive Analysis

78

Solder Materials

| Connection                     | EDX Results                |  |  |

|--------------------------------|----------------------------|--|--|

| LSI Bridge to SoC              | SAC                        |  |  |

| Substrate to RDL<br>Interposer | SAC                        |  |  |

| Board to Substrate             | Sn, Ag4%, Bi 3%<br>non-LTS |  |  |

**BGA** Adhesive

InFO LSI X-Section

InFO LSI Materials

| Package Material                                         | FTIR/Nano-IR Results                                          |

|----------------------------------------------------------|---------------------------------------------------------------|

| SoC Dielectric 1                                         | FTIR similar to HD4104 PI                                     |

| SoC Dielectric 2                                         | FTIR similar to HD4104 PI                                     |

| SoC Dielectric 3<br>(Top RDL 1)                          | Nano-IR: Polyimide<br>(Peaks match HD4104 in FTIR<br>library) |

| Bridge CUF                                               | HTC Cel-C260                                                  |

| Mold 1                                                   | Nagase R604-X17-4                                             |

| Mold 2                                                   | Nagase R604-X17-4                                             |

| BRDL Interposer Dielectrics<br>(Fan out RDL dielectrics) | Asahi BL-301 low temp<br>cure Polyimide                       |

| BRDL Interposer Bump CUF (2<br>dispenses)                | Namics U8410-302 (both dispenses)                             |

Thermal/Adhesive Materials

ATTD C/A Teardown Intel Confidential intel

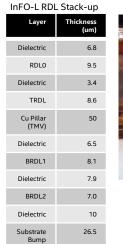

## InFO-L vs InFO PoP Design Rules

M1 Ultra: InFO-L

A15: InFO PoP

| Dielectric | 4.5 |

|------------|-----|

| RDLO       | 5.1 |

| Dielectric | 4.5 |

| RDL1       | 4.9 |

| Dielectric | 7   |

| RDL2       | 3.5 |

| Dielectric | 7   |

|            |     |

Dielectric

InFO PoP RDL Stack-up

Thickness

InFO-L Cu RDLs are thicker than InFO-PoP, other DRs are ~same

| Dimension                                  | M1 Ultra InFO-L                                                                                   | A15 InFO                                                                       |

|--------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Fan Out Area                               | 45.8x17.7mm                                                                                       | 13 x 14.8mm                                                                    |

| RDLO Die Bump Via Size                     | Bridge Area: 13um, Pad-<br>23um<br>Outside of Bridge: 20um,                                       | 25um, Pad-50um                                                                 |

|                                            | Pad-40um                                                                                          |                                                                                |

| RDLO-RDL1/RDLO-TRDL Via Size               | Bridge: Bottom- 8um, Top-<br>11um, Pad-16um<br>Outside of Bridge: Bottom-<br>28um, Top-31um, Pad- | Bottom-20, Top-25, Pad-<br>35                                                  |

| TMV (Cu Pillar) Dia                        | 40um<br>40um                                                                                      | Top-150, Middle-124,<br>Bottom-150                                             |

| TSV Size:                                  | 15um                                                                                              | N/A                                                                            |

| Pillar-BRDL1 Via Size                      | Bottom-25um, Top-30um,<br>Pad-38um                                                                | Bottom-45um, Top-50um                                                          |

| BRDL 1-2 Via Size                          | Bottom-27um, Top-32um                                                                             | Size 1: Bottom-35, Top-40,<br>Pad-50<br>Size 2: Bottom-20, Top-25,<br>Pad-35   |

| BRDL2-3 Via Size                           | Bottom-27um, Top-31um                                                                             | Size 1: Bottom-20, Top-25,<br>Pad- 35<br>Size 2: Bottom-37, Top-40,<br>Pad-N/A |

| RDL Layer Thickness                        | RDL0: 9.5um<br>TRDL: 8.6um<br>BRDL 1&2: 7-8um                                                     | RDL0: 5um<br>RDL 1-3: 3.5-5um                                                  |

| BRDL 1 Min L/S                             | No signal routing                                                                                 | SE: 8/10<br>DP: 8/10                                                           |

| BRDL 2 Min L/S                             | No signal routing                                                                                 | SE: 8/10                                                                       |

| BRDL 3 Min L/S                             | N/A                                                                                               | SE: 7/11<br>DP: 9/10                                                           |

| BRDL2 Bump Size (RDL to package substrate) | 55um                                                                                              | N/A                                                                            |

| BRDL3 BGA Pad (RDL to PCB)                 | N/A                                                                                               | Cu Pad-180                                                                     |

| Via Pattern                                | Staggered                                                                                         | Staggered                                                                      |

| Min Via Stagger                            | 29um                                                                                              | 35                                                                             |

| P/G Mesh Grid Min L/S                      | 10/29um                                                                                           | 9/31um                                                                         |

| Shape-Trace Min Space                      | N/A                                                                                               | 10                                                                             |

| Shape-Shape Min Space                      | 12um                                                                                              | 10                                                                             |

| RDL Guard ring                             | 2 staggered via structure                                                                         | 3 staggered via structure                                                      |

| Adhesion Hole Size                         | 29x29um,<br>18x18um,<br>8x8um                                                                     | 31x31um @40um pitch                                                            |

| Max Distance to Adhesion Hole              |                                                                                                   | N/A                                                                            |

|                                            |                                                                                                   | intal                                                                          |

ATTD

79

ATTD C/A Teardown Intel Confidential Intel

#### Get the latest packaging competitive analysis reports

ATTD C/A Prismark Yole TechSearch more...

#### Bookmark:

https://intel.sharepoint.com/sites/attdcompetitiveanalysis

#### Search function