# mec

# **EMERGING MEMORY PROGRAM: IGZO & OTS/PCM**

GOURI SANKAR KAR, PROGRAM DIRECTOR

ON BEHALF OF EM PROGRAM TEAM

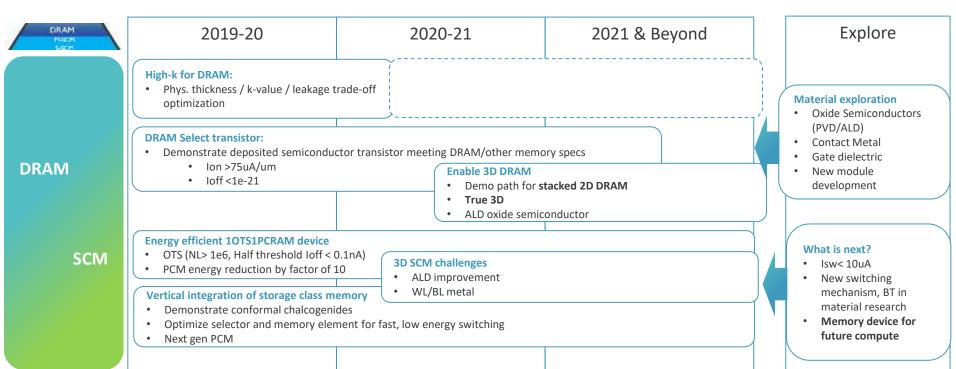

#### **EMERGING MEMORY ROAD MAP: IMEC ACTIVITIES**

# TOPIC REQUESTED

- IGZO progress and challenges

- Progress in OTS material design and switching mechanism understanding

- Progress in GST stack engineering

IGZO

# DRAM SCALING ROADMAP

| Imec | view | of | industry : | roadmap |

|------|------|----|------------|---------|

|      |      |    |            |         |

|      | Year          | 2019-2020       | 2021-2022    | 2023-2024    | 2025-2026             | 2027-2028                               |

|------|---------------|-----------------|--------------|--------------|-----------------------|-----------------------------------------|

| DRAM | DRAM          | D17, D16, D15   | D14, D13     | D13, D12?    | 3D array above peri   | 3D x layers                             |

|      | Technology    | MIM EOT 0.5     | MIM EOT 0.5  | MIM EOT 0.5  | MIM EOT 0.5           |                                         |

|      | Peri          | Poly / HK-MG    | HK-MG        | HK-MG        | HK-MG                 | HK-MG / FinFET                          |

|      | Array         | Classical       | Classical    | Classical    | Array above periphery | 3D DRAM (stack 2D/vertical integration) |

|      | Capacitance   | 10 fF           | 8 fF         | 6 fF         | 4 fF                  | IfF                                     |

|      | Cap: type, AR | Cylinder, 25-50 | Pillar 60-80 | Pillar 70-90 | Pillar 70-90          | sidewall                                |

|      | Power (VDD)   | 0.9V            | 0.9V         | 0.9V         | 0.9V                  | 0.8V                                    |

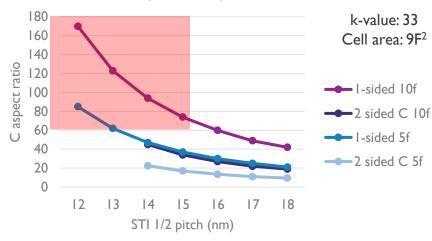

**Periphery transition**: HK/MG, eventually cheap FinFET **Capacitor evolution**: lower and lower C (design, BL optimization, ECC, ...), single sided capacitor, higher aspect ratio, pillar etch

Challenge: D12 (12nm half pitch STI): no room for even single sided capacitor

#### 3D transition

- Medium disruption: keep same architecture and put periphery under (required deposited semiconductor)

- Next level of disruption: real 3D integration, etch centric

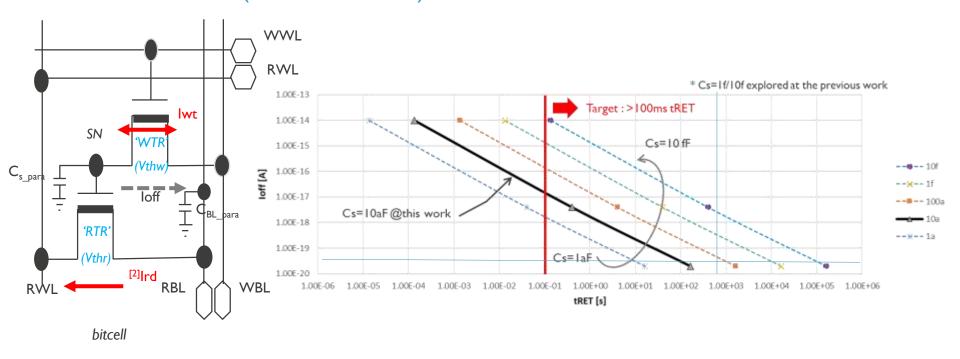

- Requires 2T cell to minimize capacitor size down to parasitic node

#### Etch aspect ratio per DRAM node

DRAM keeps going but will need to be successful in difficult transitions

# DRAM: 3D CELL (STACKED 2D)

3D flow under development (Coventor)

#### Simulation results so far for $2TIC \rightarrow 2TOC$

- Read and write possible, read disturb has small window

- Same Vth for both transistors is possible

- Stacked 2D (3D DRAM) integration is feasible

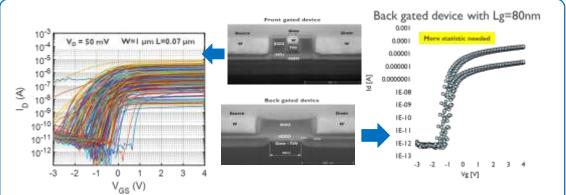

## EM5 3T IGZO SELECT DEVICE FOR MEMORY APPLICATION

#### PRESENT STATUS

Very high variability across the wafer with FG scheme, tight distribution with BG scheme

#### **CHALLENGES TO ADDRESS**

- Robust FG device scheme

- Strong process impact: Patterning, contact metal, dielectric deposition process etc,

- Post processing oxygen passivation of the channel

- Hydrogen immunity

- Reduction of contact and access resistance

- Positive Vt

- On current improvement

- Reliability of the device

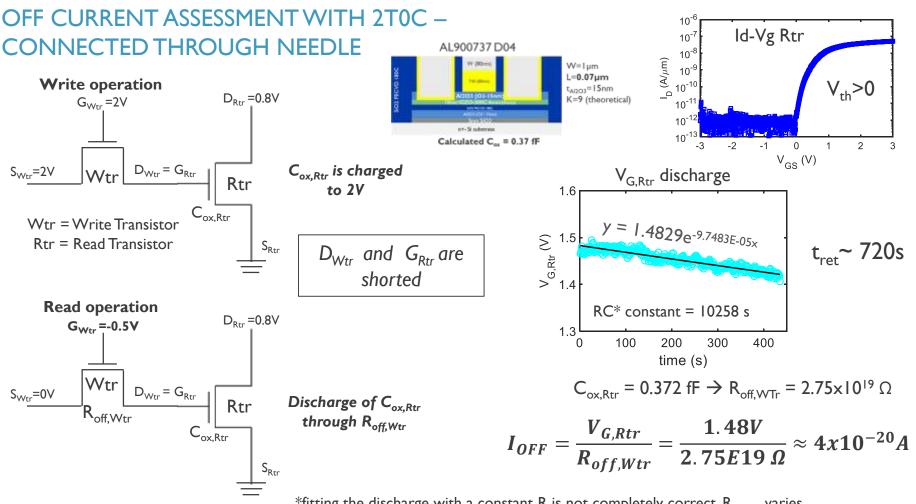

- 2TIC and 2T0C demo

#### How to address it?

- New robust FG scheme → IGZO compatible processes

- Contact resistance, IGZO passivation, IGZO stability: Ab-initio → calypso → Corte

- Doped IGZO, composition,

- Gate trimming to Lg 30nm

- Strong post IGZO material research

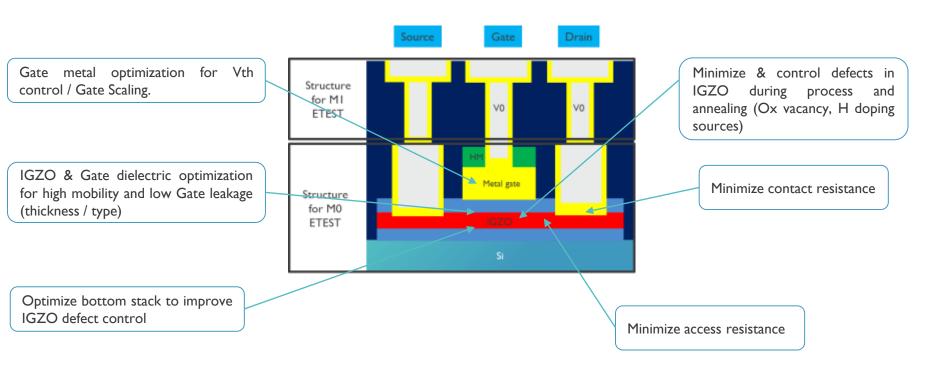

# KEY ASPECTS TO CONTROL

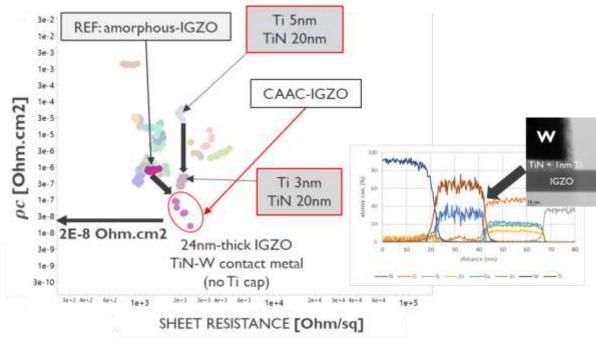

# **CONTACT METALLURGY**

TiN

umec

- The  $\rho c$  is improved with CAAC IGZO thanks to a better control of the formation of  $TiO_2$ .

- CAAC=> less driving force to scavenge oxygen

CONFIDENTIAL

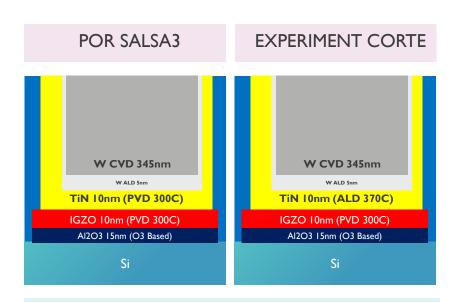

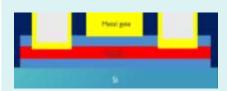

# M0BB - METALLIZATION MODULE DEVELOPMENT

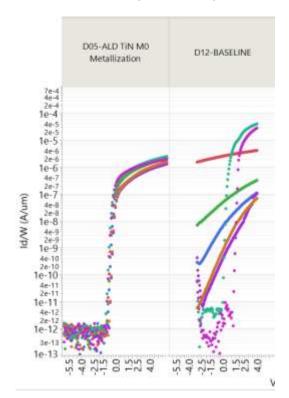

#### BARRIER PVD TIN VS ALD TIN

W=1μm L=0.07 μm

Uniformity improved using ALD TiN for the 70nm Devices.

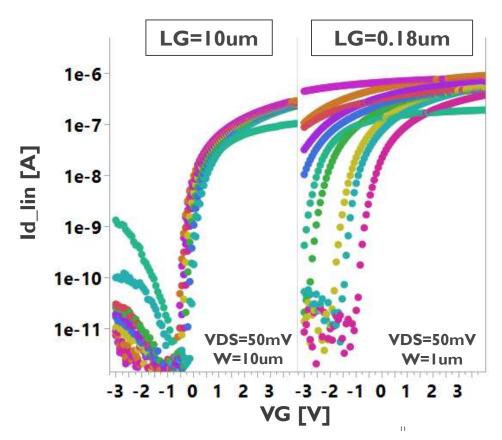

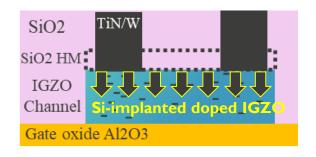

# SILICON-IMPLANTED IGZO PVD NFETS

#### WORKING DEVICES DOWN TO 180NM-LG DESIGN FOR THE FIRST TIME

24nm a-IGZO: no gate control demo'ed electrically so far!

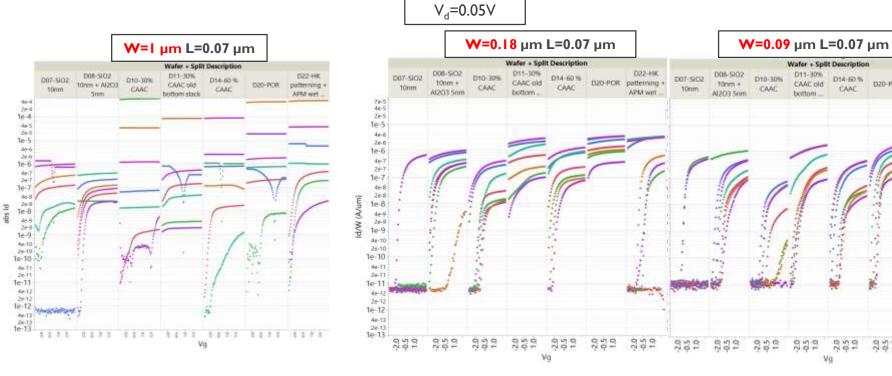

# IMPACT OF ACTIVE SIZE ON EFFICIENCY OF O2 ANNEAL

- Smaller gate area  $\rightarrow$  higher  $V_{th}$  confirming more efficient  $O_2$  anneal

- SiO2 as gate dielectric: no doping in most of the devices → full passivation with POR anneal?

- D22 (HK patterning) shows the best I<sub>ON</sub>

D22-HK

patterning +

# IMPACT OF HYDROGEN ANNEAL

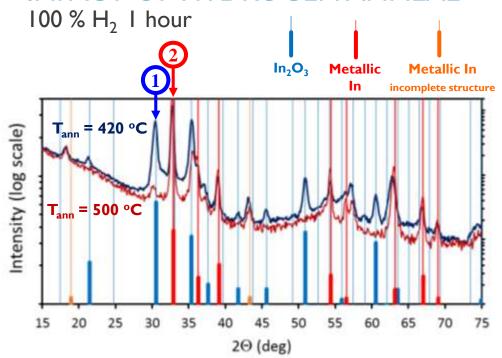

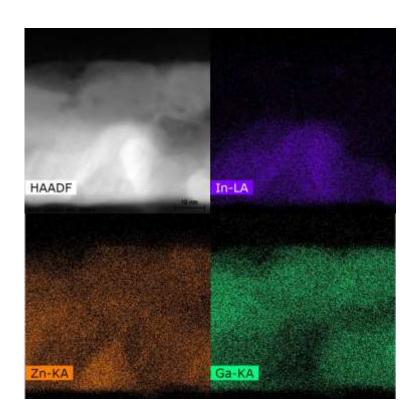

- Clear spectrum appears for 100 % H<sub>2</sub> anneal

- Phase separation into bixbyite In<sub>2</sub>O<sub>3</sub> and metallic In

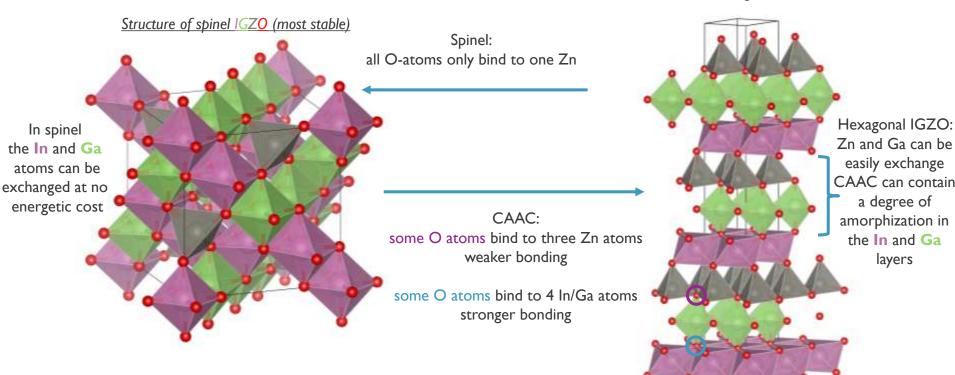

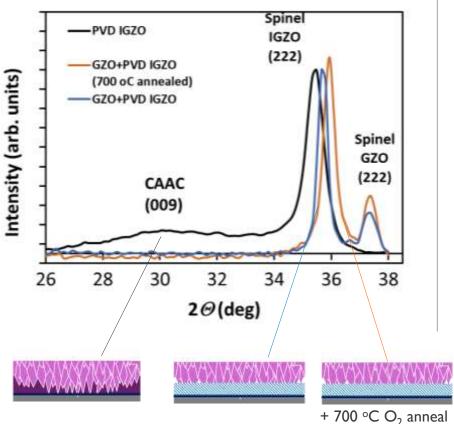

# DIFFERENCE BETWEEN SPINEL AND CAAC/HEXAGONAL

Structure of hexagonal/CAAC IGZO

Spinel has a more uniform bonding of O atoms: higher stability against defects

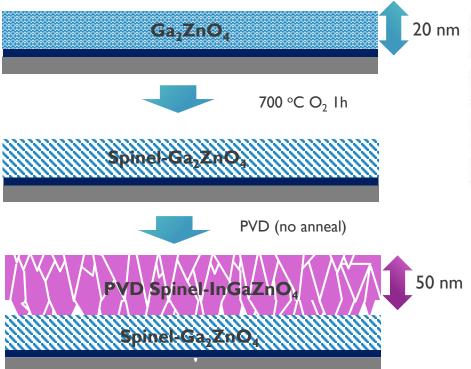

# **PURE SPINEL**

Using  $Ga_2ZnO_4$  as template

No increase in peak intensity: no additional Spinel formed

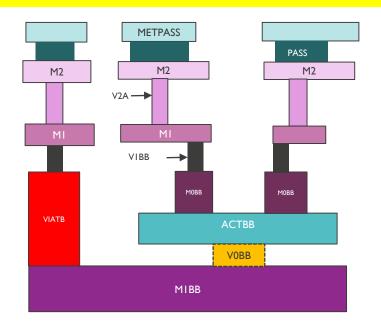

# **CORTE: MULTIPLE INTEGRATION SCHEME CAPABILITY**

#### Gate First

- Advantages

- No IGZO channel damage

- Drawbacks

- IGZO damage at contact area

- Limited O2 access for IGZO channel defect curing

- Access resistance impacted by O2 defect curing

Gate First + Buried Oxygen channel

- Advantages

- No IGZO channel damage

- Improved buried O2 access for IGZO channel defect curing

- Access resistance not impacted by <u>buried</u> O2 defect curing

- Drawbacks

- IGZO damage at contact area

Gate Last

#### Advantages

- No contact damage

- Post Gate opening O2 defect curing

- Compatible with IGZO channel recess approach

- Minimize access resistance

- One mask less

- Drawbacks

- Potential IGZO channel damage (No IGZO channel recess)

- Limited O2 access for IGZO channel defect curing

- Access resistance impacted by O2 defect curing

Gate Last + Buried Oxygen channel

#### Advantages

- No contact damage

- Post Gate opening O2 defect curing

- Compatible with IGZO channel recess approach

- Minimize access resistance

- Access resistance not impacted by <u>buried</u> O2 defect curing

- Drawbacks

- Potential IGZO channel damage (No IGZO channel recess)

# **CORTE INTEGRATION VEHICLES**

# Back Gated IGZO transistor (ITIC, 2T0C)

# Front Gated IGZO based memory (ITIC, 2TIC)

ເຫາec

\*fitting the discharge with a constant R is not completely correct,  $R_{\text{off,RTr}}$  varies with  $V_{G,Rtr}$ , but we can estimate the order of magnitude of  $I_{\text{off}}$

CONFIDENTIAL

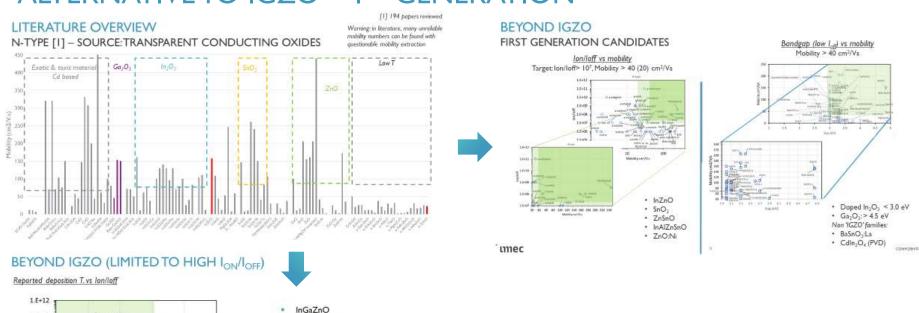

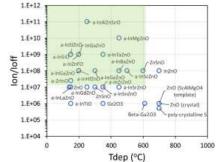

# ALTERNATIVE TO IGZO - IST GENERATION

CONFIDENTIAL

- Short listing candidates based on literature information

- Is there anything else (simpler)?

mec

InGaZnO

InAIZnSnO

InSiZnO

InGeZnO

InGeZnO

InMgZnO

InBaZnO

InHfZnO

InHfZnO

InSiZnO

InHfZnO

InSiZnO

19 CONFIDENTIAL

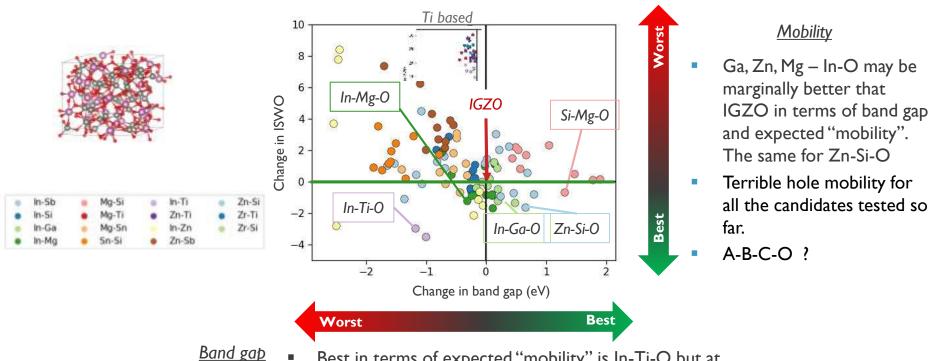

# FIGURE OF MERIT

# In BASED ALTERNATIVE BINARY (A-B-O) METALLIC OXIDE CANDIDATES

Best in terms of expected "mobility" is In-Ti-O but at the expense of a reduction in terms of band gap  $\rightarrow$ impact on lon/loff & leakage expected

# **ALD IGZO**

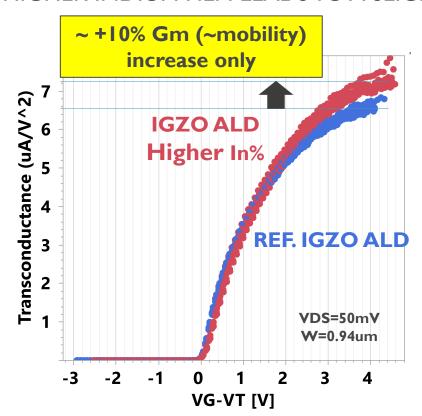

#### HIGHER INDIUM FILM LEADS TO A SLIGHT IMPROVEMENT IN CARRIER TRANSPORT

BKM IGZO ALD attempts.

More optimization in progress

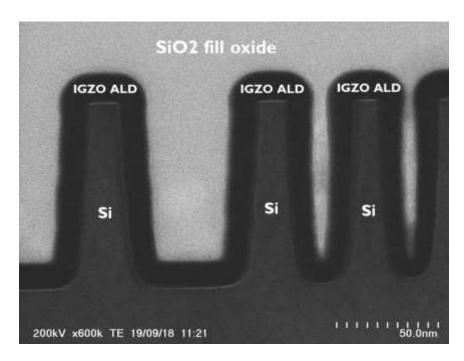

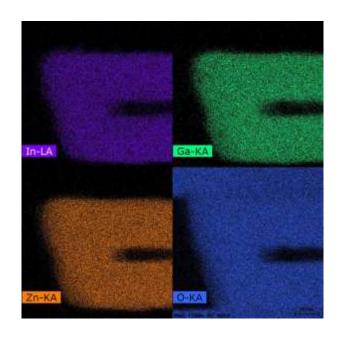

# **ALD IGZO**

IGZO composition looks uniform.

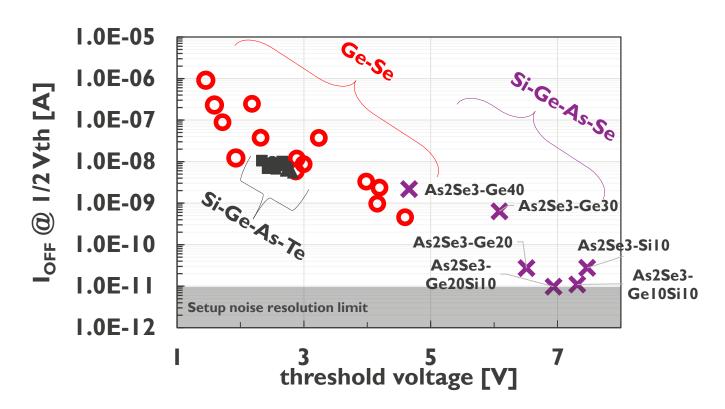

# PROGRESS IN OTS MATERIAL DESIGN

### INTRODUCTION

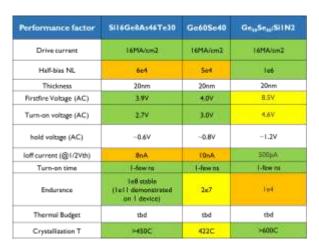

#### MOTIVATION FOR SI-GE-AS-SE DEVELOPMENT

#### Previous work

- SiGeAsTe

- Very good endurance, but relatively high I<sub>OFF</sub>

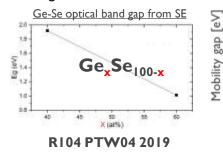

- Tellurides show limited E<sub>g</sub> tuning

- GeSe:SiN

- Lower I<sub>OFF</sub>, but limited endurance

- Ellipsometry & ab initio show larger tunability of  $E_g \rightarrow tune I_{OFF}$

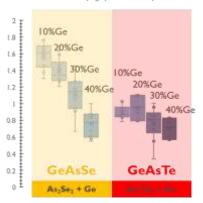

#### This work

- As and Si doping of Ge-Se system

- Benchmark SiGeAsTe versus SiGeAsSe

R104 PTW04 2019, R104 PTW10 2018

gab

Mobility gap tunability

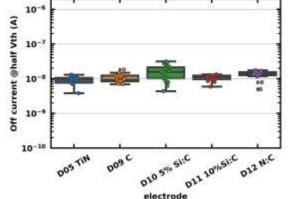

# QUATERNARY SYSTEM: SiGeAsSe VS SiGeAsTe

IMPACT OF SILICON CONTENT

- Increasing Si content → larger V<sub>TH</sub>, reduced I<sub>OFF</sub>

- Trend in agreement with SiGeAsTe

- SiGeAsSe vs SiGeAsTe

- V<sub>TH</sub> increase by a factor ~3

- I<sub>OFF</sub> reduced by a factor ~500, down to I0pA

CD = 65nm

Ge~20%

As/Te ~2/3

As/Se ~2/3

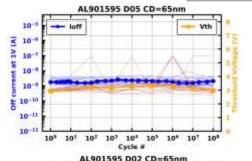

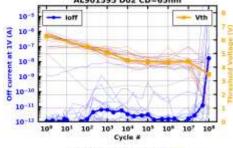

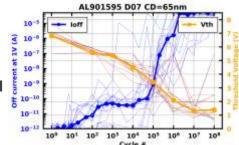

### **ENDURANCE**

- GeAsSe and SiGeAsSe → V<sub>TH</sub>

degradation with cycling, increased

leakage

- Worse endurance performance compared to SiGeAsTe

- Possible Ti intermixing (TiN TE) to be evaluated → in-situ C-based electrode now available, to be tested in next learning cycle

Vpulse=7.5V  $I_{ON}\sim 450uA-500uA$  $t_{R}=t_{F}=100ns$

ENTIAL

REF SiGeAsTe Stable V<sub>TH</sub>, I<sub>OFF</sub> I 0<sup>11</sup> cycles demonstrated

GeAsSe

Degradation

during cycling

SiGeAsSe Earlier failure compared to GeAsSe

# **COMPOSITION MAP**

#### BENCHMARKING OF MATERIAL SYSTEMS

# EXPERIMENTS AND MODELLING FOR SET E-FIELD INDUCED VH DRIFT ACCELERATION OF OTS

# IMPACT OF OPERATING CURRENT ON ENDURANCE

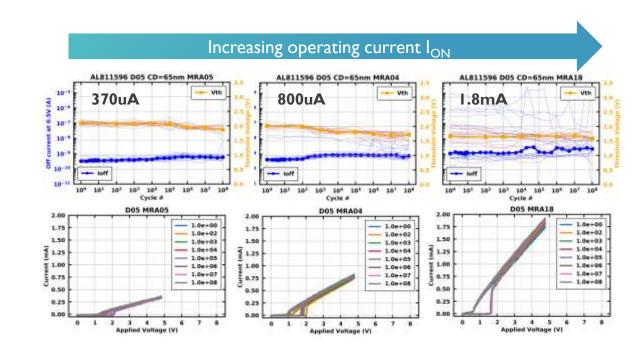

Pillar device, CD=65nm. 20nm OTS, CVD encapsulation, +5V, 100ns rise/fall time (triangular pulses)

- 10<sup>8</sup> cycles possible also with large I<sub>ON</sub>=1.8mA (median)

- slight degradation with cycling

- I<sub>OFF</sub> increasing, V<sub>TH</sub> decreasing

- Attributed to lower Si content than nominal (see TEM)

- Some leaky devices at largest operating current

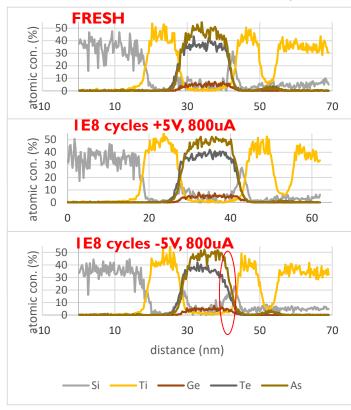

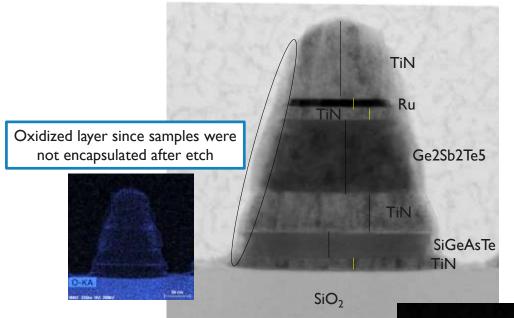

## PILLAR DEVICE TEM ANALYSIS

- Lower Si content than expected in the center of the pillar (16%nominal)

- Si-rich interfaces

- In progress: study alternative electrode material Si:C and impact of thermal budget on Si content

- Cycling does not induce Ti intermixing

- Slight shift of As/Te peaks for device cycled at -5V

#### Vertical line scans in the center of the pillar

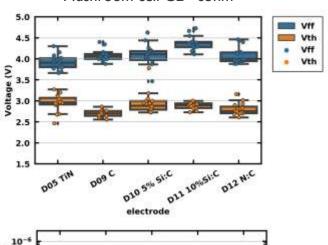

### CARBON-BASED ELECTRODES

# IMPACT ON $V_{FF}V_{TH}$ , $I_{OFF}$

- Confirmed functionality of newly developed in-situ carbon-based electrodes on mushroom cell

- compared to TiN reference, all carbon splits have

- Slightly larger V<sub>FF</sub> consistent with C resistivity trends (<u>link</u>)

- Slightly lower V<sub>TH</sub>, higher I<sub>OFF</sub>

- Possible reason is higher operating temperature due to larger C resistivity (larger cluster of delocalized defect states)

- Si:C to be tested with SiGeAsSe

- Goal: improve endurance by avoiding possible Ti intermixing in selenides.

# SiGeAsTe reference composition Mushroom cell CD=65nm

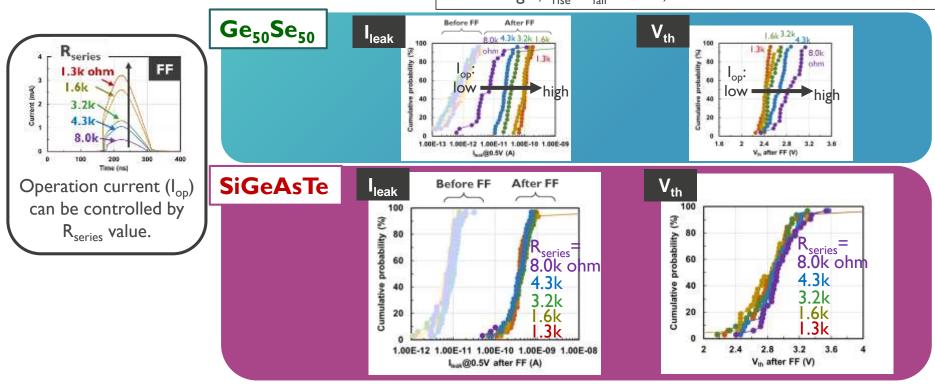

# (I) Enlargement effect

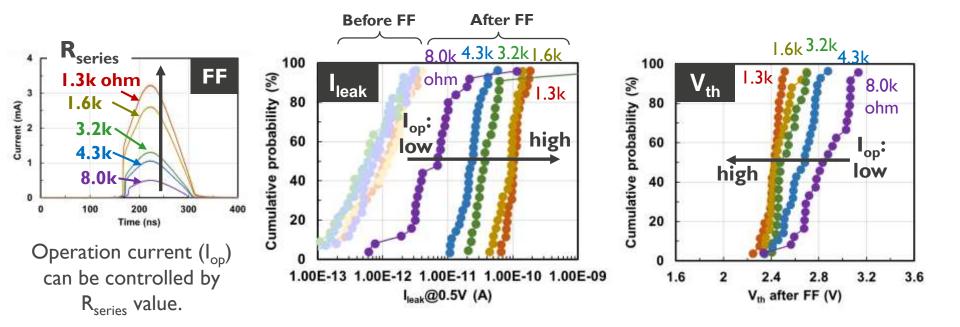

$Ge_{50}Se_{50}$ /in-situ TiN, IRIR,  $R_{series}$ =1.3~8.0 kohm FF: Triangle,  $T_{rise}$ = $T_{fall}$ =100ns, 5V SW: Triangle,  $T_{rise}$ = $T_{fall}$ =100ns, 5V

Higher I<sub>op</sub> → Higher-I<sub>leak</sub> and lower-V<sub>th</sub> after FF = Filament with <u>more</u> delocalized defects

# (I) Enlargement effect

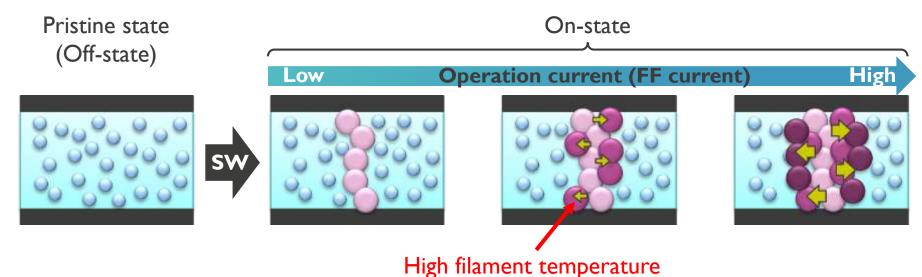

# POSSIBLE MECHANISM OF IOP DEPENDENCE

→ Additional localized-to-delocalized transition at neighboring defects

"Filament enlargement" is taking place <u>during on-state</u>, depending on operation current (=temperature).

# (I) Enlargement effect

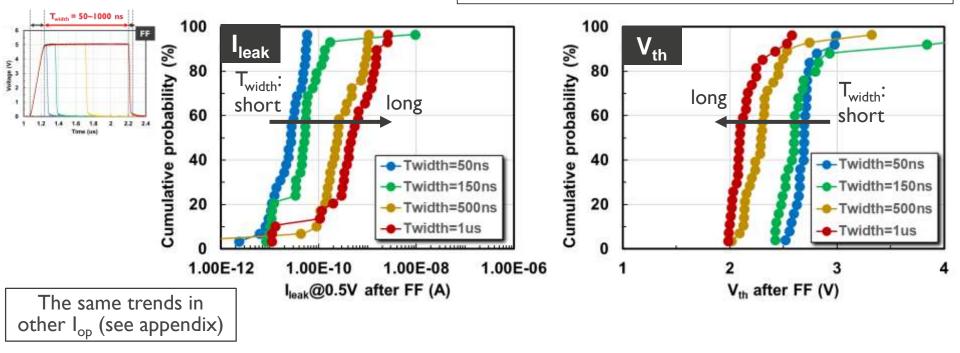

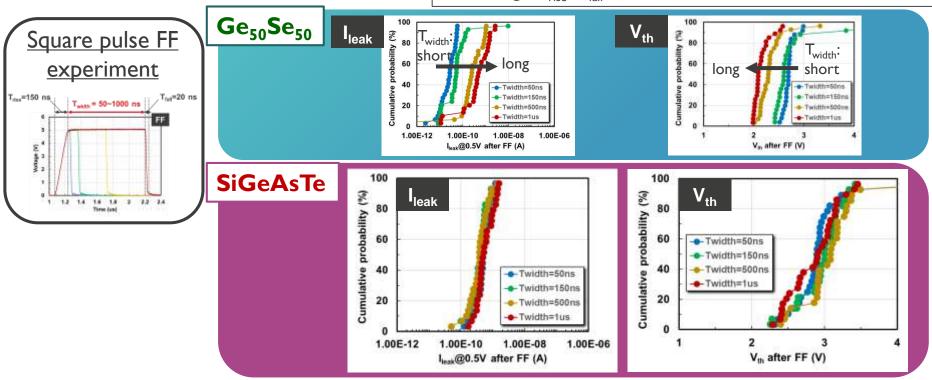

# PULSE WIDTH DEPENDENCE

$Ge_{50}Se_{50}$ /in-situ TiN, ITIR,  $V_g$ =1.75V ( $I_{op}$ =1.4 mA) FF: Square,  $T_{rise}$ =150ns,  $T_{width}$ =50~1000ns,  $T_{fall}$ =20ns, 5V SW: Triangle,  $T_{rise}$ = $T_{fall}$ =150ns, 5V

Longer T<sub>width</sub> → higher-I<sub>leak</sub>, lower-V<sub>th</sub> = Signature of "enlargement effect" during on-state

່ເກາec

# (2) Quenching effect

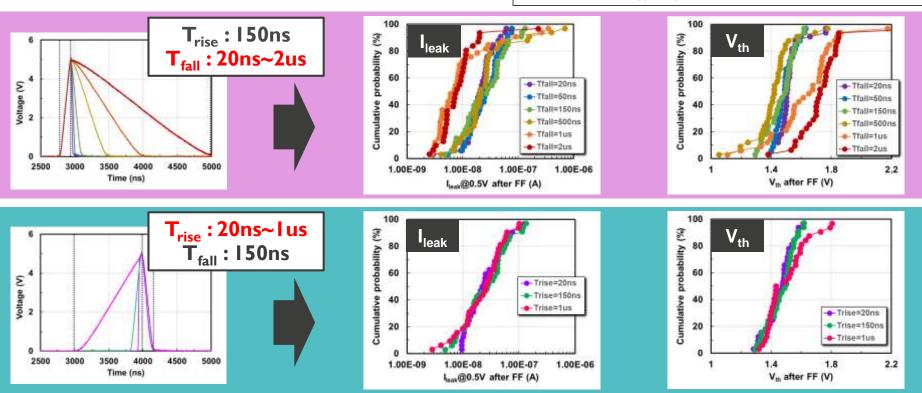

# IMPACTS OF RISE AND FALL TIME

$Ge_{60}Se_{40}$ /ex-situ TiN, ITIR,  $V_g$ =1.75V ( $I_{op}$ =1.4 mA) FF: Asymmetric,  $T_{rise}$ & $T_{fall}$ : 20~2000ns, 5V SW: Triangle,  $T_{rise}$ = $T_{fall}$ =150ns, 5V

$T_{\text{fall}}$  is a key parameter. (Shorter  $T_{\text{fall}} \rightarrow M$  ore delocalized defects)

# (2) Quenching effect

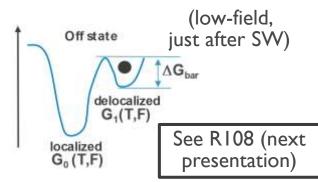

# POSSIBLE MECHANISM OF T<sub>FALL</sub> DEPENDENCE

Key: Time constant of delocalized-to-localized transition decreases at high-temp.

- → Long relax time at zero field due to energy barrier

- → Consistent with "Vth-recovery" (PTW2019H01 R106)

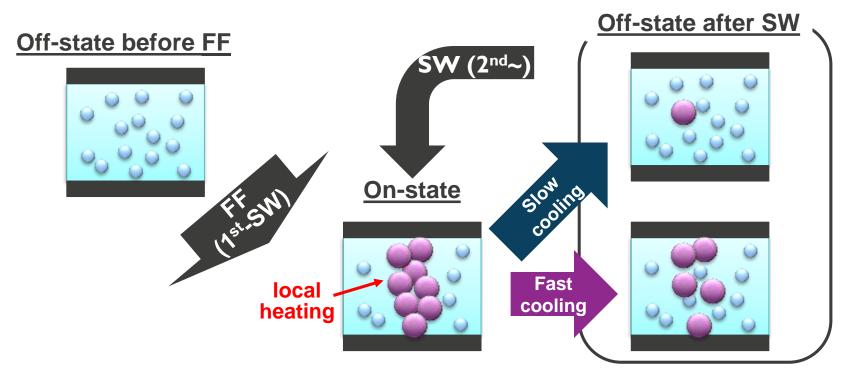

# Off-state before SW

PF-conduction through localized defects → high-R

Slow

**Fast**

cooling

Large-current by delocalization

→ low-R, local heating

#### Off-state after SW

Less delocalized defects remaining thanks to long enough time for transition

→ lower-I<sub>leak</sub>, higher-V<sub>th</sub>

More delocalized defects **<u>quenched</u>** due to insufficient transition time

→ higher-I<sub>leak</sub>, lower-V<sub>th</sub>

# (3) Flexibility and Reversibility

## POSSIBLE MECHANISM OF FLEXIBILITY AND REVERSIBILITY

Heating and quenching take place in every SW, so that filament properties are modulated every time according to  $T_{\text{fall}}$  of each SW.

### PULSE WIDTH DEPENDENCE

**SiGeAsTe(20nm)** /in-situ TiN, ITIR,  $V_g = 1.75 \text{V}$  ( $I_{op} = 1.4 \text{ mA}$ ) FF: Square,  $T_{rise} = 150 \text{ns}$ ,  $T_{width} = 50 \sim 1000 \text{ns}$ ,  $T_{fall} = 20 \text{ns}$ , 5V SW: Triangle,  $T_{rise} = T_{fall} = 150 \text{ns}$ , 5V

No dependence on T<sub>width</sub> = no "enlargement" in SiGeAsTe

# R<sub>SERIES</sub>(=I<sub>OP</sub>) DEPENDENCE

**SiGeAsTe(20nm)** /in-situ TiN, IRIR,  $R_{\text{series}}$ =1.3~8.0 kohm FF: Triangle,  $T_{\text{rise}}$ = $T_{\text{fall}}$ =100ns, 5V SW: Triangle,  $T_{\text{rise}}$ = $T_{\text{fall}}$ =100ns, 5V

# No dependence on $I_{op}$ in SiGeAsTe.

Possible reason: fewer "active" defects (further work to be done)

#### CONCLUSION AND OUTLOOK

#### Conclusion

- Filament properties of Ge<sub>x</sub>Se<sub>1-x</sub> are very sensitive to SW pulse condition

- Higher I<sub>op</sub>, longer T<sub>width</sub> or shorter T<sub>fall</sub>

- Filament with more delocalized defects (due to enlargement and quenching)

- Flexibility and reversibility, depending on T<sub>fall</sub>.

- SiGeAsTe shows no dependence on I<sub>op</sub> and T<sub>width</sub>, and less flexibility.

- → promising for stable circuit operation

- Outlook

- Filament formation mechanism in SiGeAsSe

- Retention characteristics of filament properties

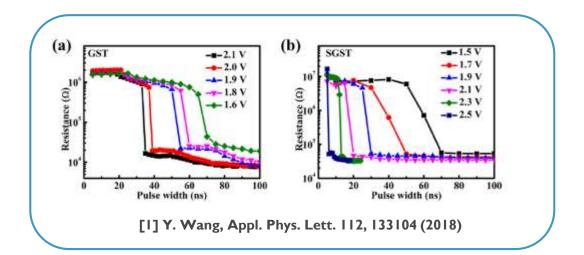

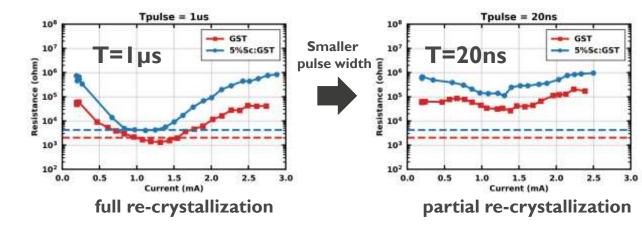

#### SCANDIUM-DOPED GST

- Scandium doping (~3%

Sc content) reported in

literature to improve

crystallization speed

(6ns SET speed) and

reset energy [1]

- First experiments at imec (~5% Sc)

- Larger cell resistance, but no significant improvement in terms of crystallization speed or operating current

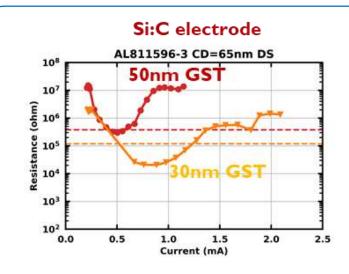

#### RESET CURRENT OPTIMIZATION

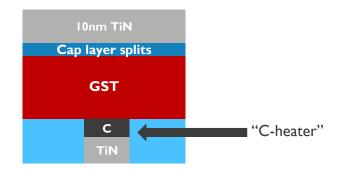

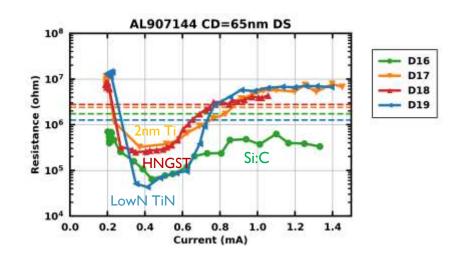

#### C HEATER WITH ALTERNATIVE CAPS

- C-heater was tested in previous LCs w/ reference TE 5nm Ti/TiN

- C-heater w/ alternative caps deliver sub-mA operating current

- LowNTiN

- Best split in terms of memory window

- HNGST (heavily nitrogen-doped GST) and 2nmTi/TiN have similar performance

- Small MW for Si:C cap

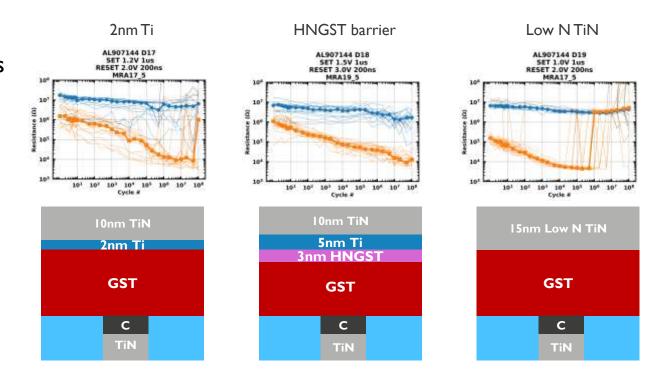

## **ENDURANCE**

#### C HEATER WITH ALTERNATIVE CAPS

- 2nm Ti and HNGST splits have similar endurance performance

- HNGST slightly better, IE8 cycles

- Low NTiN

- Confirmed larger window during cycling but failure to HRS

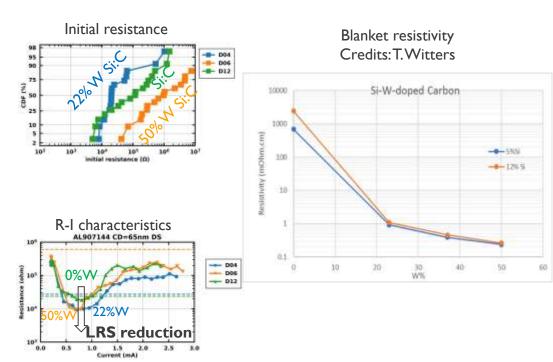

# C(W)/SI CAPS

- W:Si:C alloying (5% Si)

- 22% W

- Smaller initial resistance and tighter distribution compared to Si:C

- ✓ LRS reduced by a factor 2

- Expected benefit for ISIR cell: lower FF voltage

- 50% W

- X Higher initial resistance

- Possible interfacial oxide due to weaker interface? (pure W fails adhesion)

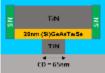

# IOTS-IPCM

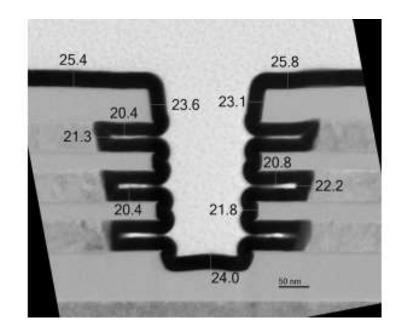

# PATTERNED ISIR TEM INVESTIGATION

- Morphological demonstration of IOTS-IPCM patterning

- Tapering angle to be improved

50 nm

## **SUMMARY**

#### Phase change memory (mushroom cell architecture)

- Reset current optimization: carbon heater coupled with optimized GST capping layer delivers sub-mA

reset current

- W-Si-C electrode → smaller initial resistance, better uniformity compared to Si-C electrode

- Expected benefit for ISIR cell → lower first fire voltage

- Results to be confirmed on pillar device lot

#### OTS selector

- IE8 endurance demonstrated with SiGeAsTe pillar device, CD=65nm

- TEM analysis reveals lower Si content than expected. Investigation of the root cause in progress.

- C-based electrodes developed in Endura5 (in-situ) and validated electrically on SiGeAsTe

- To be tested with SiGeAsSe → goal is to improve endurance

#### IOTS – IPCM

- Integrated OTS(SiGeAsTe)-IPCM(GST225) pillar patterning demonstrated morphologically

- In progress: improving tapering angle

- To be tested electrically in planned device lot

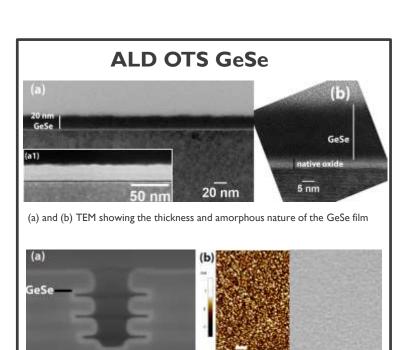

## ALD GST & OTS DEVELOPMENT

#### TOWARDS 3DSCM REALIZATION

| Items                       | ALD OTS GeSe                                 | ALD PCRAM GST                                |

|-----------------------------|----------------------------------------------|----------------------------------------------|

| GPC                         | 0.34 Å/cycle (10 nm in 2 Hrs)                | 0.66 Å/cycle (20 nm in -3 Hrs)               |

| Crystallization temperature | 370 °C                                       | 200 °C                                       |

| Composition                 | Stoichiometric                               | GST325                                       |

| WiW NU                      | 7 %                                          | 6.9 %                                        |

| Density                     | 4.1 g/cm <sup>3</sup> (75 % of bulk density) | 5.4 g/cm <sup>3</sup> (85 % of bulk density) |

| Impurities                  | 5 % C, 5 % H, 4 % CI                         | 3 % H, I % CI, 3 % O, 3% C                   |

| RMS surface roughness       | - 0.3 nm                                     | ~1.2 nm                                      |

| Step coverage               | -1                                           | -1                                           |

#### **ALD PCRAM GST**

Conformal ALD GST films

**Excellent composition uniformity** of the GST film

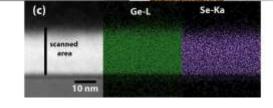

(a) Highly conformal GeSe, (b) Smooth morphology of GeSe films, (c) Composition uniformity of the film

CONFIDENTIAL

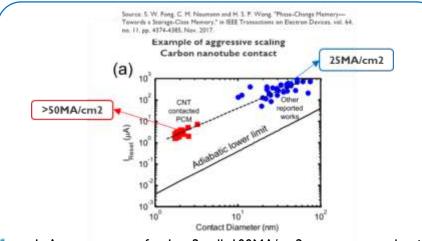

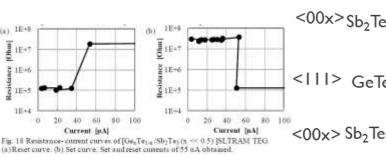

### EMI **GST 225 PCRAM** BASE LINE PROCESS

#### PRESENT STATUS

Switching current density <30mA/cm2 from 65nm pillar device

#### **CHALLENGES TO ADDRESS**

- IuA reset current for Inm2 cell, I00MA/cm2 reset current density.

- Best published switching current density is ~25MA/cm2

- Energy per bit: >InJ

- Energy scaling remains most difficult challenge in classical PCM

#### Where do we see opportunities?

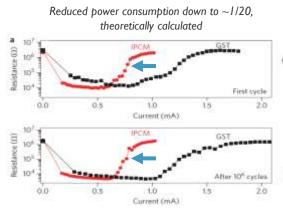

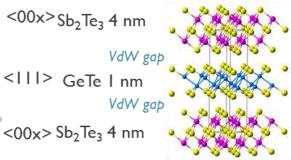

- Interfacial phase change memory (iPCM) is a recent follow-up concept for phase change memory (PCM) leaving out the inherent high-power physical mechanisms inducing amorphous to crystalline transition

- Atomic displacement that occurs when using super lattice (SL) structure of GeTe and Sb2Te3.

#### WHERE DO WE SEE OPPORTUNITIES?

#### GOING BEYOND PRESENT AMORPHOUS/CRYSTALLIZATION PCM MECHANISM

Interfacial phase change memory (iPCM) is a recent follow-up concept for phase change memory (PCM) leaving out the inherent high-power physical mechanisms inducing amorphous to crystalline transition, by subtle atomic displacement that occurs when using super lattice (SL) structure of GeTe and Sb<sub>2</sub>Te<sub>3</sub>.

Ackn. to Y. Saito, A.Kolobov et al.

Need to benchmark in imec state of the art test vehicles

N. Takaura et al, IEDM 2014

Current density I order of magnitude lower

#### GeTe/Sb<sub>2</sub>Te<sub>3</sub> superlattice

Ackn. to Y. Saito, A. Kolobov et al.

Need finetuned deposition control (layer thickness, stoichiometric composition, ...) for <00x>/<111> vdW epitaxy

# mec

embracing a better life