DRAM AND NAND PERIPHERY TRANSISTORS **DEVICE LEARNING**

ROMAIN RITZENTHALER, ON BEHALF OF LOGIC FOR MEMORY TEAM

# **LOGIC DEVICES** F203

**NOW IN COURSE:**

DRAM AND NAND PERIPHERY TRANSISTORS DEVICE LEARNING

ROMAIN RITZENTHALER

THIS PRESENTATION IS OPEN TO:

CORE PARTNERS, APPLE, SOCIONEXT

AMAT, ASM, BASF, SCREEN, KLA-TENCOR, KULEUVEN, LAM, SYNOPSYS, RIBER, COVENTOR, NOVA, THERMOFISHER, PARK SYSTEMS, SOITEC, KURITA, KOKUSAI, SILTRONIC, AIR LIQUIDE, EBARA, GLOBALTCADSOL, VERSUMMATERIALS, HPSP, ASML, MERCK, HITACHI, TEL, SHINETSU

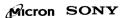

# PROJECT STATUS: CURRENT PTW VS. PREVIOUS PTW

## **OUTLINE**

- Introduction

- DRAM peripheral devices

- NAND peripheral devices

- Conclusions

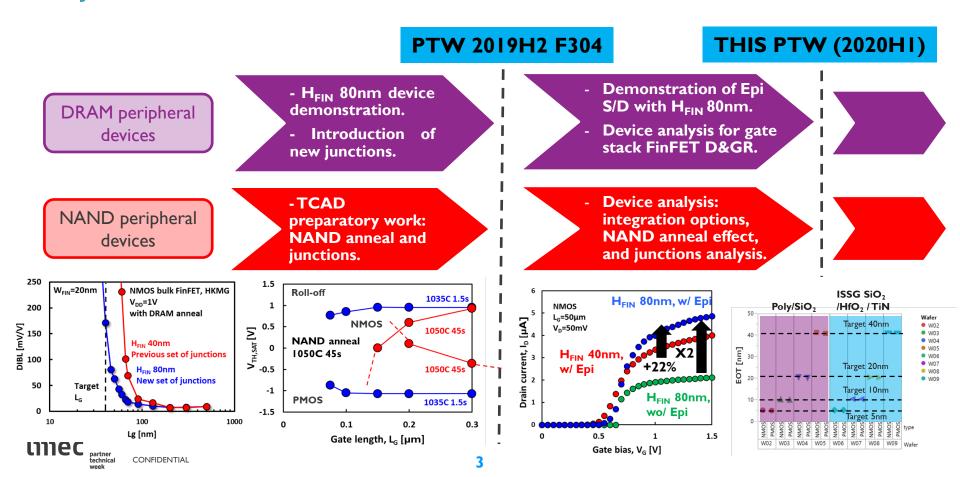

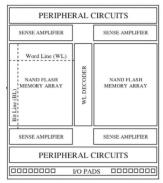

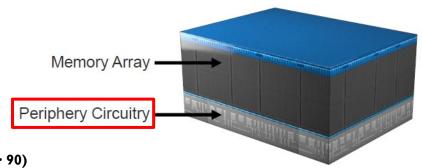

#### Courtesy A. Spessot

#### TRANSISTORS USED IN DRAM MEMORY CHIP

- In DRAM technologies, transistors are used as access devices and in the <u>peripheral circuitry</u>.

- Peripheral transistors serve several purposes: address decoders, sense amplifiers, output buffers, control circuitry

|                          | Cell Transistor                   | Periphery Transistor        |                                                |                                                |  |  |  |

|--------------------------|-----------------------------------|-----------------------------|------------------------------------------------|------------------------------------------------|--|--|--|

| Type of transistor       | Access Device                     | Regular Logic<br>Transistor | Sense/Amplifier                                | Row Decoder                                    |  |  |  |

| Applied Voltage          | VPP (~3.0V)                       | VDD (1.5V)                  | Vcore (1.0V~1.3V)                              | VPP (~3.0V)                                    |  |  |  |

| Gate Oxide thickness     | THICK (>=6nm)                     | thin (<2.5nm)               | thin (<2.5nm)                                  | THICK (>=5nm)                                  |  |  |  |

| Gate Length              | Minimum<br>Feature size           | Larger than Cell<br>(~50nm) | Longer Lg within pitched layout (e.g.: ~100nm) | Longer Lg within pitched layout (e.g.: ~120nm) |  |  |  |

| Key<br>features/Attentio | Junction Leakage<br>Short Channel | Speed<br>Short Channel      | Local Variation<br>(mismatch)                  | Reliability                                    |  |  |  |

Reference value for DDR3, DRAM 20 nm node; Adapted from \$. Y. Cha, IEDM 2011 short course;

Area breakdown: Memory Array ~50%,

Periphery Transistor ~50% (~1/3 Sense Amp; ~2/3 Regular Logic + Decoder)

#### FINFET FOR DRAM PERIVALUE PROPOSITION

#### See also PTW 201810 F800

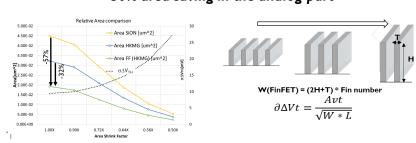

#### ~50% area saving in the analog part

Sense/Amp benefit FinFET HMGK can enable ~50% area gain due to improved mismatch and taller fin

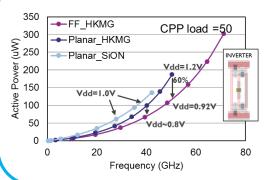

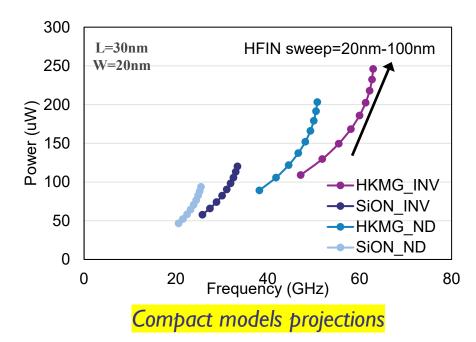

#### AC Power/Performance improvement (RO level) wrt planar

FinFET HMGK device outperform planar HKMG (60% less power at similar performance of HKMG planar with further V<sub>DD</sub> reduction down to 0.8V)

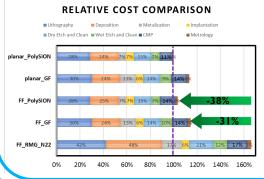

#### Cost effective flow wrt High Performance Logic

Proposed FinFET flow remains more cost effective than logic flow at corresponding dimensions

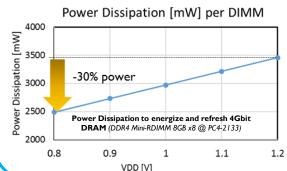

#### Power saving at system level wrt planar

FinFET HMGK can enable 30% power saving at DIMM level wrt planar SiON devices by reducing internal  $V_{\rm DD}$  down to 0.8V.

CONFIDENTIAL

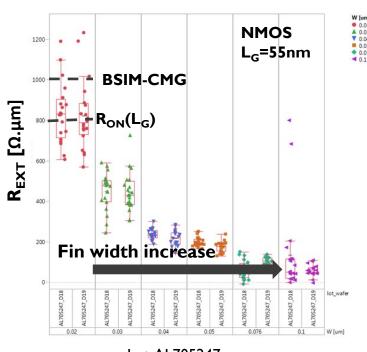

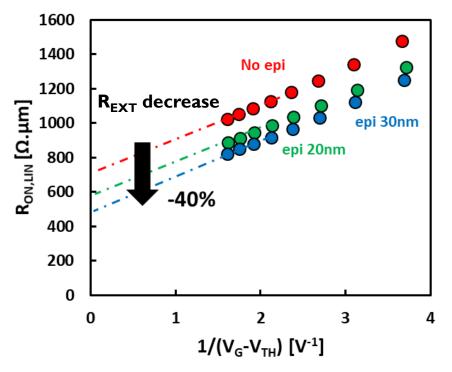

# FINFET: EXPERIMENTAL R<sub>FXT</sub> VS. FIN WIDTH

Lot: AL705247

CONFIDENTIAL

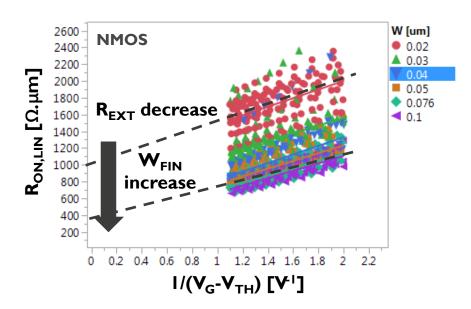

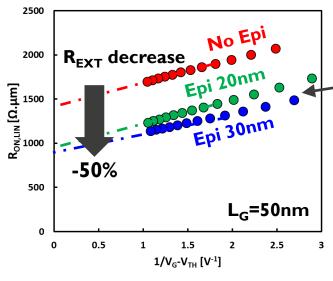

- Methods used :  $R_{ON}(I/V_G-V_{TH})^*$ ,  $R_{ON}(L_G)$ , and BSIM-CMG compact model fit.

- Clear increase of external resistance R<sub>EXT</sub> with decreased fin width.

\* A. Paul et al., IEDM 2013

## UNDOPED Si EPI S/D + ION IMPLANTATION

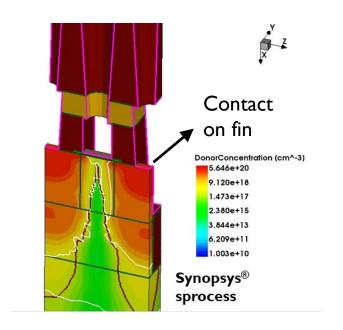

- FinFET current option: contact directly on fin.

- Undoped Epi S/D + Ion implantation could help alleviate this issue.

- Option assessed by TCAD

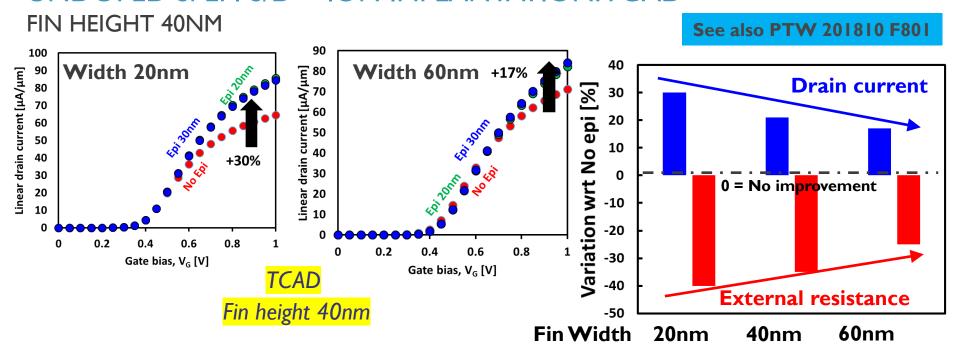

#### UNDOPED Si EPI S/D + ION IMPLANTATION:TCAD

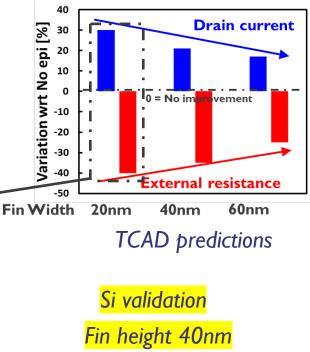

Effect of undoped Epi S/D + Ion Implantation: drive current improvement wo/ short channel margin degradation, consequent to external resistance decrease.

CONFIDENTIAL

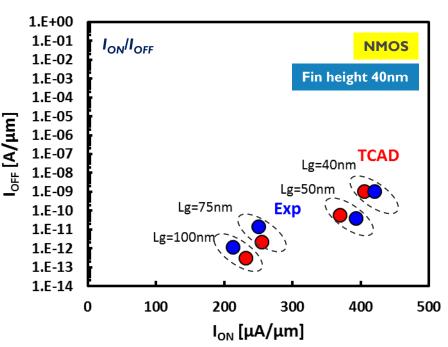

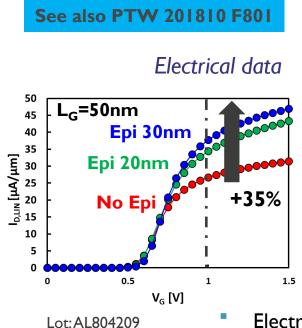

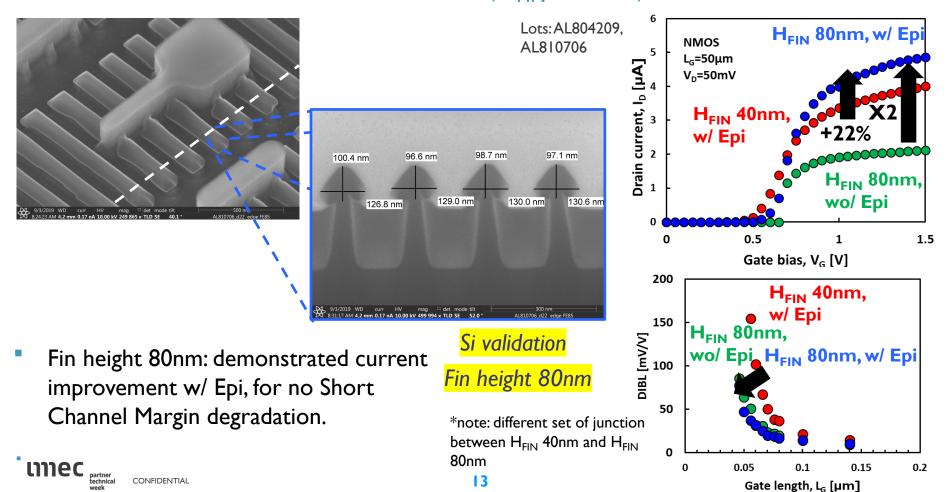

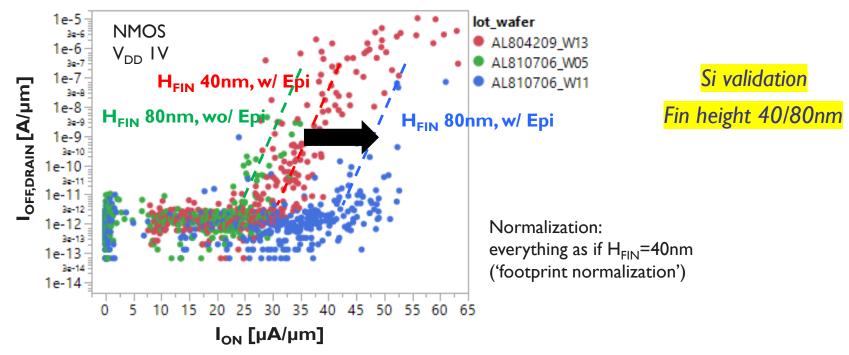

# UNDOPED Si EPI S/D + ION IMPLANTATION FIN HEIGHT 40NM

- Electrical confirmation of improved drive current w/ Epi S/D + I/I

- Numbers comparable to TCAD predictions.

- Next: validation with increased fin height of 80nm (target fin heigh).

# FINFET: H<sub>FIN</sub> IMPACT

## H<sub>FIN</sub> > 80NM LEADS TO SATURATION IN PERFORMANCE

Target Fin height set at 80nm

- Taller fins (H<sub>FIN</sub>>80nm) leads to saturation in performance benefit.

- Leads to increase in power only.

- Similar trend obtained across INV and NAND based RO.

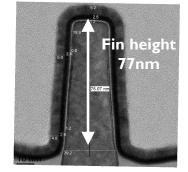

TEM Channel cross-section

CONFIDENTIAL

## FINFET WITH FIN HEIGTH 80NM + S/D EPITAXY: TCAD ASSESSMENT

External resistance improvement with Epitaxied S/D maintained with 80nm high Fins.

TCAD

Fin height 80nm

# EXPERIMENTAL DEMONSTRATION (H<sub>FIN</sub> 80NM)

# EXPERIMENTAL DEMONSTRATION (H<sub>FIN</sub> 80NM)

14

Improvements confirmed in I<sub>ON</sub>/I<sub>OFF</sub> plots.

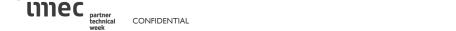

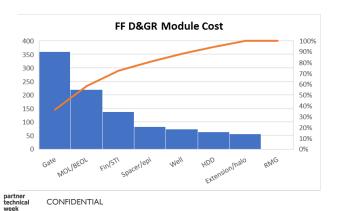

#### RELATIVE MODULES COST COMPARISON WITH S/D EPI & D&GR

#### EPI MODULES ACCOUNT FOR ~6% OF THE FINFET PERI FLOW COST

|                    | planar   | planar GF | planar | FF D&GR | FF D&GR | FF RMG  |

|--------------------|----------|-----------|--------|---------|---------|---------|

|                    | PolySiON |           | D&GR   |         | ері     | N22     |

| Lithography        | 231.91   | 231.91    | 217.72 | 217.72  | 217.72  | 321.06  |

| Deposition         | 184.44   | 308.07    | 319.18 | 321.22  | 380.01  | 339.04  |

| Metalization       | 76.45    | 130.15    | 183.86 | 199.09  | 199.09  | 195.28  |

| Implantation       | 34.4     | 30.88     | 30.88  | 30.88   | 30.88   | 29.13   |

| Dry Etch and Clean | 124.79   | 114.25    | 114.25 | 114.25  | 114.25  | 150.5   |

| Wet Etch and Clean | 31.07    | 37.7      | 32.63  | 34.29   | 36.36   | 43.91   |

| CMP                | 43.44    | 54.05     | 54.05  | 54.05   | 54.05   | 68.71   |

| Metrology          | 9.37     | 15        | 15     | 18.12   | 18.12   | 25.54   |

| Total              | 735.87   | 922.01    | 967.57 | 989.62  | 1050.48 | 1173.17 |

#### See PTW 201810 F801

Calculation assumptions: "R&D flow", thin oxide only, HKMG with I Gate Stack for NMOS and I for PMOS, single I/IV<sub>TH</sub>, periphery only; GF NMOS La; D&GR TiN/Mg/TiN

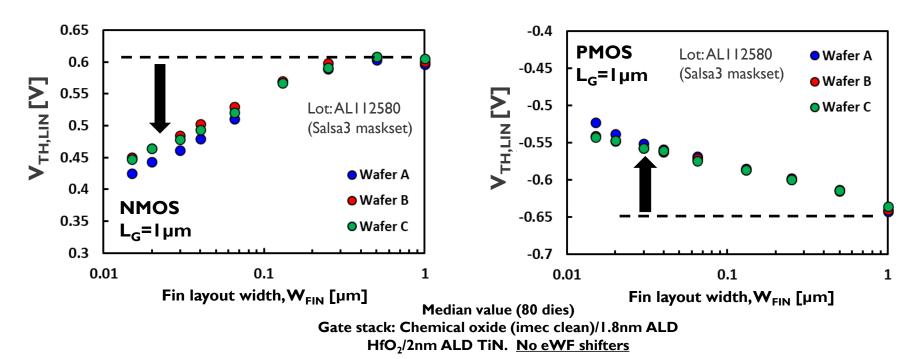

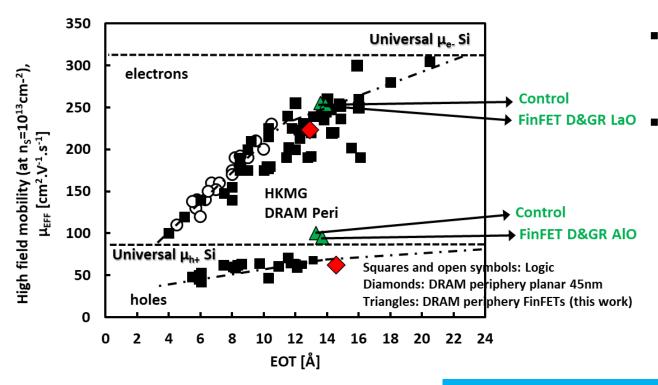

#### HKMG FINFET GATE STACK: THRESHOLD VOLTAGE

FinFETs: lower  $V_{TH}$  compared to Planar (better electrostatic control). eWF tuning with capping layers still needed for low and multi  $V_{TH}$  enablement

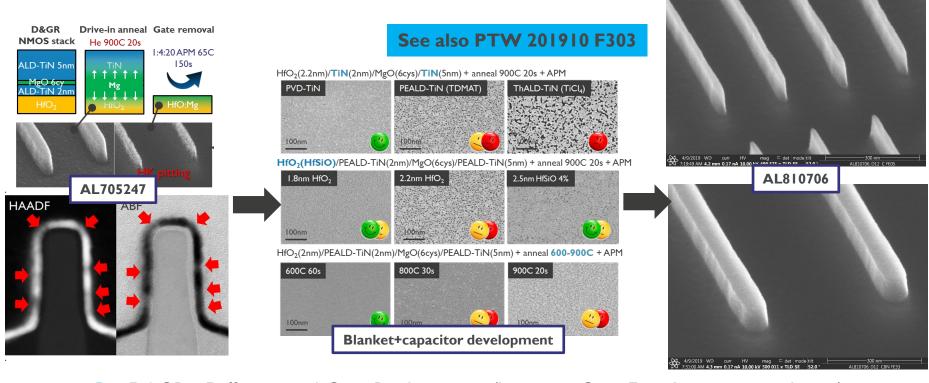

## HKMG FINFET GATE STACK

- D&GR= Diffusion and Gate Replacement (here in a Gate First Integration scheme)

- D&GR process implemented in FinFETs with PEALD TiN

Uniec partner technical CONFIDENTIAL

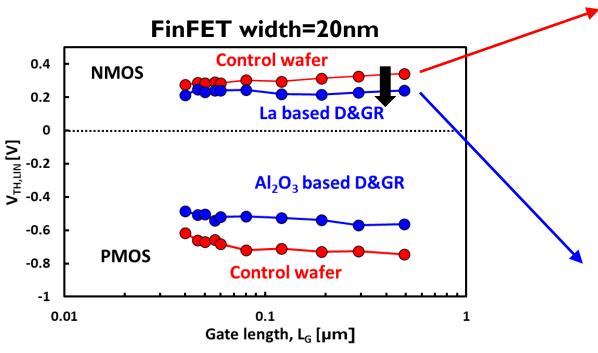

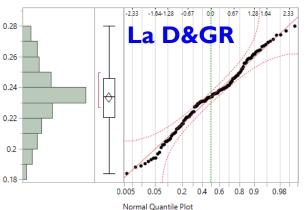

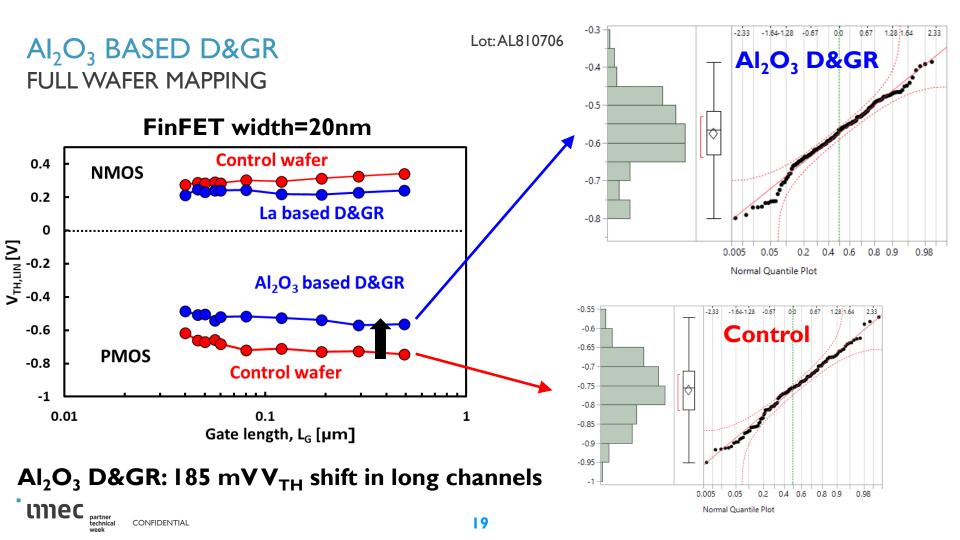

# La BASED D&GR FINFET

**FULL WAFER MAPPING**

0.36 Control 0.35 0.32 0.05 0.05 0.2 0.4 0.6 0.8 0.9 0.98

Normal Quantile Plot

La D&GR: I I 0 mV V<sub>TH</sub> shift in long channels

Lot: AL810706

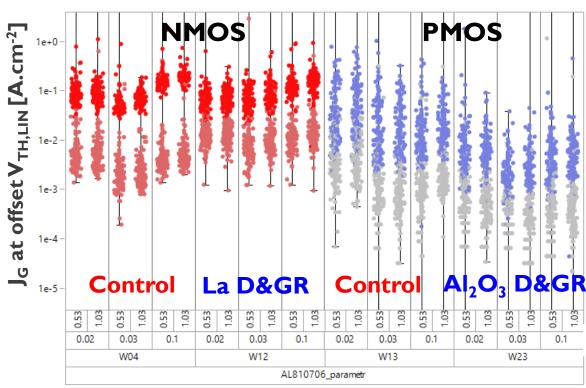

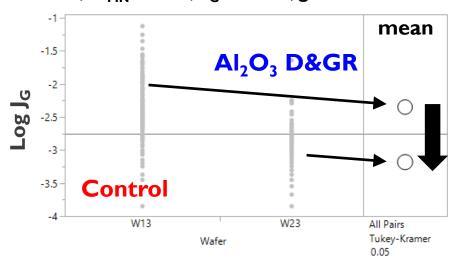

## **D&GR FINFET: GATE LEAKAGE**

#### **FULL WAFER MAPPING**

-1 -0.6 0.6

• 1

Lot: AL810706

Consistent distributions

Gate leakage apparently

not degraded with

D&GR flow

L<sub>G</sub> [µm]

Fin Width [µm]

Water Lot id

CONFIDENTIAL

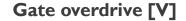

#### **D&GR FINFET: GATE LEAKAGE**

**FULL WAFER MAPPING**

NMOS, W<sub>FIN</sub>=20nm, L<sub>G</sub>=500nm, gate overdrive 0.6V

PMOS, W<sub>FIN</sub>=20nm, L<sub>G</sub>=500nm, gate overdrive 0.6V

Means anova: means are significantly different, w/ a small  $J_G$  increase for NMOS w/ eWF shifters, while for PMOS w/ eWF shifters  $J_G$  is slightly improved.

partner technical

CONFIDENTIAL

## **D&GR FINFET: GATE LEAKAGE**

## **D&GR FINFET: LONG CHANNEL MOBILITY**

- Little mobility variations between control and D&GR FinFET.

- Note: trade-off to find between obtained eWF shift and mobility degradation, through drive-in anneal thermal budget.

**Reliability performance: presentation F205**

## **OUTLINE**

- Introduction

- DRAM peripheral devices

- NAND peripheral devices

- Conclusions

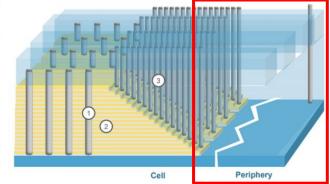

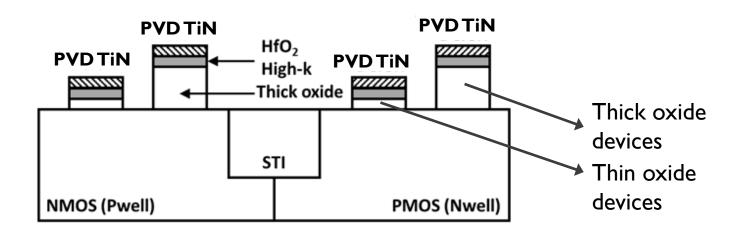

## EXAMPLE OF RELEVANT DIMENSIONS IN NAND PERIPHERAL DEVICES

- Logic LV (e.g.: Page Buffer)

- $L_G \sim 200-300 \text{ nm}$ ;

- Gate stack oxide thickness ~ 5 nm;

- CPP<500 nm;</li>

- S. Lee et al., ISSCC'18

- Logic HV (e.g.:Word Line Decoder/Switch)

- $L_G \sim 1000 \text{ nm}$ ;

- Oxide thickness >~ 40-50nm

**Courtesy A. Spessot**

\* Data extracted from state-of-the-art 3D NAND technology (# layers > 90) reverse engineering report

3D NAND memory conceptual view

https://www.extremetech.com/computing/212108-samsung-announces-new-256-bit-3d-nand-stacked-48-layers-high

#### Main objectives:

- Assess the effect of using a thick oxide device (5 to 40nm ISSG  $SiO_2$ ) with a 2nm  $HfO_2$  high-k/5nm PVD TiN Metal gate on top, vs. a purely PolySilicon/SiO<sub>2</sub> gate stack.

- Assess the effect of 'NAND anneal' (1050 °C, 45s) on gate stack and junctions.

- Assess the resistance of current junctions to higher supply voltages.

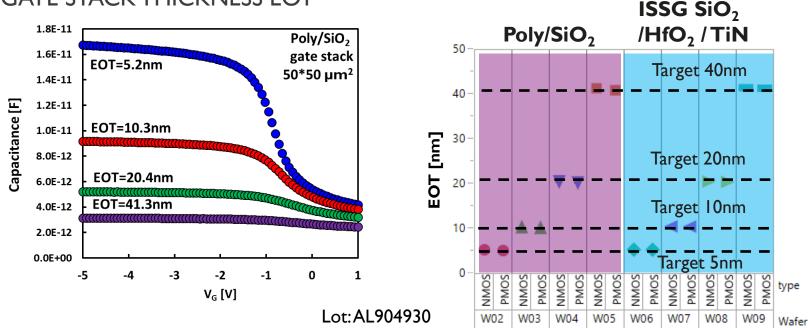

## **GATE STACK THICKNESS EOT**

- Good EOT consistency between Poly/SiO<sub>2</sub> and HKMG gate stacks.

- **EOT** on target.

\*Note:'Target 40nm' splits are using RTO SiO<sub>2</sub> iso ISSG.

CONFIDENTIAL

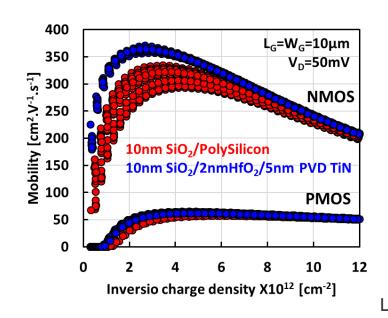

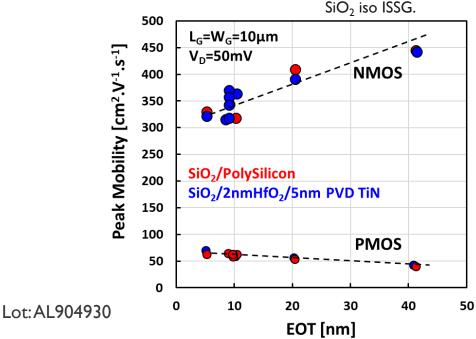

SPLIT CV LONG CHANNEL MOBILITY

\*Note:'Target 40nm' HKMG splits are using RTO SiO<sub>2</sub> iso ISSG.

$HfO_2/TiN$  layers on top of thick  $SiO_2$  have no impact on long channel mobility, for all investigated thicknesses.

CONFIDENTIAL

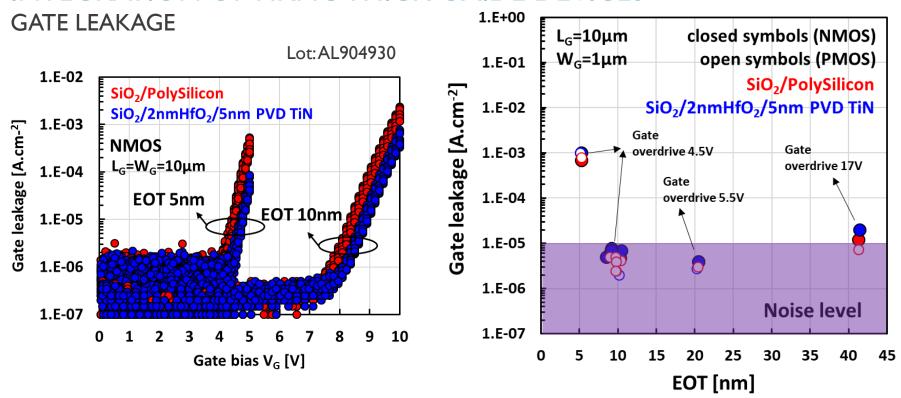

HfO $_2$ /TiN layers on top of thick SiO $_2$  have no impact on long channel gate leakage.

unec

CONFIDENTIAL

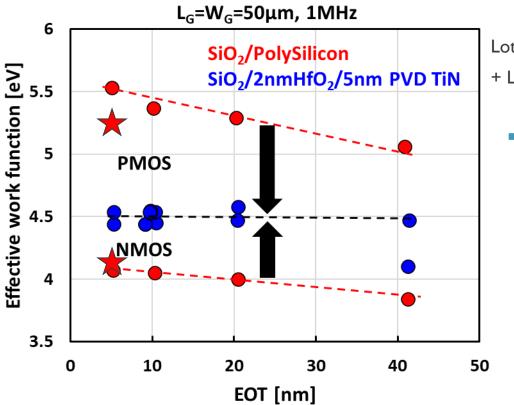

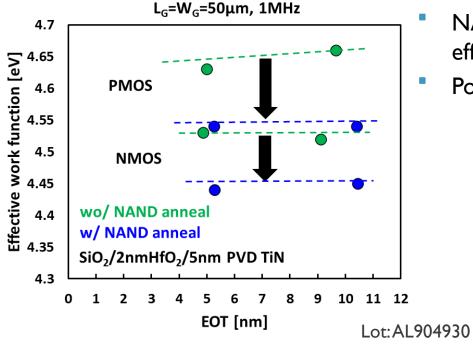

#### **EFFECTIVE WORK FUNCTION**

Lot AL904930 (NAND periphery)

+ Lot AL504455 (DRAM periphery lot, )

HKMG gate stacks: effective work functions move toward mid-gap.

unec

CONFIDENTIAL

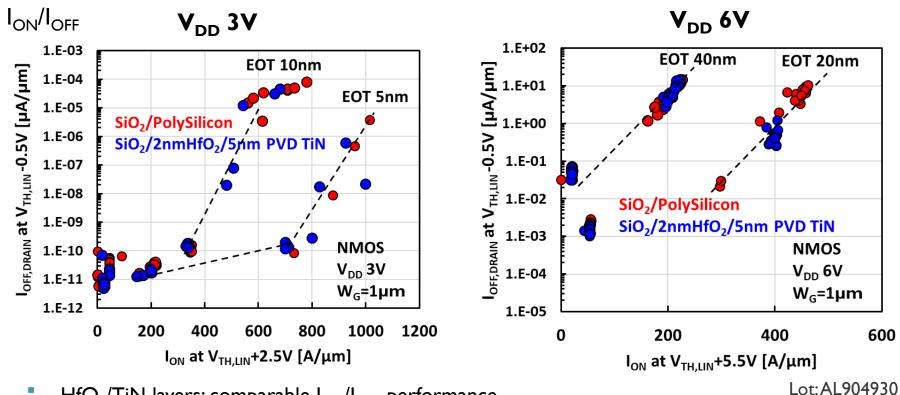

$HfO_2/TiN$  layers: comparable  $I_{ON}/I_{OFF}$  performance

Reliability performance: presentation F205

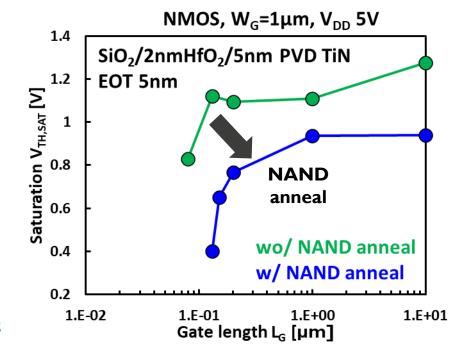

## ASSESSMENT OF NAND ANNEAL IMPACT

NAND anneal: strong roll-off increase.

- NAND anneal effect on HKMG gate stacks: effective work function decrease.

- Possible model: passivation of oxide charges.

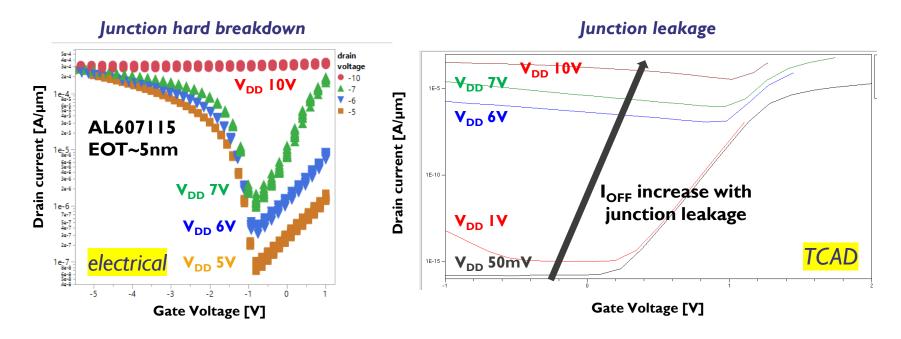

- Readout from previous lots: BKM junctions break above 7V, for both NMOS and PMOS, and junction leakage alone might be is a serious issue.

- Electric field in the junction should be decreased for  $V_{DD}$ >7V.

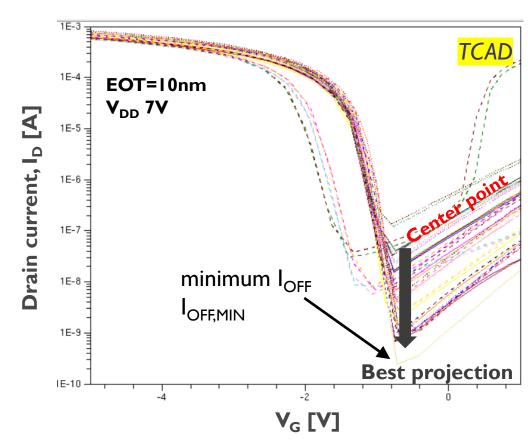

- TCAD based DOE

(Parameters: Anti Punch

Through dose, LDD dose,

HDD dose and energy).

- With doses reduction and implant energy adjustment:

2 decades minimum I<sub>OFF</sub> reduction reached.

- Proposal for new junctions set.

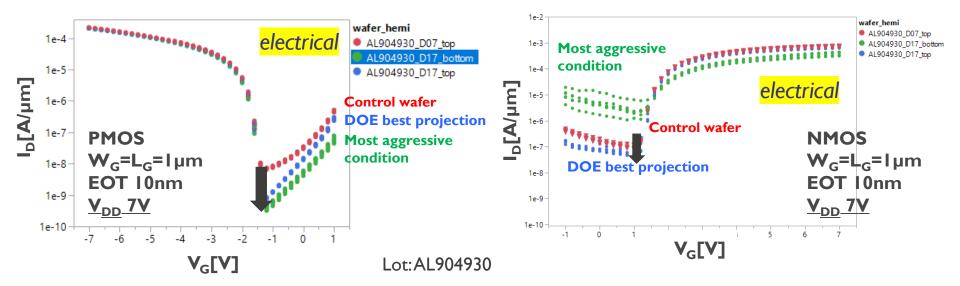

## JUNCTIONS - INCREASED SUPPLY VOLTAGE

#### **EXPERIMENTAL READ-OUT**

- PMOS: the 1 to 2 decades predicted by TCAD are obtained w/ the modified junction conditions.

- NMOS: marginal improvements.

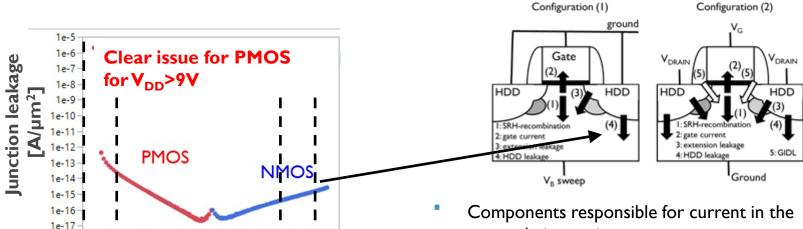

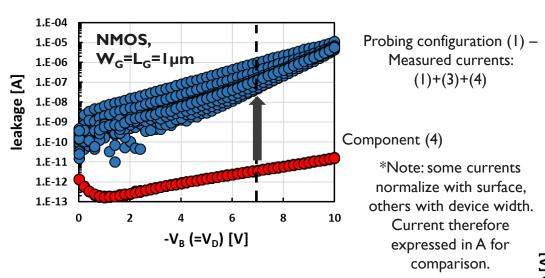

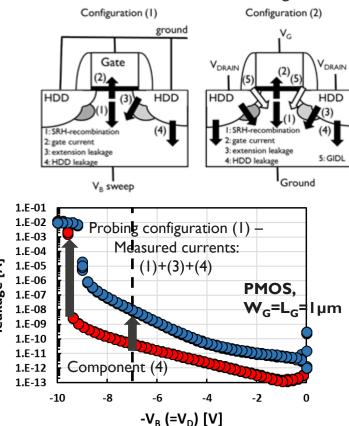

# JUNCTIONS ANALYSIS

- Probing (4) **HDD/Well junction leakage.**

- Measurements done on area diodes.

- PMOS junction: high current at  $V_{DD}$  10V, due to avalanche onset.

accumulation regime:

- Junction leakage (HDD to well leakage (4), HDD/LDD to Halo to well leakage (3)).

- **GIDL** (5)

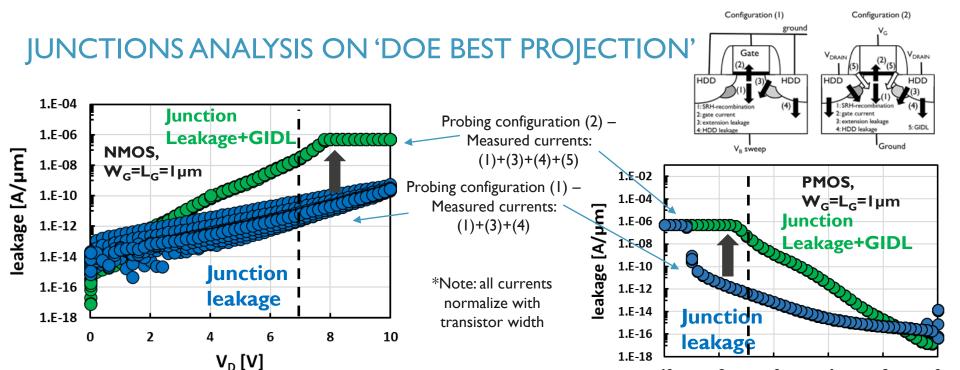

# JUNCTIONS ANALYSIS ON 'DOE BEST PROJECTION'

- At V<sub>DD</sub> 7V, NMOS/PMOS HDD to well leakage component (4) << extension leakage.</li>

- Above ~V<sub>DD</sub> 9V, PMOS HDD to well leakage component (4) becomes the dominant source of junction leakage.

CONFIDENTIAL

unec

Wafer: AL904930 'DOE best guess'

$^{\bullet}$  At  $V_{DD}$  7V and above, NMOS/PMOS GIDL is several orders of magnitude higher than junction leakage.

$V_D[V]$

Wafer: AL904930 'DOE best guess'

unec

Overall conclusion: if V<sub>DD</sub>>7V, GIDL current (NMOS/PMOS) and HDD to well leakage (PMOS) are the key parameters to optimize.

## **OUTLINE**

- Introduction

- DRAM peripheral devices

- NAND peripheral devices

- Conclusions

# CONCLUSIONS (1/2)

## DRAM peripheral devices learning:

- FinFET with Fin height 80nm and undoped epi S/D + Ion Implantation:

- Demonstrated current improvement wrt no Epi fins, for no short channel margin degradation.

- Demonstrated current improvement wrt Fin height 40nm with Epi.

- Improvements confirmed in I<sub>ON</sub>/I<sub>OFF</sub> (normalized per footprint).

- Demonstration of D&GR FinFET w/ fin height 80nm & PEALD TiN:

- II0mVV<sub>TH</sub> shift w/ LaO D&GR, I85mVV<sub>TH</sub> shift w/ Al<sub>2</sub>O<sub>3</sub> D&GR, for no gate leakage/mobility penalty.

- No Gate leakage penalty wrt to D&GR planar baseline.

# CONCLUSIONS (2/2)

## NAND peripheral devices learning:

- Poly/SiO<sub>2</sub> & HKMG (SiO<sub>2</sub> ISSG/HfO<sub>2</sub>/PVD TiN) thick oxides integration:

- Gate leakage/Long channel mobility/ $I_{ON}(I_{OFF})$ : no impact of HKMG gate stacks on top of SiO<sub>2</sub>.

- NAND anneal impact: no EOT variation, eWF reduction, and roll-off clearly increased with NAND anneal.

- <u>lunctions learning:</u>

- Current BKM junctions work with EOT=5/10nm up to V<sub>DD</sub>=7V.

- Cutting extension doses (LDD, HDD, APT, ...) yield some  $I_{OFF,MIN}$  reduction, as predicted by TCAD, but not enough to enable high  $V_{DD}$ .

- Decreasing GIDL current is key for the transistor to sustain higher supply voltages.

- HDD to Well leakage is also very high in PMOS for V<sub>DD</sub>>9V.