## Scaling in Electron Devices and Electronic Systems

A DECADAL PROJECTION IN MEMORY TECHNOLOGIES

DerChang Kau (高德昌) Intel Fellow, Director of External Technology Pathfinding Corporate Planning Group

### **Abstract**

Since 1897's discovery of electron by Sir Joseph John Thomson (Nobel Laureate 1906), electron devices started the journey of the 2nd industrial evolution onward. Under the guidance of Moore's Law and Dennard Scaling, electron devices' density increase at cadence and electronic systems strive maintaining power density while improving performance. This talk invites participants first travel down the time tunnel of electron devices. We will jointly revisit researches in material synthesis and device exploration in atomistic switching physics to disrupt electrostatic switching mechanism. Memory technology will be used to project decadal electronic system advances in homogenous and heterogenous integration through VLSI fabrication and chiplet interconnect processes.

### **About DerChang Kau**

An Intel Fellow and a Director of External Technology Pathfinding, exploring chip manufacturing and system integration technologies aligning with product roadmap. For more than 3 decades, DerChang has been involved in various technology pathfinding and scaling deployment, including logic, memory, flash, embedded memory, mixed-signal, radio and advanced packaging. He also led Intel's efforts to define strategic direction for atomistic memory switching and threshold switching devices and drove the product initiatives of Optane Memory Technology. He holds MS degrees in Electrical Engineering from OSU.

## **Outline**

- Travel down the time tunnel of electron devices

- A Centennial Journey of Electrical Charges

- State of Art of Memory Technologies

- System hierarchy and incumbent deployment

- A holistic view of Memories: Cell, Array and Subsystem

- Memories in next decade

- Cache, Memory and Storage

- Near Memory and Storage Class Memory

# TRAVEL DOWN THE TIME TUNNEL OF ELECTRON DEVICES

A Centennial Journey of Electrical Charges

## **Discoveries of Electron**

**1895 Wilhelm Conrad Röntgen** (1845 - 1923) discovered X rays, for which he received the first Nobel Prize for physics in 1901. The "hand" was taken in 1896 with cathode-ray discharge. He later demonstrated the metallurgical and medical use of X rays.

https://www.nobelprize.org/prizes/physics/1901/summary/

**1897 Sir Joseph John Thomson** (1856 - 1940) discovered and identified the electron, for which he received the Nobel Prize for physics in 1906. Thomson demonstrated that cathode rays were actually units of electrical current made up of negatively charged particles of subatomic size as an integral part of all matter and theorized the "plum pudding" model of atomic structure in which a quantity of negatively charged electrons was embedded in a sphere of positive electricity, the two charges neutralizing each other.

https://www.nobelprize.org/prizes/physics/1906/summary/

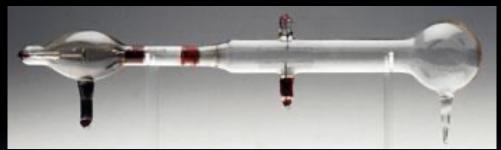

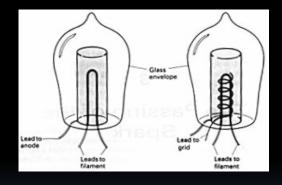

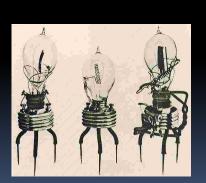

# **Innovations of Vacuum Electron Devices**

1905 Sir John Ambrose Fleming

(1849 - 1945) made the first diode tube, the Fleming valve. 1907 Lee De Forest (1873 - 1961) added a grid electrode to Flemings' valve and created the triode tube,

The device had three leads, two for the heater and the cathode and the other for the plate.

https://madeupinbritain.uk/Vacuum\_Tube

later improved and called the Audion.

He was a prolific inventor, and was granted more than 300 patents in Electronics

https://www.britannica.com/biography/Lee-de-Forest

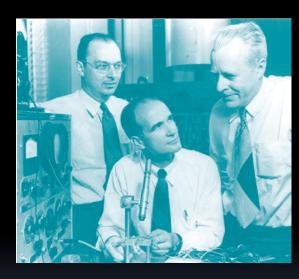

# Revolution of Electronics – From Vacuum Science to Solid State Physics

In 1948, John Bardeen (1908 - 1991), William Bradford Shockley (1910 - 1989), Walter Houser Brattain (1902 - 1987) invented the transistor for Bell labs, sharing the 1956 Nobel Physics prize for the invention.

Shockley's insight of "minority carrier injection" became the bible of the new era

[1] W. Shockley, "The Theory of *P-N* Junctions in Semiconductors and *P-N* Junction Transistors." Nokia Bell Lab, July 1949 [2] W. Shockley, "Electrons and Holes in Semiconductors: With Applications to Transistor Electronics", Van Nostrand, Jan, 1050

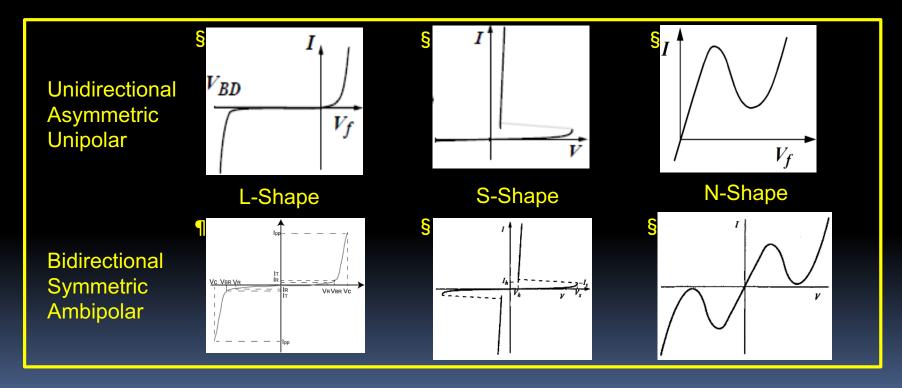

### Thermionic emission (single-/dual-carrier) and beyond

**Diode: two terminals and exhibiting a nonlinear I-V,** *IEEE Standard Dictionary of Electrical and Electronics Terms,* 1980

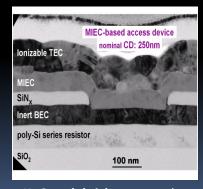

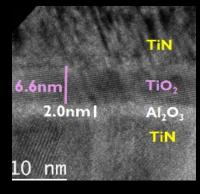

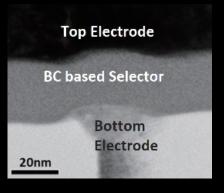

### **Thin Film Diode Candidates for Cross Point Memory**

Y. Sasago, et. al., VLSI '09. T2B-1

K. Gopalakrishnan, et. al., VLSI '10. TS19.41

B. Govoreanu, et.al., IEDM'13. S10.2

S.G. Kim, et. al., IEDM '15. S10.3

S. Yasuda, et.al., VLSI, 2017. T2-4

D. Kau, et. al., IEDM '09. S27.1

# **Threshold Switching Phenomenology & Mechanisms**

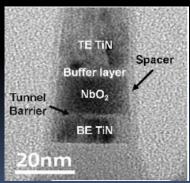

| Mechanism          | Thermionic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Filamentation                             | Tunneling                                                                                                                                                                            | MIEC                                           | MIT                                                         | ОТЅ                                                                                  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Construct.         | P-N or M-S Jx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Ion (Ag+) in Ox                           | MIM                                                                                                                                                                                  | Cu+ in SE                                      | NbO <sub>2</sub>                                            | Chalcogenide                                                                         |

| Switching          | Electronic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Atomistic                                 | Electronic                                                                                                                                                                           | Atomistic                                      | Atomistic                                                   | Electronic                                                                           |

| Polarity           | Unidirectional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Bidirectional                             | Bidirectional                                                                                                                                                                        | Bidirectional                                  | Bidirectional                                               | Bidirectional                                                                        |

| $	au_{\sf switch}$ | sub nsec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ns ~ 100s ns                              | ps or faster                                                                                                                                                                         | ns ~ 100s ns                                   | ns to 10s ns                                                | sub ns                                                                               |

| J <sub>MAX</sub>   | < 10MA/cm²                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-10MA/cm <sup>2</sup>                    | < 1MA/cm²                                                                                                                                                                            | ~10MA/cm²                                      | > 10MA/cm <sup>2</sup>                                      | > 10MA/cm²                                                                           |

| $J_{Inhibit}$      | <1A/cm²                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <1KA/cm²                                  | <1KA/cm²                                                                                                                                                                             | <1KA/cm²                                       | <1KA/cm²                                                    | <1KA/cm²                                                                             |

| $V_{Inhibit}$      | < 3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | < 1V                                      | <3V                                                                                                                                                                                  | < 1V                                           | < 3V                                                        | < 3V                                                                                 |

| I-V                | 10°   Forward bias   Forward bias | O 10° 10° 10° 10° 10° 10° 10° 10° 10° 10° | 10° lin-scale  W 10° lin-scale  10° lin-scale | 100µA                                          | 10 PtTE/NbO2/HfO2/PtBE 10-5 150 mmx 150 mm 10-7 Voltage (V) | 1e+7<br>1e+6<br>1e+6<br>1e+4<br>1e+3<br>-7 -6 -5 -4 -3 -2 -1 0 1 2 3 4 5 6 7<br>V(V) |

| Reference          | Y. Sasago, et. al.,<br>VLSI '09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | J. Yang, et.al.,<br>Adv Func Mtls (2018)  | B. Govoreanu, et.al., IEDM'13. P10.2                                                                                                                                                 | K. Gopalakrishnan, et.al., VLSI Symposium '10. | X. Liu et.al.,<br>EDL Oct.'14                               | S. Yasuda, et.al.,<br>VLSI symposium, '17,                                           |

# STATE OF ART OF MEMORY TECHNOLOGIES

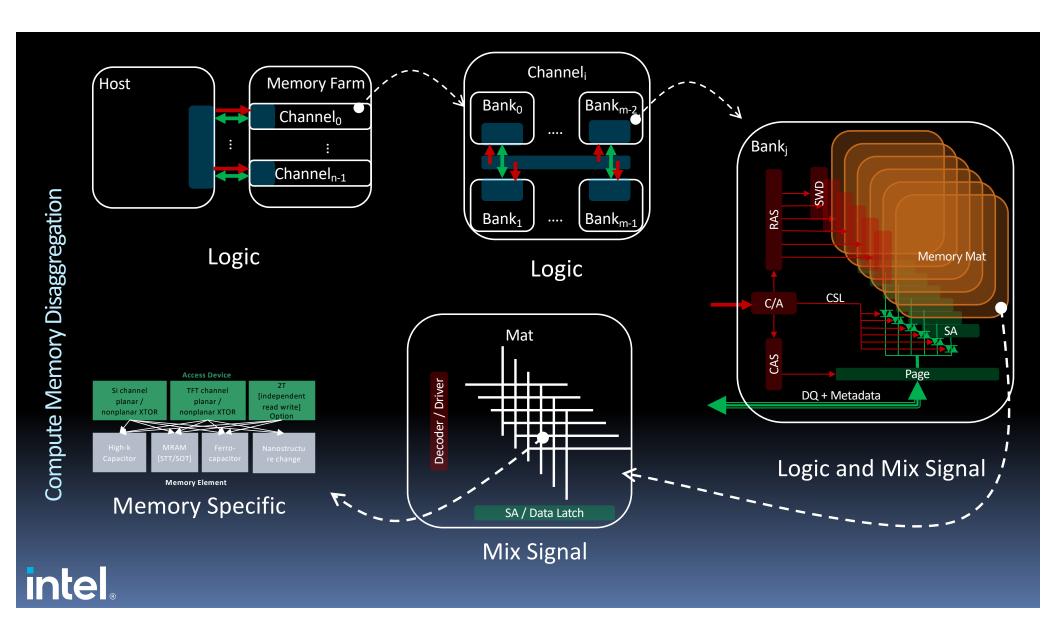

System hierarchy and incumbent deployment A holistic view of Memories: Cell, Array and Subsystem

# We are in a data-centric world Data are

stored, processed, and analyzed

Every Day Data is **EXPLODING**

3TB

1.5 GB **AVERAGE**

50 GB

SMART HOSPITAL

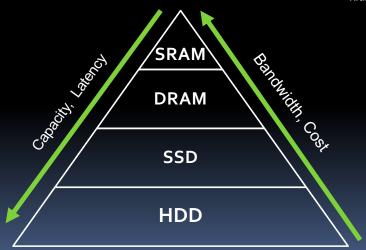

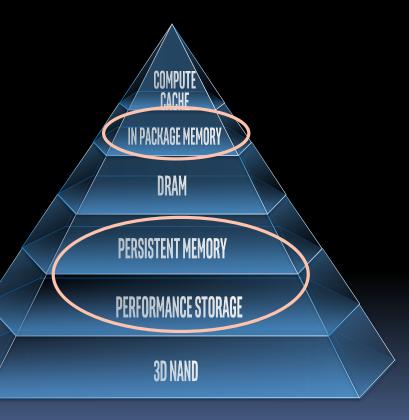

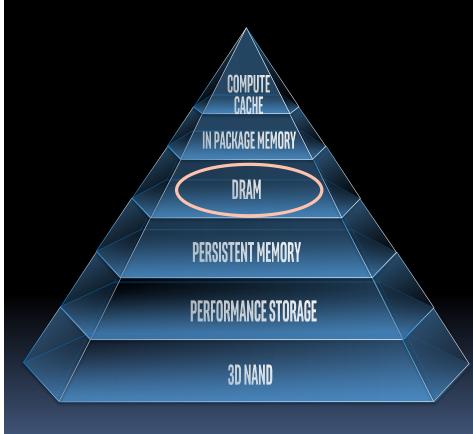

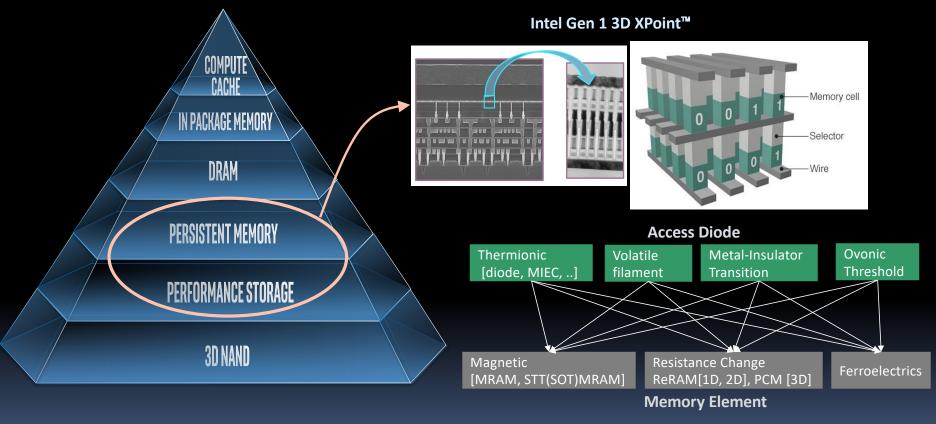

# **Incumbent Technologies in Memory/Storage Hierarchy**

each of which has greater capacity than the preceding but which is less quickly accessible

"The Memory Organ — Ideally one would desire an indefinitely large memory capacity such that any particular ... word would be immediately ... available. ... It does not seem possible physically to achieve such a capacity. ... We are therefore forced to recognize the possibility of constructing a hierarchy of memories, each of which has greater capacity than the preceding but which is less quickly accessible."

Preliminary Discussion of the Logical Design of an Electronic Computing Instrument

Arthur Burks, Herman Goldstine and John von Neumann, June/28/1946

A memory cell consists one storage element and one or more access switch(es)

- Storage Elements:

- Latch: Circuit based or Thyristor device

- Electrostatic memory switch: Two terminal capacitor, floating gate/plate, charge traps devices

- Atomistic memory switch: Phase change, Magneto Tunnel Junction, Ferroelectric, Oxy-Vacancy (Filamentation)

- Access Devices:

- 3 terminal Transistor:

- Pass logic (1T) is typical used for read/write access.

- Gated common-source amp (2T) is used for read only access

- Biased Source-follower (1T) is used for read only access

- Two-terminal diodes: Thermionic (PN junction, Schottky barrier,

DIAC & etc), MIT, OTS MIEC, volatile filamentation and etc.

Brain teaser: multiple memory storage elements share one access device

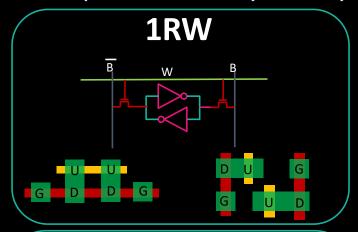

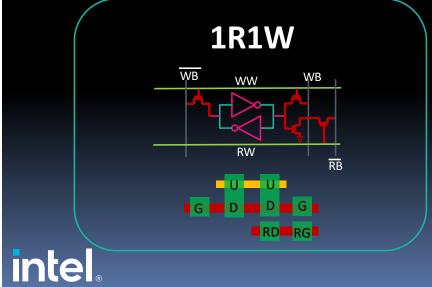

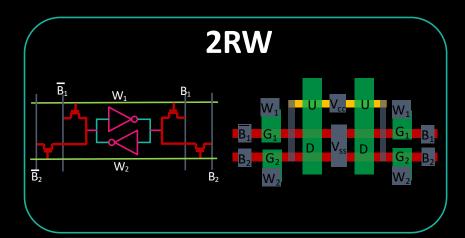

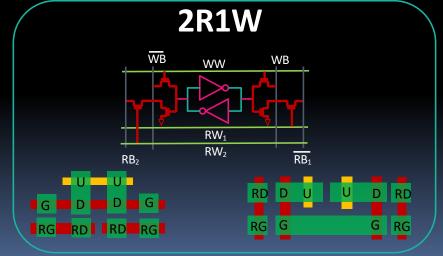

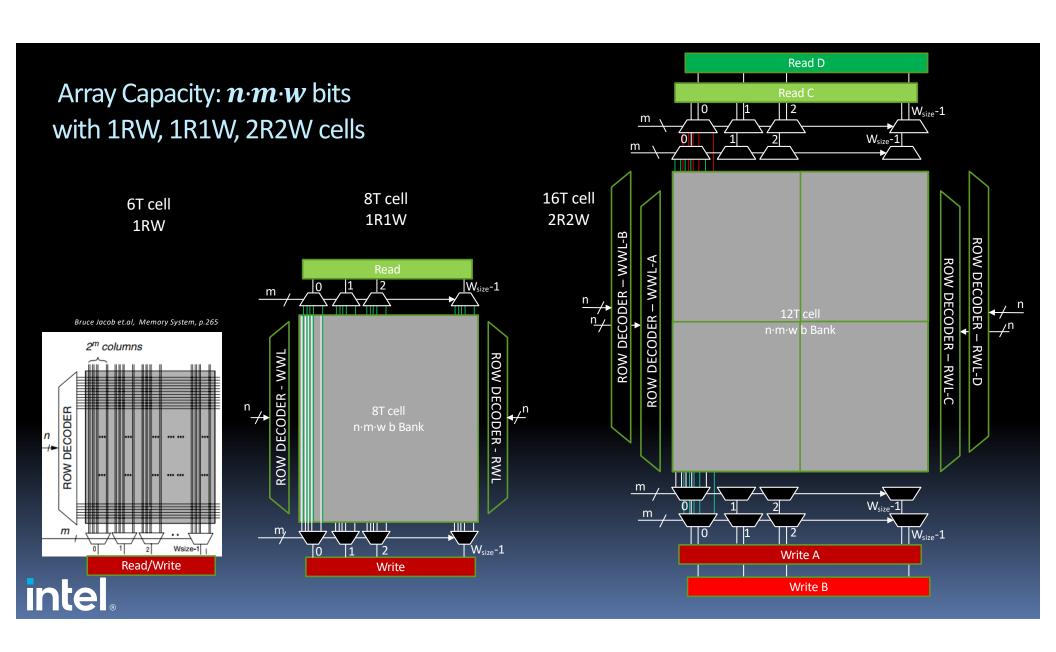

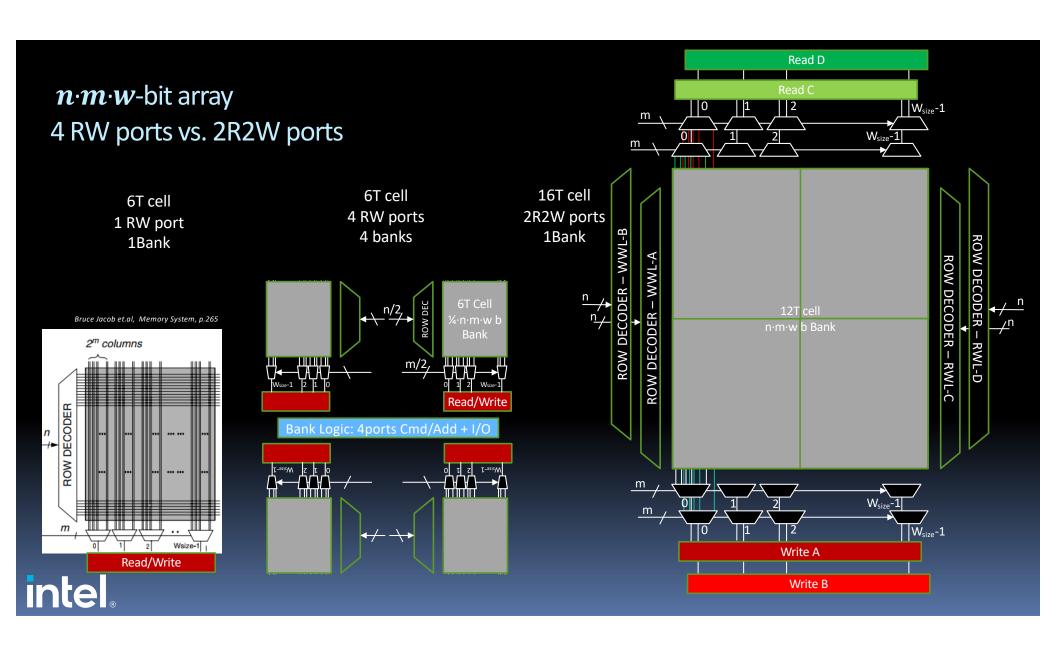

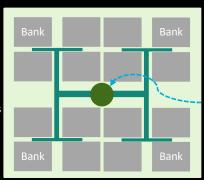

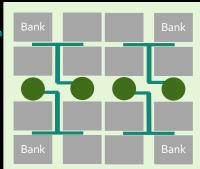

# Multi-ported SRAM Symmetry

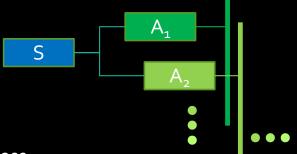

# Why "Multi-Port Memories"

- Multi-Port Memories have all the features of single-port memories

- Used for multi-tasking

- Parallel Processing increase bandwidth without cycle time compressing

- "Simultaneously" read and write data or read-while-write

- Examples

- Dedicated Memory In a branch-target-buffer memory to keep track branch prediction and decision

- Shared Memory multiple requests for data from multi-cores or networked processors

- Analysis and Synthesis

- Multi-port (MP) SRAM is a commonly used for cache design as it allows simultaneous R/W accesses.

- For CISC CPUs, such as the X86 architecture, MP cache such as mRnW configuration is used

- For RISC CPUs, such as the ARM architecture, SP cache such as 1RW with multi-bank (MB) configuration is used.

- Overall, the choice of cache memory organization and multiport SRAM configuration depends on the specific design goals, performance requirements, and trade-offs between cost, power consumption, and performance.

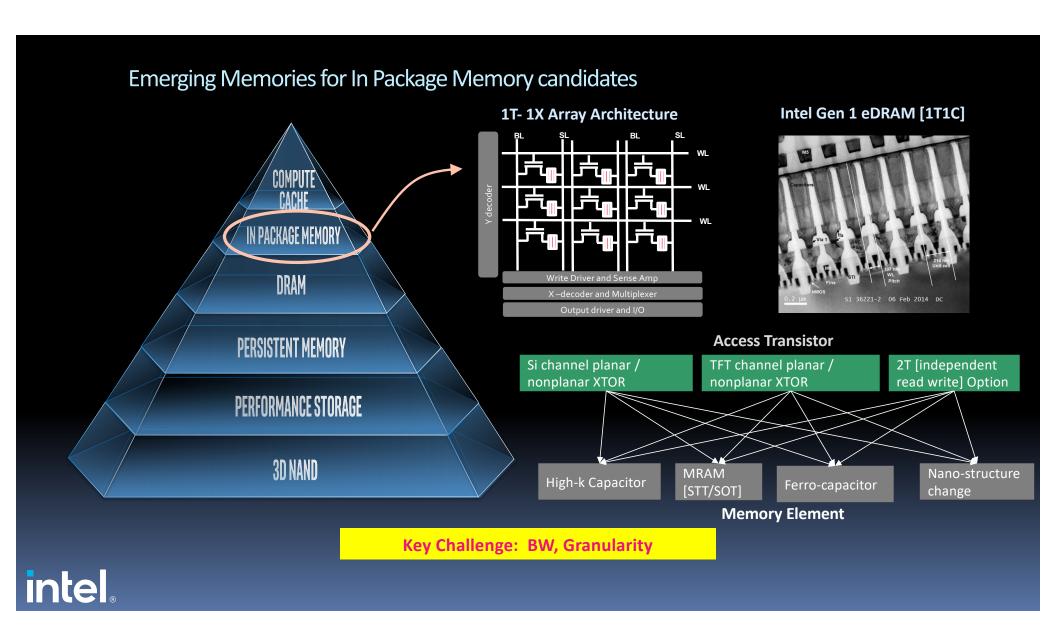

# MEMORIES IN NEXT DECADE

Cache, Memories and Storage

Near Memory and Storage Class Memory

### Gaps to fill between Caches, Main Memory & Storage beyond scaling

### "It's the Memory, Stupid!

... Processor Speed Has Outstripped Memory ... today's chips are largely able to execute code faster than we can feed them with instructions and data. There are no longer performance bottlenecks in the floating-point ... The real design action is in memory subsystems—caches, buses, bandwidth, and latency...I expect that over the coming decade memory subsystem design will be the only important design issue for microprocessors."

Architects Look to Processors of Future, Microprocessor Report, V10, No. 10, Aug/5/1996 Dick Sites, Digital Equipment Corp

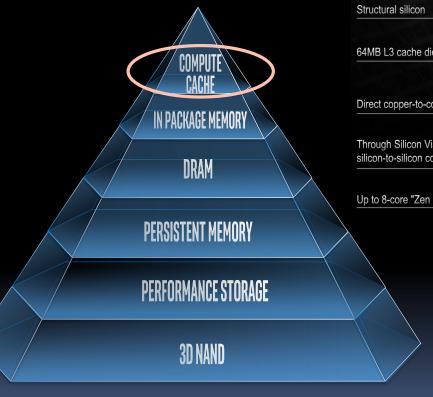

# **Cache Memory in next decade**

Structural silicon

64MB L3 cache die

Direct copper-to-copper bond

Through Silicon Vias (TSVs) for silicon-to-silicon communication

Up to 8-core "Zen 3" CCD

\*L. Su, "High-Performance Computing: Services and Products Essential to our Daily Lives" Computex, 2021.

- Scaling trajectory of mainstream logic technology yet optimized for SRAM

- IP folding to increase Cache capacity: Core

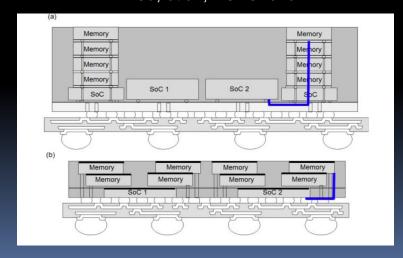

- Enabling technology: TSV, back-side metallization, reconstructed wafer, waferwafer (hybrid) bonding,

- Key Challenges: Power and Thermal

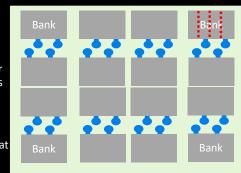

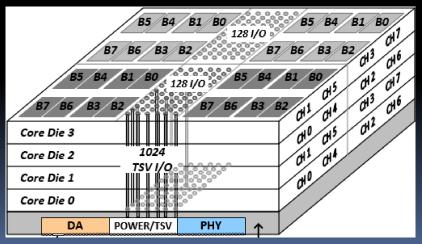

### Chiplet stacking to improve packing density, Power and Bandwidth

M. O'connor, et.al., ACM/MICRO 2017

#### **HBM2 Channels:**

Shared 16 GB/s Channel 16 banks per channel BW of idle banks is "wasted"

#### Quad-Bandwidth HBM Channels: Four 16 GB/s Channels

Four 16 GB/s Channels Shared interbank bus High datapath & array act. energy

### Fine-Grained DRAM Arch:

Partition Bank into narrower pseudo-banks 32 Dedicatedm Local 2 GB/s Channel Local, parallel I/O per bank at lower energy

#### HBM, H Jun, et.al., IMW'2017

#### A. Su, et.al., ECTC2019

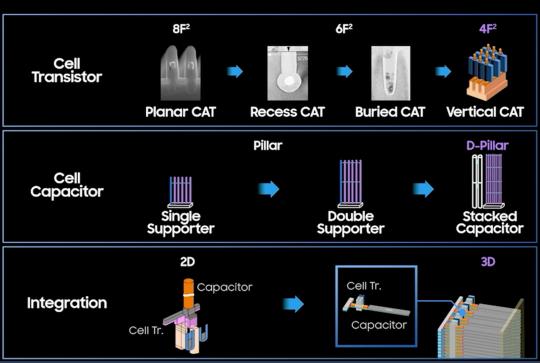

# **DRAM's Journey beyond Trench Capacitor**

Kinam Kim, IEDM'21, Plenary Session 1.1

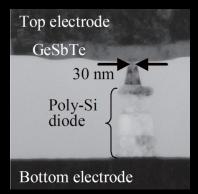

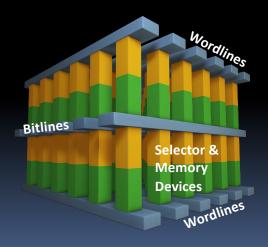

### Emerging Memories for Persistent Memory in 3D Cross Point Architectures

**Key Challenge: Matching Memory & Selector**

### Consideration of architecting a cross point memory technology

Desirable Attributes: Nonvolatile, Low Cost, High Performance

- Simple scalable, 3D stackable construction; low D·T, BEOL compatible with mainstream IC manufacturing

- Memory switching in atomistic state (bulk); superior scalability than electrostatic memory switching physics

- Individual cell access, small granularity

- Fast switching materials + local low resistance metal interconnect

### Challenge: to "mate" selector and memory in achieving a non-linear I-V for array access

#### **Potential Memory Options:**

- Spin polarization

- Phase change/segregation

- Ferroelectric hysteresis

- Interfacial barrier modulation

- Oxygen vacancy relocation

- lonic transport

- NRAM (?)

#### **Potential Selector Options:**

#### Unidirectional

- Homo/Heterogenous P/N Jx

- Schottky Barrier

#### **Bidirectional**

- Mixed ionic-electronic conduction

- Tunneling barrier

- Metal-insulator transitions

- Ovonic threshold switching

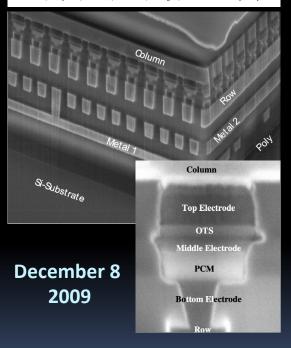

# In Pursuit of a Dream ...

September 28

1970

Amorphous semiconductors Part I

Nonvolatile and reprogramable, the read-mostly memory is here Integrated arrays combine amorphous and crystalline technologies; new memories could be prealize promise of microprograming

Pip 18, Nale and D. I. Niklar, Price foreign deviate in the price of the programming of the prealize promise of microprograming of the prealize promise of the programming of the prealize promise of the programming of the prealize promise of the programming of the prealize programming of the pre

#### A stackable cross point phase change memory

DerChang Kau, Stephen Tang<sup>1</sup>, Ilya V. Karpov, Rick Dodge<sup>1</sup>, Brett Klehn, Johannes A. Kalb, Jonathan Strand<sup>1</sup>, Aleshandre Diaz<sup>2</sup>, Nelson Leung, Jack Wu<sup>3</sup>, Sean Lee, Tim Langtry<sup>1</sup>, Kuo-wei Chang, Christina Papagiani<sup>1</sup>, Jinwook Lee, Jermey Hirsi<sup>1</sup>, Sweitha Erra, Eddie Flores<sup>2</sup>, Nick Righos, Heman Casto<sup>2</sup> and Giapapolo Spadini

August 13 2020

**A Half Century Endeavor**

D. Kau, VLSI-TSA 2021

intel

Conclusion

28

# **Long gestation of Disruptive Memory Technologies**

64Mb

180nm ½ Pitch

6-Mask Sublitho Heater

Damascene PM,

Subtractive SD

**PoC: Cell and Array**

**Research Graduation**

64Mb

50nm ½ Pitch,

2-Mask

Dual Deck,

Self Aligned

Subtractive Cell

**2<sup>nd</sup> Production Generation**

256Gb

41nm Pitch

Quad Deck

Self Aligned

Subtractive Cell

**Ideation**

2007 2012 2015

2003 2010 2013

4Kb

200nm feature,

4-mask

Sublitho Heater

Damascene PM

Subtractive SD

1970

64Mb

100nm feature

2-Mask

Self-Aligned,

Subtractive Cell

**PoC: Process Architecture**

128Gb

41nm Pitch

Dual Deck

Self Aligned

Subtractive Cell

1<sup>st</sup> Production Generation Scaled Line/Space

2019

**3**<sup>rd</sup> Production Generation

PoC: Proc: P

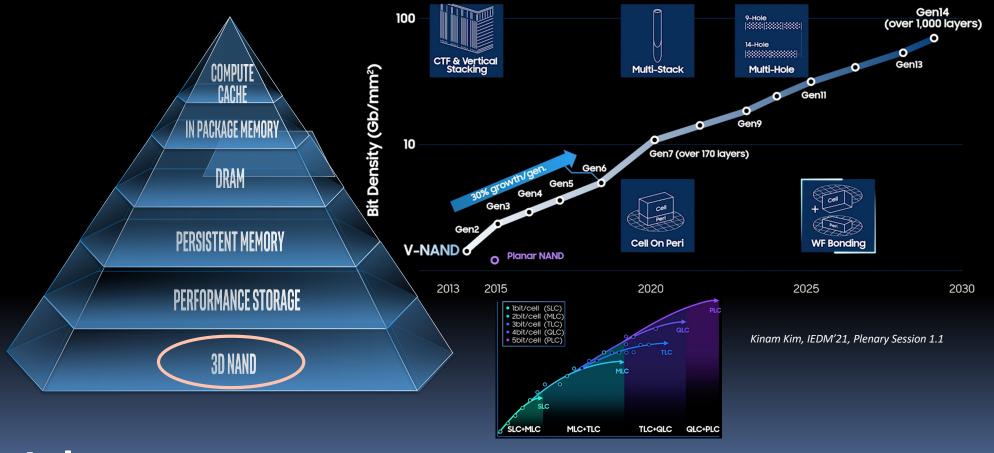

## 3D NAND in next decade will continue to drive \$/bit on par with HDD

Tiering/Decking engineering + multi-level placement algorithm

# **Takeaway of Advances of Memory Technologies**

- Universal memory

- Universal memory often sought, but hierarchy always existed and likely always will be

- FoM must be benchmarked with respect to the corresponding hierarchy of memories

- Disrupt memory technology

- Typically long gestation of Disruptive Memory Technologies

- Mainstream memories hard to establish; hard to displace or to replace;

DRAM replaced Core memory in 1960's and SSD displacing spin drive in 2000's

- Memory technology research to productization can take decades and once productized, achieving mainstream is still not guaranteed

- Memory Subsystem

- Modular, Modular, Modular

- Power/Thermal conscious: Energy from I/O and from moving bits back/forth becoming limiting

- 3D (monolithic, wafer-wafer) and packaging of multi-chip

- → TTM and Cost driven

- Pair memory tech research with compute architecture/hierarchy research.

- Software (often ignored ) enabling to alleviate adoption barriers or to unlock value