**Stacked Integrated Circuits**

# STANDARDS

**IEEE Computer Society**

Developed by the Test Technology Standards Committee

IEEE 1838™-2019

# IEEE Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits

Developed by the

Test Technology Standards Committee of the IEEE Computer Society

Approved 7 November 2019

**IEEE SA Standards Board**

**Abstract:** IEEE Std 1838 is a die-centric standard; it applies to a die that is intended to be part of a multi-die stack. This standard defines die-level features that, when compliant dies are brought together in a stack, comprise a stack-level architecture that enables transportation of control and data signals for the test of (1) intra-die circuitry and (2) inter-die interconnects in both (a) pre-stacking and (b) post-stacking situations, the latter for both partial and complete stacks in both pre-packaging, post-packaging, and board-level situations. The primary focus of inter-die interconnect technology addressed by this standard is through-silicon vias (TSVs); however, this does not preclude its use with other interconnect technologies such as wire-bonding.

**Keywords:** 3D test access, flexible parallel port, FPP, IEEE 1838, multi-tower stack, primary test access port, scan, secondary test access port, test, through-silicon via, TSV

Copyright © 2020 by The Institute of Electrical and Electronics Engineers, Inc. All rights reserved. Published 13 March 2020. Printed in the United States of America.

IEEE is a registered trademark in the U.S. Patent & Trademark Office, owned by The Institute of Electrical and Electronics Engineers, Incorporated.

PDF: ISBN 978-1-5044-6343-0 STD23997

Print: ISBN 978-1-5044-6344-7 STDPD23997

IEEE prohibits discrimination, harassment, and bullying.

For more information, visit https://www.ieee.org/about/corporate/governance/p9-26.html.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

The Institute of Electrical and Electronics Engineers, Inc. 3 Park Avenue, New York, NY 10016-5997, USA

# Important Notices and Disclaimers Concerning IEEE Standards Documents

IEEE documents are made available for use subject to important notices and legal disclaimers. These notices and disclaimers, or a reference to this page, appear in all standards and may be found under the heading "Important Notices and Disclaimers Concerning IEEE Standards Documents." They can also be obtained on request from IEEE or viewed at <a href="http://standards.ieee.org/ipr/disclaimers.html">http://standards.ieee.org/ipr/disclaimers.html</a>.

# Notice and Disclaimer of Liability Concerning the Use of IEEE Standards Documents

IEEE Standards documents (standards, recommended practices, and guides), both full-use and trial-use, are developed within IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association ("IEEE SA") Standards Board. IEEE ("the Institute") develops its standards through a consensus development process, approved by the American National Standards Institute ("ANSI"), which brings together volunteers representing varied viewpoints and interests to achieve the final product. IEEE Standards are documents developed through scientific, academic, and industry-based technical working groups. Volunteers in IEEE working groups are not necessarily members of the Institute and participate without compensation from IEEE. While IEEE administers the process and establishes rules to promote fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the accuracy of any of the information or the soundness of any judgments contained in its standards.

IEEE Standards do not guarantee or ensure safety, security, health, or environmental protection, or ensure against interference with or from other devices or networks. Implementers and users of IEEE Standards documents are responsible for determining and complying with all appropriate safety, security, environmental, health, and interference protection practices and all applicable laws and regulations.

IEEE does not warrant or represent the accuracy or content of the material contained in its standards, and expressly disclaims all warranties (express, implied and statutory) not included in this or any other document relating to the standard, including, but not limited to, the warranties of: merchantability; fitness for a particular purpose; non-infringement; and quality, accuracy, effectiveness, currency, or completeness of material. In addition, IEEE disclaims any and all conditions relating to: results; and workmanlike effort. IEEE standards documents are supplied "AS IS" and "WITH ALL FAULTS."

Use of an IEEE standard is wholly voluntary. The existence of an IEEE standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard.

In publishing and making its standards available, IEEE is not suggesting or rendering professional or other services for, or on behalf of, any person or entity nor is IEEE undertaking to perform any duty owed by any other person or entity to another. Any person utilizing any IEEE Standards document, should rely upon his or her own independent judgment in the exercise of reasonable care in any given circumstances or, as appropriate, seek the advice of a competent professional in determining the appropriateness of a given IEEE standard.

IN NO EVENT SHALL IEEE BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO: PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE PUBLICATION, USE OF, OR RELIANCE UPON ANY STANDARD, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE AND REGARDLESS OF WHETHER SUCH DAMAGE WAS FORESEEABLE.

#### **Translations**

The IEEE consensus development process involves the review of documents in English only. In the event that an IEEE standard is translated, only the English version published by IEEE should be considered the approved IEEE standard.

#### Official statements

A statement, written or oral, that is not processed in accordance with the IEEE SA Standards Board Operations Manual shall not be considered or inferred to be the official position of IEEE or any of its committees and shall not be considered to be, or be relied upon as, a formal position of IEEE. At lectures, symposia, seminars, or educational courses, an individual presenting information on IEEE standards shall make it clear that his or her views should be considered the personal views of that individual rather than the formal position of IEEE.

#### Comments on standards

Comments for revision of IEEE Standards documents are welcome from any interested party, regardless of membership affiliation with IEEE. However, IEEE does not provide consulting information or advice pertaining to IEEE Standards documents. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Since IEEE standards represent a consensus of concerned interests, it is important that any responses to comments and questions also receive the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to comments or questions except in those cases where the matter has previously been addressed. For the same reason, IEEE does not respond to interpretation requests. Any person who would like to participate in revisions to an IEEE standard is welcome to join the relevant IEEE working group.

Comments on standards should be submitted to the following address:

Secretary, IEEE SA Standards Board 445 Hoes Lane Piscataway, NJ 08854 USA

# Laws and regulations

Users of IEEE Standards documents should consult all applicable laws and regulations. Compliance with the provisions of any IEEE Standards document does not imply compliance to any applicable regulatory requirements. Implementers of the standard are responsible for observing or referring to the applicable regulatory requirements. IEEE does not, by the publication of its standards, intend to urge action that is not in compliance with applicable laws, and these documents may not be construed as doing so.

# Copyrights

IEEE draft and approved standards are copyrighted by IEEE under US and international copyright laws. They are made available by IEEE and are adopted for a wide variety of both public and private uses. These include both use, by reference, in laws and regulations, and use in private self-regulation, standardization, and the promotion of engineering practices and methods. By making these documents available for use and adoption by public authorities and private users, IEEE does not waive any rights in copyright to the documents.

# **Photocopies**

Subject to payment of the appropriate fee, IEEE will grant users a limited, non-exclusive license to photocopy portions of any individual standard for company or organizational internal use or individual, non-commercial use only. To arrange for payment of licensing fees, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

# **Updating of IEEE Standards documents**

Users of IEEE Standards documents should be aware that these documents may be superseded at any time by the issuance of new editions or may be amended from time to time through the issuance of amendments, corrigenda, or errata. An official IEEE document at any point in time consists of the current edition of the document together with any amendments, corrigenda, or errata then in effect.

Every IEEE standard is subjected to review at least every 10 years. When a document is more than 10 years old and has not undergone a revision process, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE standard.

In order to determine whether a given document is the current edition and whether it has been amended through the issuance of amendments, corrigenda, or errata, visit IEEE Xplore at <a href="http://ieeexplore.ieee.org/">http://ieeexplore.ieee.org/</a> or contact IEEE at the address listed previously. For more information about the IEEE SA or IEEE's standards development process, visit the IEEE SA Website at <a href="http://standards.ieee.org">http://standards.ieee.org</a>.

#### **Errata**

Errata, if any, for IEEE standards can be accessed via <a href="https://standards.ieee.org/standard/index.html">https://standards.ieee.org/standard/index.html</a>. Search for standard number and year of approval to access the web page of the published standard. Errata links are located under the Additional Resources Details section. Errata are also available in IEEE Xplore: <a href="https://ieeexplore.ieee.org/browse/standards/collection/ieee/">https://ieeexplore.ieee.org/browse/standards/collection/ieee/</a>. Users are encouraged to periodically check for errata.

#### **Patents**

Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken by the IEEE with respect to the existence or validity of any patent rights in connection therewith. If a patent holder or patent applicant has filed a statement of assurance via an Accepted Letter of Assurance, then the statement is listed on the IEEE SA Website at <a href="https://standards.ieee.org/about/sasb/patcom/patents.html">https://standards.ieee.org/about/sasb/patcom/patents.html</a>. Letters of Assurance may indicate whether the Submitter is willing or unwilling to grant licenses under patent rights without compensation or under reasonable rates, with reasonable terms and conditions that are demonstrably free of any unfair discrimination to applicants desiring to obtain such licenses.

Essential Patent Claims may exist for which a Letter of Assurance has not been received. The IEEE is not responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patents Claims, or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility. Further information may be obtained from the IEEE Standards Association.

# **Participants**

At the time this IEEE standard was completed, the 3D Test Working Group had the following membership:

Adam Cron, Chair Erik Jan Marinissen, Vice Chair Michael G. Wahl, Editor Eric Cormack, Secretary

Saman Adham Saurabh Gupta Gunasekaran Sandeep Bhatia Jon Haldorson Ramasamy Tapan Chakraborty Gurgen Harutyunyan Mike Ricchetti Jonathon E. Colburn Shuichi Kameyama A.T. Sivaram Harry Linzer Naveen Kumar Jean-Francois Cote Teresa McLaurin Alfred Crouch Srivastava Heiko Ehrenberg Sophocles Metsis Craig Stephan Sandeep Goel Seetal Potluri Min-Jer Wang

Etienne Racine

Previous members of the 3D Test Technology working group are:

Vincent Chalendard Michael Higgins Benoit Nadeau-Dostie Chun-Lung Hsu Chen-An Chen Christos Papameletis Marc Hutner Vivek Chickermane Ben Rogel Hongshin Jun Francisco Russi C. J. Clark Zoe Conroy Shuichi Kameyama Iftikhar Soomro Damon Domke Rakesh Kinger Brian Turmelle Bill Tuthill Ted Eaton Amit Majumdar T.M. Mak Lee Whetsel William Eklow Tom Heilmann Arie Margulis Jae Wu

The following members of the individual Standards Association balloting group voted on this standard. Balloters may have voted for approval, disapproval, or abstention.

Erik Jan Marinissen Saman Adham Heiko Ehrenberg Peter van den Eijnden Benoit Nadeau-Dostie Ken-Ichi Anzou Randall Groves Mike Ricchetti Sandeep Bhatia Anthony Sparks Bill Brown Jon Haldorson Demetrio Bucaneg Jr Peter Harrod Naveen Srivastava Tapan Chakraborty Gurgen Harutyunyan Jon Charles Stewart Werner Hoelzl Jonathon E. Colburn Walter Struppler Michael Laisne Srinivasa Vemuru Eric Cormack Michael G. Wahl Jean-Francois Cote Philippe Lebourg Adam Ley Adam Cron Lisa Ward Alfred Crouch Karl Weber

When the IEEE SA Standards Board approved this standard on 7 November 2019, it had the following membership:

### Gary Hoffman, Chair Ted Burse, Vice Chair Jean-Philippe Faure, Past Chair Konstantinos Karachalios, Secretary

Masayuki Ariyoshi David J. Law Annette D. Reilly Dorothy Stanley Stephen D. Dukes Joseph Levy J. Travis Griffith Howard Li Sha Wei Guido Hiertz Xiaohui Liu Phil Wennblom Christel Hunter Kevin Lu Philip Winston Joseph L. Koepfinger\* Daleep Mohla Howard Wolfman Thomas Koshy Andrew Myles Feng Wu John D. Kulick Jingyi Zhou

<sup>\*</sup>Member Emeritus

#### Introduction

This introduction is not part of IEEE Std 1838-2019, IEEE Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits.

Advancements in interconnect, assembly, and packaging technology have lead to a wide range of multi-die stack architectures. These die stacks need to be tested before they can be shipped with acceptable quality levels to customers. Consequently, three-dimensional design-for test (3D-DfT) structures that provide test access between the external stack I/Os and the various dies and inter-die interconnect are needed. Test access is needed for manufacturing phases that include both partially assembled and complete stacks. This standard addresses these issues.

# **Contents**

| 1. | Overview                                                                       |    |

|----|--------------------------------------------------------------------------------|----|

|    | 1.1 Scope                                                                      |    |

|    | 1.2 Three-dimensional integrated circuits (ICs) stacking technology            |    |

|    | 1.3 Motivation for a 3D-DfT standard                                           |    |

|    | 1.4 Context                                                                    |    |

|    | 1.5 Organization of the standard                                               | 15 |

|    | 1.6 Word usage                                                                 | 16 |

| 2. | Normative references                                                           | 16 |

| 2  | Definitions, acronyms, and abbreviations                                       | 16 |

| ٥. | 3.1 Definitions                                                                |    |

|    | 3.2 Acronyms and abbreviations                                                 |    |

|    | 5.2 Actonyms and addreviations                                                 |    |

| 4. | Technology                                                                     |    |

|    | 4.1 Stack model                                                                |    |

|    | 4.2 Wafer-level die access                                                     |    |

|    | 4.3 Physical attributes                                                        | 25 |

| 5. | Serial test access ports                                                       | 26 |

|    | 5.1 Primary test access port                                                   |    |

|    | 5.2 Primary test access port controller                                        |    |

|    | 5.3 Secondary test access port (STAP)                                          |    |

|    | 5.4 Secondary test access port control logic                                   |    |

|    | 5.5 Registers                                                                  |    |

|    | 5.6 Configuration elements.                                                    |    |

| 6. | Die wrapper register                                                           | 42 |

|    | 6.1 Register design                                                            |    |

|    | 6.2 DWR cell structure and operation                                           |    |

|    | 6.3 DWR operation events                                                       |    |

|    | 6.4 DWR operation modes                                                        |    |

|    | 6.5 Parallel access to the DWR                                                 |    |

|    | 6.6 DWR cell naming                                                            |    |

|    | 6.7 DWR cell examples                                                          |    |

|    | 6.8 Wrapper states                                                             |    |

| 7  | Flexible parallel port                                                         | 57 |

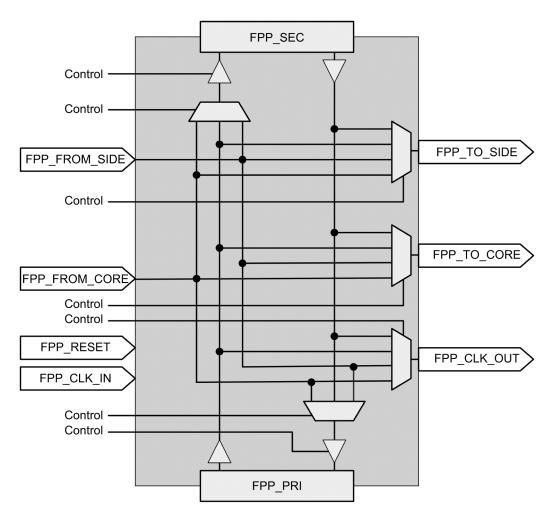

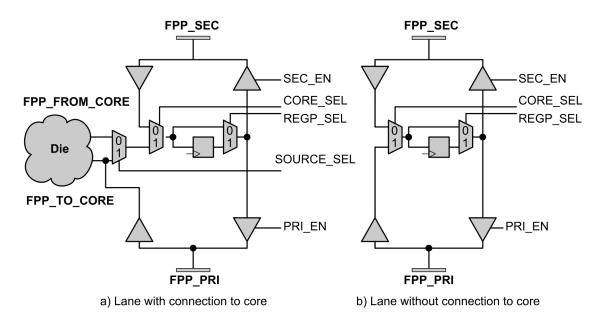

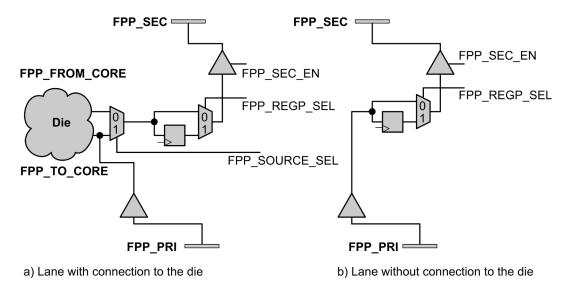

| 1. | 7.1 General introduction                                                       |    |

|    | 7.2 FPP lane examples                                                          |    |

|    | 7.3 Structure of the FPP                                                       |    |

|    | 7.4 Allocation of FPP configuration elements to the FPP lane control terminals |    |

|    | ·                                                                              |    |

|    | IEEE Std 1838 DWR relationship with other standards                            |    |

| Aı | nnex A (informative) Bubble diagrams                                           | 68 |

| Aı | nnex B (informative) Bibliography                                              | 70 |

# **List of Figures**

| Figure 1—2.5-SIC (a), 3D-SIC (b), and 5.5D-SIC (c)                                                                                                                                                            | 14 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2—Three physically different implementations of a logically equivalent stack                                                                                                                           | 23 |

| Figure 3—Die detectors switching mechanism proposal                                                                                                                                                           | 25 |

| Figure 4—Power-rail-based path selection                                                                                                                                                                      | 25 |

| Figure 5—Example of a stack comprised of two semiconductor dies                                                                                                                                               | 26 |

| Figure 6—PTAP controller state machine diagram and state definitions                                                                                                                                          | 29 |

| Figure 7—PTAP controller waveforms                                                                                                                                                                            | 29 |

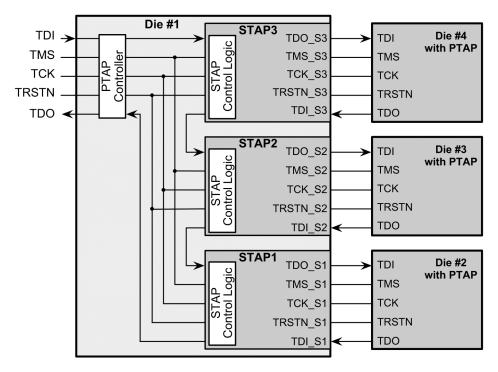

| Figure 8—Multiple numbered STAPs connected to a stacked next die                                                                                                                                              | 30 |

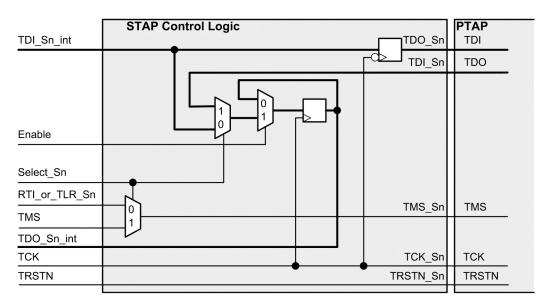

| Figure 9—STAP Control Logic                                                                                                                                                                                   | 33 |

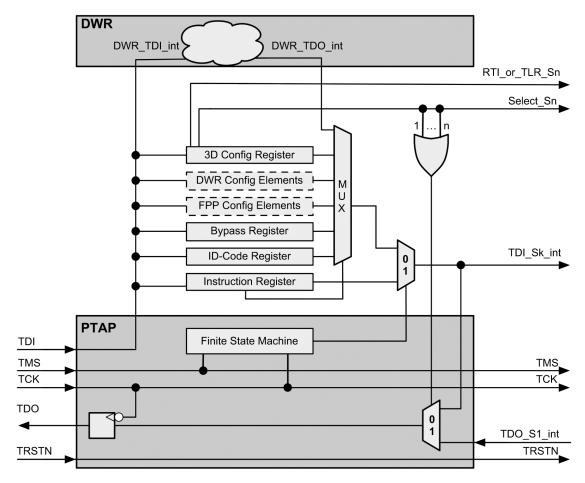

| Figure 10—Per-die PTAP and register with signal connections for 3D extensions units and feature Config-Registers                                                                                              | 34 |

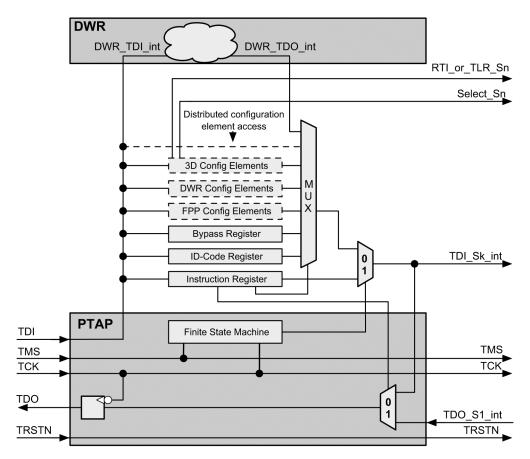

| Figure 11—Alternative implementation of the per-die PTAP and register architecture with signal connections for 3D extensions units, feature Config Registers and the distributed configuration element access | 35 |

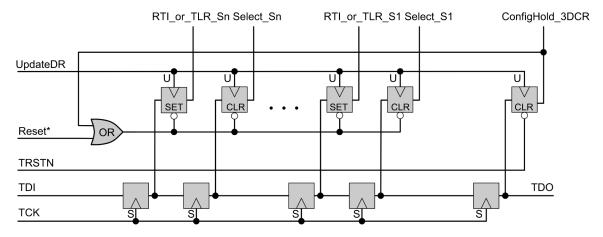

| Figure 12—Example STAP configuration register (3DCR)                                                                                                                                                          | 37 |

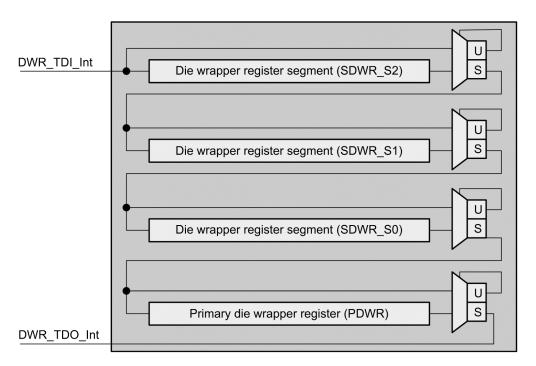

| Figure 13—Primary and secondary DWR segment concatenation                                                                                                                                                     | 40 |

| Figure 14—Example of DWR in serial test interface configuration to be accessed from IEEE 1149.1 Test Access Port                                                                                              | 43 |

| Figure 15—Example of DWR in parallel test interface configuration to be accessed from the IEEE 1838 flexible parallel port DWR structure and operation                                                        | 44 |

| Figure 16—DC_SF1_CI1 DWR cell                                                                                                                                                                                 | 54 |

| Figure 17—DC_SF1_CI1_G1 DWR cell                                                                                                                                                                              | 54 |

| Figure 18—DC_SD1_CO1 DWR cell                                                                                                                                                                                 | 55 |

| Figure 19—DC_SD2_CI2 DWR cell                                                                                                                                                                                 | 55 |

| Figure 20—DC_SD1_CI1_U DWR cell                                                                                                                                                                               | 55 |

| Figure 21—DC_SD1_CI1_U_G0 DWR cell                                                                                                                                                                            | 56 |

| Figure 22—DC_SD1_CI1_O DWR cell                                                                                                                                                                               | 56 |

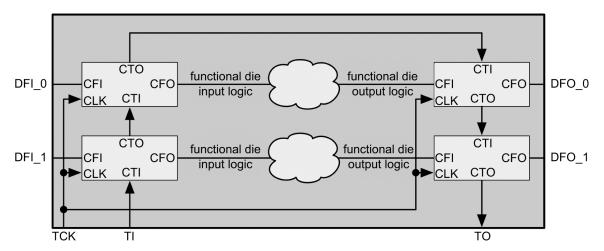

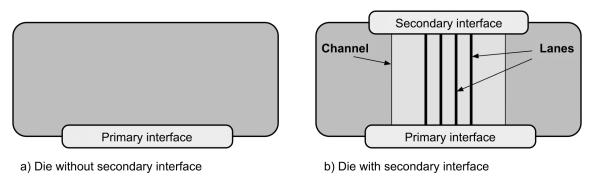

| Figure 23—Die with primary and optionally secondary interface                                                                                                                                                 | 58 |

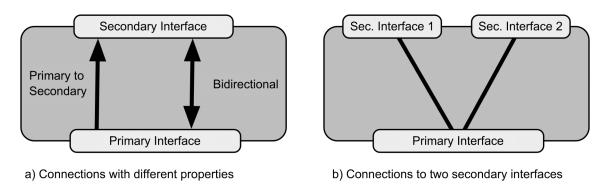

| Figure 24—Different connection types                                                                                                                                                                          | 58 |

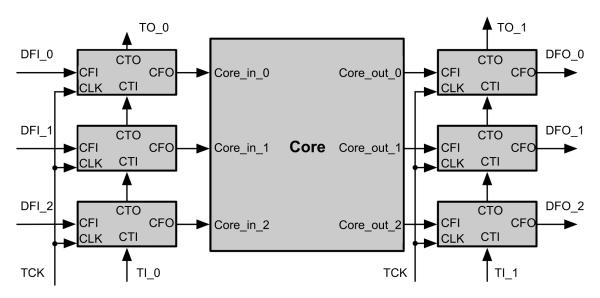

| Figure 25—Template of lane connectivity architecture                                                                                                                                                          | 59 |

| Figure 26—Bidirectional lane examples                                                                                                                                                                         | 60 |

| Figure 27—Unidirectional lane examples from primary to secondary port (up)                                                                                                                                    | 61 |

| Figure 28—Unidirectional lane examples from secondary to primary port (down)  | 61 |

|-------------------------------------------------------------------------------|----|

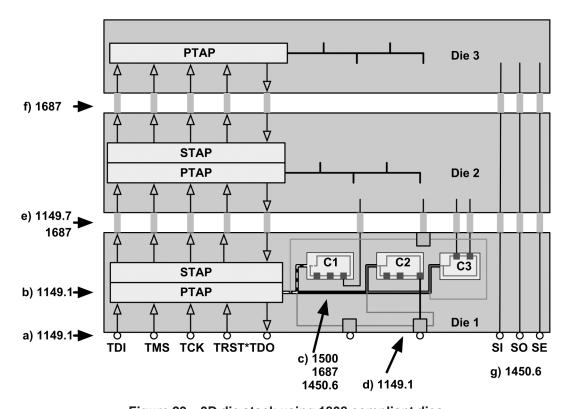

| Figure 29—3D die stack using 1838 compliant dies                              | 67 |

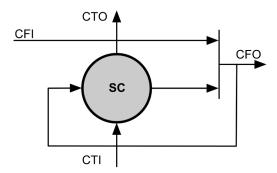

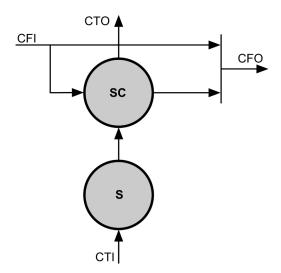

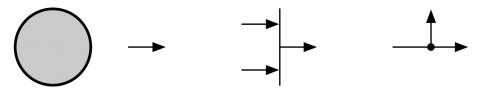

| Figure A.1—The four symbols used in bubble diagrams                           | 68 |

| Figure A.2—Various storage elements                                           | 68 |

| Figure A.3—Example of IEEE Std 1149.1 BC 1 or IEEE STD 1838 DC SD1 CI1 U cell | 69 |

# **List of Tables**

| Table 1—DWR cell example list            | 54 |

|------------------------------------------|----|

| Table 2—FPP terminal definitions.        | 59 |

| Table 3—Undirectional lane connectivity  | 60 |

| Table 4—Registered lane connectivity     | 65 |

| Table 5—Non-registered lane connectivity | 66 |

# IEEE Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits

#### 1. Overview

#### 1.1 Scope

IEEE Std 1838<sup>TM</sup>-2019 standardizes mandatory and optional on-chip hardware components for 3D test access. It is intended that in the future a standard is developed for a formal, computer-readable language in which implementation choices for the three-dimensional design-for-test (3D-DfT) hardware can be specified and described. An idea of a language/data structure has been described in [B5].<sup>1</sup>

The aim of IEEE Std 1838 is to define at die-level standardized and scalable 3D-DfT features based on and working with digital scan-based test access, such that when compliant dies are stacked, a stack-level 3D-DfT test access architecture emerges with a minimum functionality and many optional extensions. IEEE Std 1838 provides a modular test access architecture, in which dies and interconnect layers between adjacent stacked dies can be tested individually. The focus of the standard is testing the intra-die circuitry as well as the interdie interconnects in pre-bond, mid-bond, and post-bond cases in pre-packaging, post-packaging, and board-level situations. The standard provides test access via a mandatory one-bit ('serial') input/output test port and optional multi-bit ('parallel') test ports.

The standard is die-centric, i.e., compliance to the standard pertains to a die (and not to a stack of dies). Standardized die-level design-for-test (DfT) features comprise a stack-level test access architecture. In this way, the standard enables interoperability between die makers and stack maker.

The standard does not address stack-level challenges and solutions. The most prominent example of this is that the standard does not address compliance of the stack to IEEE Std 1149.1<sup>TM</sup> boundary scan for board-level interconnect testing (although the standard certainly does not prohibit application thereof).<sup>2</sup>

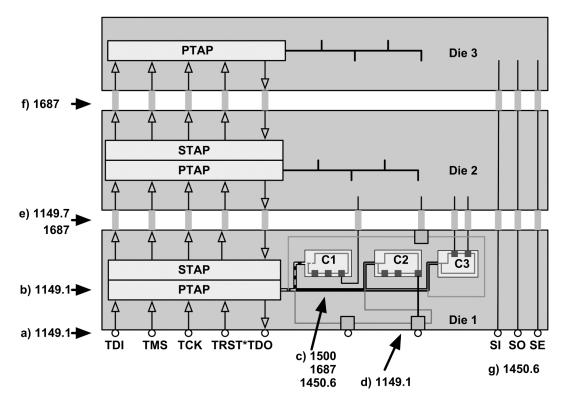

IEEE Std 1838 does not mandate specific defect or fault models, specific test generation methods, nor specific die-internal 2D-DfT features. However, the standard leverages existing 2D-DfT wherever applicable and appropriate, including test access ports (such as specified in IEEE Std 1149.1), on-chip DfT such as internal scan chains and wrappers of embedded cores (such as specified in IEEE Std 1500<sup>TM</sup>), and on-chip design-for-debug and embedded instruments (such described in IEEE Std 1687<sup>TM</sup>).

Stacking of dies requires that the vertical interconnects [e.g., micro-bumps and through-silicon vias (TSVs)] are aligned with respect to footprint (i.e., matching x,y layout locations), mechanical properties (i.e.,

<sup>&</sup>lt;sup>1</sup>The numbers in brackets correspond to those of the bibliography in Annex B.

<sup>&</sup>lt;sup>2</sup>Information on references can be found in Clause 2.

matching materials, diameter, height, etc.), and electrical properties (i.e., matching driver/receiver pairs). As a generic DfT-only standard, IEEE Std 1838 does not govern these items. Similar to IEEE Std 1149.1 and IEEE Std 1500, it only defines a DfT architecture:

- Number, name, type, and function of test I/Os

- On-chip DfT hardware and corresponding description

- Clock-cycle accurate test operation protocol

Consequently, off-the-shelf IEEE Std 1838-compliant dies are not guaranteed to 'plug-n-play' with each other without further physical alignment. The additional test I/Os as defined by IEEE Std 1838 require more parameters: footprint, mechanical, and electrical properties (but the same is true for the functional interfaces).

#### 1.2 Three-dimensional integrated circuits (ICs) stacking technology

The market continues to pull for integrated circuits (ICs) with higher performance, better energy-efficiency, and lower cost. While conventional transistor scaling runs into increasing technical and financial hurdles, the baton in the race to create attractive new IC products that meet market expectations is gradually being taken over by innovations in multi-die stack-assembly and packaging techniques. Large-array fine-pitch micro-bumps implement dense high-performance low-power inter-die interconnects. Through-silicon vias in combination with wafer thinning provide electrical connections via the back-side of a die's substrate, enabling stacks of more than two dies. Interposer dies, possibly implemented in a passive technology, offer low-cost high-performance ways to interconnect multiple dies. Packaging costs can be drastically reduced by using cheaper materials and processes and by turning packaging into a wafer-level operation. The I/O-to-pin fan-out functionality of package substrates can be replaced by redistribution metal layers, cost-effectively manufactured at wafer level. And the cost of plastic or ceramic packages can be circumvented by applying epoxy mold compounds at wafer level.

These and other interconnect, assembly, and packaging technology innovations have led to a wide range of multi-die stack architectures, including so-called "2.5D"-stacked ICs (SICs) consisting of multiple active dies stacked side-by-side on a passive silicon interposer base, "3D"-SICs comprising a tower of stacked active dies, and multi-tower-SICs that consist of multiple towers of stacked active dies side-by-side on a passive silicon interposer.

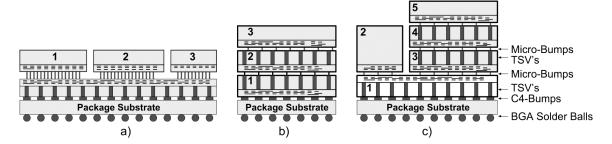

Figure 1—2.5-SIC (a), 3D-SIC (b), and 5.5D-SIC (c)

These new SIC product compositions offer various compelling benefits: (1) heterogeneous integration, i.e., the ability to use the most effective technology node for each die in the stack, for example optimized for digital logic, memory, or analog circuitry; (2) inter-die communication with high bandwidth, low latency, and low power consumption; and (3) higher component yields (and hence: lower costs per component) in case an originally large die is partitioned into multiple smaller dies that are stacked on top of each other—provided faulty dies can be adequately removed from the manufacturing process by means of testing before stacking.

Like all micro-electronic products, these die stacks need to be tested before they can be shipped with acceptable quality levels to their customers. We distinguish the following tests: (1) *pre-bond tests* prior to stacking, (2) *mid-bond tests* on incomplete, partial stacks, (3) *post-bond tests* on complete yet not packaged stacks, and (4) *final tests* on the final packaged product. The number of possible test flows grows quickly with the number of dies in the stack and hence is subject of automated trade-off evaluation and optimization (see, [B1], [B4], and [B8]).

#### 1.3 Motivation for a 3D-DfT standard

A well-architected DfT access infrastructure is indispensable for achieving a high-quality test. Not only do we need conventional 2D-DfT structures (such as internal scan chains, test data compression circuitry, IEEE Std 1500 wrappers around embedded cores, and/or built-in self-test (BIST) engines) that provide test access within a single die, we also need new approaches for testing stacked systems. Especially once a (partial or complete) vertical stack has been formed (i.e., in mid-bond, post-bond, or final testing phases), we also need novel 3D-DfT structures that provide test access from (and to) the external stack I/Os to (and from) the various dies and inter-die interconnects. For example: if a stack consists of three dies and test access from external test equipment is exclusively possible via the stack I/Os that are concentrated in, say, Die 1, then Die 1 and Die 2 need to cooperate in transporting test stimuli and responses up and down the stack in order to be able to test Die 3.

To enable separation of the test development as well as test execution for the various dies in the stack, the 3D-DfT architecture should enable modular testing, i.e., tests for dies and interconnect layers between adjacent stacked dies can be developed and executed individually. Several ad-hoc 3D-DfT architectures have been proposed, among others based on IEEE Std 1149.1, IEEE Std 1500, and IEEE Std 1687. These architectures all have their specific strong and weak points. However, these ad-hoc 3D-DfT architectures do not inter-operate together. Hence, there is a need for a per-die 3D-DfT standard, such that if compliant dies (even if designed and developed by different teams or different companies) are brought together in a die stack, a basic minimum of test features should work across the stack. This is exactly the aim of IEEE Std 1838.

#### 1.4 Context

The Standard for Test Access Architecture for Three-Dimensional Stacked ICs is conceptually related to previously developed design-for-test (DfT) standards, in particular IEEE Std 1149.1, IEEE Std 1500, and IEEE Std 1687. The first two standards specify test access architectures for ICs on boards (IEEE Std 1149.1) and IP cores embedded within an IC (IEEE Std 1500). IEEE Std 1687 describes an access architecture to embedded instruments. These three previously developed standards have influenced and are referred to in this standard, so a solid understanding of these standards is strongly recommended.

#### 1.5 Organization of the standard

- Clause 1 provides an overview and context for this standard.

- Clause 2 provides references necessary to understand this standard.

- Clause 3 defines terminology and acronyms used in this standard.

- Clause 4 is a tutorial that outlines the technologies addressed and utilized by this standard.

- Clause 5 defines the serial access bus and structure which forms the mandatory basis of the standard.

- Clause 6 specifies the construction of the mandatory die wrapper register.

Clause 7 defines the optional flexible parallel port: a mechanism to add a higher bandwidth channel to the die stack.

#### 1.6 Word usage

The word *shall* indicates mandatory requirements strictly to be followed in order to conform to the standard and from which no deviation is permitted (shall equals is required to).<sup>3,4</sup>

The word should indicates that among several possibilities one is recommended as particularly suitable, without mentioning or excluding others; or that a certain course of action is preferred but not necessarily required (should equals is recommended that).

The word may is used to indicate a course of action permissible within the limits of the standard (may equals is permitted to).

The word can is used for statements of possibility and capability, whether material, physical, or causal (can equals is able to).

#### 2. Normative references

The following referenced documents are indispensable for the application of this document (i.e., they must be understood and used, so each referenced document is cited in text and its relationship to this document is explained). For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments or corrigenda) applies.

IEEE Std 1149.1TM-2013, IEEE Standard for Test Access Port and Boundary-Scan Architecture. 5,6

IEEE Std 1500<sup>TM</sup>-2005, IEEE Standard Testability Method for Embedded Core-based Integrated Circuits.

IEEE Std 1687TM-2014, IEEE Standard for Access and Control of Instrumentation Embedded within a Semiconductor Device.

# 3. Definitions, acronyms, and abbreviations

#### 3.1 Definitions

For the purposes of this document, the following terms and definitions apply. The *IEEE Standards Dictionary* Online should be consulted for terms not defined in this clause. 7

active functional interface: An active functional interface includes all of the terminals under test while using the die-wrapper register (DWR).

apply event: A derivative event that coincides with the Shift, Capture, or Update event, whereby test data become active and effective as test stimuli. For example, while the wrapper is in IF mode, the apply event is when test data is applied from input cells onto the internal die functional logic.

<sup>&</sup>lt;sup>3</sup>The use of the word must is deprecated and cannot be used when stating mandatory requirements, must is used only to describe unavoidable situations.

<sup>&</sup>lt;sup>4</sup>The use of will is deprecated and cannot be used when stating mandatory requirements, will is only used in statements of fact.

The IEEE standards or products referred to in Clause 2 are trademarks owned by the Institute of Electrical and Electronics Engineers,

<sup>&</sup>lt;sup>6</sup>IEEE publications are available from the Institute of Electrical and Electronics Engineers (http://standards.ieee.org/).

<sup>7</sup>IEEE Standards Dictionary Online is available at: http://dictionary.ieee.org. An IEEE Account is required for access to the dictionary, and one can be created at no charge on the dictionary sign-in page.

# IEEE Std 1838-2019 IEEE Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits

bidirectional terminal: A terminal that can be controlled to switch between driving or receiving signals.

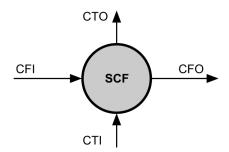

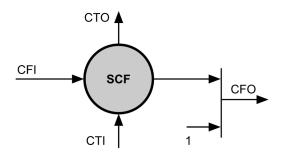

**capture event**: An event whereby the value present on the cell function input (CFI) or cell functional output (CFO) is stored in a storage element in the shift path.

**capture mode**: The mode in which all required die-wrapper register (DWR) cells apply the capture event. For instance, during an external test mode, only the DWR cells attached to die terminal inputs are required to capture, all other die-wrapper register (DWR) cells can apply any event.

cell test input (CTI): A die-wrapper register (DWR) cell's test data input.

**cell test output (CTO)**: A die-wrapper register (DWR) cell's test data output.

**chip**: Active component typically mounted on a board or some other package with other components. It can be a packaged die or die stack (often a user does not need to know whether his/her chip contains one die or multiple dies stacked together). The more general term "component" is normally used in this standard for a compliant object as there may be multiple integrated circuits in a package, even when they behave as a single object. *Syn:* **integrated circuit (IC)**.

**component**: An active or passive electronic part. For the sake of this standard, this usually refers to an integrated circuit, although it could include non-integrated-circuit devices mounted on a board. See also: chip.

**core**: A functional circuit design that is part of a single die. In case of non-hierarchical design of the die's circuitry, all functional circuitry on that die is part of the core. In case of hierarchical design and test architecture of the die's circuitry, there are multiple embedded cores on a single die, which are assumed to be equipped with an IEEE Std 1500<sup>TM</sup> core-test wrapper.

**core test**: A test methodology that is applied to an embedded core.

dedicated shift path: A shift path comprising storage elements that do not participate in functional operation.

**dedicated wrapper (cell)**: A wrapper style that does not share hardware with core functionality. This style allows certain test operations to occur concurrently and transparently during functional operation. This definition could apply to individual cells.

**die**: A (typically rectangular) piece of processed semiconductor substrate, containing circuitry. A die is the result of dicing a semiconductor wafer after processing.

die sequence: The first die in the stack is accessible to the outside world. The following dies are referred to as the second, third, etc. The sequence of the dies does not imply any orientation of the dies. A stack can have multiple dies that are last dies; this is called a multi-tower stack.

**die stack**: A construction in which multiple individual dies are stacked and electrically interconnected, such that together they form a bigger circuit.

die terminal: The physical connection point between dies or between the first die and the interposer or PCB.

die-wrapper register (DWR): The register surrounding the die for facilitating die test or die-to-die tests.

**external safe state**: A configuration of safe register values in which the outputs of a die are in a state that prevents them from interfering with a block of logic outside the die. See also internal safe state; safe state.

**EXTEST**: This is a shortening of the two words external test.

#### IEEE Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits

**external test**: Occurs when the die-wrapper register (DWR) is used to test logic or interconnect external to the die while the DWR is in outward-facing mode. This may include logic on the die if the DWR cell is not at the die boundary.

**falling-edge**: A transition from a high to a low logic level. In positive logic, a change from logic 1 to logic 0. Events that are specified to occur on the falling edge of a signal should be completed within a fixed (frequency independent) delay specified by the component supplier.

**first die**: The first die is the die which is connected to the printed circuit board (PCB) or an equivalent carrier or interposer. It is typically the bottom die of the stack.

**first die external-I/O**: Package-level connection to the board or system level.

**flexible parallel port (FPP)**: Optional multi-bit test access mechanism allowing test data and protocols to be transferred over a set of FPP lanes.

**flexible parallel port (FPP) channel**: A set of identical FPP lanes controlled by common signals.

**flexible parallel port (FPP) clock lane**: An FPP lane used to provide an FPP lane clock to registered FPP lanes.

**flexible parallel port (FPP) configuration element**: A test access port (TAP)-accessible test data register (TDR) bit which controls the functionality and configuration of the FPP channels.

**flexible parallel port (FPP) lane**: A collection of lane paths connecting: a primary interface terminal, a secondary interface terminal, die-level DfT, and/or other lanes.

**flexible parallel port (FPP) lane clock (signal)**: Clock signal used to drive registration within registered FPP lanes.

**flexible parallel port (FPP) lane path**: A single-bit logical connection between a lane input terminal (source) and a lane output terminal (sink). This connection may contain sequential elements.

**fully-provisioned (cell)**: A die-wrapper register (DWR) cell with full functionality, including capture, shift, and control features. In addition, it may have safe or update features.

**input cell**: A die-wrapper register (DWR) cell that is provided on a die input.

**input pin**: A component pin that receives signals from an external connection.

**instruction**: A binary data word shifted serially into the test logic in order to define its subsequent operation.

**integrated circuit (IC)**: A collection of transistors, resistors, and capacitors and their interconnections constructed to perform specific functions on a single thin slice of a semiconductor crystal.

**internal safe state**: A configuration of safe register values whereby a core is protected from the impact of a test outside the core. See also external safe state; safe state.

interface: The collection of terminals connecting to another die or package substrate.

**INTEST**: is a shortening of the two words internal test.

**internal test**: occurs when the die-wrapper register (DWR) is used to test logic on the die while the DWR is in inward-facing mode.

IEEE Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits

**inward-facing (IF) mode**: The test mode where core inputs are controlled by the die-wrapper register (DWR) and core outputs are observed by the DWR.

**last compliant die**: Die number k in a stack with n dies of which the first k dies are compliant with this standard  $(1 \le k \le n)$ .

**last die**: This is the last die in the stack. Last die refers to the logical position in the test hierarchy.

**least significant bit (LSB)**: The digit in a binary number representing the lowest numerical value. For shift registers, the bit located nearest to the serial output, or the first bit to be shifted out. The least significant bit of a binary word or shift-register is numbered 0.

**mission mode**: The mode in which the die-wrapper register (DWR) does not interfere with the functional operation of a wrapped die.

most significant bit (MSB): The digit in a binary number representing the greatest numerical value. For shift registers, the bit farthest from the serial output, or the last bit to be shifted out. Logic values expressed in binary form are shown with the most significant bit on the left.

**multi-tower stack**: A system with a multi-tower design has a structure, where one base die is connected to two or more other dies or die stacks, where these dies or die stacks are not connected to each other.

**no-connect**: A signal of the component, which is brought to an input-output pad of the die but not connected to a package pin due, for instance, to a constrained pin-count for the package.

output cell: A die-wrapper register (DWR) cell that is provided for a die output.

**output pin**: A component pin that drives signals onto external connections.

**outward-facing (OF) mode**: The test mode where wrapper functional outputs are controlled by the diewrapper register (DWR) and wrapper functional inputs are observed by the DWR.

**parallel configuration**: Selected architecture of the die-wrapper register (DWR) test logic wherein more than one serial input and serial output are used to access multiple DWR segments during the test.

**partially-provisioned (cell)**: Die-wrapper register (DWR) cell with less than the maximum functionality. It supports the Shift event and either the Capture event or the Apply event. In addition, it may have safe or update features. *See also*: **fully-provisioned.**

**pin**: The point at which connection is made between the integrated circuit and the substrate on which it and other components are mounted (e.g., the printed circuit board). For packaged components, this would be the package pin; for components mounted directly on the substrate, this would be the bonding pad. The actual form of connection (bonding wire, landing pad, solder ball, or metal pin inserted into a via) is not material to the definition. See also: **terminal.**

**port**: A single signal, terminal, or pin; or collection of signals, terminals, or pins.

**power-up reset**: A reset of test or system logic that occurs when the power supply goes from OFF to ON. This can be achieved by design of latches that causes them to power up in a specific state, or by an ON-component or OFF-component circuit that generates an asynchronous reset signal that stays active for some nontrivial time after the power supply has reached its operating voltage. *Synonym:* **power-on reset (POR)**.

**primary interface**: The interface connecting towards the first die or to the package substrate.

IEEE Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits

register: A set of typically contiguous or related storage elements.

**reset**: The establishment of an initial logic condition that can be either logic 0 or logic 1, as determined by the context.

**rising-edge**: A transition from a low to a high logic level. In positive logic, a change from logic 0 to logic 1. Events that are specified to occur on the rising edge of a signal should be completed within a fixed (frequency independent) delay, specified by the component supplier.

sample: Action to capture the value of a signal at a specific moment in time, such as defined by a clock edge.

safe data: Data that satisfy safe state configuration requirements. These data are user-defined.

**safe state**: A property whereby a test of one block of logic is prevented from interfering with or damaging another block of logic. See also external safe state; internal safe state.

scan path: The shift-register path through a circuit designed using the scan design technique.

secondary interface: An interface connecting away from the first die or package substrate.

**segment**: A set of contiguous (in terms of the scan chain) register bits obeying the rules for test data registers and from which a test data register may be assembled.

**segment insertion bit (SIB)**: A configuration of at least a shift and an update cell and a scan-multiplexor that is used to include or exclude a scan chain segment from the active scan path.

**selected test data register**: A test data register is selected when it is required to operate as instructed by associated test logic.

**shared wrapper (cell)**: The wrapper style that shares logic between the test and mission modes of operation of a system storage element. This style prevents simultaneous functional and test operation uses of the shared storage element.

**shift event**: An event whereby the data stored in the die-wrapper register (DWR) shift path are advanced one storage position closer to the DWR's test output (TO). The data present at the DWR's test input (TI) are loaded into the shift path storage element closest to the DWR's TI. If multiple DWR segments are implemented, this definition applies individually to each DWR segment.

**shift mode**: This mode occurs while the shift event is applied to all die-wrapper register (DWR) cells with the intent of loading/unloading DWR scan chains.

**stackID**: A field in an electronic chip identification (ECID) that describes the position of the die in the stack.

**storage element**: A bi-stable circuit element, such as a latch or a flip-flop, which retains state until certain enabling and/or clocking conditions are met that cause it to take on a new state.

**system logic**: Any circuitry that is dedicated to realizing the non-test function of the component or is at the time of interest configured to achieve some aspect of the non-test function.

**terminal**: A logical endpoint from which connections can be made between dies, hierarchical modules, and leaf cells. A terminal can be unidirectional or bidirectional. *See also*: **pin**.

**test access mechanism (TAM)**: A feature of a system-on-chip (SoC) design that enables the delivery of test data to and from dies, cores, or core wrappers.

**test access mechanism (TAM) harness**: Die wrapper register (DWR) logic that enables the coupling of a TAM to cell test inputs (CTIs) and cell test outputs (CTOs).

test input (TI): The serial test data input of a die-wrapper register (DWR) segment.

**test logic**: Any item of logic that is a dedicated part of the test logic architecture or is at the time of interest configured as part of the test logic architecture.

**test mode**: The state of a component in which the component's test logic interferes with the flow of signals to and from the system logic. In addition, the system logic may be controlled as needed to prevent an undesired response to system inputs, excessive heating, and so on.

test output (TO): The serial test data output of a die-wrapper register (DWR) segment.

**three-state**: An adjective describing the ability of an output pin capable of being in one of 3 states: driving a logic 1 or 0, or not driving and inactive (for example, at high impedance).

through silicon via (TSV): A via that electrically connects the front side to the back-side of a (thinned-down) wafer substrate.

**update**: Transfer a logic value from the shift-register stage of a data register cell or an instruction register cell into the latched parallel output stage of the cell.

**update event**: An optional event whereby data stored in a die-wrapper register (DWR) cell's shift path storage element is loaded into an off-shift-path storage element (e.g., update register).

**update register**: The register used to prevent the outputs of a shift register from propagating to other circuitry during a Shift operation. After shifting is complete, the content of the associated shift register is parallel-loaded (updated) into the update register or otherwise applied.

**wrapper**: A wrapper is a test access and isolation ring at the boundary of a test module, being either an embedded core or a stacked die. A wrapper is typically based on scannable flip-flops.

#### 3.2 Acronyms and abbreviations

ATE automatic test equipment

ATPG automatic test pattern generation

AUXCK auxiliary clock

BiDi short for bidirectional

BGA ball grid array (packaging style)

BIST built-in self-test

BSDL Boundary-Scan Description Language or a file containing BSDL statements

CFI cell functional input

CFO cell functional output

CMOS complementary metal-oxide semiconductor

CTI cell test input

CTO cell test output

# IEEE Std 1838-2019 IEEE Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits

dc direct current

DFI die functional input

DFO die functional output

DfT design-for-test

DWR die wrapper register

ECID electronic chip identification (ID)

FPP flexible parallel port

IC integrated circuit

ICL Instrument Connectivity Language

IF inward facing I/O input/output

IP intellectual property

LSB least significant bit

MSB most significant bit

OF outward facing

PDL Procedural Description Language or a file containing PDL statements

PLL phase-locked loop POR power-on reset

PTAP primary test access port

SIB segment insertion bit

SoC system on chip

STAP secondary test access port

TAM test access mechanism

TAP test access port

TCK test clock

TDI test data input

TDO test data output

TDR test data register

TI test input

TMS test mode select

TO test output

TSV through silicon via

WIR wrapper instruction register

WRCK wrapper clock

# 4. Technology

#### 4.1 Stack model

IEEE Std 1838 is defined at the logical level and abstracts from the physical implementation of the stack. To that end, it avoids terms such as 'top', 'bottom', 'up', and 'down' (which intuitively seem obvious terms to use in the context of vertical die stacking). Instead, IEEE Std 1838 has adopted terminology based on the logical position of the interconnects relative to the external stack I/Os, which the standard assumes are concentrated in a single die, referred to as the *first die*. Relative to a die, the adjacent die connected in the direction of the external I/Os is referred to as the *previous die*; the collection of signals going to the previous die is referred to as the *primary interface* of this die. IEEE Std 1838 assumes that every die has a single primary interface, which connects to its unique previous die; an exception is the first die, for which its primary interface connects to the external system logic. Relative to the external stack I/Os, an adjacent die connected to this die in the opposite direction, (i.e., *away* from the external I/Os), is referred to as a *next die*; the collection of signals going to a next die is referred to as a *secondary interface* of this die. The idea is that pairs of primary and secondary interfaces form the interconnect between two stacked dies; the primary interface of one die plugs into the secondary interfaces of its previous die. A die can have zero or more secondary interfaces that is not a first die is called a *middle die*.

Figure 2—Three physically different implementations of a logically equivalent stack

Figure 2 depicts three different physical implementations of what are for IEEE Std 1838 logically equivalent stacks. The stacks consist of three active dies. Die 1 holds all external I/Os as its primary interface and hence is the first die. The secondary interface of Die 1 connects to the primary interface of Die 2 and the secondary interface of Die 2 connects to the primary interface of Die 3. Hence, Die 2 is a middle die. Die 3 has no secondary interfaces and therefore is the last die in the stack. The stacks in Figure 2 part a) and Figure 2 part b) are both single-tower 3D stacks. In Figure 2 part a), all dies are face-down (i.e., with the processed, active side down) and the external I/Os are implemented as area-array bumps at the bottom-side of the stack. Consequently, the primary interfaces are implemented at the bottom-side of each die and the secondary interfaces are implemented at the top-side of each die. In Figure 2 part b), all dies are face-up and the external

I/Os are implemented as wire-bonded pads at the top-side of the stack. As a result, in Figure 2 part b), 'up' and 'down' are reversed in comparison to Figure 2 part a): the primary interfaces are implemented at the top-side of each die and the secondary interfaces are implemented at the bottom-side of each die. The stack in Figure 2 part c) is a 2.5D-SIC, with the three active dies stacked side-by-side on top of and interconnected by a passive interposer die. In this example, the primary and secondary interfaces of a die are both located on the same bottom-side of that die.

#### 4.2 Wafer-level die access

For components containing multiple stacked dies, we distinguish the following moments during the manufacturing flow (including wafer processing, stack assembly, and packaging) at which tests for manufacturing defects can be performed: (1) pre-bond tests prior to stacking, (2) mid-bond tests on incomplete, partial stacks, (3) post-bond tests on complete, though not yet packaged, stacks, and/or (4) final tests on the final packaged product. At each of these moments, it might be possible (but certainly not mandated by IEEE Std 1838) to test dies and inter-die interconnects for manufacturing defects incurred during wafer processing, stack assembly, and/or packaging. The number of possible test flows grows quickly with the number of dies in the stack and determining a test flow that optimizes test quality and reduces test cost for given quality and cost parameters is therefore a complex task that typically requires automated trade-off evaluation and optimization.

IEEE Std 1838 focuses on standardizing die-level DfT features such that when compliant dies are brought together in a die stack, a minimum of test access is guaranteed. The benefits of the 3D-DfT in compliant dies apply mainly at those test moments after at least one stack-assembly operation has been performed, i.e., from mid-bond testing onwards. Pre-bond testing takes place prior to stacking, and hence does not require cooperative test access via standardized, compatible DfT through other dies. However, to limit the associated silicon area and other implementation costs, it is preferred to reuse the 3D-DfT architecture as provided in the various dies in the stack as much as possible, so also during the pre-bond test of these dies.

Pre-bond test may be distinctly different from the stack test because the semiconductor test equipment accesses the die-under-test via wafer-level probing. For die stacks, probe access is typically via the stack's external I/O interface, which consists of a regularly-sized interface to the package substrate and/or the package pins. The functional I/Os on to-be-stacked dies prior to stacking normally comprise large arrays of fine-pitch microbumps. Typical examples are given by JEDEC standards JESD229 ('Wide I/O Single Data Rate'), JESD229-2 ('Wide I/O 2'), and JESD235B ['High Bandwidth Memory DRAM (HBM1, HBM2)'], which contain microbump arrays of 1200, 1752, and 4955 micro-bumps, respectively, at pitches of 40/50  $\mu$ m, 40/40  $\mu$ m, and 55  $\mu$ m, respectively.

For pre-bond tests of dies accessed via such large fine-pitch micro-bump arrays, there are essentially three options:

- Do not execute pre-bond tests. However, this might imply that compound yields of stacked dies are unacceptably low and hence product costs soar.

- Use advanced MEMS-type probe cards on these large-array fine-pitch micro-bumps.

- Provide dedicated pre-bond probe pads. This requires additional design effort and silicon real estate, but does make pre-bond testing feasible.

The DfT infrastructure in non-first dies is connected via micro-bump connections to the previous die for mid-bond, post-bond, and final testing. In the latter case, the same on-die DfT infrastructure now also needs to be connected to the dedicated pre-bond probe pads. This requires a mechanism to select between (1) pre-bond test access via dedicated pre-bond probe pads and (2) mid-bond and later test access via micro-bump connections coming from the previous die in the stack.

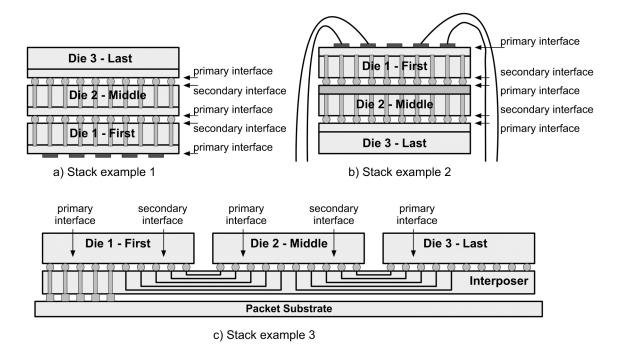

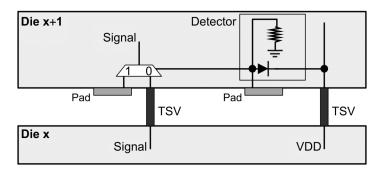

Figure 3 and Figure 4 show two alternative implementations for the above-mentioned selection mechanism. In Figure 3, a die detector switches between dedicated probe pads and micro-bump connections from/to the previous die. The solution in Figure 4 eliminates the need to provide a dedicated "post-bond" control signal from the previous die to this die, as it uses the fact that VDD is connected between the previous die and this die as a detector for the post-bond situation.

Figure 3—Die detectors switching mechanism proposal

Dedicated probe pads (sacrificial pads shown in Figure 4) to support pre-bond testing and a selection mechanism for them are not part of IEEE Std 1838, as it does not affect the interoperability of the test access architecture in die stacks. The decision to provide them (or not), and if so, how exactly to implement them, is a per-die decision, which does not affect the testability of other dies in the stack. It is certainly possible to combine dedicated pre-bond probe pads and compliance to IEEE Std 1838.

Figure 4—Power-rail-based path selection

#### 4.3 Physical attributes

In addition to the exclusions mentioned in the previous subclause, physical aspects of construction are also not addressed by this standard. It is assumed that any die stacked upon another die will have aligned micro-bumps and other physical geometries that allow such a prospect to occur. As such, it is likely that port directionality

and other design attributes will also be shared amongst teams participating in building the stack so that their design goals can be met. But this standard will only focus on the logical design to enable interoperability between die in the stack and tools interfacing to the databases produced by such a flow and methodology.

# 5. Serial test access ports

Each die is a separate logical plug-and-play entity enabling a 3D component to be assembled with test and debug features. Being a per-die standard, terminals and terminal behavior will be defined. The mating of terminals from one die within a 3D stack to the complementary terminals of an abutting die enables a contiguous test and debug access architecture that spans multiple die within the stack.

It should be noted, though, that this standard defines the functional, behavioral, and logical but not physical terminal connections—defining the physical location of terminals, pads or bumps and the sizing and pitch of physical connections is beyond the scope of this standard.

The goal of this clause is to define the signals/terminals, terminal behavior, and associated logic associated with the serial access and control of test and debug features on each die, and how those features are extended by abutting, bonding, or otherwise connecting to other die.

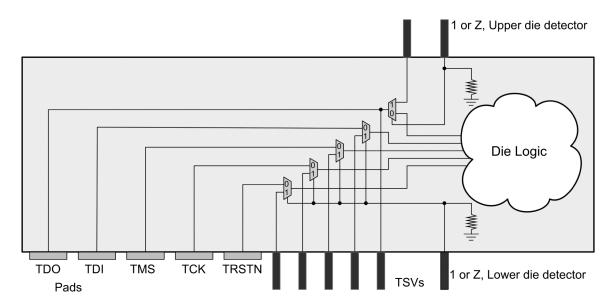

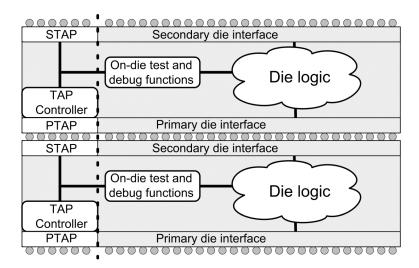

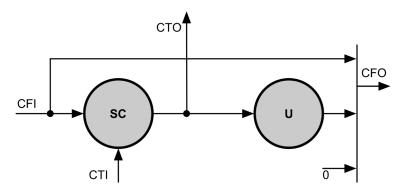

As shown in Figure 5, one subset of the primary interface shall be the primary test access port (PTAP) that will contain the signals and internal die logic connections that are associated with the Primary Interface; and a subset of the secondary interface will be the one or more secondary test access ports (STAPs) that will contain the signals and internal die logic connections that are associated with the secondary interface. Note that the primary and secondary interfaces may also include an optional flexible parallel port (FPP), which will be further discussed in Clause 7.

Figure 5—Example of a stack comprised of two semiconductor dies

#### 5.1 Primary test access port

In support of a per-die standard, the mandatory test interface and access to all on-die test and debug features is the serial PTAP. The PTAP is associated with the surface closest to the board connection or package interface and is represented by five die terminals: TCK, TMS, TDI, TDO, and TRSTN.

#### 5.1.1 Specifications

The rules are as follows:

- Each compliant die shall have a serial test access port as part of its primary interface and it shall be referred to as the PTAP.

- b) The PTAP shall consist of five signals named TCK, TMS, TDI, TDO and TRSTN.

- c) The TCK signal shall be a clock input signal that synchronizes test architecture operations and registers.

- d) The signal presented at TMS (Test Mode Select) shall be sampled into the test logic on the rising edge of TCK.

- The signal presented at TDI (Test Data Input) shall be sampled into the test logic on the rising edge of TCK.

- f) Changes in the state of the signal driven through TDO (Test Data Output) shall occur only on the falling edge of either TCK or upon assertion of Reset\*.

- g) The TRSTN (Test Reset) signal shall be an asynchronous active-low control input signal which provides an asynchronous reset function to test registers defined by this standard.

- h) The TCK, TMS, and TDI signals shall be driven from dedicated terminals.

- i) The TDO signal shall drive a dedicated terminal.

- j) The TRSTN signal for a first die shall be driven from either a dedicated terminal or logic providing a power-on-reset function (POR).

- k) The TRSTN signal for a non-first die shall be driven from a dedicated terminal.

The recommendation is as follows:

1) The TRSTN signal for a first die should be driven from a dedicated terminal.

#### 5.1.2 Description

The five die terminals represent the signals normally associated with a compliant IEEE 1149.1 interface—and in the case of an IEEE 1838 die used as a first die (i.e., a die nearest to the board attachment), the five die terminals may actually represent the IEEE 1149.1 TAP interface to the board connection if an IEEE 1149.1 compliance mandate is required (note that IEEE 1838 compliance does not require IEEE 1149.1 compliance—IEEE 1149.1 compliance is only mandated if there is a separate IEEE 1149.1 compliance imposed on the final component). The five signals are: the input test clock, TCK, that synchronizes all test architecture registers; the test mode select, TMS, that provides the input control signal to the test controller finite-state-machine (FSM) that generates the operation protocol for all test architecture registers; the active-low test reset, TRSTN, that provides the input asynchronous reset signal that can be used to put all test architecture registers into a known default state; the serial test data input, TDI, that allows serial data to be delivered to test architecture data registers on the rising edge of the TCK clock when the test controller FSM is in one of the shift states; and the serial test data output, TDO, that allows serial data from the test architecture data registers to be presented to the die interface on the falling edge of the TCK clock when the test controller FSM is in one of the shift states.

TMS, TCK, TDI and TDO are connected to dedicated test terminals. For a first die, the TRSTN signal should be connected to a dedicated test terminal unless there is POR logic that can drive this signal.

#### 5.2 Primary test access port controller

The PTAP signals drive the PTAP controller, which is an IEEE 1149.1 compatible TAP controller. The register architecture associated with the PTAP controller includes registration to support the 3D features that are required or optional in IEEE Std 1838.

#### 5.2.1 Specifications

The rules are as follows:

- a) The PTAP signals shall be connected to a PTAP controller and associated register architecture.

- b) The PTAP controller shall operate in accordance with the sequence of operations defined by the IEEE 1149.1 TAP controller finite-state-machine based on the TMS input control signal and synchronized by the TCK input clock signal (see 6.1 of IEEE Std 1149.1-2013).

#### 5.2.2 Description

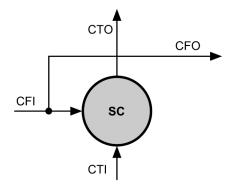

Like the IEEE 1149.1 TAP, the PTAP can access any number of die-internal registers available in the stack. However, the PTAP controller register architecture shall, at a minimum, have the bypass register, one or more die-wrapper register (DWR) segments, the 3D configuration register (3DCR), and all required instructions that support these registers.

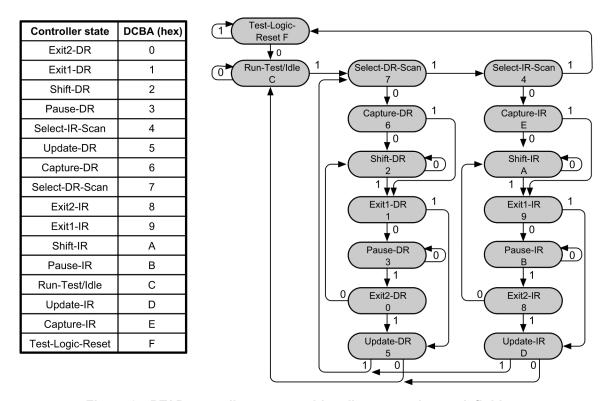

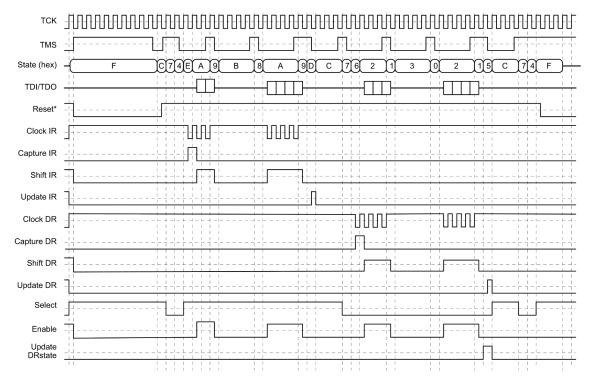

The PTAP Controller operates in the same manner as the IEEE Std 1149.1 TAP controller described in 6.1 of IEEE Std 1149.1-2013. Figure 6 shows the PTAP controller state diagram and names the states with hexadecimal numbering which coincides with the waveforms of the PTAP controller shown in Figure 7.

NOTE—The hexadecimal state numbering of the PTAP Controller shown here is for illustration purposes only. The actual state numbering of the PTAP controller is determined by the designer.<sup>8</sup>

Notes in text, tables, and figures of a standard are given for information only and do not contain requirements needed to implement this standard.

Figure 6—PTAP controller state machine diagram and state definitions

Figure 7—PTAP controller waveforms

#### 5.3 Secondary test access port (STAP)

The baseline IEEE 1149.1 architecture is extended to the secondary interface with the addition of STAPs and their associated selection and configuration control logic. This control logic is composed of the STAP itself, and control from the Primary TAP Controller's three-dimensional configuration register (3DCR, see 5.5.1). The Secondary Interface may support multiple STAPs, each with a mandated five-pin test interface enabling it to plug into a next die's PTAP.

Figure 8—Multiple numbered STAPs connected to a stacked next die

In this standard, an STAP shall be referred to as STAP*n*, with *n* beginning at 1. As shown in Figure 8, the STAPs will be numbered from 1 to *n* starting from the TDO PTAP signal and tracing backwards to the TDI PTAP starting point of the serial scan chain. If more than one STAP exists, then the numbering will increment in scan path order from the PTAP TDO terminal toward the PTAP TDI terminal. Therefore, the STAP named STAP1 will be connected closest in scan path order to the PTAP TDO terminal.

#### 5.3.1 Specifications

The rules are as follows:

- Each die shall have N selectable STAPs, one for each directly connected die.

NOTE—N may be zero if the die does not support any next dies to be stacked.

- b) Each STAP shall comprise the terminals named TDI\_Sn, TDO\_Sn, TMS\_Sn, TCK\_Sn, and TRSTN Sn where n represents the STAP number, where  $0 \le n \le N$ .

- c) The TCK\_Sn output terminal shall be driven from the PTAP TCK terminal with no added in-line registration or combinational gating logic.

- d) The TRSTN\_S*n* output terminal shall be driven from the PTAP TRSTN signal with no added in-line registration or combinational gating logic.

# IEEE Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits

- The TMS Sn output terminal, when driven by the PTAP TMS terminal, shall be driven with no added in-line registration.

- f) The TDI Sn input terminal shall sample data on the rising edge of TCK.

- The TDO Sn output terminal shall present new data on the falling-edge of TCK. g)

The permission is as follows:

It is permitted to buffer signals driving the TCK Sn, TMS Sn and TRSTN Sn terminals for drive h) strength.

#### 5.3.2 Description

The TCK and TRSTN signals are delivered directly to the STAP, as is, except for some buffering (but no additional in-line registration is allowed). They should always be enabled to the next die whether or not the STAP is selected. The TMS, TDI, and TDO signals are only enabled to or from the next die when the STAP is selected. Each of these signals has at least one multiplexer or in-line gate delay as part of the handling process to enable the selection and deselection.

The STAP terminals drive terminals on the secondary interface of the current die that then connect to their associated PTAP terminals on the next die, TCK Sn, TMS Sn, and TRSTN Sn outputs drive the associated PTAP terminals on the next die: TCK, TMS, and TRSTN, respectively. The STAP serial data terminals, the TDO Sn output and the TDI Sn input, are meant to, respectively, drive and receive the next die PTAP terminal counterparts, the TDI input and TDO output.

TDI Sn and TDO Sn also require registration, as they react on the rising or falling edge of TCK Sn. TDI Sn should sample data on the rising edge of TCK Sn and TDO Sn should present data on the falling edge of TCK Sn.

#### 5.4 Secondary test access port control logic

The STAP Control Logic (or STAP, for short) consists of several sub-components: the selector and the retiming elements.

#### 5.4.1 Specifications

The rules are as follows:

- Each STAP shall be selectable using the corresponding Select Sn signal from the 3DCR.

- b) When the Select Sn signal is asserted, it shall cause the STAP to select the associated PTAP of the next die between TDO Sn and TDI Sn.

- The first STAP (numbered k) shall source TDO Sk from TDI Sk int of the PTAP on the falling edge c) of TCK.

- STAPn (n < k) shall source TDI Sn int from TDO Sn+1 int of STAPn+1. d)

- If any STAPs are selected (at least 1 Select Sn is asserted) the PTAP shall source TDO from TDO S1 int of STAP1.

- NOTE—Refer to Figure 8 for reference numbering of STAPs.

- f) The last STAP (numbered I) shall connect TDO SI int to a point prior to the hold-time element (clocked by the falling edge of TCK) of the PTAP TDO.

- g) TDO\_Sn\_int shall be driven by a register element (clocked by the rising edge of TCK only in the ShiftDR and ShiftIR states) with data driven by TDI\_Sn or TDI\_Sn\_int according to the value of Select Sn.

- NOTE—ShiftDR and nd ShiftIR is represented in Figure 9 by the Enable signal. The Enable signal is the OR of the Shift IR and Shift DR signals (see Figure 7).

- h) TDO\_Sn shall be driven by a hold-time element (for example, clocked by the falling edge of TCK) with data driven by TDI Sn int.

- i) When STAP\_Sn is not selected (Select\_Sn is 0), TMS\_Sn shall be driven by RTI\_or\_TLR\_Sn (see 5.5.1).

- j) When STAP Sn is selected (Select Sn is 1), TMS Sn shall be driven by TMS.