# R105

#### NOW IN COURSE:

#### **2T0C** electrical assessment

Attilio Belmonte

#### **OPEN TO:**

Globalfoundries, Intel, Sony, TSMC, Samsung, Micron, SKHynix, Qualcomm, Kioxia, Western Digital, Huawei, KU Leuven, UGent

## If you have questions?

# 3 min Q&A slot at the end of each presentation

#### **Online Viewers**

You can post your questions during the presentation by clicking on the 'text balloon'

The session chair will handle all questions 'Live' at the end of the presentation.

If you are watching in delay, you can still post your questions. These questions will be answered by email.

### 6-months progress

#### 300-mm FRONT-GATED IGZO TRANSISTORS

#### 2T0C Gate-First structures:

- First reliable assessment of:

- retention time  $\rightarrow \sim 150$ s for  $C_{ox} = 126$ aF

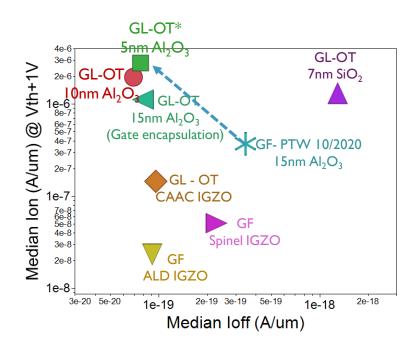

- $I_{OFF} = 3 \times 10^{-19} A/\mu m$

PTW October 2020

- 2T0C implementation for Gate-Last devices

- Median retention time > 900s for  $C_{ox}=127aF$ (Gate-Last with oxygen-tunnel)

- First assessment of 2T0C retention for spinel and ALD a-IGZO

#### Gate-Last with oxygen tunnel

echnical

#### Outline

- Introduction: Previous 2T0C results on Gate-First Devices

- 2T0C results in Gate-Last devices

- Effect of oxygen-tunnel on retention / off-current

- Gate First: 2T0C structures with different IGZO phase / deposition method

- CAAC / Spinel IGZO

- ALD a-IGZO

- Conclusions

confidential

### Outline

- Introduction: Previous 2T0C results on Gate-First Devices

- 2T0C results in Gate-Last devices

- Effect of oxygen-tunnel on retention / off-current

- Gate First: 2T0C structures with different IGZO phase / deposition method

- CAAC / Spinel IGZO

- ALD a-IGZO

- Conclusions

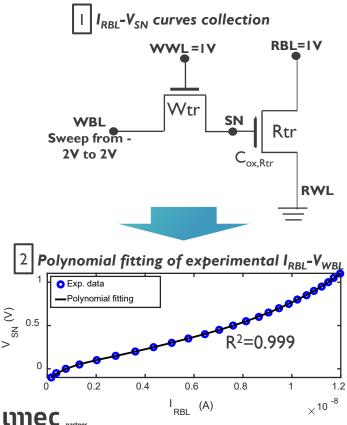

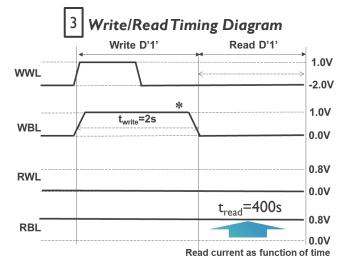

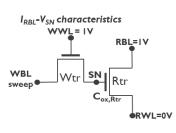

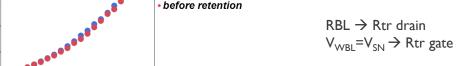

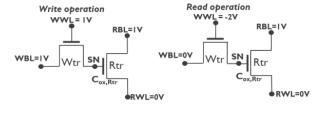

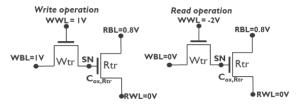

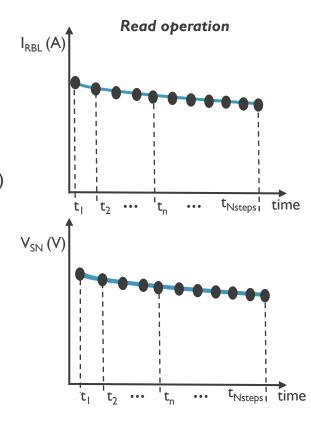

### Retention assessment method

Indirect monitoring of the storage-node voltage evolution

(V) NS V

\*WBL=IV for Is after WWL transition: Avoiding C discharge during WWL transition

$I_{RBI}$  is translated into  $V_{SN}$  by the polynomial fitting

confidential

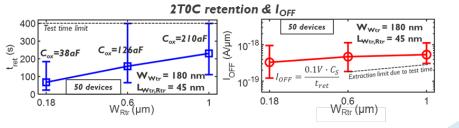

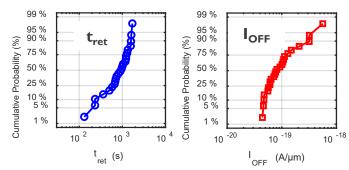

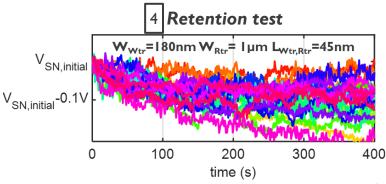

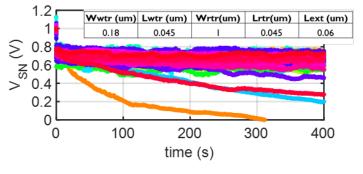

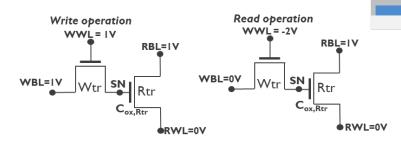

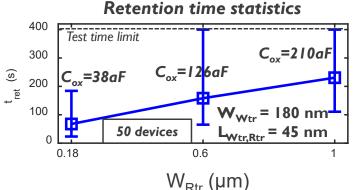

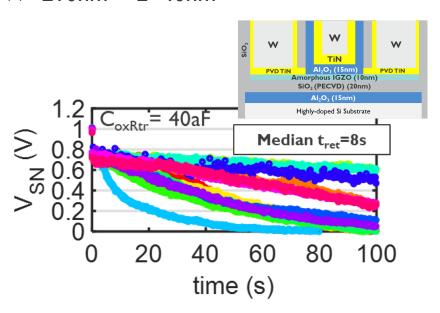

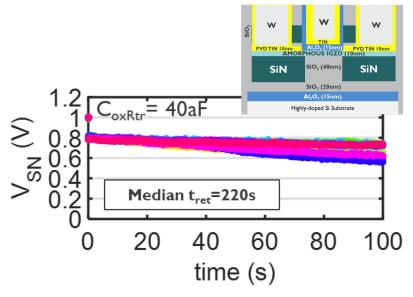

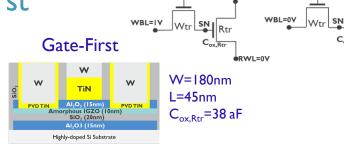

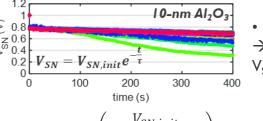

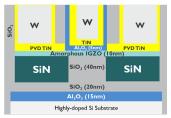

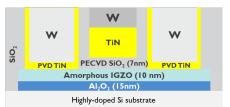

# Retention test: retention time scales with Cox

Retention assessment - 50 devices tested

Median  $t_{ret} > 60s$  achieved for  $C_{ox} = 38aF$  $W_{Rrr} = I \mu m$  and  $L_{Rrr} = 45nm \rightarrow > 25\%$  of the bits show  $t_{ret} > 400s$

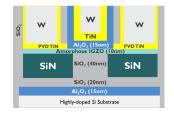

W

Amorphous IGZO (10nm)

SiO<sub>2</sub> (20nm)

Al<sub>2</sub>O3 (15nm)

Highly-doped Si Substrate

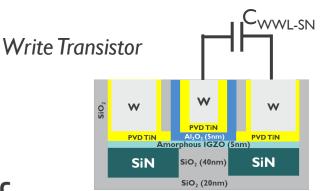

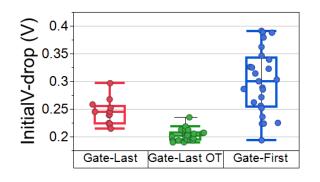

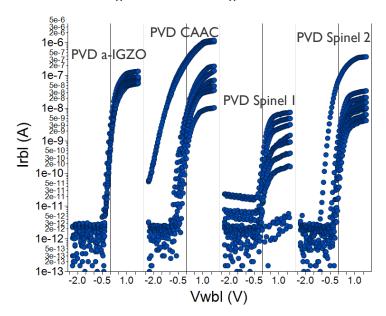

## High gate-drain capacitance may hinder 2T0C retention assessment

in Gate-Last PTW 10/2020 R104

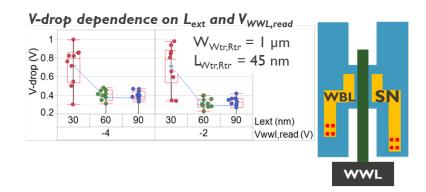

Initial V-drop always observed in the write/read transition

- Strong dependence of V-drop on  $L_{ext}$  and  $V_{WWL,read}$

- Capacitive coupling between SN and WWL

- $\rightarrow$   $V_{WWL}$  transition from 1V to -2V induces partial SN discharge

$C_{GD}$  is expected to be higher in Gate-Last configuration  $C_{GD}$  increases for thinner gate dielectric

Low  $V_{SN}$  after the transition between write and read?

confidential

### Outline

- Introduction: Previous 2T0C results on Gate-First Devices

- 2T0C results in Gate-Last devices

- Effect of oxygen-tunnel on retention / off-current

- Gate First: 2T0C structures with different IGZO phase / deposition method

- CAAC / Spinel IGZO

- ALD a-IGZO

- Conclusions

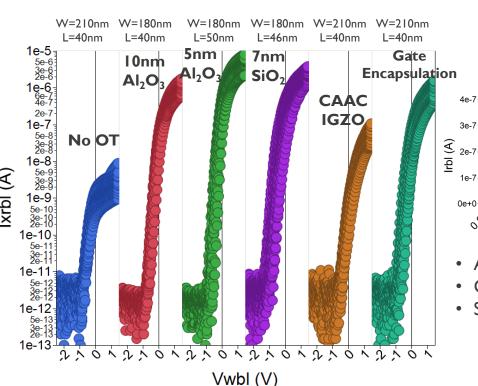

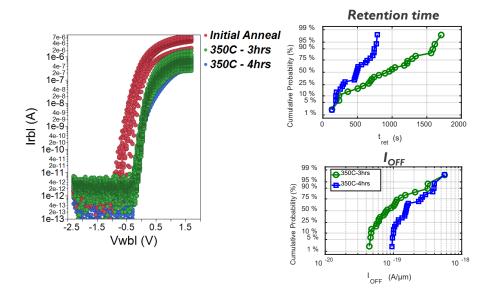

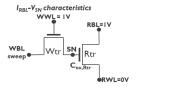

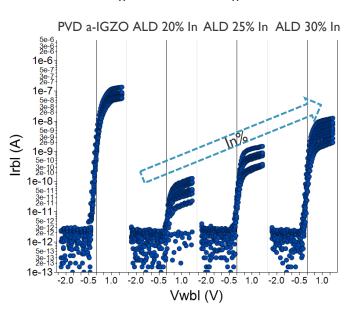

# Id-Vg characteristics of read transistors

after 400s retention test

Anneals were optimized to have similar V<sub>th</sub> in all split

Vwbl sweep

- Gate-Last reproducibility observed also for 2T0C structures

- Slight V<sub>th</sub> degradation after 400-s stress on read transistor

- $\rightarrow$  Polynomial fitting of a single  $I_D$ - $V_G$  may be misleading

- $\rightarrow$  Weighted average between the two I<sub>D</sub>-V<sub>G</sub> curves\*

3e-7

1e-7

Vwbl (V)

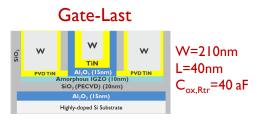

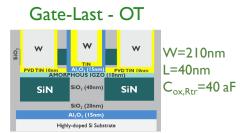

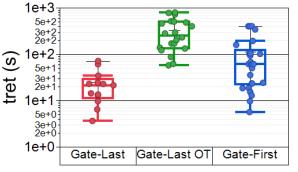

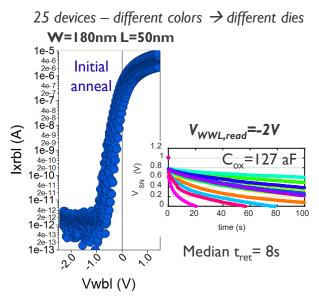

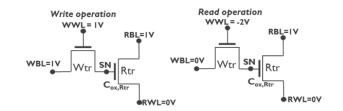

# Effect of Oxygen Tunnel on 2T0C retention

W=210nm - L=40nm

25 devices – different colors → different dies

Strong improvement in 2T0C retention thanks to the oxygen tunnel

More efficient defect passivation in the channel

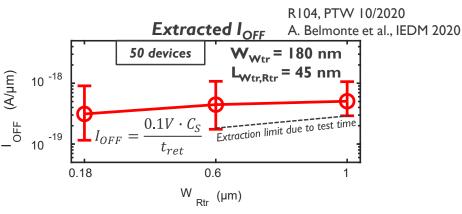

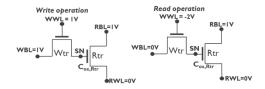

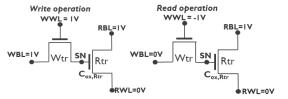

# Benchmarking against reference Gate-First

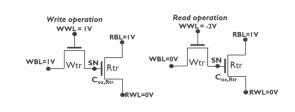

Write operation

RBL=IV

Read operation

RBL=IV

RWL=0V

- Gate-Last with oxygen tunnel enables longer retention thanks to lower l<sub>OFF</sub>

→More efficient defect passivation in write transistor channel

- Initial V-drop is lower than in Gate-First → to be investigated

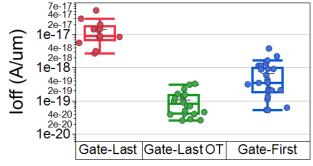

## 2T0C retention GL - Summary

• t<sub>ref</sub>>400s in some structures  $\rightarrow$  t<sub>ret</sub> and I<sub>OFF</sub> extrapolated from V<sub>SNI</sub> exponential decay

$$t_{ret} = ln\left(\frac{V_{SN,init}}{V_{SN,init} - 0.1V}\right) \cdot \tau$$

$I_{OFF} = \frac{V_{SN,init} \cdot Cox_{Rtr}}{\tau \cdot W_{Wtr}}$

$$I_{OFF} = \frac{V_{SN,init} \cdot Cox_{Rti}}{\tau \cdot W_{Wtr}}$$

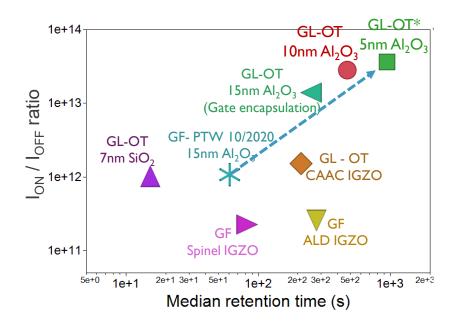

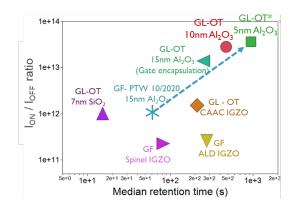

Longest retention time (>400s) and lowest I<sub>OFF</sub> achieved with 10-nm Al<sub>2</sub>O<sub>3</sub> gate dielectric + oxygen tunnel

- Initial V-drop depends on gate dielectric thickness

- Dependence on material (CAAC vs amorphous) to be investigated

- High  $I_{off}$  extracted for 5-nm  $Al_2O_3 \rightarrow High I_{gate}$  at -2V?

- Lower V<sub>WWI</sub> to prove the impact of I<sub>gate</sub>

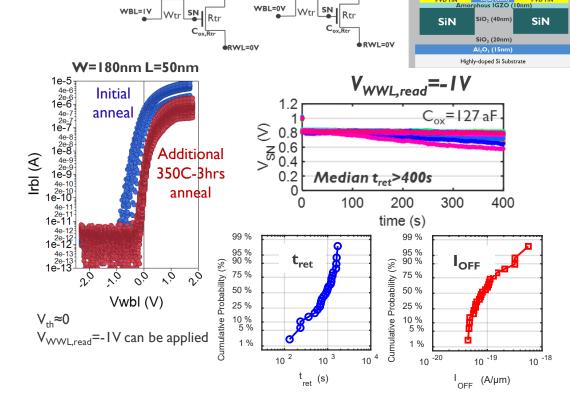

# Effect of V<sub>WWL,read</sub> on retention time

### 5nm Al<sub>2</sub>O<sub>3</sub> with oxygen-tunnel

- V<sub>th</sub> <-0.5V

- →Less negative V<sub>WWL,read</sub> cannot be applied

- →Additional anneal to increase V<sub>th</sub>

Read oberation

RBL=IV

Write operation

RBL=IV

- Lower  $|V_{WWL,read}| \rightarrow best retention ever$

- Benefit of <u>higher C<sub>ox,Rtr</sub> without penalty in I<sub>OFF</sub></u>

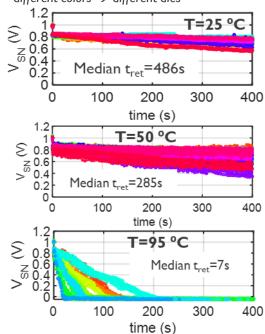

# Effect of additional $O_2$ -anneal and retention at high temperature

W=180nm L=50nm

Additional anneal does not improve  $V_{th}$  $\rightarrow$  But it induces  $I_{OFF}$  and  $t_{ret}$  degradation

#### Retention at high temperature

25 devices − different colors → different dies

Current fluctuation at high temperature

→ Retention can still be assessed

Strong V<sub>SN</sub> discharge at 95 °C

### Outline

- Introduction: Previous 2T0C results on Gate-First Devices

- 2T0C results in Gate-Last devices

- Effect of oxygen-tunnel on retention / off-current

- Gate First: 2T0C structures with different IGZO phase / deposition method

- CAAC / Spinel IGZO

- ALD a-IGZO

- Conclusions

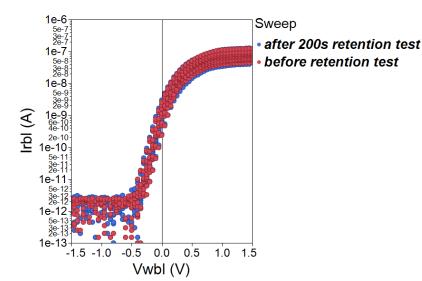

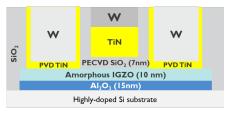

### Significant $V_{th}$ degradation after retention test in

Gate-First devices

W=180nm L=45nm

- Strong V<sub>th</sub> degradation induced by H diffusion from PECVD SiO<sub>2</sub> → see R106 / R107

- Weighted average between the two I<sub>RBL</sub>-V<sub>WBL</sub> curves necessary to have valid retention assessment\*

→ Unstable test-vehicle limits the learning for Gate-First devices

W

PECVD SiO<sub>2</sub> (7nm) p

Amorphous IGZO (10 nm)  $AI_2O_3$  (15nm)

Highly-doped Si substrate

W

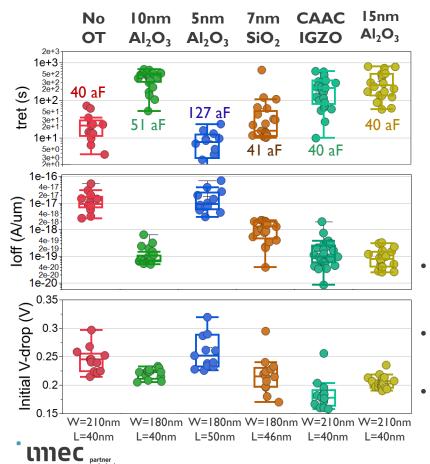

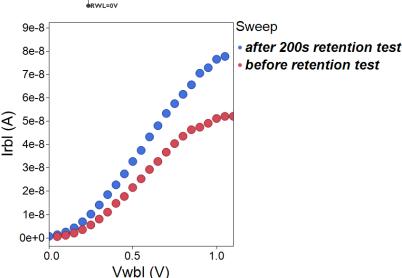

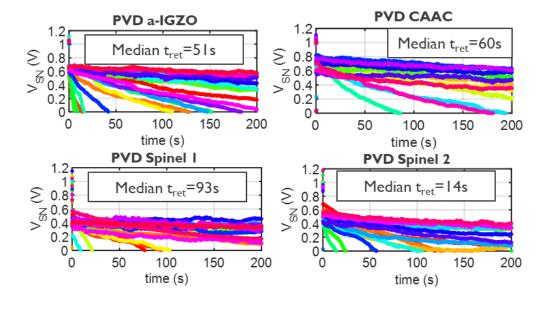

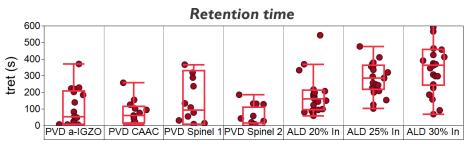

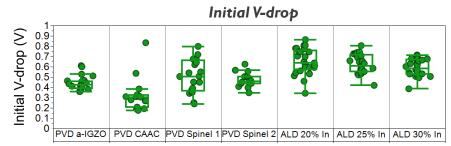

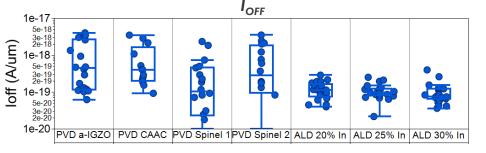

### Impact of IGZO Phase

W=180nm L=45nm;  $C_{ox,Rtr}=40$ aF

13 devices − different colors → different dies

- Large variability in transfer characteristics (PTW 10/2020 R106) → large variability in 2T0C retention

- No major impact of IGZO phase on retention

- Strong variability also for initial V-drop

| s-IGZO I | GZO 6 nm template: IGZO 90% O <sub>2</sub> , RT                                |

|----------|--------------------------------------------------------------------------------|

| s-IGZO 2 | GZO 6 nm template: IGZO 90% O <sub>2</sub> , RT - O <sub>2</sub> anneal 500 °C |

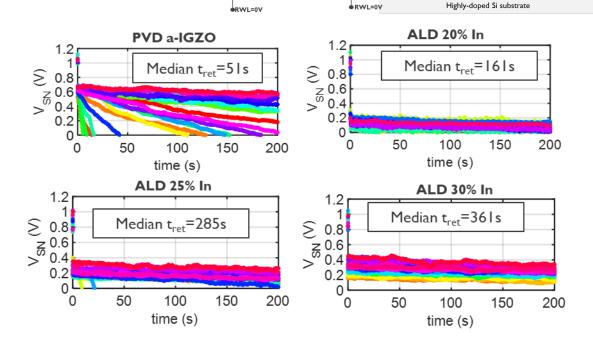

Impact of IGZO Deposition method

W=180nm L=45nm;  $C_{ox,Rtr}=40$ aF

13 devices – different colors  $\rightarrow$  different dies

Read operation

RBL=IV

Strong initial V-drop for ALD IGZO → V-drop not only due to WWL-SN capacitive coupling

Write operation

Promising retention with ALD IGZO  $\rightarrow$  to be assessed on Gate-Last

W

PECVD SiO<sub>2</sub> (7nm)

Amorphous IGZO (10 nm) Al<sub>2</sub>O<sub>3</sub> (15nm)

W

# Summary of Gate-First results

- Large variability hinders the learning for different channel materials

- V-drop dependence on channel material to be investigated

- Promising retention with ALD IGZO

→ To be re-assessed in Gate-Last devices

21

# Summary of I<sub>ON</sub> / I<sub>OFF</sub> / retention time

$$*V_{WWL,read} = -IV$$

### Conclusions

- 2T0C retention assessed on Gate-Last (w. and w/o Oxygen Tunnel) and Gate-First with different IGZO phase / deposition method

- Gate-Last with oxygen tunnel ensures better retention thanks to lower I<sub>OFF</sub>

- Initial V-drop depends on device architecture and channel material

- 5nm  $Al_2O_3$  gate dielectric:

- Retention and I<sub>OFF</sub> can be improved by reducing V<sub>WWL,read</sub>

- Gate-Last is a more reliable test-vehicle for 2T0C assessment:

- Lower initial V-drop

- Better reproducibility across the wafer

### Outlook

- Focus on understanding the trends observed in Gate-First and Gate-Last

- Impact of architecture and channel material on initial V-drop

- Effect of gate V-stress on 2T0C retention

- AC test implementation

- 2T0C and 2T1C implementation for best Gate-Last and Gate-First devices with oxygen tunnel

23

### Acknowledgments

#### **2T0C** characterization

Subhali Subhechha

Hyungrock Oh

Albert Vanhelmont

Gregor Vercaigne

Tom Daenen

Luc Dupas

#### **Integration**

**Hubert Hody**

Nouredine Rassoul

#### **CMP**

Lieve Teugels

Diana Tsvetanova

#### Film deposition

Harold Dekkers

#### Etch

24

Harinarayanan Puliyalil

Ming Mao

Laurent Souriau

#### **IGZO Team Management**

Romain Delhougne

Gouri Sankar Kar

Backup Slides

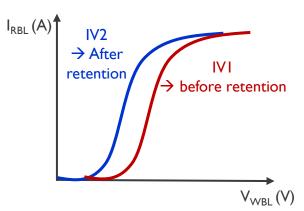

# Weighted average between I<sub>RBI</sub> before retention and after retention

Purpose: consider  $V_{th}$  degradation in the  $V_{SN}$  calculation

For each time step t<sub>n</sub>, the weighted average between the two I<sub>RRI</sub> -V<sub>WRI</sub> curves is calculated:

$$N_{\text{steps}}$$

= total number of time steps during read operation

For each time step

$$t_n$$

:

$f_{p,n}$  = polynomial fitting of IVavg $(t_n)$

$V_{SN}(t_n)$

=  $fp_n(IRBL(t_n))$

$$IVavg\left(t_{n}\right) = \frac{\left(IV1 \cdot N_{steps}\right) + \left(IV2 \cdot 0\right)}{N_{steps}} \qquad \text{First time step} \Rightarrow \text{only IVI is considered}$$

$$IVavg\left(t_{n}\right) = \frac{\left(IV1 \cdot \left(N_{steps} - n\right)\right) + \left(IV2 \cdot n\right)}{N_{steps}} \qquad \text{Time step n} \Rightarrow \text{weighted average between IVI and IV2}$$

$$N_{steps} \qquad \qquad \text{between IVI and IV}$$

$$IVavg (t_{Nsteps}) = \frac{(IV1 \cdot 0) + (IV2 \cdot N_{steps})}{N_{steps}} \qquad \qquad \text{Last time step} \Rightarrow \text{only IV}$$

Last time step → only IV2 is considered

27