# A Read Voltage Modulation Technique for Leakage Current Compensation in Cross-Point OTS-PRAM

Kwang Woo Lee, Hyun Kook Park and Seong-Ook Jung School of Electrical and Electronic Engineering Yonsei University Seoul 03722, South Korea Email: {kw2801.lee, hyunkuky, sjung}@yonsei.ac.kr

Abstract—In this paper, a read voltage modulation technique (RVM) is proposed to compensate for leakage current in a cross-point phase change random access memory with an ovonic threshold switch (OTS-PRAM). The leakage current, the sum of off-state current (IOFF) of OTS selectors, causes the voltage drop and increases the variation of sensing voltage (V<sub>SENSE</sub>) which is the electric potential difference between a selected bit line (BL) and a word line (WL). Eventually, the voltage drop reduces the sensing margin (SM). To compensate for the BL voltage drop, the proposed RVM reduces the V<sub>SENSE</sub> variation by applying an adaptive voltage to the selected WL. Thus, a sufficient SM is guaranteed. HSPICE simulation results with industry-compatible 65-nm model parameters show that the cross-point OTS-PRAM with the proposed RVM achieved a remarkable improvement in SM (from 105 mV to 395 mV) in high BL leakage current condition

Keywords—Cross-point array, leakage current compensation, off-state current, ovonic threshold switch (OTS), phase change memory (PRAM), read voltage modulation (RVM)

## I. INTRODUCTION

Phase change random access memory (PRAM) is one of the promising storage class memory (SCM) candidates to overcome both the slow latency of flash memory and the short-term data retention of dynamic random access memory. Since the prototype 3D cross-point PRAM with an ovonic threshold switch (OTS-PRAM) in [1] was introduced, highdensity 3D cross-point OTS-PRAM has been developed by major semiconductor vendors [2], [3]. Owing to an OTS with low temperature processing, a multi-stackable cell structure is enabled in a cross-point array, unlike diode selectors that require high temperature processing such as dopant activation [4], [5]. Accordingly, various OTS alloys have been studied [4], [6]-[9]. However, when the OTS material exhibits poor off-state current (IOFF) characteristic, the high I<sub>OFF</sub> causes problems in read and write operations [2]. Especially, as the array size increases, the effect of I<sub>OFF</sub> on the read and write operations increases [10], [11]. In this study, a new technique is proposed to resolve the high I<sub>OFF</sub> issue in the cross-point OTS-PRAM during the read

This paper is organized as follows. In Section II, the effect of the high I<sub>OFF</sub> on the read operation is verified. Section III describes a novel read voltage modulation technique (RVM) for resolving the high I<sub>OFF</sub> issue. Subsequently, results of various experiments are compared in Section IV. Finally, Section V provides the conclusion in this paper.

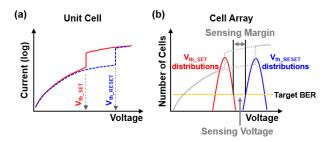

Fig. 1. (a) I-V curves of OTS-PRAM cell in SET and RESET state. (b)  $V_{\text{TH SET}}$  and  $V_{\text{TH RESET}}$  distributions in an array.

#### II. EFFECT OF $I_{OFF}$ ON READ OPERATION

#### A. OTS-PRAM Cell Characteristics

An OTS-PRAM cell consists of an OTS selector and a storage element GeSbTe (GST). The OTS has only an irreversible amorphous phase, while the GST has two different phases: crystalline phase for a SET state (low resistance state) and amorphous phase for a RESET state (high resistance state) [1].

Fig. 1(a) shows the current-voltage (I-V) curve of the OTS-PRAM cell and Fig. 1(b) shows the threshold voltage  $(V_{th})$  distribution of a cell array, where  $V_{th}$  SET and  $V_{th}$  RESET are V<sub>th</sub> of OTS-PRAM cells in the SET and RESET state, respectively. The sensing margin (SM), a key factor to estimate the yield of a product, is the voltage difference between  $V_{\text{th}\ \text{SET}}$  and  $V_{\text{th}\ \text{RESET}}$  distributions. To sense the data, the applied sensing voltage (V<sub>SENSE</sub>) which is the electric potential difference between a selected bit line (BL) and a word line (WL), is normally middle voltage between the  $V_{th SET}$  and  $V_{th RESET}$  distributions, as shown in Fig. 1(b). When the V<sub>SENSE</sub> is applied to the selected cell with the SET state during the read operation, a snapback phenomenon occurs in the OTS [12]. The phenomenon causes the excessive current, which flows to a sense amplifier (SA). Whereas in the case of a cell with the RESET state, the snapback phenomenon does not occur and only the I<sub>OFF</sub> of the cell is transferred to the SA. As a result, the data of the selected cell is extracted due to the snapback phenomenon.

# B. OTS-PRAM Core Operation and $I_{OFF}$ Issue

A 1/2 V<sub>BIAS</sub> scheme in read and write operations is well known for preventing a sneak current and minimizing standby power consumption in the cross-point OTS-PRAM with a bidirectional symmetric I-V characteristic of OTS [10], [11]. In case of a  $x \times y$  cell array, x-1 and y-1 half-selected cells in the selected BL and WL exist, respectively. Thus, as the array size increases, the number of half-selected cells increases.

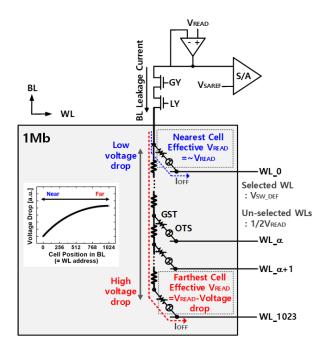

Fig. 2. Description of voltage drop induced by the BLC, the sum of  $I_{OFF}$  of half-selected cells in a selected BL in an 1 Mb array (1 Kb  $\times$  1 Kb). The inset shows an example of the voltage drop depending on a cell postion.

As shown in Fig. 2, when the selected BL is precharged to a read bias voltage (V<sub>READ</sub>) and the selected WL is discharged to  $V_{\text{SW\_DEF}}$  in the read operation, the middle voltage between V<sub>READ</sub> and V<sub>SW\_DEF</sub>, typically half voltage of V<sub>READ</sub> (1/2 V<sub>READ</sub>), is applied to half-selected cells in the selected BL. The IOFF of the half-selected cells flows from the selected BL to the un-selected WLs, and the sum of the I<sub>OFF</sub> is called the BL leakage current (BLC). As the number of cells per BL increases, the BLC increases and eventually the voltage drop increases. If the BLC induces the voltage drop, V<sub>READ</sub> is not fully transmitted to the far cell. Thus, the effective V<sub>th</sub> of a cell detected by a sense amplifier (SA) is higher than the intrinsic V<sub>th</sub> due to the voltage drop. The inset of Fig. 2 shows the voltage drop depending on the cell position in a BL. As the WL address increases, the voltage drop becomes saturated. This is because the effective V<sub>READ</sub> of the far cells is reduced, thereby reducing the I<sub>OFF</sub>.

## C. Verification of SM Degradation due to Leakage Current

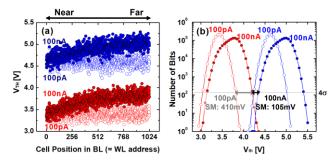

Based on an 1 Mb array (1 K/WL × 1 K/BL), a HSPICE simulation with OTS and GST models was performed to verify the effect of the I<sub>OFF</sub> on the SM degradation [13]-[15]. In particular, the V<sub>th SET</sub> and V<sub>th RESET</sub> were modified by controlling the amorphous chalcogenide thickness parameter. The  $V_{\text{th\_SET}}$  and  $V_{\text{th\_RESET}}$  were extracted  $10^6$  times through a Monte-Carlo simulation, where the mean of  $V_{th SET}$  is 3.4 V, the standard deviation of  $V_{th \ SET}$  ( $\sigma_{V_{th \ SET}}$ ) is 100 mV, the mean of  $V_{th\_RESET}$  is 4.6 V, and the standard deviation of  $V_{th\_RESET}$  is 100 mV. To extract the effective  $V_{th}$  depending on the cell position in a BL, several BL sheet resistance (Rs) were assumed (from 5  $\Omega$ /sq to 20  $\Omega$ /sq) and OTS models with various I<sub>OFF</sub> were used (from 100 pA to 100 nA). Fig. 3 compares the V<sub>th SET</sub> and V<sub>th RESET</sub> extracted using the Monte-Carlo simulation when a BL Rs is assumed to be 10  $\Omega$ /sq and the OTS models with  $I_{OFF} = 100 \text{ pA}$  and 100 nA are used. Fig. 3(a) shows the  $V_{th\ SET}$  and  $V_{th\ RESET}$  depending on the cell position in a BL. In the case of the 100 pA I<sub>OFF</sub>, there

Fig. 3. (a) Simulated  $V_{th\_SET}$  and  $V_{th\_RESET}$  of a cell with  $I_{OFF} = 100$  pA and 100 nA depending on the cell position in a BL, respectively. (b) Simulated  $V_{th}$  distribution of an 1 Mb array with  $I_{OFF} = 100$  pA and 100 nA, respectively.

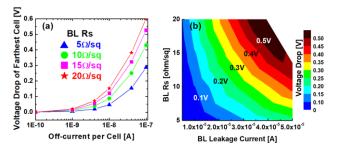

Fig. 4. (a) Voltage drop of farthest cell depending on various  $I_{\text{off}}$  and BL Rs. (b) Voltage drop of farthest cell depending on various BLC and BL Rs.

is no cell position dependency in the effective  $V_{th}$ . However, in the case of the 100 nA  $I_{OFF}$ , the increase in the effective  $V_{th}$  at the far cells is clearly observed. The effective  $V_{th}$  in the farthest cell increases by 0.430 V compared to the intrinsic  $V_{th}$ . Fig. 3(b) shows the  $V_{th}$  distribution of an 1 Mb array. The SM at  $4\sigma$  is 410 mV and 105 mV when the  $I_{OFF}$  is 100 pA and 100 nA, respectively. The huge SM degradation is observed under the condition with  $I_{OFF}=100$  nA.

To achieve a high production yield, a sufficient SM should be guaranteed. As shown in Fig. 4(a), to avoid the SM degradation, it is necessary to use the OTS with  $I_{OFF} < 1$  nA. In addition, the BLC should be less than 5 uA, as shown in Fig. 4(b). If the OTS exhibits the high  $I_{OFF}$  (over 1 nA), alternatives are needed to prevent the SM degradation. Thus, we focus on the  $I_{OFF}$  compensation circuit technique.

#### III. READ VOLTAGE MODULATION TECHNIQUE (RVM)

In this section, we introduce the BLC monitoring method and the technique to compensate for the voltage drop based on the measured BLC.

## A. BLC Monitoring

To measure the BLC, a dummy BL with cells is placed on the edge of the 1 Mb array (1 K/BL  $\times$  1 K/WL) and a pad to measure the BLC is connected to the dummy BL. The BL coupled with the pad causes timing skew during read operations. This is due to the parasitic capacitance and resistance induced by circuits and extra wiring for leakage current measurement. Thus, the pad is not connected to an actual BL. The BLC is measured by applying  $V_{READ}$  (4 V) to the pad when the voltages of un-selected BLs and all WLs are 1/2  $V_{READ}$  (2 V). The voltage drop can be estimated by comparing the measured BLC with the simulation results shown in Section II. If the  $I_{OFF}$  of a cell at 1/2  $V_{READ}$  is 100

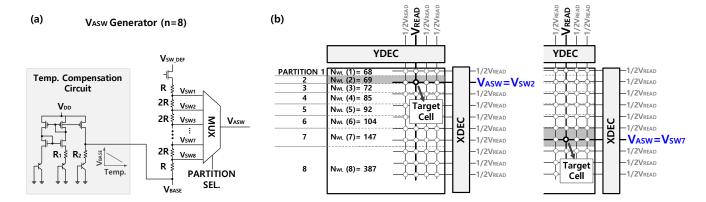

Fig. 5. (a)  $V_{ASW}$  generator with 3 parts for the proposed RVM: temperature compensation circuit [17], voltage divider, and MUX. (b) WL partitioning example and  $V_{ASW}$  for each partition.

TABLE I.  $I_{OFF},$  BLC, and Voltage drop at T = –25 °C, 25 °C, and 85 °C.

|               | I <sub>OFF</sub> per cell [nA] | BLC [uA] | Voltage drop in<br>the farthest cell<br>[V] |  |

|---------------|--------------------------------|----------|---------------------------------------------|--|

| 85 °C         | 100.0                          | 51.3     | 0.430                                       |  |

| 25 °C         | 15.4                           | 12.1     | 0.123                                       |  |

| <b>-25</b> °C | 3.9                            | 3.7      | 0.038                                       |  |

nA, the 51.3 uA BLC will be measured in the pad. With the known BL Rs and the measured BLC, it can be estimated that the voltage drop in the farthest cell is 0.430 V.

As temperature increases, the  $I_{OFF}$  of the OTS increases exponentially and the voltage drop also increases. Thus, it is essential to check the relation between voltage drop and temperatures. Table I shows the  $I_{OFF}$ , the BLC, and the voltage drop in the farthest cell at  $T=-25~^{\circ}C$ , 25  $^{\circ}C$ , and 85  $^{\circ}C$ . Commonly,  $I_{OFF}$  is proportional to  $\exp(-1/T) \times \sinh(1/T)$ , where T is the absolute temperature [12], [13]. When the temperature rises from  $-25~^{\circ}C$  to 85  $^{\circ}C$ , the voltage drop increases more than 10 times. Thus, the BLC temperature coefficient should be extracted by measuring the BLC at various temperatures and considered in the BLC compensation technique.

### B. Read Voltage Modulation Technique (RVM)

A conventional method for a BL voltage drop compensation is to control the BL bias voltage [16]. However, the variation of the BL bias voltage affects the BLC and eventually results in the BL voltage drop variation. Therefore, the control of the BL bias voltage is not a suitable method for the BL voltage drop compensation. In order to effectively compensate for the BL voltage drop, a robust RVM that is an adaptive control method of the selected WL voltage is proposed. The proposed RVM reduces the  $V_{\rm SENSE}$  variation by controlling the selected WL voltage. Compared with the conventional BL voltage control, the proposed RVM does not affect the  $I_{\rm OFF}$  of the half-selected cells in the selected BL during read operations because there is no variation in the electric potential difference between the selected BL and un-selected WLs.

Fig. 5 shows adaptive selected WL voltages ( $V_{ASW}$ ) generator for the proposed RVM, WL partitioning example, and the  $V_{ASW}$  for each partition. As shown in Fig. 5(a), the

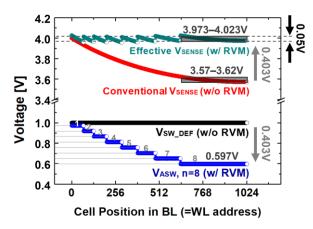

Fig. 6. Conventional  $V_{\text{SENSE}}$ , Effective  $V_{\text{SENSE}}$ ,  $V_{\text{SW\_DEF}}$ , and  $V_{\text{ASW}}$  (n=8) depending on the cell position in a BL.

$V_{ASW}$  generator consists of 3 parts: a bandgap type temperature compensation circuit [17], a voltage divider, and a MUX. To generate a reference voltage called  $V_{BASE}$ , the bandgap type temperature compensation circuit is used. Because the voltage drop induced by the BLC is temperature dependent,  $V_{BASE}$  should also be temperature dependent. The target  $V_{BASE}$  for each temperature is controlled by the ratio of  $R_1$  to  $R_2$ . In addition, to compensate for the voltage drop in the farthest cell, the potential difference between  $V_{BASE}$  and  $V_{SW\_DEF}$  should be equal to the voltage drop in the farthest cell. Subsequently, evenly distributed multiple voltages are generated using the voltage divider. Finally, the  $V_{ASW}$  is applied to the selected WL based on the target cell address information during read operations. The  $V_{ASW}$  is expressed as follows:

$$V_{ASW} = V_{SW\_DEF} - \left\{ \frac{V_{BASE}}{n} \times \left( m - \frac{1}{2} \right) \right\}$$

(1)

, where  $V_{SW\_DEF}$  is the default voltage of the selected WL, n is the number of partitions, m is the partition number. The WLs in an 1 Mb array are divided into n partitions and the  $V_{ASW}$  are applied to the partitions, as shown in Fig. 5(b). In the case of n=8, the eight  $V_{ASW}$  (from  $V_{SW1}$  to  $V_{SW8}$ ) are required. If the cell in the seventh partition is selected during read operations,  $V_{SW7}$  is applied to the selected WL.

Fig. 6 compares the selected WL voltage and the  $V_{\text{SENSE}}$  with and without the RVM (n=8) when the voltage drop in

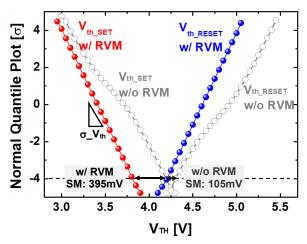

Fig. 7. Comparison of normal quantile plot w/o and w/RVM (n=8).

| TABLE II. RESULTS OF VAI | RIOUS EXPERIMENT |

|--------------------------|------------------|

|--------------------------|------------------|

|                                                              | I <sub>OFF</sub> : 100 pA<br>(w/o RVM) | I <sub>OFF</sub> : 100 nA<br>(w/o RVM) | Ioff: 100nA (w/ RVM) |      |      |      |

|--------------------------------------------------------------|----------------------------------------|----------------------------------------|----------------------|------|------|------|

|                                                              |                                        |                                        | n=2                  | n=4  | n=8  | n=16 |

| Mean of<br>V <sub>th_SET</sub> [V]                           | 3.40                                   | 3.71                                   | 3.44                 | 3.42 | 3.41 | 3.40 |

| $\begin{matrix} \sigma_{\_}V_{th\_SET} \\ [mV] \end{matrix}$ | 100                                    | 160                                    | 118                  | 105  | 101  | 100  |

| SM at 4σ<br>[mV]                                             | 410                                    | 105                                    | 300                  | 370  | 395  | 400  |

the farthest cell is 0.430 V. The selected BL is precharged to V<sub>READ</sub> (5 V, not shown in Fig. 6) and the selected WL is discharged to V<sub>SW DEF</sub> (1 V). Thus, the target V<sub>SENSE</sub> is 4 V. Without the RVM, the reduction of the conventional V<sub>SENSE</sub> is observed as the WL address increases. For example, the reduced conventional V<sub>SENSE</sub> in the eighth partition varies between 3.57 V and 3.62 V, as shown in Fig. 6. However, with the proposed RVM, the selected WL voltage is replaced from the V<sub>SW DEF</sub> to the V<sub>ASW</sub>. Accordingly, the V<sub>SW8</sub> (0.597 V) calculated in (1) is applied to the eighth partition. Since the selected WL voltage is replaced by 0.597 V from 1 V, the effective V<sub>SENSE</sub> in the eighth partition is in the range 3.973 V to 4.023 V, close to the target  $V_{SENSE}$  (4V). As a result, with the proposed RVM, the variation of the effective V<sub>SENSE</sub> is less than 0.05V regardless of the cell position in a BL, as shown in Fig. 6. By reducing the V<sub>SENSE</sub> variation, the effective V<sub>th</sub> of a cell detected by a SA is very close to the intrinsic V<sub>th</sub>.

# IV. EXPERIMENTAL RESULTS

In the case of  $I_{OFF} = 100$  nA, Fig. 7 shows a comparison of a normal quantile plot with and without the RVM (n=8). The high  $I_{OFF}$  causes  $\sigma_{-}V_{th}$  increase (a slope of graphs shown in Fig. 7), resulting in the SM degradation. However, with the proposed RVM, it is possible to compensate for the voltage drop induced by the high  $I_{OFF}$  and to achieve the improved SM. Despite the high  $I_{OFF}$ , the SM has extended from 105 mV to 395 mV with the RVM.

Table II compares the results of various RVM cases, where the number of partitions is 2, 4, 8, and 16. As the

number of partitions increases, the RVM is more effective. Eventually, both  $\sigma_-V_{th}$  and SM become closer to the intrinsic characteristics of cells. However, when comparing n=8 with n=16, there is no remarkable improvement in the results. Thus, considering the area efficiency and the circuit complexity for the RVM, the eight partitions are a reasonable choice

#### V. CONCLUSION

This paper proposed the RVM to significantly reduce the effect of the leakage current, the sum of IOFF of OTS selectors, in the cross-point OTS-PRAM. The OTS selector enables multi-stackable cell arrays, but the SM degradation is caused by the voltage drop due to the leakage current. The proposed RVM to resolve the BL voltage drop issue reduces the V<sub>SENSE</sub> variation by applying the adaptive voltage to the selected WL. Even though this technique requires additional circuits for the BLC measurement and the V<sub>ASW</sub> generation and the modified core decoder, the proposed RVM has high immunity to the leakage current as compared to a conventional read method. As a result, we successfully improved the SM (from 105mV to 395 mV) in the crosspoint array with the high leakage current using the proposed RVM. With the proposed RVM, the cross-point OTS-PRAM will be more valuable for the cost-effective SCM application.

#### REFERENCES

- [1] D. Kau et al., "A stackable cross point phase change memory," IEEE Int. Electron Devices Meeting, pp. 27.1.1–27.1.4, 2017.

- [2] T. Kim et al., "High-perfrmance, cost-effective 2z nm two-deck cross-point memory integrated by self-align scheme for 128 Gb SCM," IEEE Int. Electron Devices Meeting, pp. 37.1.1–37.1.4, 2018.

- [3] Intel and Micron produce breakthrough memory technology., https://newsroom.intel.com/news-releases/intel-and-micron-producebreakthrough-memory-technology/#gs.09gr6x, July 28, 2015.

- [4] Y. Koo, K. Baek and H. Hwang, "Te-Based Amorphous Binary OTS Device with Excellent Selector Characteristics for X-point Memory Applications," Symp. VLSIT, pp. 86–87, 2016.

- [5] M.J. Kang et al., "PRAM cell technology and characterization in 20nm node size," IEEE Int. Electron Devices Meeting, pp. 3.1.1– 3.1.4, 2012.

- [6] M.C. Cyrille et al., "Invited paper: OTS Selector Device: Material Engineering for Switching Performance," Proc. ICICDT, doi: 10.1109/ICICDT.2018.8399769, 2018.

- [7] S.D. Kim et al., "Effect of Ge Concentration in Ge<sub>x</sub>Se<sub>1-x</sub> Chalcogenide Glass on the Electronic Structures and the Characteristics of Ovonic Threshold Switching (OTS) Devices," ECS Solid State Lett. vol. 2(10), pp. Q75–Q77, 2013.

- [8] H. Y. Cheng et al., "Ultra-High Endurance and Low I<sub>OFF</sub> Selector based on AsSeGe Chalcogenides for Wide Memory Window 3D Stackable Crosspoint Memory," IEEE Int. Electron Devices Meeting, pp. 37.3.1–37.3.4, 2018.

- [9] A. Velea et al., "Te-based chalcogenide materials for selector application," Nature, Scientific reports 7, 8013, August, 2017.

- [10] G.W. Burr et al., "Access devices for 3D crosspoint memory," Journal of Vacuum Science and Technology B, vol. 32, no. 4, pp. 040802, 2014.

- [11] W.C. Chien et al, "Comprehensive Scaling Study on 3D Cross-Point PCM toward 1Znm Node for SCM Applications," Symp. VLSIT, pp. T60–T61, 2019.

- [12] W. D. Parkinson, "Reading a phase change memory," U.S. Patent 8427862B2, Nov. 14, 2011.

- [13] Sentaurus Device User Guide, K-2015.06, Synopsys, MountainView, CA, USA, 2015.

- [14] D. Ielmini and Y. Zhang, "Analytical model for subthreshold conduction and threshold switching in chalcogenide-based memory devices," J. Appl. Phys. 102, 054517, 2007.

- [15] H. K. Park, T. H. Choi, H. K. Ahn, and S. Jung, "Thermoelectric Cooling Read for Resolving Read Disturb With Inrush Current Issue in OTS-PRAM," IEEE Trans. Nanotechnol., vol. 18, pp. 421–431, 2019.

- [16] H-R Oh et al, "Enhanced Write Performance of a 64-Mb Phase-Change Random Access Memory," IEEE Int. Solid-State Circuits Conf. (ISSCC), pp. 48–49, 2005.

- [17] B. Razavi, "Design of Analog CMOS Integrated Circuits," McGraw-Hill, 2002.