# Journal Pre-proofs

A physics-based compact model for phase-change memory considering the ratio of vertical-to-lateral crystal growth rate for the design of cross-point storage-class memory

Donguk Kim, Jun Tae Jang, Dong Myong Kim, Sung-Jin Choi, Sanghyun Ban, Minchul Shin, Hanwool Lee, Hyung Dong Lee, Hyun-Sun Mo, Dae Hwan Kim

PII: S0038-1101(20)30422-6

DOI: https://doi.org/10.1016/j.sse.2020.107955

Reference: SSE 107955

To appear in: Solid-State Electronics

Please cite this article as: Kim, D., Tae Jang, J., Myong Kim, D., Choi, S-J., Ban, S., Shin, M., Lee, H., Dong Lee, H., Mo, H-S., Hwan Kim, D., A physics-based compact model for phase-change memory considering the ratio of vertical-to-lateral crystal growth rate for the design of cross-point storage-class memory, *Solid-State Electronics* (2020), doi: https://doi.org/10.1016/j.sse.2020.107955

This is a PDF file of an article that has undergone enhancements after acceptance, such as the addition of a cover page and metadata, and formatting for readability, but it is not yet the definitive version of record. This version will undergo additional copyediting, typesetting and review before it is published in its final form, but we are providing this version to give early visibility of the article. Please note that, during the production process, errors may be discovered which could affect the content, and all legal disclaimers that apply to the journal pertain.

© 2020 Published by Elsevier Ltd.

<u>Donguk Kim</u><sup>1</sup>, Jun Tae Jang<sup>1</sup>, Dong Myong Kim<sup>1</sup>, Sung-Jin Choi<sup>1</sup>, Sanghyun Ban <sup>2</sup>, Minchul Shin <sup>2</sup>, Hanwool Lee <sup>2</sup>, Hyung Dong Lee<sup>2</sup>, Hyun-Sun Mo<sup>1</sup>, and Dae Hwan Kim<sup>1\*</sup>

<sup>1</sup>School of Electrical Engineering, Kookmin University, Seoul 136-702, Korea <sup>2</sup>SK hynix, 2091, Gyeongchung-daero, Bubal-eup, Icheon-si, Gyeonggi-do, 17336, Korea

#### ARTICLE INFO

### **ABSTRACT**

Kevwords:

PcRAM physics-based compact model Ovonic threshold switching Poole-Frenkel emission GST crystal growth

A physics-based compact model for phase-change random access memory (PcRAM) was proposed considering the ratio of vertical-to-lateral crystal growth rate (a) and it was incorporated into HSPICE via Verilog-A. The proposed model was verified by using the experimental results taken from the 256 × 256 cross-point (X-point) PcRAM cell array with the  $Ge_2Sb_2Te_5$ technology node. The proposed compact successfully reproduced measured PcRAM cell resistance (R<sub>C</sub>) depending on the SET pulse width and amplitude after a background RESET, which is a challenging issue in the X-point PcRAM as the promising candidate for a

### 1. Introduction

With the advent of the memory-centric computing era, the demand for storage-class memory (SCM) with large capacity and high performance for data centers and cloud computing systems has exploded [1-4]. The SCM requirements, such as low latencies, byte-addressability, long-endurance, and persistency at low cost, are unable to be satisfied by the current NAND and DRAM technology [5]. Among the emerging nonvolatile memories with low latency and fair reliability, phase-change memory (PCM) has attracted much attention as a promising SCM candidate which can fill the performance gap between DRAM and 3-D NAND Flash [6]. Therefore, the read latency and cost-effectiveness of PCM need to be improved further to play the role of an SCM [7]. However, simple downscaling of the conventional PCM cannot achieve these improvements. Cross-point (X-point) PCM has emerged as a solution for these issues since it has not only an ultimate areal density of 4F<sup>2</sup> and 3-D stackability for superior cost-effectiveness but also a low read latency [8].

Since the Intel-Micron announced the successful development and mass production for stackable 3-D X-point memory using an amorphous selector [9], many efforts have been made not only for the technological optimization for the PCM and selector materials but also in perspective of the compact model for the X-point-level memory design including the thermal/electrical disturbance and/or an analog modulation of PCM cell resistance in the viewpoint of neuromorphic application [10-11]. Very recently, the Hynix announced the successful development of high-performance and cost-effective X-point 2z-nm PCM technology for two-deck 128 Gb SCM with very low latencies of write (set < 300 ns) and read (< 100 ns) [12].

From the viewpoint of the compact modeling for the design of the X-point PCM, three issues need to be emphasized. First, there is a need for modeling that reflects the physical meaning while reducing the computational burden for heat distribution and thermal disturbance. The

traditional line-type (L-type) PCM caused an asymmetric thermal disturbance due to the different thermal conductivity of phase-change material (along the bit line), oxide, and the interface (along the word line). In other words, the L-type PCM resulted in a more severe thermal disturbance since the accumulated heat was distributed more along the line direction than the other direction [2], [13-14]. And then, via the confined structures (C-type) of PCM for reducing the RESET current (I<sub>RESET</sub>) and thermal disturb, the X-point PCM was spotlighted as abovementioned. Efforts to precisely calculate the structure-dependent thermal distribution would be significantly compromised with the compactness and computation efficiency (including acceptable convergence) of the models for the X-point PCM design. An efficient and natural approach to solving the trade-off among the precision, physics-based, and compactness is considering the ratio of vertical-to-lateral crystal growth rate.

Secondly, in the C-type or X-point PCM, which use the solid-phase crystallization, the SET operation is much more challenging rather than  $I_{RESET}$  in the perspective of the write latency and power consumption because the SET operation takes a much longer time than the RESET operation [15-16]. Thus, the resistance of PCM cell needs to be carefully characterized and reproduced by the compact model-based simulation, mainly depending on the SET pulse width and amplitude.

Finally, either the continuous change of PCM cell resistance or the dynamic variables such as a crystallization ratio and the size of conducting filament (CF), needs to be considered according to a write pulse. This model property is essential, especially in the PCM-based neuromorphic circuit simulations.

In this paper, we proposed a physics-based compact model for PcRAM (phase-change random access memory) considering the ratio of vertical-to-lateral crystal growth rate ( $\alpha$ ), incorporated it into HSPICE via Verilog-A, and verified it through the experimental results taken from the 256  $\times$  256

successfully reproduced the measured PcRAM cell resistance (R<sub>C</sub>) depending on the SET pulse width and amplitude while capturing the essence of physical meaning via the multi-domain simulation, including the threshold switching, electrical, thermal, and phase-change modules.

Furthermore, the proposed model was described as a voltage-driven model rather than a current-driven model because the input in a real circuit and the solution method in a circuit simulator usually take voltage as an input other than current.

# 2. Physics-based compact model for PcRAM simulation

# 2.1. Description of crystal volume, geometry, and the ratio of vertical-to-lateral crystal growth rate $(\alpha)$

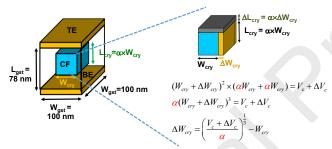

The structure and fabrication process was the same as [12] except excluding the selector. The  $256 \times 256$  X-point PcRAM cell array with GST 2z-nm technology node was fabricated as a test pattern. The length (L<sub>gst</sub>) and width (W<sub>gst</sub>) of GST in the X-point PcRAM test pattern were 78 nm and 100 nm. The area of GST was  $100 \text{ nm} \times 100 \text{ nm}$  (W<sub>gst</sub><sup>2</sup>).

After fully resetting (background RESET process), the crystal volume ( $V_c$ : CF volume) increases during the SET process. The SET time-evolution of  $V_c$  and the ratio of vertical-to-lateral crystal growth rate ( $\alpha$ ) were taken into account as shown in Fig. 1.

**Fig. 1.** Schematic view of the PcRAM cell structure illustrating the SET time evolution of the crystal CF volume.

If the  $V_c$  at a specific time spot  $(t=t_0)$  is  $L_{cry}\times W_{cry}{}^2=\alpha\times W_{cry}{}^3,$  the  $V_c$  at the next time spot  $(t=t_0+\Delta t)$  is determined by both  $\Delta L_{cry}$   $(=\alpha\times\Delta W_{cry})$  and  $\Delta W_{cry}.$  Here,  $L_{cry},$   $W_{cry},$  and  $\alpha$   $(=L_{cry}/W_{cry}=\Delta L_{cry}/\Delta W_{cry})$  are the length of crystal CF, the CF width, and the ratio of vertical-to-lateral crystal growth rate, respectively.

# 2.2. Threshold switching

The ovonic threshold switching (OTS) is the most critical physical mechanism on PcRAM operation. Many studies suggest that OTS occurs in specific threshold electric fields of amorphous chalcogenide materials; various mechanisms have been introduced to address this [17-19]. We used a ballistic tunneling mechanism for OTS [20-21].

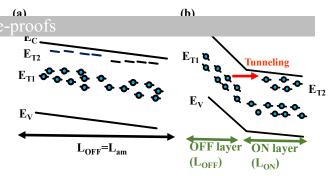

In the initial state of amorphous GST, steady-state electrons are trapped in the deep state ( $E_{T1}$ ) near the Fermi level, as shown in Fig. 2(a). In this state, when a voltage is applied across amorphous GST, the electric field can be calculated by dividing the voltage by the length of amorphous GST length ( $L_{am}$ ). The electric field supplies the energy for the electrons to facilitate tunneling from  $E_{T1}$  to the shallow state ( $E_{T2}$ ) near the conduction band as shown in Fig. 2(b).

Fig. 2. Energy band of amorphous GST (a) before and (b) after OTS occurs.

Here, the tunneling rate can be defined as (1) [21]

$$\frac{d\Delta n_{t2}}{dt} = G_0 \exp\left(\frac{-B}{F_{OEE}}\right) - \frac{\Delta n_{t2}}{\tau_n} \tag{1}$$

where  $\tau_n$  denotes an effective time for electron relaxation from  $E_{T2}$  to  $E_{T1}$ , B represents the Fowler–Nordheim tunneling characteristic constant [22],  $G_0$  indicates maximum tunneling rate,  $F_{OFF}$  is the electric field across the OFF layer, and  $n_{t2}$  denotes electron density at  $E_{T2}$ . As the tunneling rate increases in a strong electric field, the electron concentration at the  $E_{T2}$  level increases, and the amorphous state becomes a high conductance state; thus, OTS occurs. Therefore, as shown in Fig. 2(b), electric field discontinuity occurs between the layers where electron concentration in  $E_{T2}$  is high (ON layer) and low (OFF layer). At this time, since  $E_{T2}$ – $E_{T1}$  is the tunneling barrier, the length of the OFF layer ( $L_{OFF}$ ) in which tunneling occurs can be defined as (2), and the length of the ON layer ( $L_{ON}$ ) can be subsequently determined by (3).

$$L_{OFF} = \frac{E_{T2} - E_{T1}}{qF_{OFF}} \tag{2}$$

$$L_{ON} = L_{GST} - L_{OFF} \tag{3}$$

# 2.3. Electrical model

For amorphous GST, the electron transport model is based on the Poole–Frenkel emission model, and two activation energies are considered according to different trap levels of  $E_{T1}$  and  $E_{T2}$ , as shown by (4) [21], [24].

$$\begin{split} I_{am} &= 2A_a \times q \times \frac{\Delta z_a}{\tau_0} n_{t1} \times \exp\left(-\frac{E_C - E_{T1}}{kT}\right) \times \sinh\left(\frac{qF\Delta z_a}{2kT}\right) \\ &+ 2A_a \times q \times \frac{\Delta z_a}{\tau_0} n_{t2} \times \exp\left(-\frac{E_C - E_{T2}}{kT}\right) \times \sinh\left(\frac{qF\Delta z_a}{2kT}\right) \end{split} \tag{4}$$

where q denotes unit charge, kT denotes thermal energy,  $n_{t1}$  indicates the trap concentration at  $E_{T1}$ ,  $A_a$  denotes an amorphous area,  $\Delta z_a$  denotes an average distance between traps in amorphous GST,  $E_C$  means the conduction band minimum energy level,  $\tau_0$  indicates the electron characteristic time, and F denotes electric field ( $F_{OFF}$  before OTS and  $F_{ON}$  after OTS). Before/after OTS, the electric field of the current model (4) is defined differently, as shown by (5).

# Journal Pre-proof

$= \frac{L_{ON}}{L_{am}}$  (Before OTS)

After OTS,  $F_{OFF}$  is obtained by inverting the current equation, as shown by (6); it can be used again to define the tunneling rate (1) and  $L_{OFF}$  (2).

$$F_{OFF} = \frac{2kT}{q\Delta z} \sinh^{-1} \left( \frac{\tau_0 I_{am}}{2A_a q \Delta z_a n_{t1} \times \exp\left(-\frac{E_C - E_{T1}}{kT}\right)} \right)$$

(6)

When OTS occurs, although the GST is in an amorphous state, the current increases to a sufficiently high value for the GST to reach crystallization temperature. When crystallization occurs, the electron transport model of GST is changed into the ohmic model, defined by (7) [25].

$$I_{cry} = A_c \times \frac{q \mu n_c}{L_{cry}} \times \exp\left(\frac{-E_{a\_c}}{kT}\right) \times V \tag{7}$$

where  $\mu$  denotes the electron mobility in crystalized GST,  $n_c$  denotes electron concentration in the crystalized GST,  $L_{cry}$  denotes the length of crystal CF, and  $E_{a\_c}$  indicates the activation energy of the crystal GST resistivity. Depending on the state of the GST phase, amorphous or crystal current models ( $I_{am}$  or  $I_{cry}$ ) can be used, which will be discussed in Section 2.6.

#### 2.4. Thermal model

The thermal model is based on Fourier's law [26], which is defined by (8)

$$T = T_0 + P \times R_t \tag{8}$$

where T is temperature as the function of position,  $T_0$  is the temperature at a reference position, P is the dissipated power between the T and  $T_0$  positions, and  $R_t$  is thermal resistance. The temperature is distributed spatially point by point, and then the P is calculated spatially and time-by-time depending on  $R_t$ .

P can be calculated by the current flowing through the GST and the voltage applied between the top electrode (TE) and the bottom electrode (BE). Besides, T<sub>0</sub> plays the role of boundary condition, which can be, for example, the temperature outside the GST. By updating the equivalent R<sub>t</sub> according to the SET time-evolution of CF, we can simplify the complicated effect of thermal distribution, capturing the essence of the influence of thermal distribution on the direction-dependent crystallization rate of GST. It relieves the computing burden of a compact model without losing the physical parameters and their meanings, which will be explained the Section 2.6.

# 2.5. Phase change model

The phase change model consists of melting, cooling, and crystallization, and two types of crystallization mechanisms,

the cooling process is performed rapidly under crystallization temperature, the GST hardens into an amorphous state [29]. These mechanisms can be expressed by (9) and (10), respectively,

$$\frac{dV_m}{dt} = \frac{\gamma_m}{1 + \exp(-\frac{T - T_m}{H})}\tag{9}$$

$$\left(\frac{dV_a}{dt}\right)_{cooling} = \frac{\gamma_c}{1 + \exp(\frac{T - T_c}{H_c})} \qquad (V_m > 0)$$

(10)

where  $\gamma_m$  and  $\gamma_c$  denote the melting and cooling probability.  $T_m$  and  $T_c$  also denote the melting and crystallization temperature, and  $V_a$  and  $V_m$  mean the amorphous and melted volume of GST, respectively.  $H_m$  and  $H_c$  are the fitting parameters describing the melting and cooling, respectively.

Then, the nucleation rate of GST is given by (11),

$$\left(\frac{dV_c}{dt}\right)_{nucle} = P_{n0} \exp\left\{-\frac{1}{kT} \left[E_{a_n} + \frac{\beta_n^2}{\left(1 - \frac{T}{T_m}\right)^2}\right]\right\} \times V_{GST}C_a \tag{11}$$

where  $V_c$  denotes the crystal volume,  $P_{n0}$  means the crystallization probability by nucleation mechanism,  $E_{a\_n}$  denotes nucleation activation energy,  $\beta_n$  denotes the fitting parameter,  $V_{GST}$  denotes the GST volume, and  $C_a$  means the amorphous volume ratio and is given by  $V_a/V_{GST}$  with  $V_a$  = the amorphous volume. The nucleation mechanism originates from the nucleus of amorphous GST, and the crystallization rate with the nucleation mechanism is proportional to the volume of amorphous material  $V_a$ , as shown in (11).

On the other hand, the growth rate of GST is given by (12).

$$\left(\frac{dV_c}{dt}\right)_{gro} = v_{g0} \times \exp\left(-\frac{0.8T_m}{T_m - T}\right) \times \left[1 - \exp\left(-\frac{\Delta G}{kT}\right)\right] \times \exp\left(-\frac{E_{a\_g}}{kT}\right) \times \frac{S_a}{S_{amax}}$$

(12)

where  $v_{g0}$  denotes the fitting parameter,  $\Delta G$  denotes the excess Gibbs free energy of the amorphous phase over the crystalline solid,  $E_{a\_g}$  denotes growth activation energy,  $S_a$  denotes amorphous-crystal cross-section area, and  $S_{amax}$  denotes the maximum amorphous-crystal cross-section area. Noticeably, since the growth-based crystallization occurs at the boundary between amorphous and crystal GST, the growth-based crystallization rate is proportional to the interface area of the two material states, as shown by (12).

The equations (9)-(12) describe the time-temperature-transformation (TTT) characteristic curve, which expresses the phase transformation in combination with time and temperature. From the TTT curve, the phase change of GST can be traced time-wise, depending on temperature and time. In our transient simulation, the SET

$$\Delta V_c = \left| \left( \frac{dV_c}{dt} \right)_{nucle} + \left( \frac{dV_c}{dt} \right)_{gro} - \left( \frac{dV_a}{dt} \right)_{cooling(V_m > 0)} \right| \Delta t \quad (13)$$

where  $\Delta t$  denotes the time step in a transient simulation.

#### 2.6. Compact model-based multi-domain simulation

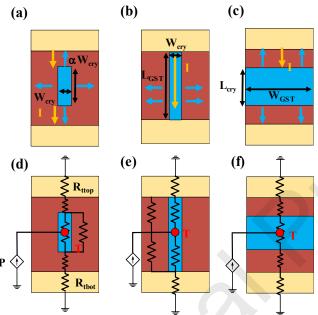

It is assumed that in a C-type structure without a heater, the internal temperature of the GST increases from the GST center position. Therefore, the phase change also begins at the center of the GST, as shown in Figs. 3(a) and (d). Then, we can describe the shape of the crystal structure determined by the complex thermal distribution using parameter  $\alpha$ .

Thanks to  $\alpha$ , we can reflect a variety of possibilities for the phase-change rate varied depending on the direction, temperature distribution, and X-point aspect ratio, as shown in Fig 3.

**Fig. 3.** The SET time-evolution of CF in the viewpoint of the electrical (a), (b), (c) and thermal (d), (e), (f) model. (a), (d) The crystal volume reaches neither the electrode nor the GST wall. (b), (e) The crystal volume reaches the electrode first (large  $\alpha$ ). (c), (f) The crystal volume reaches the GST wall first (small  $\alpha$ ).

After a background RESET, the SET time-evolution of CF is illustrated from the viewpoint of the electrical model in Figs. 3(a)-(c). If the crystallization rate in the vertical direction is relatively high (large  $\alpha$ ), the CF evolves from Fig. 3(a) to Fig. 3(b). In contrast, when the crystallization rate along the lateral direction is relatively high (small  $\alpha$ ), it evolves from Fig. 3(a) to Fig. 3(c). When the CF reaches the electrode first [Fig. 3(b)], amorphous and crystal volumes form in parallel, so the amorphous current with low conductance is ignored, and the crystal current model is followed. In the other case, the amorphous and crystal volumes are connected in series [Fig. 3(c)], so the amorphous current model is followed, as shown by (14).

$$I = I_{am} \quad \left( L_{cry} < L_{GST} \right)$$

$$I_{cry} \quad \left( L_{cry} = L_{GST} \right)$$

(14)

case of the electrical model, if the crystallization rate in the vertical direction is relatively high (large  $\alpha$ ), the CF evolves from Fig. 3(d) to Fig. 3(e). In contrast, when the crystallization rate along the lateral direction is relatively high (small  $\alpha$ ), it evolves from Fig. 3(d) to Fig. 3(f). Thus, the effect of thermal distribution can be concisely calculated by updating  $R_t$  in (8) and by tracking the temperature in the center of GST, as shown by (15)

$$R_{l} = R_{ttop} + R_{tbot} + \frac{1}{2} \left[ \sigma_{a} \frac{L_{GST} - L_{cry}}{W_{GST}^{2}} + \left( \sigma_{a} \frac{L_{cry}}{W_{CST}^{2} - W_{cry}^{2}} \| \sigma_{c} \frac{L_{cry}}{W_{cry}^{2}} \right) \right]$$

(15)

where  $\sigma_a$  and  $\sigma_c$  denote the thermal conductivities of amorphous and crystal states, and  $R_{ttop}$  and  $R_{tbot}$  mean the thermal resistances of top and bottom electrodes.

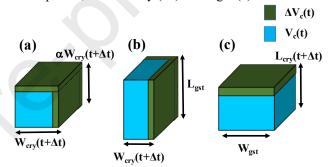

The SET time-evolution of CF is calculated as follows. The crystal volume is determined by both the updated  $\Delta V_c$  from (13) and parameter  $\alpha$ . If the CF reaches neither the electrode nor the GST wall ( $L_{cry} < L_{GST}$  and  $W_{cry} < W_{GST}$ ), the CF is updated, as shown by (16) and Fig. 4(a).

Fig. 4. The SET time-evolution of CF during the SET time step  $\Delta t$  in crystallization. (a) When CF reaches neither the electrode nor the GST wall, (b) when CF reaches the electrode first, and (c) when CF reaches the GST wall first.

$$W_{cry}(t+\Delta t) = \left(\frac{V_c(t) + \Delta V_c}{\alpha}\right)^{\frac{1}{3}}$$

(16)

Furthermore, if the CF reaches the electrode first ( $L_{cry} = L_{GST}$  and  $W_{cry} < W_{GST}$ ), the CF evolves, as shown by (17) and Fig. 4(b)

$$W_{cry}(t+\Delta t) = \sqrt{\frac{V_c(t) + \Delta V_c}{L_{gst}}}$$

(17)

Finally, if the CF reaches the GST wall first ( $L_{cry} \le L_{GST}$  and  $W_{cry} = W_{GST}$ ), the CF is updated, as shown by (18) and Fig. 4(c).

$$L_{cry}(t + \Delta t) = L_{cry}(t) + \Delta L_{cry}$$

(18)

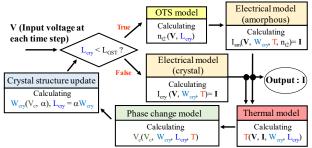

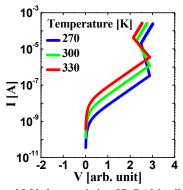

Figure 5 shows the simulation sequence of the proposed multi-domain compact model. Furthermore, Fig. 6 shows the simulated I-V characteristic of PcRAM cell depending on temperature. The snap-back is well reproduced. Here, it should be noted that the threshold switching voltage is independent of temperature, which is reasonable because, in

Fig. 5. Simulation sequence of the proposed multi-domain compact model.

**Fig. 6.** Simulated I-V characteristic of PcRAM cell depending on temperature.

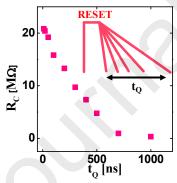

Figure 7 shows the simulated quenching time-dependence of  $R_{\rm C}$  during RESET operation. As the quenching time ( $t_{\rm Q}$ ) increases, the  $R_{\rm C}$  after RESET decreases. It is because the longer  $t_{\rm Q}$ , the more time margin for the amorphization process is performed. In other words, the PcRAM cell has the duration enough to be further amorphized.

Fig. 7. (a) simulated quenching time-dependence of RC during RESET operation

Our results suggest that our multi-domain model is reliably computing the electrical and thermal as well as the phase-change and OTS properties of GST material and PCM cell.

# 3. Model verification by comparing experimental results

To verify our model, we compare the simulation results with the measured ones. Extracted parameters are summarized in Table I.

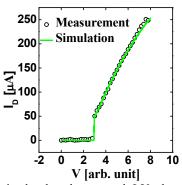

Figure 8 shows the I-V characteristic of the PcRAM cell in the center position of the  $256 \times 256$  cell array. The parasitic resistance from the metal pad to the PcRAM cell (from the bit line pad via the target cell to the word line pad) in the X-point array was extracted to be  $10~\mathrm{k}\Omega$ . The simulated I-V

Table I. Extracted model parameters

| Domain                | Parameter                               | Value                                                        | Unit                |

|-----------------------|-----------------------------------------|--------------------------------------------------------------|---------------------|

| -                     | α                                       | 1.55                                                         | -                   |

|                       | $\Delta t$                              | 1                                                            | ns                  |

|                       | q                                       | 1.6×10 <sup>19</sup>                                         | С                   |

| Electrical            | $n_{t1}$                                | $1 \times 10^{19}$                                           | cm <sup>-3</sup>    |

| model                 | $\Delta z_{ m a}$                       | 2                                                            | nm                  |

| (Amorphous)           | $	au_0$                                 | 5x10 <sup>-14</sup>                                          | S                   |

|                       | $E_C$ - $E_{T1}$ and $E_C$ - $E_{T2}$   | 0.25 and 0.01                                                | eV                  |

| Electrical            | $\mathrm{E_{a\_c}}$                     | 0.14                                                         | eV                  |

| model                 | $n_c$                                   | $1 \times 10^{22}$                                           | cm <sup>-3</sup>    |

| (Crystal)             | μ                                       | $4.69 \times 10^{3}$                                         | $cm^2/(V \cdot s)$  |

| OTS                   | $\tau_{ m n}$                           | 1                                                            | ns                  |

|                       | В                                       | 4×10 <sup>5</sup>                                            | cm/V                |

|                       | $G_0$                                   | $1 \times 10^{27}$                                           | $cm^{-3}/s$         |

| Thermal               | $\sigma_a$ and $\sigma_c$               | 0.01 and 0.015                                               | $W/(cm \cdot K)$    |

| model                 | R <sub>ttop</sub> and R <sub>tbot</sub> | $6\times10^6$ and $6\times10^6$                              | K/W                 |

| Phase change<br>model | γ                                       | 7.73                                                         | $(J/cm^2)$          |

|                       | $E_{a,n}$ and $E_{a,g}$                 | 0.94 and 0.73                                                | eV                  |

|                       | $P_{n0}$                                | $3.84 \times 10^{11}$                                        | $s^{-1}$            |

|                       | $ m V_{g0}$                             | 13.35                                                        | cm·s-1              |

|                       | β                                       | 1                                                            | -                   |

|                       | $r_{\rm m}$ and $r_{\rm c}$             | $1{\times}10^{\text{-}11}\text{and}1{\times}10^{\text{-}11}$ | $cm^3 \cdot s^{-1}$ |

|                       | $H_{\rm m}$ and $H_{\rm c}$             | 5 and 5                                                      | K                   |

|                       | $T_m$ and $T_c$                         | 889 and 450                                                  | K                   |

|                       | $\Delta h_1$                            | 453                                                          | J/cm <sup>3</sup>   |

Fig. 8. The simulated and measured I-V characteristic of the PcRAM cell in the center position of the  $256 \times 256$  cell array.

In order to further verify the proposed model, the resistance of PcRAM cell  $R_{\rm C}$  was characterized depending on the SET pulse width and amplitude after a background RESET. As mentioned in the Introduction, in the X-point PCM, the SET operation is much more challenging rather than  $I_{\rm RESET}$  in the perspective of the write latency and power consumption. Thus, the  $R_{\rm C}$  needs to be carefully characterized and reproduced by the compact model-based simulation, depending on the SET pulse width and amplitude.

The measurement sequence is illustrated in Fig. 9.

Fig. 9. (a)  $256 \times 265$  cell array with series resistance  $R_S$  and GST stacked and (b) the pulse sequence of the background RESET  $\rightarrow$  SET  $\rightarrow$  Read, where both the amplitude and width of the SET pulse were changed.  $R_C$  is readout by applying V= 0.3 V.

Pulse measurements were performed with series resistance ( $R_S$ ) to suppress excessive current, as shown by Fig. 9(a). For pulse measurement, the pulse sequence consists of background RESET pulse, SET pulse, and read pulse, as shown by Fig. 9(b). The background RESET pulse was used to ensure the GST was fully amorphized. In fully amorphous GST, crystallization is performed by applying SET pulse. We split the amplitude of the SET pulse ( $V_{SET}$ ) and the width of the SET pulse ( $V_{SET}$ ). After SET pulse, a Read pulse of 0.3 V was applied to measure the GST current. We calculated the GST resistance  $R_C$  at this point, which allowed us to analyze the crystallization properties.

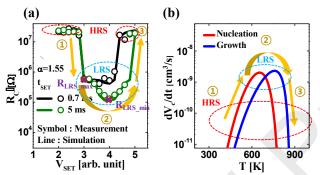

Fig. 10. (a) Measured and simulated  $R_C$  depending on  $V_{SET}$  and  $t_{SET}$ . (b) TTT curve is defined by (11) and (12).

Figure 10(a) shows the pulse measurement and simulation results. In the write operation, where V<sub>SET</sub> and t<sub>SET</sub> are determined, the following behavior exists: The larger the crystal volume, the lower the GST R<sub>C</sub> taken from the 0.3-V Read pulse. By analyzing the trend of the measured data, it is evident that R<sub>C</sub> follows a U-shape according to V<sub>SET</sub>, as shown by Fig. 10(a)  $\bigcirc \rightarrow \bigcirc \rightarrow \bigcirc$ . This is because, when  $V_{SET}$ increases, the temperature inside the GST increases, so it follows the trend of the TTT curve of Fig. 10(b)  $\bigcirc \rightarrow \bigcirc \rightarrow \bigcirc$ . Regardless of pulse width, the R<sub>C</sub> changes from the high resistance state (HRS) to the low resistance state (LRS) abruptly, as shown in Fig. 10(a) ①. From this trend, since OTS occurrence is independent of t<sub>SET</sub>, we can assume that OTS occurs in Fig. 10(a) ①, and crystallization occurs in the GST. However, the voltage that changes from LRS to HRS (as seen in Fig. 10(a) ③) increases as t<sub>SET</sub> increases.

When a long SET pulse is applied (longer  $t_{SET}$ ), crystallization time increases, but overall resistance reduces. By analyzing Fig. 10(b) ③, it is interpreted that the crystallization rate decreases as temperature increases, which suggests that, when  $t_{SET}$  is long, the GST is in the LRS.

Undoubtedly, it is essential to use an appropriate value of  $\alpha$  to reproduce the trend of Fig. 10(a) in the simulations. The

that the GST is 100% crystal when  $R_C = R_{LRS\_min}$  in Fig. 10(a). Then,  $R_{LRS\_max}$  is taken from the maximum  $R_C$  in the LRS domain in Fig. 10(a), and it is assumed that the crystal immediately reaches both electrodes. Since the cross-sectional area of the crystal pillar  $(W_{cry}^2)$  and  $R_C$  is inversely proportional, the crystal pillar width and the  $\alpha$  can both be calculated by (17).

$$\alpha = \frac{L_{GST}}{W_{cry\_init}} = \frac{L_{GST}}{\left(W_{GST}\sqrt{\frac{R_{LRS\_min}}{R_{LRS\_max}}}\right)}$$

(17)

where  $W_{cry\_init}$  denotes the crystal pillar width when  $R_{\rm C}$  =  $R_{LRS~max}$ . In this way, the  $\alpha$  was extracted to be 1.55.

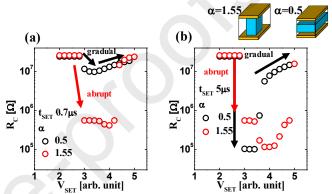

Fig. 11.  $R_C$  -V<sub>SET</sub> simulation result with  $\alpha$ =1.55,  $\alpha$ =0.5 and different  $t_{SET}$ . (a)  $t_{SET}$  =0.7 $\mu$ s and (b)  $t_{SET}$  =5 $\mu$ s.

We can also simulate the effect of  $\alpha$  on the  $R_C$  – $V_{SET}$  characteristics. Figure 11 compares the  $R_C$  – $V_{SET}$  curves for  $\alpha$  = 1.55, where the CF reaches the electrodes in the SET process, as well as for  $\alpha$  = 0.5, where the CF reaches the GST wall in different  $t_{SET}$  = (a) 0.7  $\mu$ s and (b) 5  $\mu$ s. As shown in Fig. 11(a), when  $\alpha$  = 1.55, crystal and amorphous GST form in parallel, and abrupt switching characteristic is observed; when  $\alpha$  = 0.5, crystal and amorphous GST form in series, and gradual switching characteristic is observed.

However, as shown in Fig. 11(b), since  $t_{SET}$  is long enough for the GST to be entirely crystallized, abrupt characteristics are observed for both  $\alpha = 0.5$  and  $\alpha = 1.55$ . Moreover, in Fig. 11(b), when  $\alpha = 0.5$ , under the condition of low crystallization rate, the gradual characteristic is observed for the same reason as the case of  $\alpha = 0.5$  in Fig. 11(a).

These results suggest that by employing the ratio of vertical-to-lateral crystal growth rate  $\alpha$ , the  $R_C$  in the 2z-nm technology node X-point PcRAM can be reproduced depending on the SET pulse width and amplitude without a heavy computing burden. Furthermore, it is found that the  $V_{SET}$ -dependent abrupt/gradual change of  $R_C$  is sensitive to  $\alpha$ , which means that  $\alpha$  should be carefully optimized for the PCM-based neuromorphic applications.

# 4. Conclusion

A physics-based compact model for PcRAM was proposed considering the ratio of vertical-to-lateral crystal growth rate  $\alpha$ , and it was incorporated into HSPICE via Verilog-A. The proposed model was verified by using the experimental results taken from the 256  $\times$  256 PcRAM cell array with 2z-nm GST X-point technology. The proposed

and amplitude while capturing the essence of physical meaning via the multi-domain simulation, which includes the threshold switching, electrical, thermal, and phase-change modules.

#### Acknowledgments

This work was supported by SK hynix and in part by the NRF funded by the Korean government under Grant 2016R1A5A1012966, 2019M3F3A1A02071845 and 2020R1A2B5B01001979.

#### References

- IelLee S-H. Technology Scaling Challenges and Opportunities of Memory Devices. In: IEDM Tech Dig 2017:1.1.1-8.

- [2] Fong SW, Neumann CM, Wong H-SP. Phase-change memory —Towards a storage-class memory. IEEE Trans. Electron Devi ces 2017;64(11):4374-85.

- [3] Burr GW, Kurdi BN, Scott JC, Lam CH, Gopalakrishnan K, She noy RS. Overview of candidate device technologies for storageclass memory. IBM J Res Dev 2008;52(4/5):449-64.

- [4] Lee S, Song J, Lim S, Chekol SA, Hwang H. Excellent data rete ntion characteristic of Te-based conductive-bridge RAM using semiconducting Te filament for storage class memory Sangmin. Solid-State Electron 2019;153:8-11.

- [5] Kim T, Lee S. Evolution of Phase-Change Memory for the Storage-Class Memory and beyond. IEEE Trans Electron Devices 2020;67(4):1394-06.

- [6] Navarro G, Navarro G, Kluge J, Serra AL, Verdy A, Garrione J, et al. Phase-change memory: Performance, roles and challenges. Proc. Int. Memory Workshop (IMW) 2018.

- [7] Molas G, Robayo A, Lopez M, Grenouillet L, Carabasse C, Nav arro G, et al. Crosspoint Memory Arrays: Principle, Strengths a nd Challenges. Proc. Int. Memory Workshop (IMW) 2020:56-9.

- [8] Kim IS, Cho SL, Im DH, Cho EH, Kim DH, Oh GH, et al. High performance PRAM cell scalable to sub—20 nm technology with below cell size, extendable to DRAM applications. In: Symp VLSI Technol 2010:T19.3.

- [9] Clarke P. Intel, Micron launch "bulk-switching" ReRAM. 2015

[Online]. Available: https://www.eenewsanalog.com/news/intel-micron-launch-bulk-switching-reram

- [10] Chen X, Hu H, Huang X, Cai W, Liu M, Lam C, et al. A SPICE Model of Phase Change Memory for Neuromorphic Circuits. IEEE Access. 2020;8;95278-87.

- [11] Burr GW, Brightsky MJ, Sebastian A, Cheng H-Y, Wu J-Y, Kim S, et al. Recent progress in phase-change memory technology. IEEE J Emerg Sel Topics Power Electron. 2016;6(2):146-62.

- [12] Kim T, Choi H, Kim M, Yi J, Kim D, Cho S, et al. High-performance, cost-effective 2z nm two-deck crosspoint memory integrated by self-align scheme for 128 Gb SCM. In: IEDM Tech Dig 2018:37.1.1-4.

- [13] Yoo S, Lee HD, Lee S, Choi H, Kim T. Electro-Thermal Model for Thermal Disturbance in Cross-Point Phase-Change Memory. IEEE Trans Electron Devices 2020;67(4):1454-9

- [14] Lee JI, Park H, Cho SL, Park YL, Bae BJ, Park JH, et al. Highly scalable phase change memory with CVD GeSbTe for sub 50 nm generation. In: Symp VLSI Technol. 2007:102-03.

- [15] Wong HSP. Phase Change Memory. Proc IEEE 2011;98(12):22 01-27.

- [17] Pirovano A, Lacaita AL, Benvenuti A, Pellizzer F, Bez R. Electronic Switching in Phase-Change Memories Agostino. IEEE Trans. Electron Devices 2004;51(3):452-59.

- [18] Sarwat SG. Materials Science and Engineering of Phase Change Random Access Memory. Mater. Sci. Technol 2017;33(16):1890-06.

- [19] Redaelli A, Pirovano A, Benvenuti, Lacaita AL. Threshold Switching and Phase Transition Numerical Models for Phase Change Memory Simulations. J Appl Phys 2008;103(11):1890-06.

- [20] Ielmini D. Threshold Switching Mechanism by High-Field Energy Gain in the Hopping Transport of Chalcogenide Glasses. Phys Rev B-Condens Matter 2008;78(3):1-8.

- [21] Ielmini D, Zhang Y. Analytical Model for Subthreshold Conduction and Threshold Switching in Chalcogenide-Based Memory Devices. J Appl Phys 2007 102(5).

- [22] Lenzlinger M, Snow EH. Fowler Nordheim Tunneling into Thermally Grown SiO<sub>2</sub>. J Appl Phys 1969;40(1):278-83.

- [23] Ielmini D, Lacaita AL, Mantegazza D. Recovery and Drift Dynamics of Resistance and Threshold Voltages in Phase-Change Memories Daniele. IEEE Trans Electron Devices 2007;54(2):308-15.

- [24] Buscemi F, Brunetti R, Piccinini E, Rudan M. A Model for Charge Transport in Amorphous GST Based on a Modified Variable-Range Hopping Process. Phase Transit 2007:182-89.

- [25] Kato T, Tanaka K. Electronic Properties of Amorphous and Crystalline Ge2Sb2Te5 Films. Jpn J Appl Phys Part 1 - Regul Pap Short Notes Rev Pap 2005;44(10):7340-44.

- [26] Sonoda K, Sakai A, Moniwa M, Ishikawa K, Tsuchiya O, Inoue Y. A Compact Model of Phase-Change Memory Based on Rate Equations of Crystallization and Amorphization. IEEE Trans Electron Devices 2008;55(7):1672-81.

- [27] Peng C, Cheng L, Mansuripur M. Experimental and Theoretical Investigations of Laser-Induced Crystallization and Amorphization in Phase-Change Optical Recording Media. J Appl Phys 1997;82(9):4183-91.

- [28] Senkader S, Wright CD. Models for Phase-Change of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> in Optical and Electrical Memory Devices. J Appl Phys 2004;95(2):504-11.

- [29] Xu N, Wang J, Deng Y, Lu Yang, Fu B, Choi W, et al. Multi-domain compact modeling for GeSbTe-based memory and selector devices and simulation for large-scale 3-D crosspoint memory arrays. In: IEDM Tech Dig 2016:7.7.1-4.

Donguk Kim received the B.S. degree in electrical engineering from

Journal Pre-proofs

**Jun Tae Jang** received the B.S. and M.S. degrees in electrical engineering from Kookmin University, Seoul, Korea, in 2016, where he is currently pursuing the Ph.D. degree with the School of Electrical Engineering.

**Dong Myong Kim** received the B.S. (magna cum laude) and M.S. degrees in electronics engineering from Seoul National University, Seoul, Korea, in 1986 and 1988, respectively, and the Ph.D. degree in electrical engineering from the University of Minnesota, Twin Cities, MN, USA, in 1993.

He is currently a Professor the School of Electrical Engineering, Kookmin University, Seoul, since 1993.

**Sung-Jin Choi** received the M.S. and Ph.D. degrees in electrical engineering from Korea Advanced Institute of Science and Technology, Daejeon, Korea, in 2012.

He is currently an Associate Professor with the School of Electrical Engineering, Kookmin University, Seoul, Korea.

**Hyun-Sun Mo** received the B.S, M.S. and Ph.D. degrees in electrical engineering from Kookmin University, Seoul, Korea, in 1993, 2011, and 2014, respectively.

She is currently a Professor the School of Electrical Engineering, Kookmin University, Seoul, since 2011.

**Dae Hwan Kim** received the B.S., M.S., and Ph.D. degrees in electrical engineering from Seoul National University, Seoul, Korea, in 1996, 1998, and 2002, respectively.

He is currently a Professor with the School of Electrical Engineering, Kookmin University, Seoul, Korea. His current research interests include nanoCMOS, oxide and organic thin-film transistors, biosensors, and neuromorphic devices.

# Journal Pre-proofs

Jun Tae Jang

Dong Myong Kim

Sung-Jin Choi

Hyun-Sun Mo

Dae Hwan Kim

# Journal Pre-proofs

# Highlight

- ✓ We proposed a physics-based compact model for phase-change random access memory (PcRAM).

- ✓ The ratio of vertical-to-lateral crystal growth rate (α) was incorporated into HSPICE via Verilog-A.

- ✓ The proposed model was verified by using the experimental results taken from the 256×256 cross-point (X-point) PcRAM cell array with the Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> 2z-nm technology node.

- ✓ Furthermore, we found that the SET pulse-dependent abrupt/gradual change of PcRAM resistance is sensitive to  $\alpha$ .