# Pulse Dependent Threshold Voltage Variation of the Ovonic Threshold Switch in Cross-Point Memory

Sanghyun Ban, Hyejung Choi<sup>®</sup>, Wootae Lee, Seokman Hong, Hwanjun Zang, Beomseok Lee, Myoungsub Kim, Seungyun Lee, Hyungdong Lee, and Taehoon Kim<sup>®</sup>, *Senior Member, IEEE*

Abstract—We report the pulse dependent threshold voltage  $(V_t)$  variation of the Ovonic Threshold Switch (OTS) and its effect on the read window margin (RWM) in Cross-Point Memory (XPM). We found that OTS  $V_t$  varies by the height and width of the write-current pulse. The varied V<sub>t</sub> is persistently maintained even after 2E4 cycling of the write pulse, which means that the phenomenon is not a temporary one, but a type of memory effect in OTS itself. Therefore, it would affect the overall  $V_t$  window  $(\Delta V_t)$  of XPM by changing the Set  $V_t$   $(V_{t\_Set})$  and Reset  $V_t$  ( $V_{t \text{ Reset}}$ ) when combined with either phase-change memory (PCM) or resistive memory (RM). High-resolution transmission electron microscopy (HRTEM) and fast Fourier transform (FFT) images have proved that this phenomenon is not caused by the phase change of the OTS. Instead, a sub-threshold analysis extracted from the Poole-Frenkel model suggests that the phenomenon is associated with the variation of the amorphous network either by changes in the atomic bonding configuration or trap density.

Index Terms—Ovonic threshold switch, selector, cross-point memory, phase-change memory, resistive memory,  $V_t$  instability, trap density, Poole-Frenkel.

## I. INTRODUCTION

ROSS-POINT type memory is recognized as the most ideal device structure for the next generation of high density memory [1]–[4]. It also showed very promising performance as a storage class memory (SCM) [2]. The simple structure of one-selector and one-memory (1S1M) of XPM can be easily fabricated with a self-aligned etch scheme, which will cut down the total number of photo mask steps and process steps to reduce the cost per bit [2]. The key technology of XPM is the selector technology, which enables the operation of XPM and decides the overall memory performance.

Among many candidates for two-terminal selector materials, OTS has been considered as the most promising one [5]–[7]. It shows extremely low sneak-current ( $I_{sneak}$ ), high on-current, and adjustable  $V_t$  by thickness modulation, which provides the adaptability for different memories of different  $\Delta V_t$  [8]. The

Manuscript received January 7, 2020; accepted January 16, 2020. Date of publication January 28, 2020; date of current version February 25, 2020. The review of this letter was arranged by Editor A. Chin. (Corresponding author: Taehoon Kim.)

The authors are with SK Hynix Inc., Icheon-si 17336, South Korea (e-mail: taehoon12.kim@sk.com).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2020.2969962

traditional OTS parameter for XPM is  $I_{sneak}$ , which enables high density array and reduces power consumption. A recent report also emphasized the importance of  $V_t$  instabilities such as random telegraph noise (RTN) and drift [2].

In this paper, we report another instability factor of the OTS called pulse dependent threshold variation (PDTV). We found that the OTS  $V_t$  systematically changes with write-current pulse conditions such as pulse height (PH) and pulse width (PW). The  $V_t$  change is stably maintained even after the 2E4 cycle and with different measurement temperatures. The result indicates that the variation is not a temporary one, but a type of memory effect on OTS itself. Therefore, the phenomenon will affect RWM during the overall write cycle. HRTEM and FFT images indicate that the  $V_t$  variation is not caused by the phase change of the OTS. Instead, the fit result of the Poole-Frenkel model implies that it is associated with the change of the bonding states of the amorphous network.

# II. EXPERIMENT

We fabricated cross-point arrays of the OTS with 2z nm technology by using the self-aligned etch scheme as in ref.2. The resulting pillar structure is formed between two crossing metal lines called the word line (WL) and the bit line (BL) and is composed of the OTS alloy and two electrodes at the top and bottom of the OTS, i.e. (BL/TE/OTS/BE/WL). The OTS (Ge-As-Se) alloy and carbon electrode was deposited by an RF and DC sputtering system respectively. Processing temperatures after OTS deposition were limited below the glass transition temperature  $(T_g)$  to prevent the OTS from causing pattern collapsing or characteristics change. However, the thermal budget is enough for the given  $T_g$ . The single device was patterned to a size of 20×20 nm, and an array consisted of a 2k×1k cross-point cell. Most of the electrical measurements were carried out at 55 °C except for Fig. 2 (d), which used the Nextest Magnum 2 memory test system. All measurements but Fig.4 were done by AC pulse, since it can exclude the drift effect by making a fast sweep and the  $V_t$  can be measured with a high resolution. Fig. 4 is measured by DC pulse, since it can provide good resolution in the subthreshold current region ( $< 1\mu A$ ), which cannot be done by AC measurement.

# III. RESULTS AND DISCUSSION

Fig.1 (a) shows the variation of OTS  $V_t$  after having different write-current ( $I_{WRT}$ ) pulses. In all measurements,

0741-3106 © 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

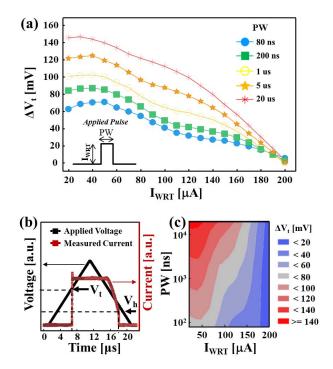

Fig. 1. (a) Memory behavior of the OTS-only cross-point structure. Threshold voltage of the OTS depends on the amplitude and pulse width of the write current applied to the OTS. The Y-axis,  $V_t$  is a  $V_t$  shift relative to the minimum  $V_t$ , i.e.  $V_t$  – minimum  $V_t$  (the minimum  $V_t$  is defined as the minimum  $V_t$  at  $I_{WRT} = 200~\mu$ A). (b) Applied voltage and measured current in the time axis.  $V_t$  is defined as the voltage when a current is turned on. (c) Contour plot of  $V_t$  as the function of the current amplitude and pulse width based on (a).

the delay time after write to read was fixed at 1  $\mu$ s to exclude the drift effect. The y-axis,  $\Delta V_t$  (=  $V_t - V_{t,min}$ ) is the variation of  $V_t$  after each write pulse condition with respect to the minimum  $V_t$  ( $V_{t,min}$ ) of 200  $\mu$ A write. The result shows that OTS  $V_t$  is fully dependent upon the write PH and PW. In all PWs,  $V_t$  decreases and converges into the  $V_{t,min}$  as  $I_{WRT}$  (PH) increases. For the same  $I_{WRT}$ , a shorter pulse decreases the  $V_t$  and the trend becomes larger as the  $I_{WRT}$  decreases. Overall,  $V_t$  dependence on PW and PH is shown in the contour plot in Fig. 1(b). The result indicates that when a memory component (PCM or RM) is added (e.g. 1S1M),  $\Delta V_t$  ( $V_{t\_Reset} - V_{t\_Set}$ ) will depend on the OTS as well as the memory component, since  $V_{t\_Set}$  is same with the  $V_{t\_OTS}$  and  $V_{t\_Reset}$  is the sum of  $V_{t\_OTS}$  and  $V_t$  of the memory component.

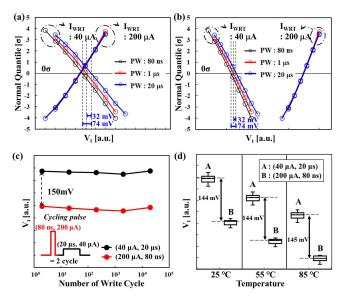

The  $V_t$  distributions of the 64k OTS-only cell arrays are shown in Fig. 2(a). Since there is no memory component,  $V_t$  represents  $V_{t\_OTS}$ . If there is no PDTV effect, the distribution groups of 200uA-I<sub>WRT</sub> (corresponding to Reset PH) and 40uA-I<sub>WRT</sub> (corresponding to Set PH) should cross at the zero sigma line; here, 200uA-I<sub>WRT</sub> group is just inverted to better show the  $\Delta V_t$  and RWM. However, due to the PDTV effect, the crossing point moves up and the  $V_t$  distribution shifts to the right as the PW becomes longer. This indicates a reduction of  $\Delta V_t$  by PDTV. Fig. 2(b) shows the expected  $V_t$  distributions when a memory component is added (e.g. 1S1M). The 200uA-I<sub>WRT</sub> group will shift to the right due to the memory component. Then, there will be a net difference in  $\Delta V_t$  (at median) or RWM (at low probability region) by the different  $V_t$   $S_{et}$  (PDTV). The PDTV phenomenon

Fig. 2. (a)  $V_t$  distributions of a 64k OTS-only (no memory component) cell array for different pulse conditions. The variation of  $V_{t\_Set} (= V_{t\_OTS})$  is due to the PDTV effect at low current regions, as shown in Fig. 1(a). Little variation of  $V_{t\_Reset}$  is also due to the little PDTV effect at high current region. (b) The expected  $V_t$  distributions and RWMs when a constant memory window is added to a memory component.  $V_{t\_Reset}$  has little variation since  $V_{t\_Reset}$  is the sum of the  $V_{t\_OTS}$  (no PDTV at high Reset current) and the constant  $V_{t\_memory}$ . (c) Cycling endurance characteristics of the PDTV effect from the median  $V_t$  of 64k OTS-only array. The  $V_t$  gap is formed by two write conditions of 20  $\mu$ s - 40  $\mu$ A and 80 ns - 200  $\mu$ A and is maintained even after 2E4. (d) A variation of PDTV at different temperature (25, 55, 85 °C). Note that the  $V_t$  gap by PDTV is maintained at all temperatures, while the  $V_t$  depends on the temperature.

was also found from other alloy systems (not shown here). Although both the magnitude and sign of the  $\Delta V_t$  were different in each alloy system, the PDTV phenomenon was very consistent and repeatable. Therefore, the PDTV effect should be considered as another instability factor of the OTS like RTN and drift, to change RWM.

In order to further investigate the consistency of the PDTV effect, a cycling endurance test was carried out. The high and short write pulse (200  $\mu$ A for 80 ns), and low and long write pulse (40  $\mu$ A for 20  $\mu$ s) were alternately applied as shown in the inset of Fig. 2(c). The result indicates that the  $V_t$  gap by PDTV remains even after the 2E4 cycling write pulses. The PDTV also remains the same between 25 °C and 85 °C as shown in Fig. 2(d). It shows that  $V_t$  decreases with an increase in temperature, but the gaps of  $V_t$  caused by the PDTV remain the same. Based on these results, we concluded that PDTV is not a transient phenomenon, affected by neither a temperature nor a write cycle stress.

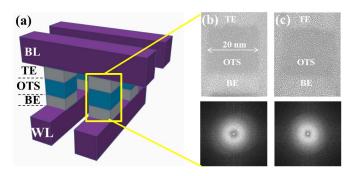

Since the phenomenon was so consistent, we performed a HRTEM and FFT pattern analysis to check whether these results are associated with the phase change phenomenon or not. Fig. 3 shows the HRTEM image and its FFT pattern after 200  $\mu$ A – 80 ns (a) and 40  $\mu$ A – 20  $\mu$ s (b) for minimum and maximum  $V_t$ , respectively. The results show that their atomic structure was still in an amorphous state, that is, the  $V_t$  change of the OTS was not related to the phase change phenomenon.

In the confined structure, since the stress from the current pulse cannot change the composition of the OTS alloy, the only

Fig. 3. (a) Cross-point array structure composed of the OTS and two electrodes. HRTEM (top) and FFT pattern (bottom) images of the OTS device: (b) OTS state after writing the cell with a high and short pulse ( $I_{WRT} = 200~\mu\text{A}$ , PW = 80 ns). (c) OTS state after writing the cell with a low and long pulse ( $I_{WRT} = 40~\mu\text{A}$ , PW = 20  $\mu\text{s}$ ).

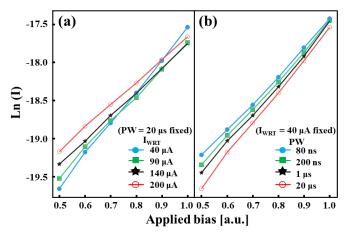

Fig. 4. Measured sub-threshold IV characteristics by DC after writing a cell with different programming conditions: (a) Increasing write currents  $I_{WRT}=40~\mu\text{A},\,90~\mu\text{A},\,140~\mu\text{A},\,\text{and}\,200~\mu\text{A}$  with a fixed PW  $=20~\mu\text{s}.$  (b) Increasing pulse widths PW=80 ns, 200 ns, 1  $\mu\text{s},\,\text{and}\,20~\mu\text{s}$  with a fixed  $I_{WRT}=40~\mu\text{A}.$

possible mechanism will be the change of either the bonding state or the defect density in the amorphous network. The best way to analyze such information is to use subthreshold IV characteristics. DC-IV was measured after various write pulses. Fig. 4(a) shows the sub-threshold IV characteristics after various PHs with a constant of 20  $\mu$ s PW, and Fig. 4(b) shows the characteristics after various PWs with a constant of 40  $\mu$ A PH. Obviously, sub-threshold IV slopes change systematically with different PH and PW. To extract the material's information, the IV curves are fit to the Poole-Frenkel model [10], which is

$$I = 2qAN_{T,tot}\frac{\Delta z}{\tau_0}e^{-(E_C - E_F)/kT}\sinh(\frac{qV_A}{kT}\frac{\Delta z}{2u_a}), \qquad (1)$$

where q is the elementary charge, A is the area of the device,  $N_{T,tot}$  is the integral of the trap distribution in the gap above the Fermi level  $(E_F)$ ,  $\Delta$  is the inter-trap distance,  $\tau_0$  is the characteristics attempt-to-escape time for the trapped electron,  $E_C - E_F$  is the activation energy  $(E_a)$ ,  $V_A$  is the applied bias, k is Boltzmann constant, T is the temperature, and  $u_a$  is the thickness of the amorphous chalcogenide. Two fitting parameters,  $E_a$  and  $\Delta$ , are obtained assuming  $\tau_0$  and  $N_{T,tot}$  as

### TABLE I

ACTIVATION ENERGIES ( $E_a=E_C-E_F$ ) AND TRAP DISTANCES ( $\Delta z$ ) EXTRACTED FROM THE SUB-THRESHOLD IV FITTING ANALYSIS IN FIG.4. THE TABLE SHOWS THE INFLUENCE OF (a) I<sub>WRT</sub> (WITH FIXED PW = 20  $\mu$ s) AND (b) PW (WITH FIXED I<sub>WRT</sub> = 40  $\mu$ A) ON  $E_a$  AND  $\Delta z$

| (a)                   |                                                          |            | <b>(b)</b> |                                                          |            |

|-----------------------|----------------------------------------------------------|------------|------------|----------------------------------------------------------|------------|

| I <sub>WRT</sub> (μA) | E <sub>a</sub> (E <sub>C</sub> -E <sub>F</sub> )<br>(eV) | Δz<br>(nm) | PW (ns)    | E <sub>a</sub> (E <sub>C</sub> -E <sub>F</sub> )<br>(eV) | Δz<br>(nm) |

| 40                    | 0.767                                                    | 4.29       | 80         | 0.706                                                    | 3.68       |

| 90                    | 0.707                                                    | 3.61       | 200        | 0.723                                                    | 3.86       |

| 140                   | 0.674                                                    | 3.25       | 1000       | 0.739                                                    | 4.02       |

| 200                   | 0.655                                                    | 3.07       | 20000      | 0.767                                                    | 4.29       |

|                       |                                                          |            |            |                                                          |            |

$(PW = 20 \mu s fixed)$

$(I_{WRT} = 40 \mu A \text{ fixed})$

$10^{-15}$ s and  $1/(\Delta)^3$ , respectively [3], [11]–[13]. The fit results are summarized in the Table I (a) and (b).

As the PH increases, both  $\Delta$  and  $E_a$  decrease. Also, the increasing PW increases both  $\Delta$  and  $E_C - E_F$ . It is interesting to note that the dependence of  $E_a$  and  $\Delta$  on the condition of the write pulse is consistent with the trend of  $V_t$  change in Fig. 1(a) and (b). The results are in good agreement with the mobility edge theory [14] in which  $V_t$  is a direct function of mobility edge variation ( $E_C - E_F$ ), and the cause is associated with the trap density (1/ $\Delta$ ) of the amorphous chalcogenide. In other words, changing pulse conditions seems to change the bonding state of the amorphous network, either by reconfiguring the atomic bonding states or by charging the traps. These results indicate there could be some different aspects for each OTS alloy whose amorphous structure is different.

# IV. CONCLUSION

In this study, the PDTV phenomenon of the ternary OTS device was investigated. OTS  $V_t$  decreases with increasing PH, while it increases with a longer PW. The results indicate that, when the OTS is combined with a memory component such as a PCM or a RM for a 1S1M device, it will affect the overall  $\Delta V_t$  and RWM of a cell array. Particularly for PCM, the effect will be more obvious, due to the Reset pulse (short PW and high PH) and the Set pulse (long PW and low PH). The phenomenon was maintained even after the 2E4 cycle and in the temperature range between 25 to 85 °C, which means that the phenomenon is not a temporary one, but a kind of memory effect of OTS itself. HRTEM and FFT analyses confirmed that the behavior is not due to the phase change. Sub-threshold IV analysis of OTS implies changes caused by different pulse conditions to the mobility edge  $(E_C - E_F)$ and the trap density  $(1/\Delta)$ . At this moment, we don't fully understand how the different pulse conditions affect the atomic bonding states or traps, and result in the PDTV phenomenon. Unfortunately, it is not possible to characterize the bonding states or configurations in a nano-scale area with current characterization technology. More studies will be required in terms of physics in the future.

In conclusion, when an OTS material is developed for XPM, the PDTV effect should be considered as one of the  $V_t$  instability factors such as RTN and drift.

### REFERENCES

- D. Kau, S. Tang, I. V. Karpov, R. Dodge, B. Klehn, J. A. Kalb, J. Strand, A. Diaz, N. Leung, J. Wu, S. Lee, T. Langtry, K.-W. Chang, C. Papagianni, J. Lee, J. Hirst, S. Erra, E. Flores, N. Righos, H. Castro, and G. Spadini, "A stackable cross point phase change memory," in *IEDM Tech. Dig.*, Dec. 2009, pp. 27.1.1–27.1.4, doi: 10.1109/ IEDM.2009.5424263.

- [2] T. Kim, H. Choi, M. Kim, J. Yi, D. Kim, S. Cho, H. Lee, C. Hwang, E.-R. Hwang, J. Song, S. Chae, Y. Chun, and J.-K. Kim, "Highperformance, cost-effective 2z nm two-deck cross-point memory integrated by self-align scheme for 128 Gb SCM," in *IEDM Tech. Dig.*, Dec. 2018, pp. 37.1.1–37.1.4.

- [3] S. Kim, Y.-B. Kim, K. M. Kim, S.-J. Kim, S. R. Lee, M. Chang, E. Cho, M.-J. Lee, D. Lee, C. J. Kim, U.-I. Chung, and I.-K. Yoo, "Performance of threshold switching in chalcogenide glass for 3D stackable selector," in *symp. VLSI Tech. Dig.*, Jun. 2013, pp. T240–T241.

- [4] S. G. Kim, J. C. Lee, T. J. Ha, J. H. Lee, J. Y. Lee, Y. T. Park, K. W. Kim, W. K. Ju, Y. S. Ko, H. M. Hwang, B. M. Lee, J. Y. Moon, W. Y. Park, B. G. Gyun, B.-K. Lee, D. Yim, and S.-J. Hong, "Breakthrough of selector technology for cross-point 25-nm ReRAM," in *IEDM Tech. Dig.*, Dec. 2017, pp. 4.1.1–4.1.4, doi: 10.1109/IEDM.2017.8268309.

- [5] S. Clima, B. Govoreanu, K. Opsomer, A. Velea, N. S. Avasarala, W. Devulder, I. Shlyakhov, G. L. Donadio, T. Witters, S. Kundu, L. Goux, V. Afanasiev, G. S. Kar, and G. Pourtois, "Atomistic investigation of the electronic structure, thermal properties and conduction defects in Ge-rich Ge<sub>x</sub>Se<sub>1-x</sub> materials for selector applications," in *IEDM Tech. Dig.*, Dec. 2017, pp. 2.1.1–2.1.4, doi: 10.1109/IEDM.2017.8268323.

- [6] M. Alayan, E. Vianello, G. Navarro, C. Carabasse, S. L. Barbera, A. Verdy, N. Castellani, A. Levisse, G. Molas, L. Grenouillet, T. Magis, F. Aussenac, M. Bernard, B. Desalvo, J. M. Portal, and E. Nowak, "Indepth investigation of programming and reading operations in RRAM cells integrated with Ovonic Threshold Switching (OTS) selectors," in *IEDM Tech. Dig.*, Dec. 2017, pp. 2.3.1–2.3.4, doi: 10.1109/IEDM.2017. 8268311.

- [7] H. Y. Cheng, W. C. Chien, I. T. Kuo, E. K. Lai, Y. Zhu, J. L. Jordan-Sweet, A. Ray, F. Carta, F. M. Lee, P. H. Tseng, M. H. Lee, Y. Y. Lin, W. Kim, R. Bruce, C. W. Yeh, C. H. Yang, M. Brightsky, and H. L. Lung, "An ultra high endurance and thermally stable selector based on TeAsGeSiSe chalcogenides compatible with BEOL IC Integration for cross-point PCM," in *IEDM Tech. Dig.*, Dec. 2017, pp. 2.2.1–2.2.4, doi: 10.1109/IEDM.2017.8268310.

- [8] H.-W. Ahn, D. S. Jeong, B.-K. Cheong, S.-D. Kim, S.-Y. Shin, H. Lim, D. Kim, and S. Lee, "A study on the scalability of a selector device using threshold switching in Pt/GeSe/Pt," ECS Solid State Lett., vol. 2, no. 9, pp. N31–N33, Jul. 2013, doi: 10.1149/2.011309ssl.

- [9] H. Y. Cheng, W. C. Chien, I. T. Kuo, C. W. Yeh, L. Gignac, W. Kim, E. K. Lai, Y. F. Lin, R. L. Bruce, C. Lavoie, C. Cheng, A. Ray, F. M. Lee, F. Carta, C. H. Yang, M. H. Lee, H. Y. Ho, M. Brightsky, and H. L. Lung, "Ultra-high endurance and low I<sub>OFF</sub> selector based on AsSeGe chalcogenides for wide memory window 3D stackable crosspoint memory," in *IEDM Tech. Dig.*, Dec. 2018, pp. 37.3.1–37.3.4.

- [10] D. Ielmini and Y. Zhang, "Analytical model for subthreshold conduction and threshold switching in chalcogenide-based memory devices," J. Appl. Phys., vol. 102, no. 5, Sep. 2007, Art. no. 054517, doi: 10. 1063/1.2773688.

- [11] Y. Koo and H. Hwang, "Zn<sub>1-x</sub>Te<sub>x</sub> Ovonic threshold switching device performance and its correlation to material parameters," Sci. Rep., vol. 8, Aug. 2018, Art. no. 11822, doi: 10.1038/s41598-018-30207-0.

- [12] D. Ielmini, "Threshold switching mechanism by high-field energy gain in the hopping transport of chalcogenide glasses," *Phys. Rev. B, Condens. Matter*, vol. 78, Jul. 2008, Art. no. 035308.

- [13] T. Gao, J. Feng, H. Ma, and X. Zhu, "The ovonic threshold switching characteristics in Si<sub>x</sub>Te<sub>1-x</sub> based selector devices," *Appl. Phys. A, Solids* Surf., vol. 124, p. 734, Oct. 2018, doi: 10.1007/s00339-018-2153-9.

- [14] D. Ielmini, D. Sharma, S. Lavizzari, and A. L. Lacaita, "Reliability impact of chalcogenide-structure relaxation in phase-change memory (PCM) cells—Part I: Experimental study," *IEEE Trans. Electron Devices*, vol. 56, no. 5, pp. 1070–1077, May 2009.