# NVIDIA GV100-400-A1 TSMC 12FFN FinFET Process

**Advanced CMOS Essentials**

All copyright, proprietary and intellectual property rights related to this report reside with TechInsights, except as, and only to the extent, expressly agreed otherwise, in writing.

The report is provided under license, exclusively for the use of the organization to which TechInsights has delivered the report and may only be used in accordance with the terms of the license set out in the agreement between TechInsights and that organization, or with the other express, prior, written consent of TechInsights.

If distribution of the report is permitted, TechInsights accreditation, including watermarks must remain attached.

The information contained in this report may describe technical innovations, which are the subject of patents held by third parties. The disclosure by Techlnsights of any such information is in no form whatsoever an inducement to infringe any patent. Techlnsights assumes no liability for patent infringement arising from the use of the information contained in this report.

ACE-1801-801

94359OWLG

Published: March 26, 2018

#### **Overview**

This is an Advanced CMOS Essentials (ACE) Summary document, provided as a companion deliverable for Advanced CMOS Essentials projects. The complete Advanced CMOS Essentials deliverable includes:

- Concise analyst's summary of critical device metrics, TEM-EDS results, and salient features supported by the following image folders:

- Downstream product teardown

- Package photographs and X-rays, top metal and poly die photographs

- SEM bevel

- SRAM

- Logic

- SEM cross section of the general device structure, metals, dielectrics, and detail of the FEOL structures

- TEM bevel

- SRAM

- Logic

- TEM cross section

- Orthogonal to transistor fins

- Orthogonal to transistor gates

### **Observed Critical Dimensions**

| Report code                                      | ACE-1801-801                                             |  |

|--------------------------------------------------|----------------------------------------------------------|--|

| Package dimensions                               | 55 mm x 55 mm x 3.8 mm thick                             |  |

| Manufacturer, part number, downstream            | NVIDIA, GV100-400-A1, NVIDIA Titan V graphics card       |  |

| Wafer size, foundry, process type                | 300 mm, TSMC, 12FFN finFET high-k metal gate (HKMG) CMOS |  |

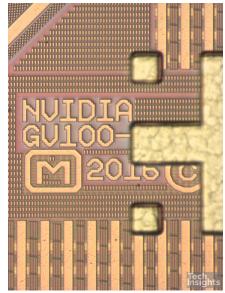

| Die markings                                     | NVIDIA<br>GV100-<br>(M) 2016 ©                           |  |

| Die size (from die seal)                         | 25.52 mm x 31.97 mm (815.87 mm <sup>2</sup> )            |  |

| Die size (actual)                                | 25.60 mm x 32.23 mm (825.09 mm <sup>2</sup> )            |  |

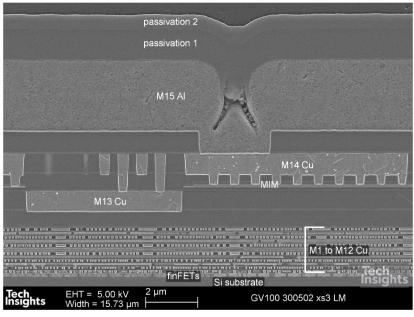

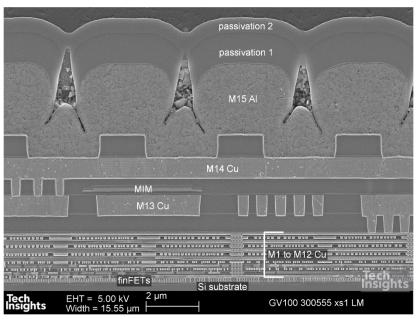

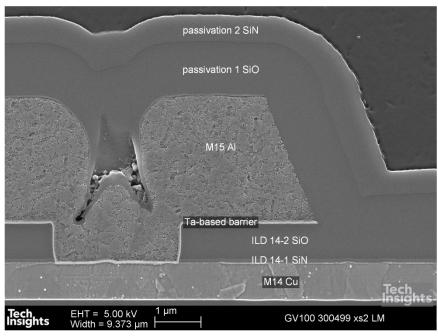

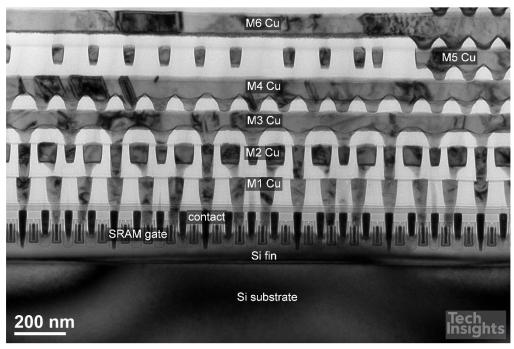

| Number, type of metals                           | 15 (14 copper (Cu), 1 aluminum (Al))                     |  |

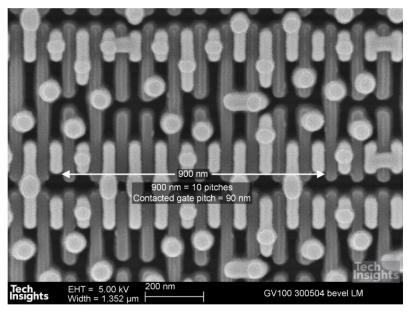

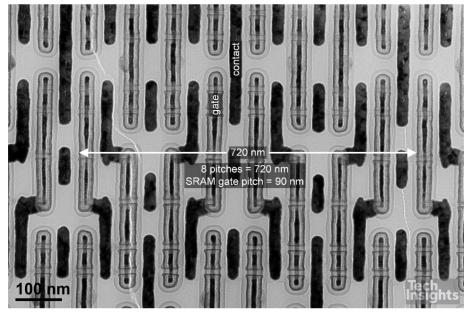

| Contacted logic gate pitch                       | 90 nm                                                    |  |

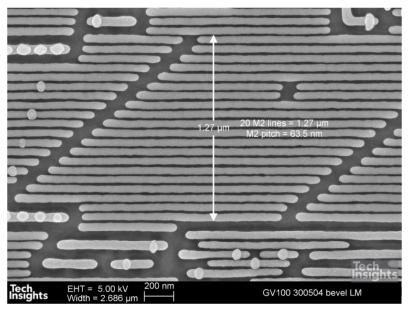

| Minimum metal pitch                              | 64 nm                                                    |  |

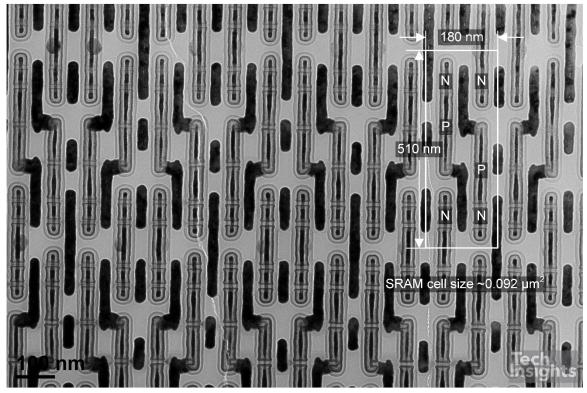

| SRAM cell size                                   | 0.51 μm x 0.18 μm (0.092 μm²)                            |  |

| Technology generation                            | 16 nm                                                    |  |

| Feature measured to determine process generation | Metal 2 pitch                                            |  |

#### **Salient Features**

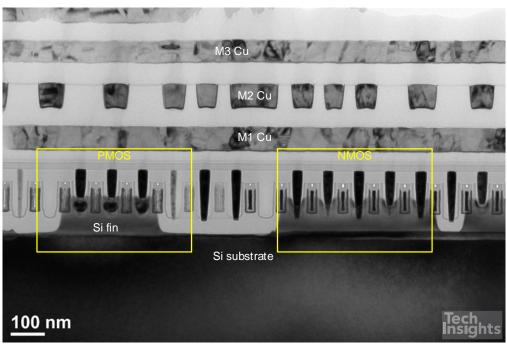

- The NVIDIA GV100-400-A1 was built on 300 mm wafers using TSMC's 12FFN finFET HKMG CMOS process

- Despite the node naming of "12FFN", the technology appears to only be a back end of line (BEOL) update of the previously analyzed TSMC 16FF+ process

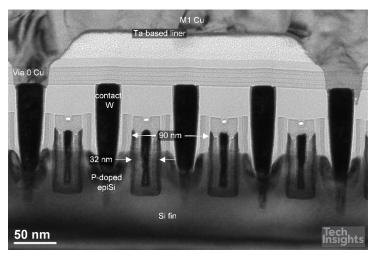

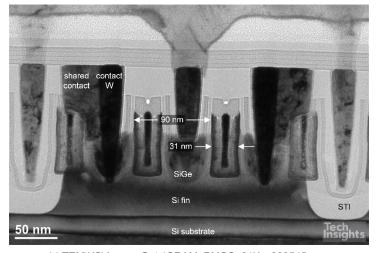

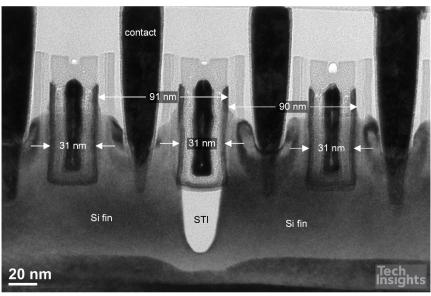

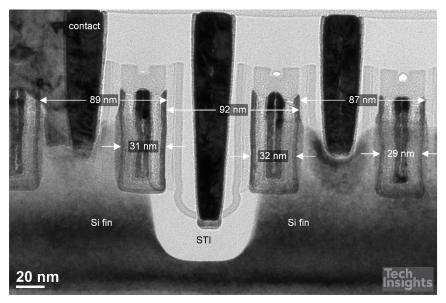

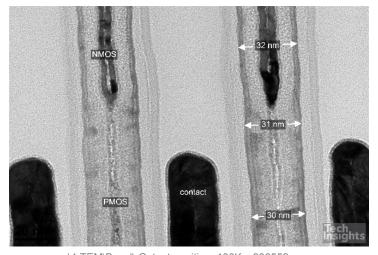

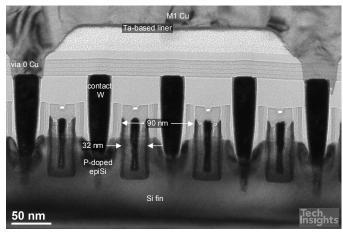

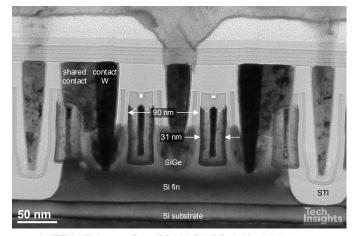

- The minimum gate pitch observed in both the standard logic array and memory array is ~90 nm

- The minimum gate length observed is ~25 nm

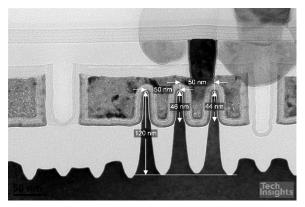

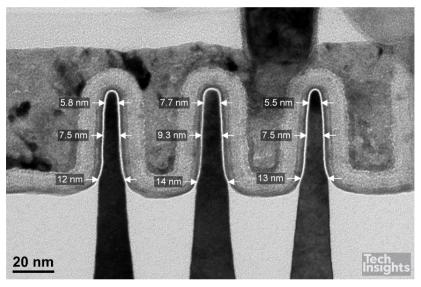

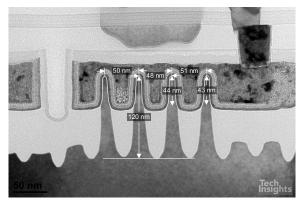

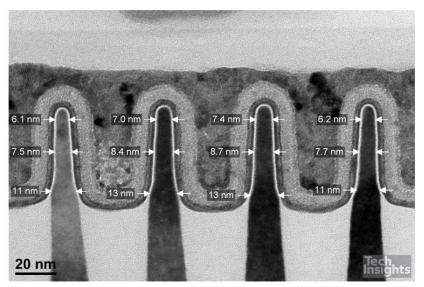

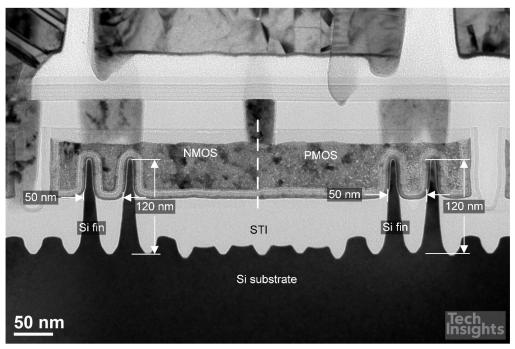

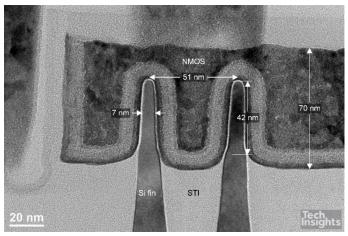

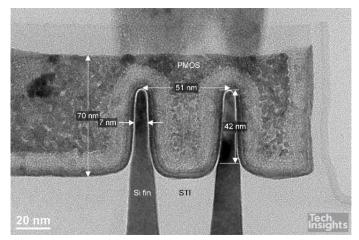

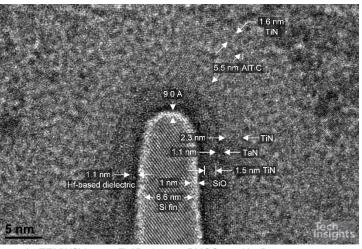

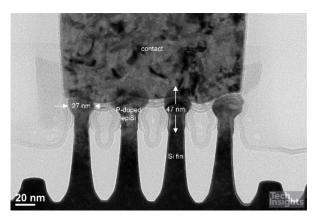

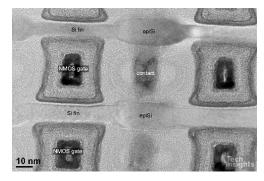

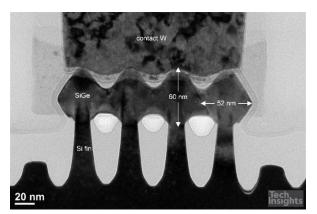

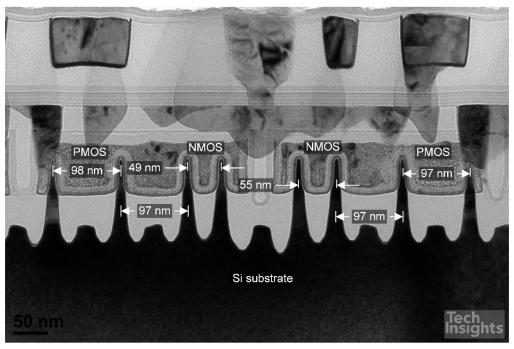

- The logic fin height is ~42 nm and the fin pitch is ~48 nm. SRAM fins have a variable pitch

- The fin width of ~7 nm, measured at the center of the fin height, is the same for both NMOS and PMOS

- The logic gate height is ~70 nm

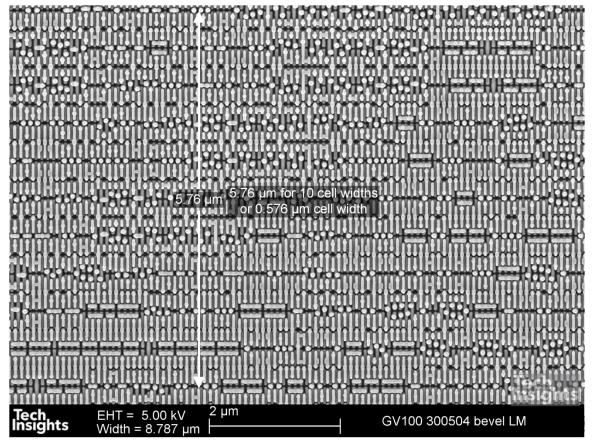

- The standard cell width is ~576 nm (equivalent to nine tracks)

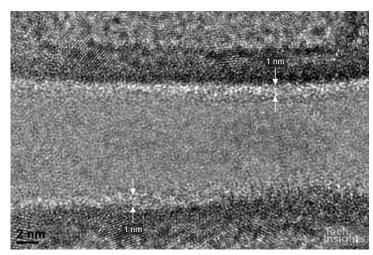

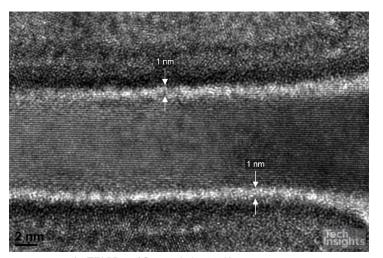

- The minimum metal (M2) pitch observed is ~64 nm

- The minimum 6-transistor (6T) SRAM cell size is ~0.092 μm<sup>2</sup>

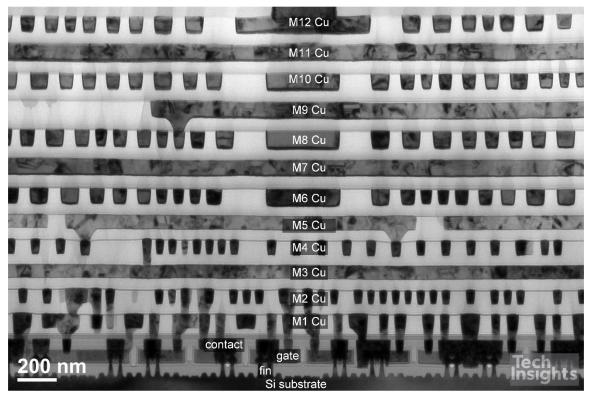

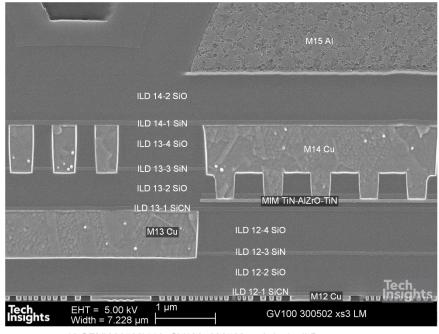

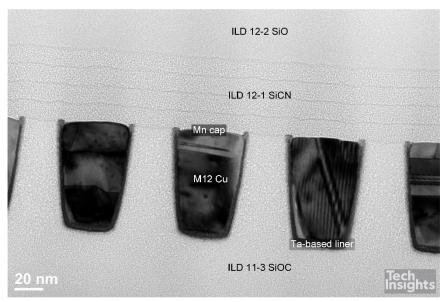

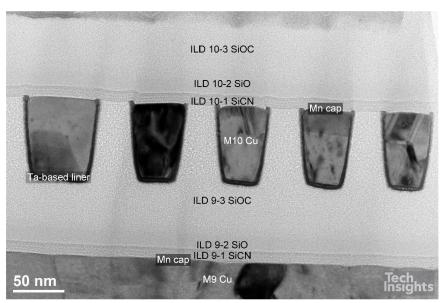

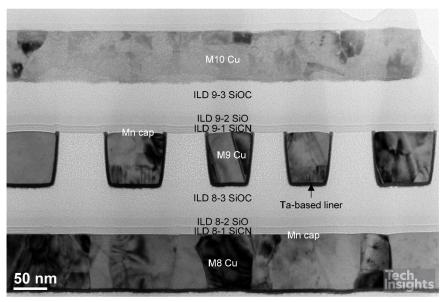

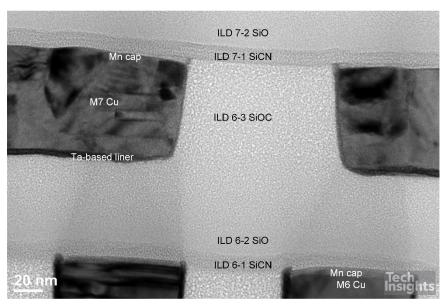

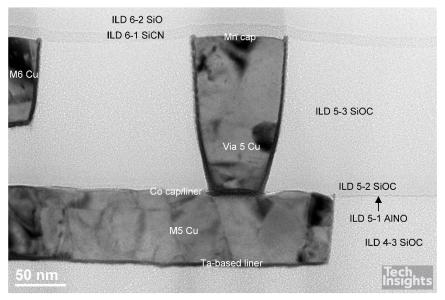

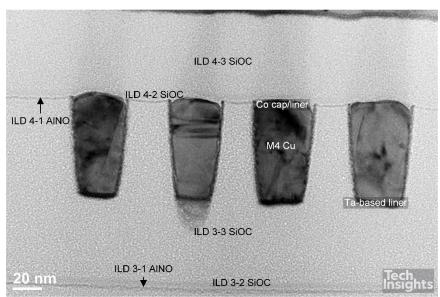

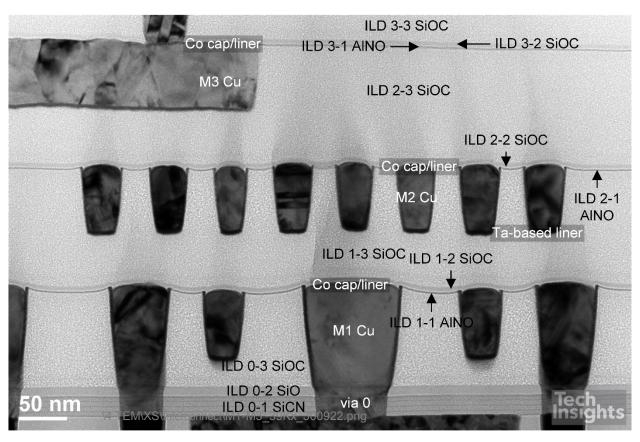

- Metal 1 to metal 5 consist of Cu with a cobalt (Co) cap and liner, metal 6 to metal 12 consist of a Cu with a manganese (Mn) cap, and metal 13 to metal 14 consist of Cu. All the Cu metals have Ta-based liners

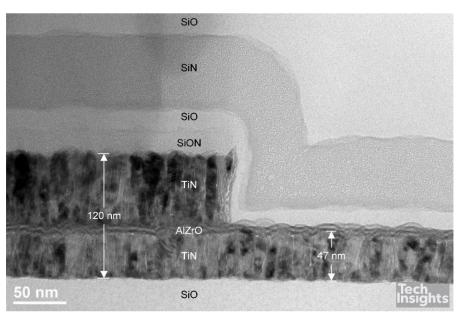

- A metal-insulator-metal (MIM) capacitor lies between metal 13 and metal 14 and consists of titanium nitride (TiN)/aluminum zirconium oxide (AIZrO)/TiN stack

- An etch stop layer (AINO)/(SiOC) was used over metal 1 through metal 5

- An etch stop layer (SiCN)/(SiO) was used over metal 6 through metal 12

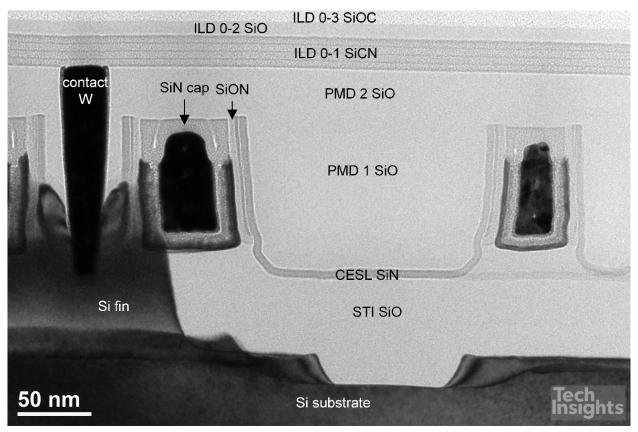

- Similar to TSMC's 16FF+ process, the minimum shallow trench isolation (STI) width is reduced to

~30 nm to enable a dummy poly single diffusion break (SDB) between standard cells

#### **Salient Features**

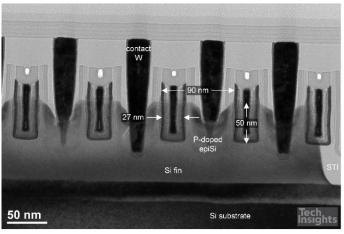

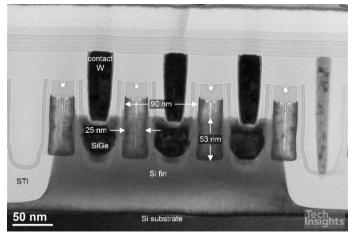

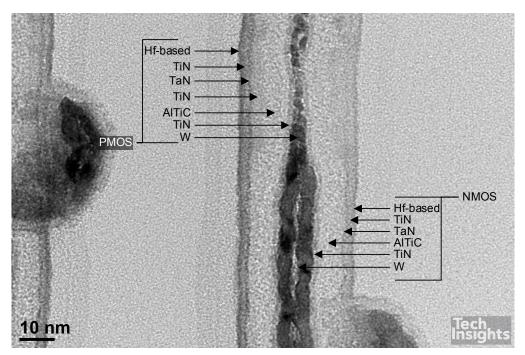

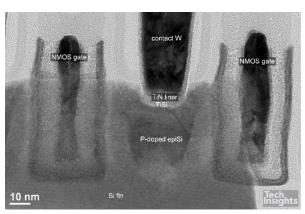

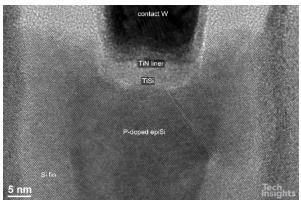

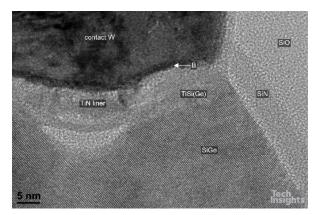

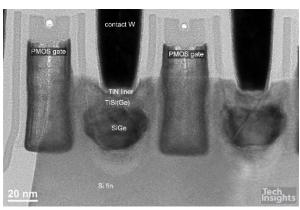

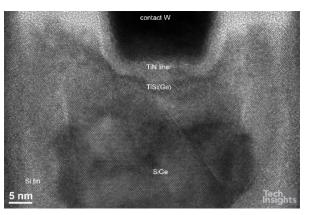

- Source and drain PMOS areas consist of silicon germanium (SiGe) epi, while those of NMOS

areas consist of phosphorus (P)-doped Si epi. NMOS epi are unmerged and heavily gouged by the

contact etch, while PMOS epi are merged and slightly gouged by the contact etch

- The end fins of multiple (more than two) fins are narrower and more tapered than the middle fin(s), indicating that there is no improvement from previous 16 nm process variants

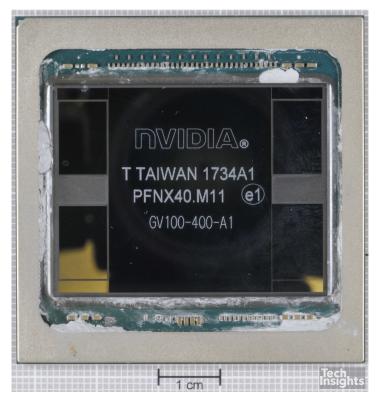

# **NVIDIA GV100-400-A1 Package**

\2 Package\_and\_Die\_Photographs\_X-rays\_and\_Optical\ GV100-400-A1\_Pkg\_Top\_299982\_Cropped.png

Top

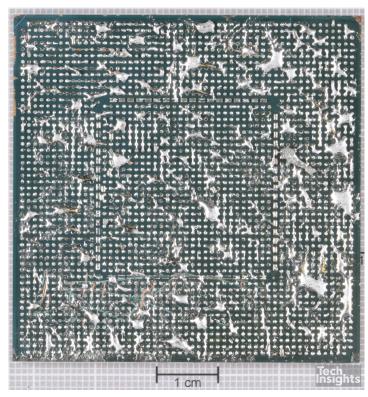

\2 Package\_and\_Die\_Photographs\_X-rays\_and\_Optical\ GV100-400-A1\_Pkg\_Bot\_299982\_Cropped.png

**Bottom**

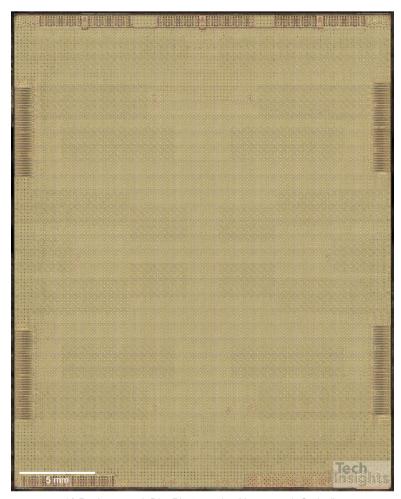

# **NVIDIA GV100-400-A1 Die Photograph and Die Markings**

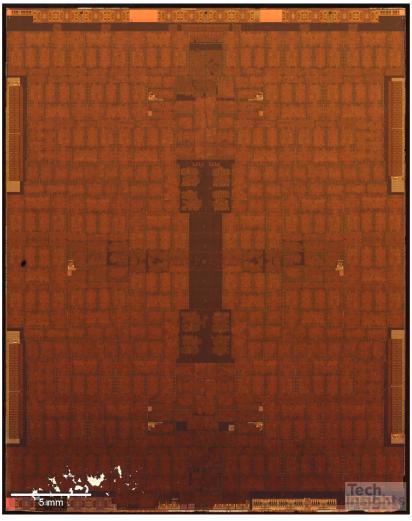

\2 Package\_and\_Die\_Photographs\_X-rays\_and\_Optical\ GV100-400-A1\_GV100\_300084\_Oriented.png

#### Die Photograph

\2 Package\_and\_Die\_Photographs\_X-rays\_and\_Optical\ GV100-400-A1\_GV100\_300084\_DieMrk-50XRotated.png

**Die Markings**

# **NVIDIA GV100-400-A1 Substrate Die Photograph**

\2 Package\_and\_Die\_Photographs\_X-rays\_and\_Optical\ GV100-400-A1\_GV100\_300084\_BPoly.png

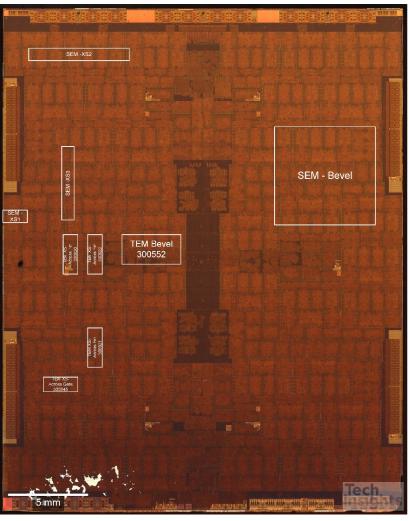

### **Sample Locations – TEM and SEM**

\2 Package\_and\_Die\_Photographs\_X-rays\_and\_Optical\ GV100-400-A1\_GV100\_300084\_BPoly.png

■ The logic contacted gate pitch is ~90 nm

\4 TEM\Bevel\Bottom gate\_17,5Kx\_B\_300552.png

\3 SEM\300504\_bevel\406\_GV100\_300504\_bevel\_gates.png

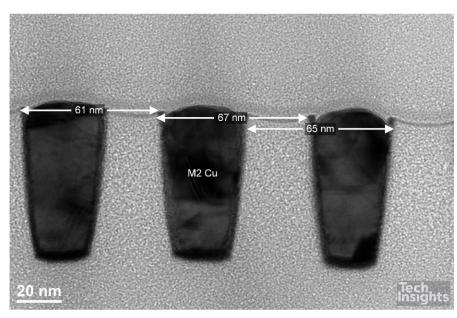

■ The minimum metal pitch of ~64 nm is located on the metal 2 level

\3 SEM\300504\_bevel\227\_GV100\_300504\_bevel\_M2.png

\4 TEM\XS\Interconnect\M2\_130Kx\_B\_300922.png

■ The standard cell width is ~576 nm (equivalent to nine tracks)

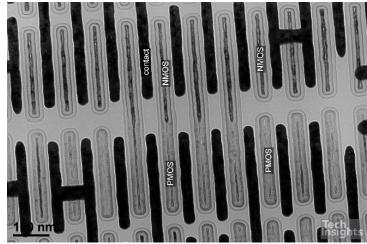

■ The SRAM contacted gate pitch is ~90 nm

\4 TEM\Bevel\SRAM\_26,5Kx\_300552.png

\4 TEM\XS\Across Gate\SRAM\_NMOS\_64Kx\_300545.png

\4 TEM\XS\Across Gate\SRAM\_PMOS\_64Kx\_300545.png

The 6T SRAM cell size is ~0.092 µm²

\4 TEM\Bevel\SRAM\_17,5Kx\_B\_300552.png

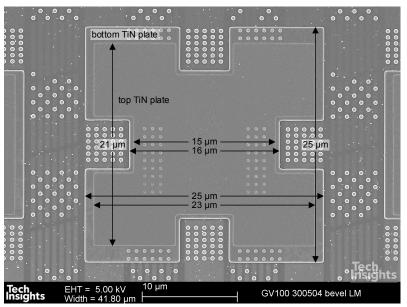

#### **General Structure – SEM**

\3 SEM\300502\553\_GV100\_300502\_xs3\_logic\_overview.png

#### **Across the Fins**

\3 SEM\300555\_XS\_across gate\

010\_GV100\_300555\_xs1\_overview\_all\_layers.png

#### **Across the Gates**

### **General Structure – Lower Metals – TEM**

\4 TEM\XS\Interconnect\M1-M12\_8,9Kx\_300922.png

\3 SEM\300499\_XS\_across\_gate\ 414\_GV100\_300499\_xs2\_logic\_passivation.png

Metal 15

\3 SEM\300502\558\_GV100\_300502\_xs3\_logic\_ILD\_upper.png

Metal 13 and Metal 14

### **Dielectrics – Materials Analysis – MIM Capacitor**

\3 SEM\300504\_bevel\372\_GV100\_300504\_bevel\_MIMS.png

\4 TEM\XS\Interconnect\MIM\_64Kx\_B\_300922.png

\4 TEM\XS\Interconnect\M12\_88Kx\_300921.png

Metal 12

\4 TEM\XS\Interconnect\M10\_64Kx\_300922.png

Metal 10

\4 TEM\XS\Interconnect\M9\_39Kx\_300545.png

Metal 9

\4 TEM\XS\Interconnect\M7\_88Kx\_300921.png

Metal 7

\4 TEM\XS\Interconnect\M5-Via5-M6\_64Kx\_300922.png

Metal 5 and Metal 6

\4 TEM\XS\Interconnect\M4\_88Kx\_B\_300922.png

Metal 4

Metal 1 to Metal 3

\4 TEM\XS\Across Gate\SRAM\_PMOS\_edge\_64Kx\_300545.png

**PMD**

### **Logic – Single and Double Diffusion Breaks**

\4 TEM\XS\Across Gate\NMOS\_singlediffbreak\_88Kx\_300545.png **SDB**

\4 TEM\XS\Across Gate\Dummy contact\_88Kx\_300545.png

**DDB**

### **Logic – Three and Four Fins**

\4 TEM\XS\Across Fin\Three fins\_N\_130Kx\_300920.png

\4 TEM\XS\Across Fin\Four fins\_N\_64Kx\_300920.png

Four Fins

\4 TEM\XS\Across Fin\Four fins\_N\_130Kx\_300920.png

### **Logic PMOS and NMOS – Across the Gate**

\4 TEM\XS\Across Gate\PMOS-NMOS2\_17,5Kx\_300545.png

\4 TEM\XS\Across Gate\NMOS\_2\_64Kx\_300545.png

#### **NMOS**

\4 TEM\XS\Across Gate\PMOS\_64Kx\_300545.png

# Logic PMOS and NMOS – Across the Fins

\4 TEM\XS\Across Fin\N-PMOS\_2\_39Kx\_300922.png

### **Transition Between PMOS and NMOS**

\4 TEM\Bevel1\ Transition\_180Kx\_300552.png

\4 TEM\Bevel\Gate\_transition\_26,5Kx\_300552.png

#### **NMOS**

\4 TEM\Bevel\ Gate\_transition\_130Kx\_300552.png

#### **Transition Between PMOS and NMOS**

$\verb|\A TEM\XS\A cross Gate - n_180Kx_300545_overlap_cropped.png| \\$

\4 TEM\XS\Across Fin\ N-PMOS\_2\_410Kx\_300922.png

#### Source and Drain - NMOS and PMOS

$\verb|\A TEM\XS\Across Fin\Periphery\_NMOS\_530Kx\_300920.png| \\$

#### **NMOS Cross Section**

\4 TEM\Bevel\Sourcedrain\_epiSi\_800Kx\_300552.png

**NMOS Planar**

$\verb|\A TEM\XS\Across Fin\Periphery\_PMOS\_530Kx\_B\_300920.png| \\$

#### **PMOS Cross Section**

$\verb|\ATEM\Bevel| Sourced rain_800Kx_300552.png| \\$

**PMOS Planar**

#### **Source and Drain - NMOS**

\4 TEM\XS\Across Fin\SD epiSi\_88Kx\_300922.png

\4 TEM\XS\Across Fin\EpiSi\_410Kx\_300920.png

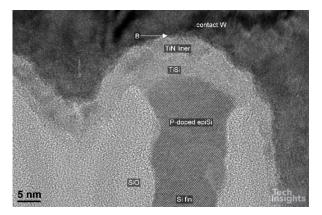

\4 TEM\XS\Across Gate\Contact\_180Kx\_300545.png

\4 TEM\XS\Across Gate\Contact\_410Kx\_300545.png

\4 TEM\Bevel\

Sourcedrain\_epiSi\_180Kx\_B\_300552.png

### **Source and Drain - PMOS**

\4 TEM\XS\Across Fin\SD SiGe\_88Kx\_300922.png

\4 TEM\XS\Across Fin\EpiSiGe\_410Kx\_300920.png

\4 TEM\XS\Across Gate\P-contact\_180Kx\_300545.png

\4 TEM\XS\Across Gate\P-contact\_410Kx\_300545.png

\4 TEM\Bevel\

Sourcedrain\_180Kx\_B\_300552.png

#### **SRAM PMOS and NMOS – Across the Gate**

\4 TEM\XS\Across Gate\SRAM\_13,5Kx\_300545.png

\4 TEM\XS\Across Gate\SRAM\_NMOS\_64Kx\_300545.png **NMOS**

\4 TEM\XS\Across Gate\SRAM\_PMOS\_64Kx\_300545.png

### **SRAM PMOS and NMOS – Across the Fins**

\4 TEM\XS\Across Fin\SRAM\_35Kx\_B\_300920.png

\4 TEM\XS\Across Fin\SRAM-NMOS\_360Kx\_300920.png

#### **PMOS**

\4 TEM\XS\Across Fin\SRAM-PMOS\_360Kx\_300920.png

**NMOS**

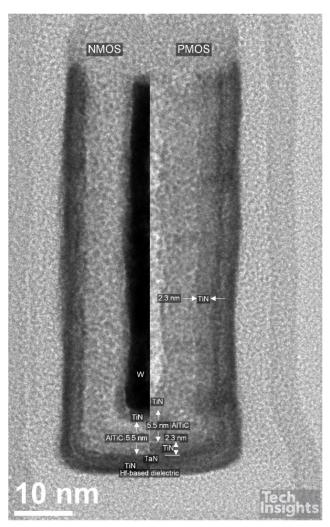

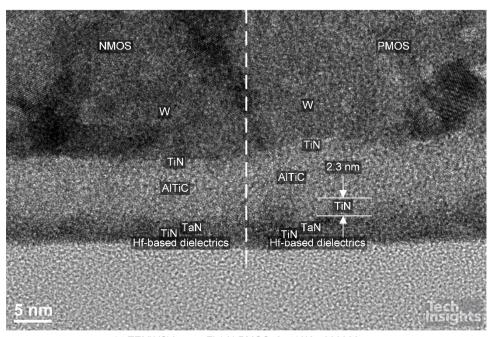

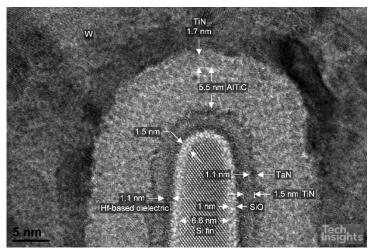

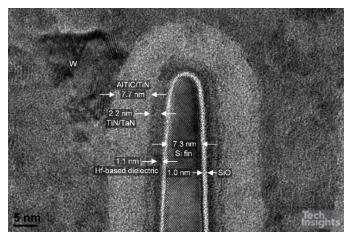

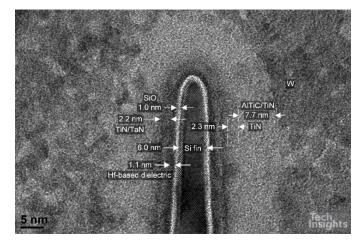

# **NMOS** and **PMOS** Gate and Epi Dimensions

#### **NMOS**

| Structure                                                                    | Size (nm)      |

|------------------------------------------------------------------------------|----------------|

| Gate length                                                                  | ~27            |

| NMOS gate fill thickness (TiN)                                               | ~1.7           |

| NMOS WF metal (AITiC) thickness                                              | ~5.5           |

| NMOS TiN/TaN cap thickness                                                   | 1.5/1.1        |

| NMOS logic gate dielectric thickness (Hf-based dielectric/SiO <sub>2</sub> ) | ~2.1 (1.1/1.0) |

| NMOS source/drain Si epi thickness/width                                     | ~47/27         |

| Structure                                                                    | Size (nm)      |

|------------------------------------------------------------------------------|----------------|

| Gate length                                                                  | ~25            |

| PMOS gate fill thickness (AITiC/TiN)                                         | ~7.1 (5.5/1.6) |

| PMOS WF metal (TiN) thickness                                                | ~2.3           |

| PMOS TiN/TaN cap thickness                                                   | 1.5/1.1        |

| PMOS logic gate dielectric thickness (Hf-based dielectric/SiO <sub>2</sub> ) | ~2.1 (1.1/1.0) |

| PMOS source/drain SiGe epi thickness/width                                   | ~60/52         |

# Statement of Measurement Uncertainty and Scope Variation

#### **Statement of Measurement Uncertainty**

TechInsights calibrates length measurements on its scanning electron microscope (SEM), transmission electron microscope (TEM), and optical microscopes using measurement standards that are traceable to the International System of Units (SI).

Our SEM/TEM cross-calibration standard was calibrated at the National Physical Laboratory (NPL) in the UK (Report Reference LR0304/E06050342/SEM4/190). This standard has a 146 ± 2 nm (± 1.4%) pitch, as certified by the NPL. TechInsights verifies every six months that its SEM and TEM are calibrated to within ± 2% of this standard, over the full magnification ranges used.

TechInsights' optical microscopes are calibrated using a stage micrometer calibrated at the National Research Council of Canada (CNRC) (Report Reference LS-2005-0010). This standard has an expanded uncertainty of 0.3 µm (0.3%) for the stage micrometer's 100 µm pitch lines.

Random measurement errors, introduced during measurements of features on the calibrated images, yield an additional expanded uncertainty, which together with calibration uncertainty, is approximately  $\pm$  5% or better for features larger than about 20% of the image width.

TechInsights camera systems, used for package photographs and teardown photographs, and TechInsights X-ray instruments are not calibrated. Package dimensions are measured physically with calipers.

The materials analysis reported in TechInsights reports is normally limited to approximate elemental composition, rather than stoichiometry. Quantification of energy dispersive spectroscopy (SEM-EDS and TEM-EDS) and TEM-based electron energy loss spectroscopy (TEM-EELS) materials analysis is usually not provided, unless otherwise stated. TechInsights will typically abbreviate the material composition, using only the elemental symbols (rather than full chemical formula) in approximate order of the peak heights in the spectra, but this does signify the relative concentration.

Secondary ion mass spectrometry (SIMS) data may be calibrated for certain dopant elements, provided suitable standards were available. Spreading resistance profiling (SRP) data is typically calibrated. Scanning microwave impedance microscopy (sMIM) provides spatial information on the dopant type; however, it is not quantitative. The accuracy of other methods is available on request.

#### **Statement of Scope Variation**

Due to the nature of reverse engineering and the diversity of analyzed devices, there is a possibility of content variation in TechInsights technical reports.

### **About TechInsights**

For over 25 years TechInsights has been a trusted patent and technology partner to the world's largest and most successful companies including 37 of the top 50 U.S. patent holders. By revealing the innovation others can't inside the broadest range of advanced technology products, we prove patent value and enable business leaders to make the best, fact-based IP and technology investment decisions. Headquartered in Ottawa Canada, TechInsights' Patent and Technology Analysts deliver specialized products and services from global offices.

#### **Contact TechInsights**

To find out more information on this report, or any other reports in our library, please contact TechInsights at 1-613-599-6500.

#### **TechInsights**

1891 Robertson Road, Suite 500 Ottawa, Ontario K2H 5B7 Canada T 1-613-599-6500 F 1-613-599-6501

Web site: <a href="www.techinsights.com">www.techinsights.com</a> <a href="mailto:info@techinsights.com">info@techinsights.com</a>

Please send any feedback to feedback@techinsights.com