Adv. Packaging report by Romain FRAUX December 2018 – Version 2

## Versions of the Report

| Version | Date       | Updates                                                                                                                                                                                                                                                                                                                              |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1      | 15/12/2018 | o Initial release                                                                                                                                                                                                                                                                                                                    |

| V2      | 02/01/2019 | <ul> <li>Added DRAM Driver Die         ✓ Interposer μBumps Tweak</li> <li>Added GPU Die         ✓ μBumps dimensions         ✓ Interposer μBumps dimensions: added middle and side differences</li> <li>Added Interposer Die         ✓ Reticle Stitching size and location         ✓ μBumps Dimensions         ✓ L/S Width</li> </ul> |

|         |            |                                                                                                                                                                                                                                                                                                                                      |

|         |            |                                                                                                                                                                                                                                                                                                                                      |

|         |            |                                                                                                                                                                                                                                                                                                                                      |

## Table of Contents

| Overview     | Introduction                                            | Λ  |                                     | Interposer Die                                                                 |    |

|--------------|---------------------------------------------------------|----|-------------------------------------|--------------------------------------------------------------------------------|----|

| Overview /   | Executive Summary                                       | 4  | 0                                   | ✓ View, Dimensions & Marking                                                   |    |

| _            | •                                                       |    |                                     |                                                                                |    |

| 0            | Reverse Costing Methodology                             |    |                                     | μυαπησια 13 / 3                                                                |    |

| Company Pi   | rofile                                                  | 8  | 0                                   | ✓ Interposer Cross-Section  Comparison with AMD Fury X including SK-Hynix HBM1 |    |

| 0            | 2.5D & 3D Packaging Market                              |    | O                                   | companson with this rary Americang Sk Hyma Heini                               |    |

| 0            | NVIDIA Company Profile                                  |    | Manufacturir                        | ng Process Flow                                                                | 95 |

| 0            | NVIDIA Company Frome  NVIDIA Tesla P100 Characteristics |    | 0                                   | Global Overview                                                                |    |

|              | Volta GPU Supply Chain                                  |    | 0                                   | GPU Process Description & Foundry                                              |    |

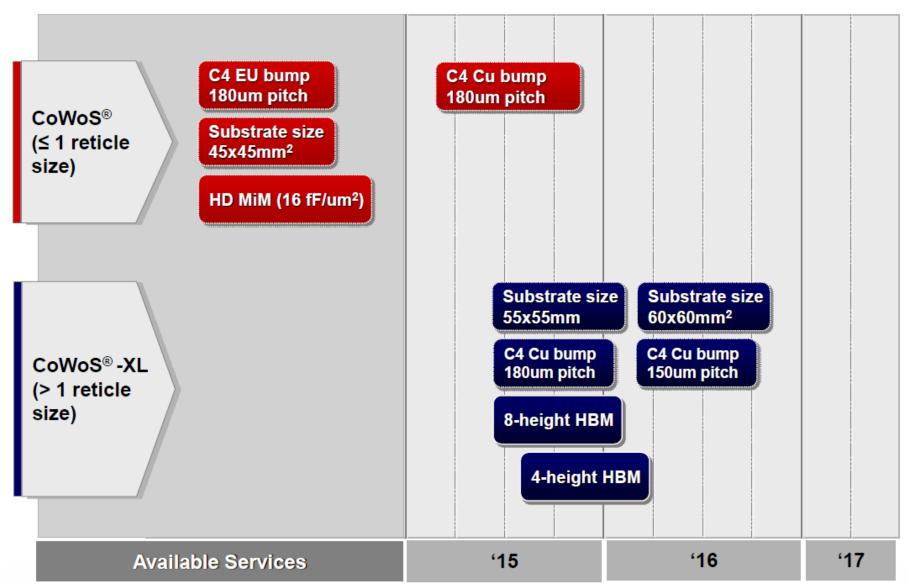

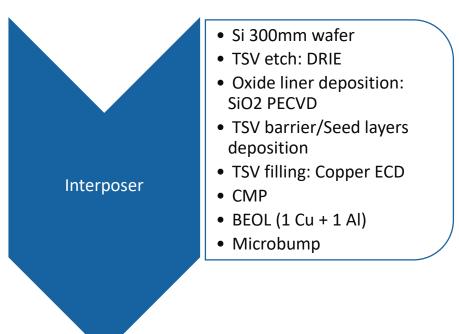

| 0            | TSMC CoWoS                                              |    | o Interposer Process Flow & Foundry |                                                                                |    |

| 0            |                                                         |    | 0                                   | HBM2 Stack Process Flow & Foundry                                              |    |

| 0            | Samsung HBM2                                            |    | 0                                   | CoWoS Process Flow & Foundry                                                   |    |

| Physical Ana | alysis                                                  | 21 | Cost Analysis                       |                                                                                | 12 |

| 0            | Summary of the Physical Analysis                        |    | 0                                   | Summary of the cost analysis                                                   |    |

| 0            | Physical Analysis Methodology                           |    | 0                                   | Yields Explanation & Hypotheses                                                |    |

| 0            | NVIDIA Tesla P100 Teardown                              |    | 0                                   | GPU Front-End & Die Cost                                                       |    |

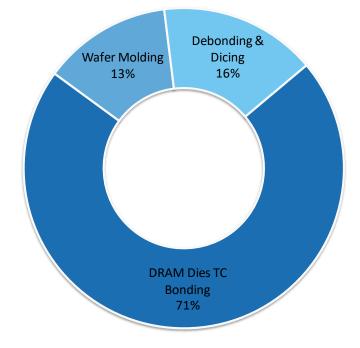

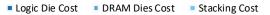

| 0            | Package                                                 |    | 0                                   | HBM2 Stack                                                                     |    |

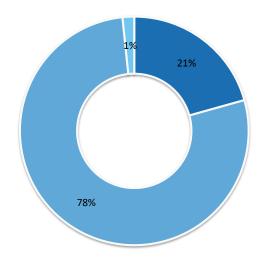

|              | ✓ Views & Dimensions                                    |    |                                     | ✓ TSV Manufacturing Cost                                                       |    |

|              | ✓ Passives Assembly                                     |    |                                     | ✓ Micro-Bumping Manufacturing Cost                                             |    |

|              | ✓ Laminate & Frame Cross-Section                        |    |                                     | ✓ Dies Cost (DRAM + Logic)                                                     |    |

| 0            | DRAM Die                                                |    |                                     | ✓ HBM2 Stack Cost                                                              |    |

| O            | ✓ View, Dimensions & Marking                            |    | 0                                   | Interposer                                                                     |    |

|              | ✓ µBumps & TSVs                                         |    |                                     | ✓ TSV Manufacturing Cost                                                       |    |

|              |                                                         |    |                                     | ✓ Microbumping Cost                                                            |    |

|              |                                                         |    |                                     | ✓ Interposer Cost                                                              |    |

| o GPU Die    |                                                         |    | 0                                   | CoWoS Assembly Manufacturing Cost                                              |    |

|              | ✓ View, Dimensions & Marking                            |    | 0                                   | Final Component Cost                                                           |    |

|              | √ µBumps                                                |    | Estimated Pri                       | ice Analysis                                                                   | 14 |

|              | ✓ GPU Cross-Section                                     |    | O                                   | Manufacturer Financial Ratios                                                  | 17 |

| 0            | Filler Die                                              |    | 0                                   | Component Manufacturer Price                                                   |    |

|              | ✓ View, Dimensions & Marking                            |    |                                     |                                                                                |    |

|              | ✓ Filler Cross-Section                                  |    | <u>Feedbacks</u>                    |                                                                                | 15 |

|              |                                                         |    | System nlus (                       | Consulting services                                                            | 15 |

# OVERVIEW METHODOLOGY

- Executive Summary

- o Reverse Costing Methodology

- o Glossary

Company Profile & Supply Chain

Physical Analysis

Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

About System Plus

### **Executive Summary**

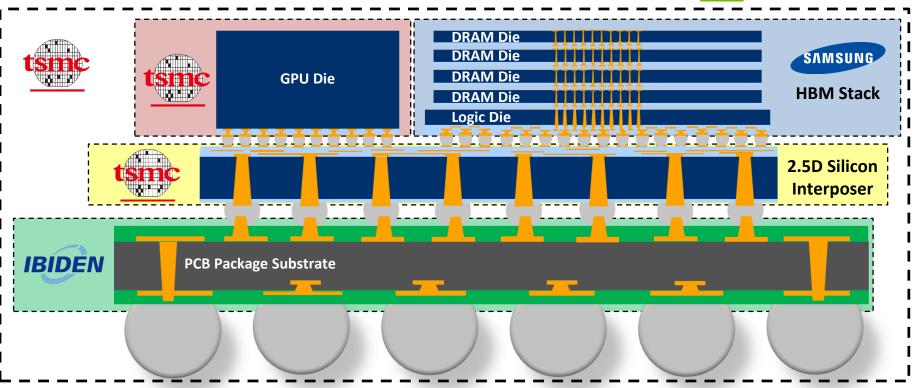

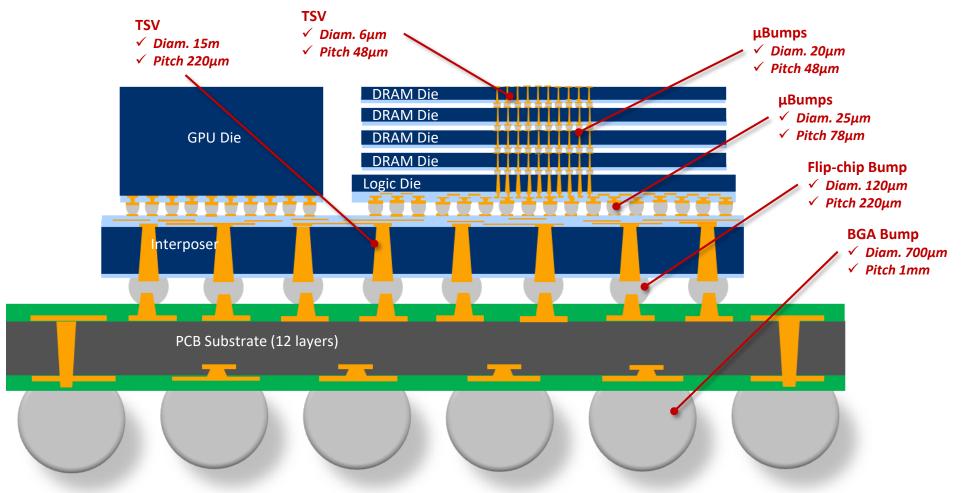

- Targeted for High Performance Computing (HPC) and deep learning, the NVIDIA Tesla V100 includes3D stacked memory with 2.5D integration on a silicon interposer in a Chip-on-Wafer-on-Substrate (CoWoS) process.

- The Tesla V100 accelerators are equipped with 16GB or 32GB of second generation high bandwidth memory (HBM2).

- HBM2 greatly increases memory capacity and bandwidth over first generation HBM1 technology. HBM1 was limited to 1GB of memory per stack of four dynamic random access memory (DRAM) die with maximum capacity of 256MB and 125GB/sec of bandwidth. That compares to 8GB of memory per stack of eight stacked DRAM dies with maximum capacity of 1GB and 180GB/sec bandwidth for HBM2.

- The single 55mm x 55mm 12-layer ball grid array (BGA) package of the NVIDIA Tesla V100 includes more than 4,000 mm<sup>2</sup> of silicon area. Two industry leaders, TSMC and Samsung, had to come together to deliver this much silicon area in a package.

- TSMC is the main provider for the Tesla V100. Using its 2.5D CoWoS platform, it manufactures the GV100 GPU die, featuring a 12nm FinFET process and 21.1 billion transistors. It also produces a large silicon interposer on top of which the GPU is assembled at the wafer-level with its four HBM2 stacks.

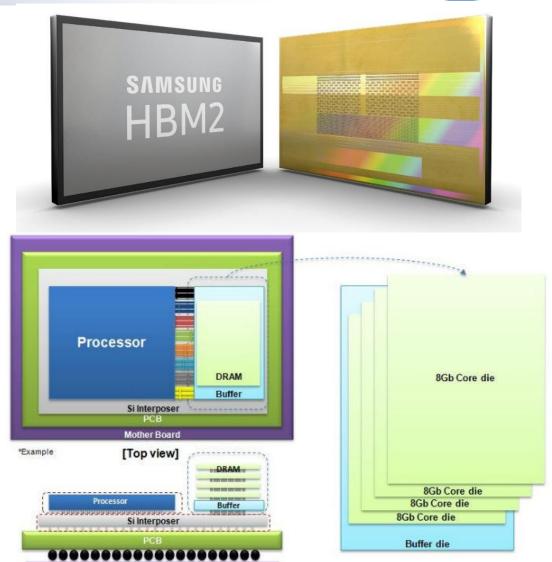

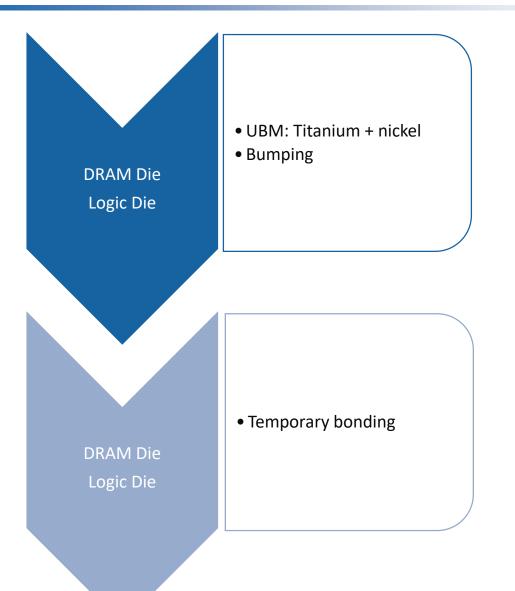

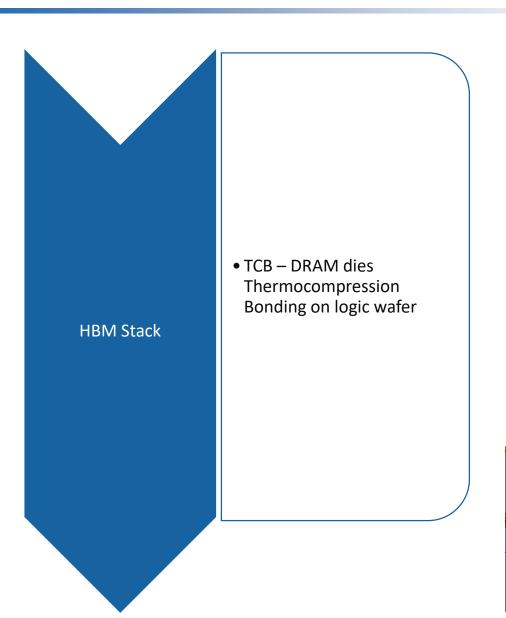

- Samsung provides the HBM2 stacks. A 3D assembly process yields HBM2 stacks composed of four 1GB DRAM memory dies and one buffer die, connected with via-middle through-silicon vias and micro-bumps.

- The report includes a complete physical analysis of the packaging process, with details on all technical choices regarding process, equipment and materials. Also, the complete manufacturing supply chain is described and manufacturing costs are calculated.

### Reverse Costing Methodology

#### Overview / Introduction

- o Executive Summary

- **Reverse Costing** Methodology

- o Glossary

Company Profile & Supply Chain

Physical Analysis

Manufacturing Process Flow

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

The reverse costing analysis is conducted in 3 phases:

Package is analyzed and measured The dies are extracted in order to get overall data: dimensions, main blocks, pad number and pin out, die marking Setup of the manufacturing process.

Setup of the manufacturing environment Cost simulation of the process steps

Supply chain analysis Analysis of the selling price

## Glossary

#### Overview / Introduction

- o Executive Summary

- o Reverse Costing Methodology

- Glossary

Company Profile & Supply Chain

Physical Analysis

Manufacturing Process Flow

Cost Analysis

Selling Price Analysis

<u>Feedback</u>

About System Plus

| Acronym | Definition                              |

|---------|-----------------------------------------|

| Al      | Aluminum                                |

| ASIC    | Application Specific Integrated Circuit |

| BGA     | Ball Grid Arra                          |

| CMOS    | Complementary Metal–Oxide–Semiconductor |

| CoWoS   | Chip-on-Wafer-on-Substrate              |

| DRAM    | Dynamic Random Access Memory            |

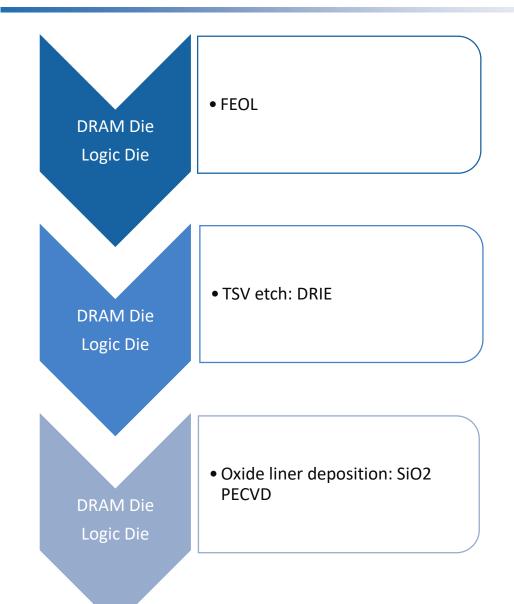

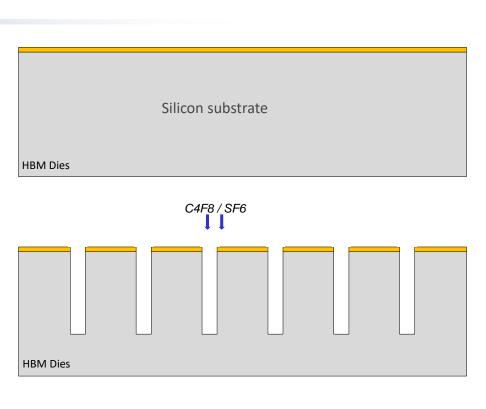

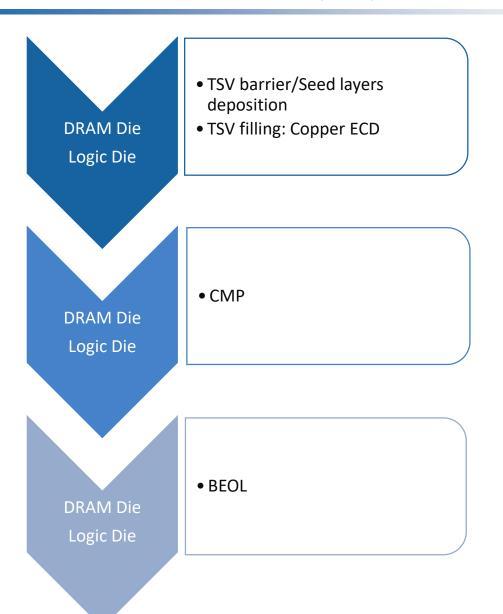

| DRIE    | Deep Reactive Ion Etching               |

| EDX     | Energy Dispersive X-ray spectroscopy    |

| G&A     | General & Administrative                |

| GPU     | Graphics Processor Unit                 |

| НВМ     | High Bandwidth Memory                   |

| HMC     | Hybrid Memory Cube                      |

| OEM     | Original Equipment Manufacturer         |

| PCB     | Printed Circuit Board                   |

| PGDW    | Potential Good Dies per Wafer           |

| R&D     | Research and Development                |

| SEM     | Scanning Electron Microscope            |

| Si      | Silicon                                 |

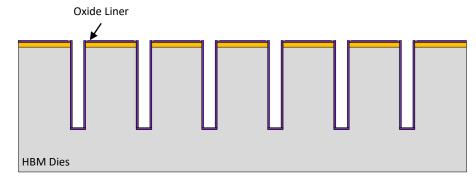

| SiO2    | Silicon Dioxide                         |

| TSV     | Through-Silicon Via                     |

# **COMPANY** PROFILE

### Market Forecast

#### Overview / Introduction

#### Company Profile & Supply Chain

- ▶ 2.5D & 3D Packaging Market

- o NVIDIA Profile

- NVIDIA Tesla P100 Characteristics

- o Volta GPU Supply Chain

- TSMC CoWoS

- o Samsung HBM2

**Physical Analysis**

Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

About System Plus

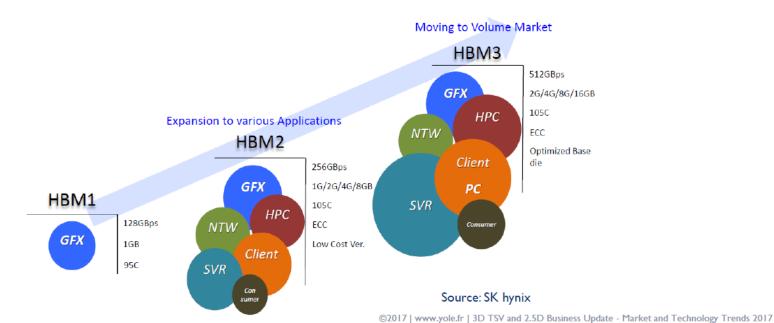

### HIGH-BANDWIDTH MEMORY ROADMAP

- High-Bandwidth Memory product is continuously adopted by players and is integrated in many advanced and essential products.

- AMD adopted first HBM 1st generation in 2015 in high-performance graphic card for gaming.

- Since AMD, others have followed such as Nvidia, Xilinx, Intel pushing HBM2 products in HPC, servers and other applications.

- A 3rd generation is in preparation by memory manufacturers (Samsung & SK hynix) enabling twice the data flowrate.

HBM will penetrate various market segments in the short future

Because of further

adoption of

HBM2, a 3rd generation is

under

development

#### Company Profile & Supply Chain

- ▶ 2.5D & 3D Packaging Market

- o NVIDIA Profile

- o NVIDIA Tesla P100 Characteristics

- o Volta GPU Supply Chain

- TSMC CoWoS

- o Samsung HBM2

#### **Physical Analysis**

Manufacturing Process Flow

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

### Market Forecast

#### 3D STACKED MEMORY CUBE

### Technical comparison between HBM and HMC Memory Systems

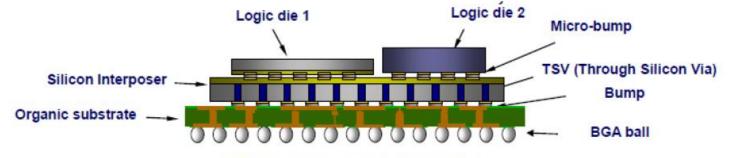

In terms of packaging, one of the main differences between HMC and HBM is the final integration. HBM will require a silicon interposer mounted on a substrate whereas HMC can be placed directly on an organic substrate.

#### High Bandwidth Memory Interfaces

- HMC: Stand-Alone Memory Module on Board

- Uses Serial Interface between ASIC and HMC - few high speed signals.

- Wired across system board.

- High speed signals need isolation; Drives number of BGA's up.

- Single fast SERDES lane.

- 15-30 Gbps bidirectional bandwidth.

- · Also requires many isolation pins.

- · HBM: On-Module Memory Integrated w/ Si Interposer

- Uses Parallel Interface many, many, fairly slow signals.

- Generally simpler IO and lower power.

- Too many signals to get off package.

- Lower cost memory, but higher complexity package integration.

- Many slow parallel lanes. ~2 Gbps/line unidirectional.

- 30 Gbps bidirectional BW needs15 parallel signal lines for each direction.

Source: GlobalFoundries

| Variables                     | HBMI               | HBM2          | HMCI                                 | HMC2                              |  |

|-------------------------------|--------------------|---------------|--------------------------------------|-----------------------------------|--|

| VDD (V)                       | 1.5                | 1.5           | 1.35                                 | 1.2                               |  |

| Max. Data Rate<br>(Gbps)      | 1                  | 2             | 15                                   | 30                                |  |

| Bus Width (bits)              | 1024               |               | 4 Links (16 TX                       | 4 Links (16 TX/RX lanes per link) |  |

| Max Stack<br>Bandwidth (GB/s) | 128                | 256           | 120                                  | 320                               |  |

| Signaling                     | Sin                | Single ended  |                                      | Differential                      |  |

| Interface                     | Wid                | Wide parallel |                                      | Serial                            |  |

| Channel overhead              | Short              |               | L                                    | Long                              |  |

| Format                        | In a Si Interposer |               | Stand-alone as a complete<br>package |                                   |  |

| Control distribution in logic | Simple DRAM        |               | Advanced                             | Advanced Transactional            |  |

Source: Rambus

©2017 | www.yole.fr | 3D TSV and 2.5D Business Update - Market and Technology Trends 2017

### Market Forecast

enabled

performance

hardware for

deep learning

applications

### DEEP LEARNING HARDWARE

Hardware for TRAINING require large bandwidth, 3D-based products offer solutions.

INFERENCE require less bandwidth but low latency. Interposer could come as a solution because of its modularity and its capacity to integrate more than 4 chips.

Main players offer clear different product lines as solutions for both steps.

#### Overview / Introduction

#### Company Profile & Supply Chain

- ▶ 2.5D & 3D Packaging Market

- o NVIDIA Profile

- o NVIDIA Tesla P100 Characteristics

- o Volta GPU Supply Chain

- TSMC CoWoS

- o Samsung HBM2

**Physical Analysis**

Manufacturing Process Flow

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

**TRAINING**

Tesla PI00

Volta

Titan X

**XEON**

DLIA FPGA based

accelerator

MI6 Vega

RADEON INSTINC

letson TKI/TXI

Tesla P40 and P4 accelerator

Drive PX2

### Company Profile – NVIDIA

#### Overview / Introduction

#### Company Profile & Supply Chain

- o 2.5D & 3D Packaging Market

- NVIDIA Profile

- o NVIDIA Tesla P100 Characteristics

- o Volta GPU Supply Chain

- TSMC CoWoS

- o Samsung HBM2

#### Physical Analysis

Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

About System Plus

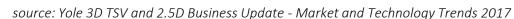

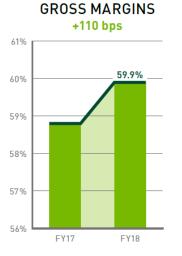

#### **NVIDIA Financial Highlights:**

- o Sales revenues 2018: \$9.7 Billion

- 59.9% o Gross margin 2018:

- Net income 2018: \$3.0 Billion

#### **NVIDIA Employees:**

- o Date of Establishment

- ✓ April, 1993

- o Headquarter:

- ✓ Santa Clara, California, USA

- ✓ 10,299 employees worldwide (as of 29 January, 2017).

#### Company Profile & Supply Chain

- o 2.5D & 3D Packaging Market

- NVIDIA Profile

- o NVIDIA Tesla P100 Characteristics

- o Volta GPU Supply Chain

- o TSMC CoWoS

- o Samsung HBM2

#### Physical Analysis

Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

About System Plus

### Company Profile – NVIDIA

- Manufacturing Supply Chain (source: NVIDIA)

- Semiconductor wafers:

- > TSMC

- > Samsung

- Assembly, Testing and Packaging:

- > ASE

- > BYD Auto

- ➤ Hon Hai Precision

- > JSI Logistics

- ➤ King Yuan Electronics

- > Siliconware Precision Industries

- Substrates:

- > Ibiden

- Nanya Technology

- ➤ Unimicron Technology

- Memories:

- Samsung

- ➤ SK Hynix

### NVIDIA Telsa V100 Characteristics

#### Overview / Introduction

#### Company Profile & Supply Chain

- o 2.5D & 3D Packaging Market

- o NVIDIA Profile

- NVIDIA Tesla P100 Characteristics

- o Volta GPU Supply Chain

- o TSMC CoWoS

- o Samsung HBM2

Physical Analysis

Manufacturing Process Flow

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

### ■ NVIDIA Tesla V100 with Volta GV100 GPU

#### **VOLTA ARCHITECTURE**

By pairing CUDA Cores and Tensor Cores within a unified architecture, a single server with Tesla V100 GPUs can replace hundreds of commodity CPU servers for traditional HPC and Deep Learning.

#### **TENSOR CORE**

Equipped with 640 Tensor Cores, Tesla V100 delivers 125 teraFLOPS of deep learning performance. That's 12X Tensor FLOPS for DL Training, and 6X Tensor FLOPS for DL Inference when compared to NVIDIA Pascal™ GPUs.

### MAXIMUM **EFFICIENCY MODE**

The new maximum efficiency mode allows data centers to achieve up to 40% higher compute capacity per rack within the existing power budget. In this mode, Tesla V100 runs at peak processing efficiency, providing up to 80% of the performance at half the power consumption.

#### HBM2

With a combination of improved raw bandwidth of 900GB/s and higher DRAM utilization efficiency at 95%, Tesla V100 delivers 1.5X higher memory bandwidth over Pascal GPUs as measured on STREAM. Tesla V100 is now available in a 32GB configuration that doubles the memory of the standard 16GB offering.

#### **SPECIFICATIONS**

Tesla V100

Tesla V100

|                                 | PCle                                     | SXM2          |  |

|---------------------------------|------------------------------------------|---------------|--|

| GPU Architecture                | NVIDIA Volta                             |               |  |

| NVIDIA Tensor<br>Cores          | 640                                      |               |  |

| NVIDIA CUDA®<br>Cores           | 5,120                                    |               |  |

| Double-Precision<br>Performance | 7 TFLOPS                                 | 7.8 TFLOPS    |  |

| Single-Precision<br>Performance | 14 TFLOPS                                | 15.7 TFLOPS   |  |

| Tensor<br>Performance           | 112 TFLOPS                               | 125 TFLOPS    |  |

| GPU Memory                      | 32GB /16GB HBM2                          |               |  |

| Memory<br>Bandwidth             | 900GB/sec                                |               |  |

| ECC                             | Yes                                      |               |  |

| Interconnect<br>Bandwidth       | 32GB/sec                                 | 300GB/sec     |  |

| System Interface                | PCIe Gen3                                | NVIDIA NVLink |  |

| Form Factor                     | PCIe Full<br>Height/Length               | SXM2          |  |

| Max Power<br>Comsumption        | 250 W                                    | 300 W         |  |

| Thermal Solution                | Passive                                  |               |  |

| Compute APIs                    | CUDA, DirectCompute,<br>OpenCL™, OpenACC |               |  |

#### Company Profile & Supply Chain

- o 2.5D & 3D Packaging Market

- o NVIDIA Profile

- NVIDIA Tesla P100 Characteristics

- ▶ Volta GPU Supply Chain

- TSMC CoWoS

- o Samsung HBM2

Physical Analysis

Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

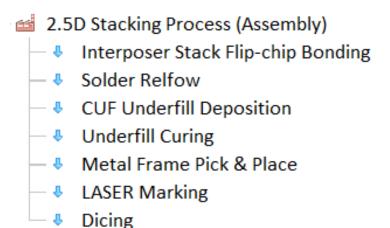

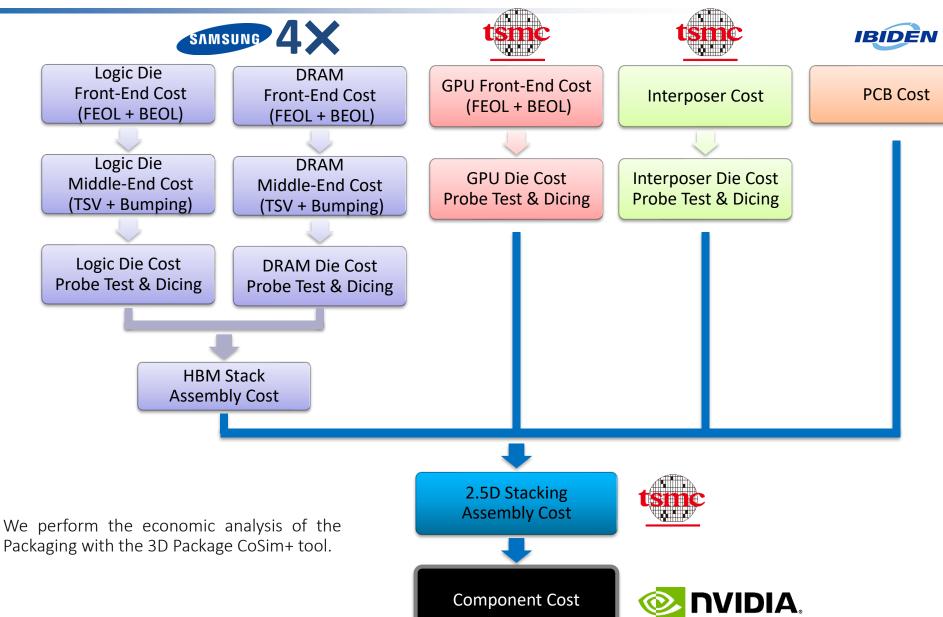

### Volta GPU Supply Chain

Component manufacturing supply chain:

#### Package Manufacturing Supply Chain:

- The HBM stack (memory dies, logic die and 3D interconnection) is made by Samsung in Korea.

- The GPU die is manufactured by TSMC in Taiwan.

- The Interposer is produced by TSMC in Taiwan.

- The PCB package substrate is made by Ibiden in Japan.

- The final assembly (HBM and GPU on interposer, interposer on PCB, passives assembly and BGA balls) is realized by TSMC in Taiwan.

#### Overview / Introduction

#### Company Profile & Supply Chain

- o 2.5D & 3D Packaging Market

- o NVIDIA Profile

- o NVIDIA Tesla P100 Characteristics

- o Volta GPU Supply Chain

- TSMC CoWoS

- o Samsung HBM2

Physical Analysis

Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

About System Plus

Overview / Introduction

#### Company Profile & Supply Chain

- o 2.5D & 3D Packaging Market

- o NVIDIA Profile

- NVIDIA Tesla P100 Characteristics

- o Volta GPU Supply Chain

- TSMC CoWoS

- o Samsung HBM2

**Physical Analysis**

Manufacturing Process Flow

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

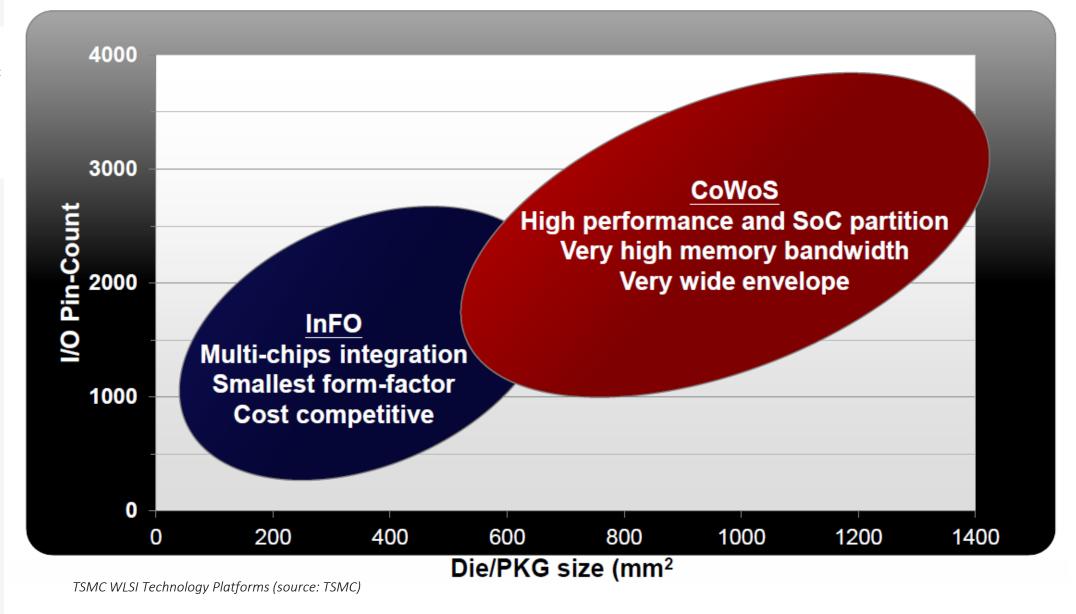

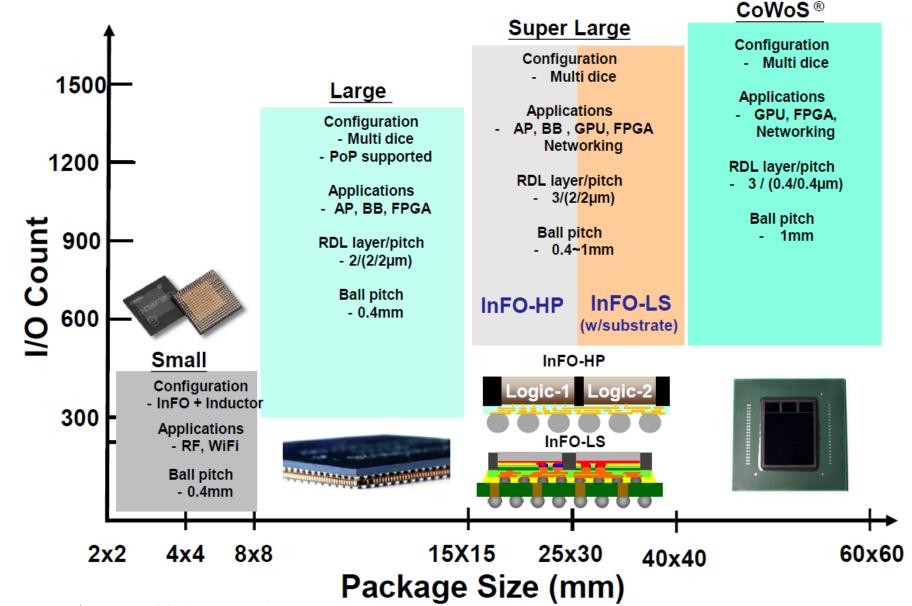

Integrate multiple chips into one single package using a submicron scale silicon interface (interposer)

- Enable higher performance, lower power consumption, and smaller form factor

- Best integrated flow for high yield and reliability

Heterogeneous Integration

#### Overview / Introduction

#### Company Profile & Supply Chain

- o 2.5D & 3D Packaging Market

- o NVIDIA Profile

- o NVIDIA Tesla P100 Characteristics

- o Volta GPU Supply Chain

- TSMC CoWoS

- o Samsung HBM2

**Physical Analysis**

Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

About System Plus

#### Overview / Introduction

#### Company Profile & Supply Chain

- o 2.5D & 3D Packaging Market

- o NVIDIA Profile

- o NVIDIA Tesla P100 Characteristics

- o Volta GPU Supply Chain

- ► TSMC CoWoS

- o Samsung HBM2

Physical Analysis

Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

About System Plus

### Samsung HBM2

#### Overview / Introduction

#### Company Profile & Supply Chain

- o 2.5D & 3D Packaging Market

- o NVIDIA Profile

- NVIDIA Tesla P100 Characteristics

- o Volta GPU Supply Chain

- TSMC CoWoS

- ▶ Samsung HBM2

Physical Analysis

Manufacturing Process Flow

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

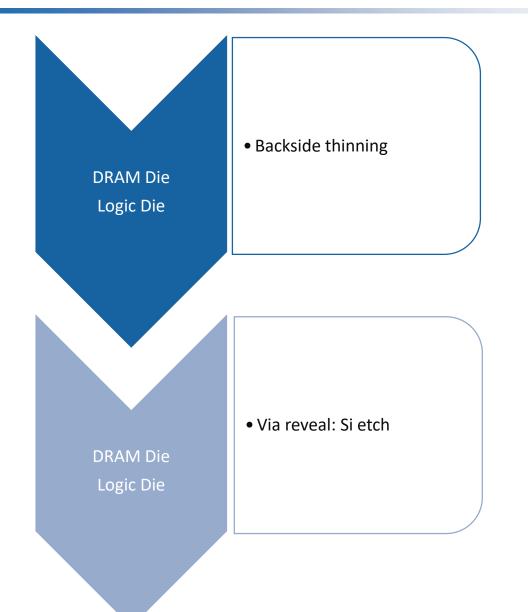

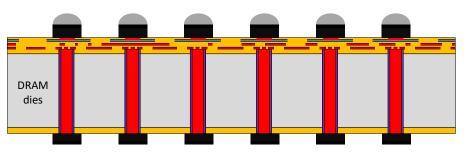

### ■ Samsung HBM2 Stack

- Mass production: beginning of 2016

- Stack of 4GB

- > 4 stacked dies of 1GB

- The 4GB HBM2 package is created by stacking a buffer die at the bottom and four 8-gigabit (Gb) core dies on top. These are then vertically interconnected by TSV holes and microbumps. A single 8Gb HBM2 die contains over 5,000 TSV holes, which is more than 36 times that of a 8Gb TSV DDR4 die, offering a dramatic improvement in data transmission performance compared to typical wirebonding based packages.

- Samsung's new DRAM package features 256GBps of bandwidth, which is double that of a HBM1 DRAM package. This is equivalent to a more than seven-fold increase over the 36GBps bandwidth of a 4Gb GDDR5 DRAM chip, which has the fastest data speed per pin (9Gbps) among currently manufactured DRAM chips. Samsung's 4GB HBM2 also enables enhanced power efficiency by doubling the bandwidth per watt over a 4Gb-GDDR5-based solution, and embeds ECC (error-correcting code) functionality to offer high reliability.

\*Example

Mother Board

[Side view]

[4GB HBM2 Package Structure]

# **PHYSICAL** ANALYSIS

#### Company Profile & Supply Chain

Overview / Introduction

#### Physical Analysis

- Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

### Summary of the Physical Analysis

#### **PACKAGE STRUCTURE:**

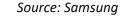

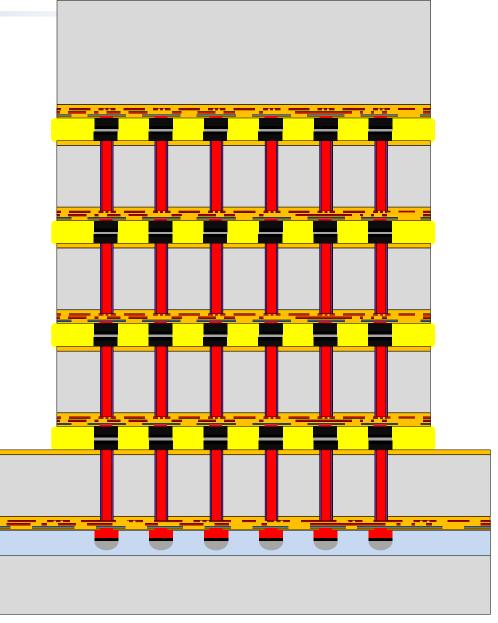

- 3D Packaging: 5 stacked dies with TSV & μBumps (HBM stack).

- 2.5D Packaging: HBM stack and GPU stacked with µBumps on a silicon interposer holding TSV.

- Flip-chip BGA: silicon interposer flip-chipped to a 12-layers PCB substrate

#### Company Profile & Supply Chain

#### Physical Analysis

- Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

### Physical Analysis Methodology

- Package is analyzed and measured.

- The package is opened to get overall die data: dimensions, main characteristics, device marking.

- o Pictures of selected area are made in order to understand the assembly.

- The dies are separated to get overall die data: dimensions, main blocks, pad number and pin out, die marking.

- o Removal of metal layers.

- Pictures (SEM & optical) of selected areas.

- Cross section to measure thicknesses.

### **Graphic Card Teardown**

#### Overview / Introduction

#### Company Profile & Supply Chain

#### **Physical Analysis**

- o Summary

- ▶ Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### Manufacturing Process Flow

Cost Analysis

Selling Price Analysis

**Feedback**

About System Plus

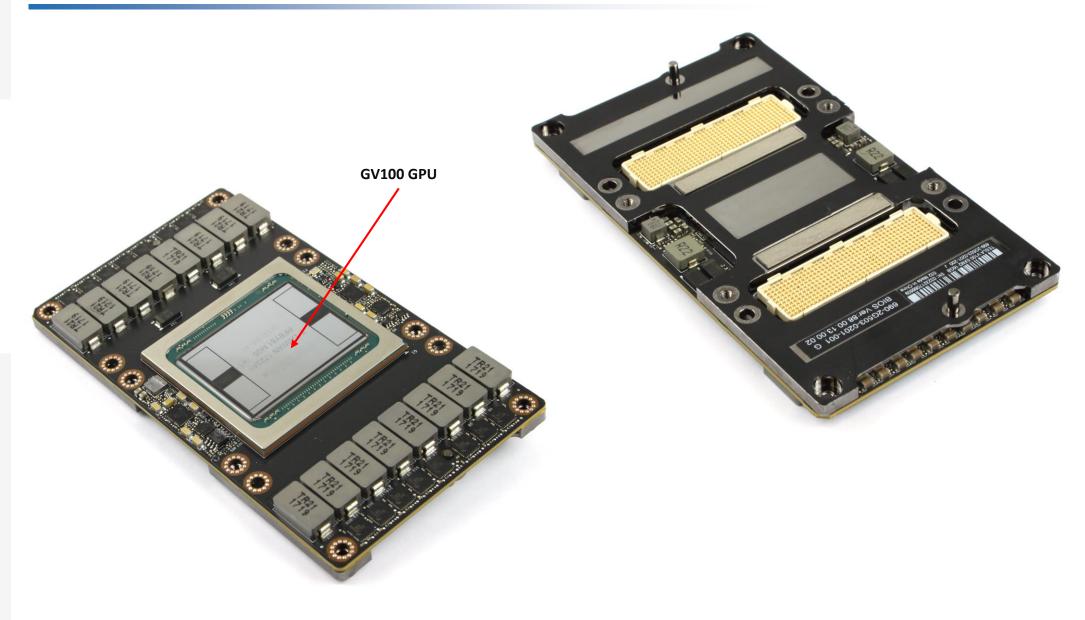

### **Graphic Card Teardown**

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- ► Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### Manufacturing Process Flow

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

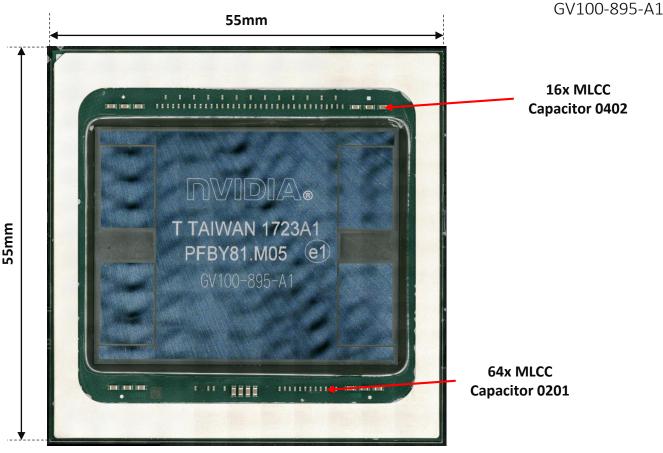

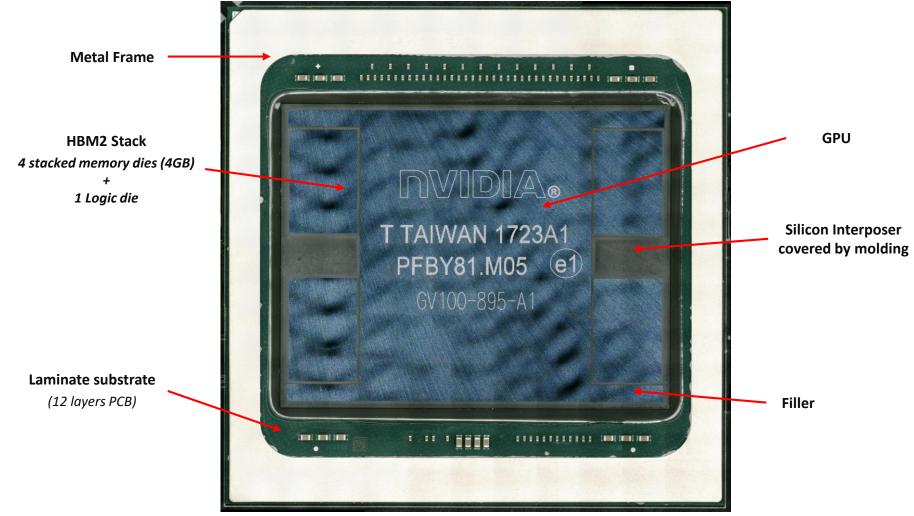

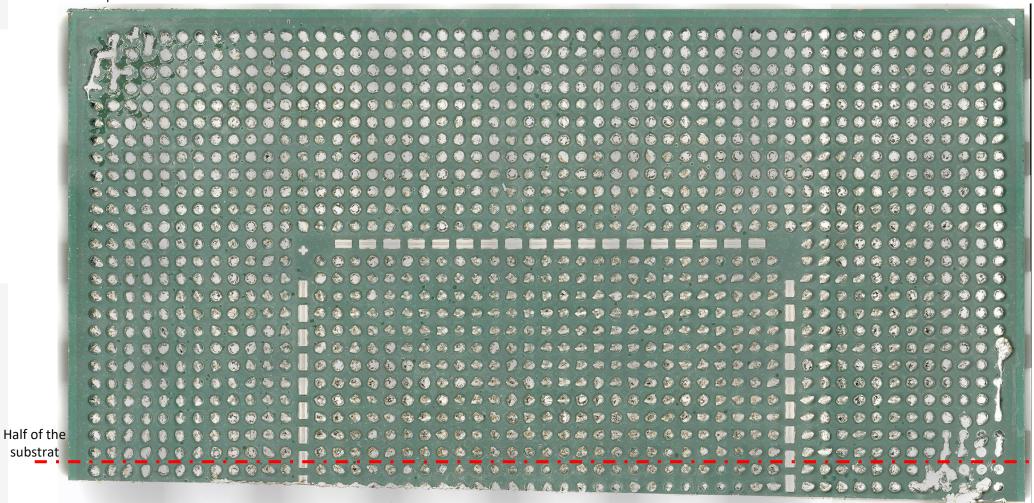

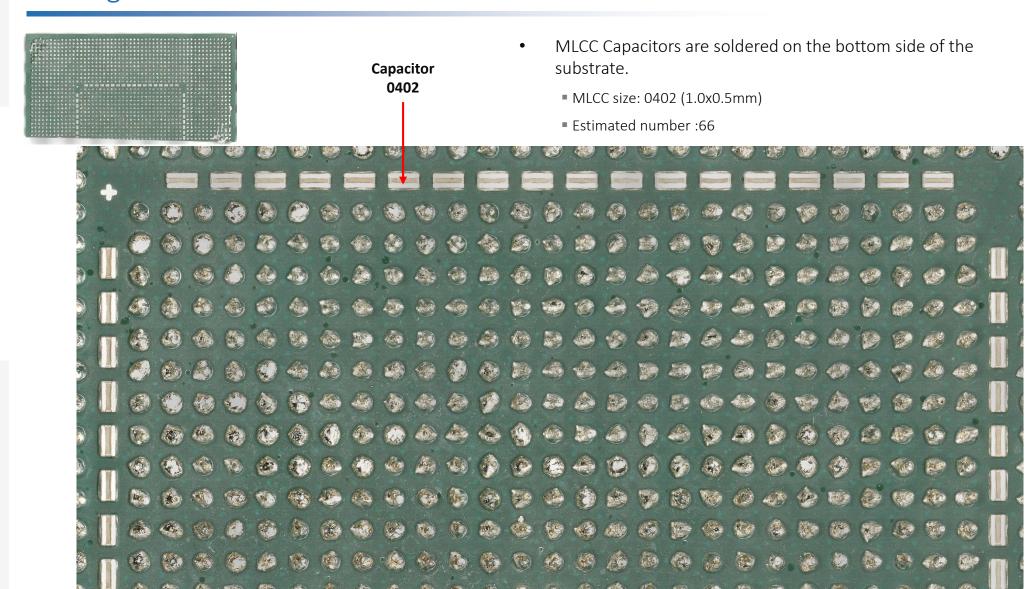

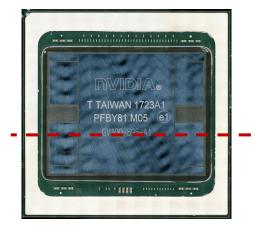

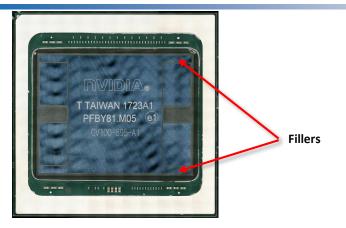

## Package Views & Dimensions

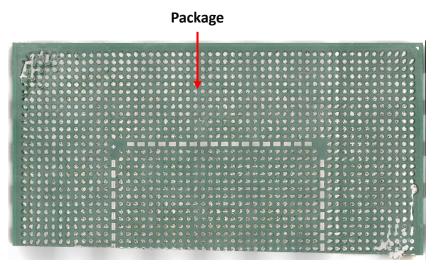

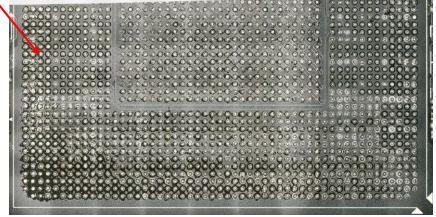

Package: FCBGA 2540-ball

55 x 55 mm Dimensions:

Pin Pitch: 1mm

Package Bottom View ©2018 by System Plus Consulting

Marking:

<logo Nvidia>

PFBY81.M05

**T TAIWAN 1723A1**

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

### Package Views & Dimensions

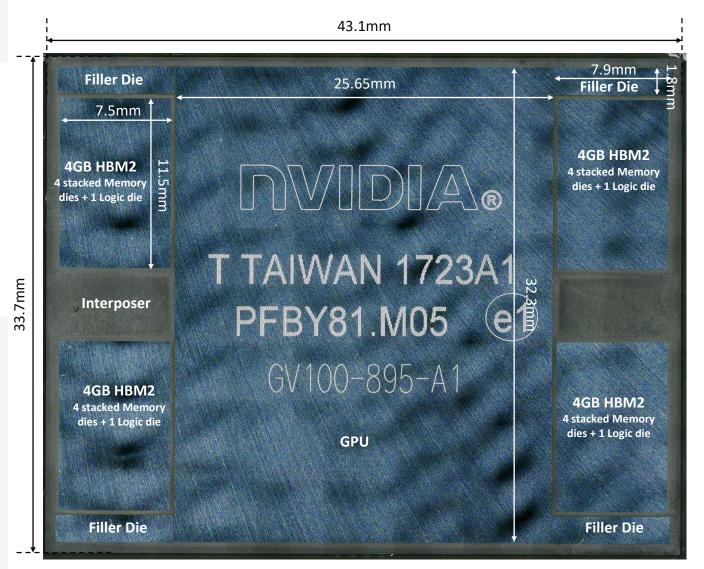

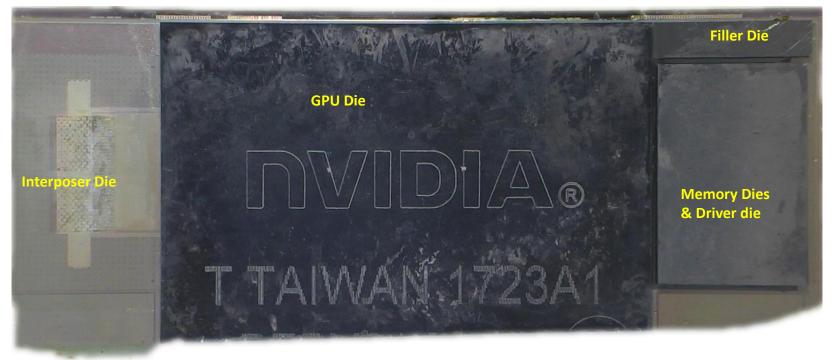

Single package with GV100 GPU and 16GB HBM2 Memory on a silicon interposer.

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

### Package Views & Dimensions

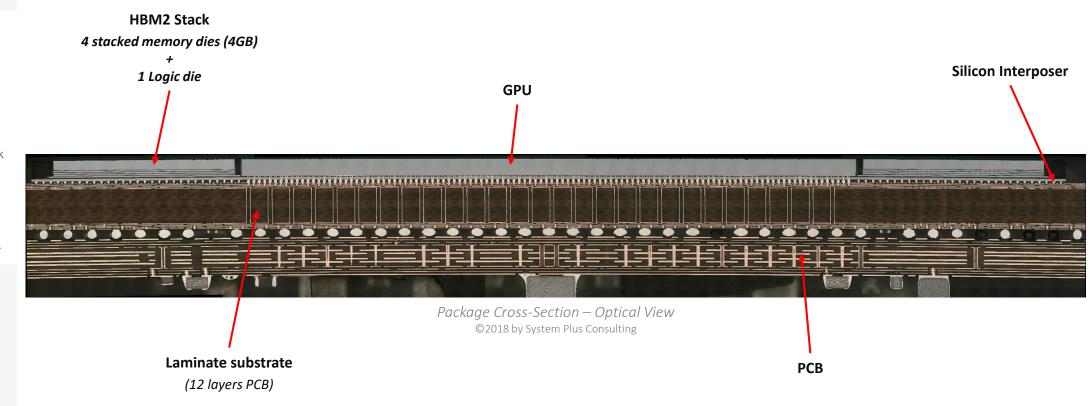

A cross-section of the package was made before unsoldering to have access to the complete assembly structure.

#### **PCB Board**

Package Unsoldered from PCB Board ©2018 by System Plus Consulting

**Package**

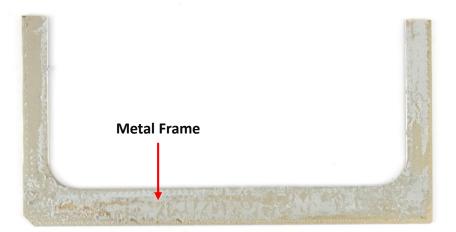

Metal Frame Removed ©2018 by System Plus Consulting

## Package Views & Dimensions

Overview / Introduction

Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

**Manufacturing Process Flow**

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

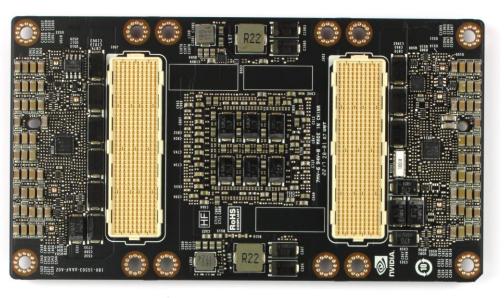

Estimated number of balls: 2,540

Ball pitch: 1mm

Package Bottom View after Cross-Section ©2018 by System Plus Consulting

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

### Package Views & Dimensions

MLCC View ©2018 by System Plus Consulting

### Dies Size

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- GPU Die

- Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

### Die Size (with scribe line):

Interposer Area: 1.452mm<sup>2</sup>

(43.1x33.7mm)

Nb of candidates per 12-inch wafer: 36

GPU Die Area: 828.5mm<sup>2</sup>

(25.65x32.3mm)

Nb of candidates per 12-inch wafer: 64

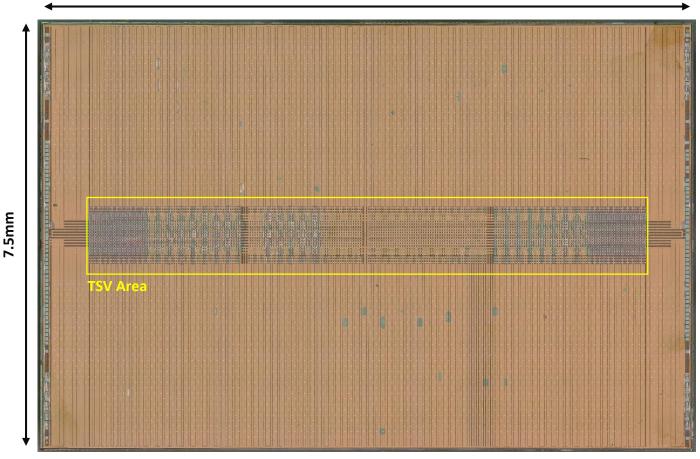

DRAM Dies Area: 86mm<sup>2</sup>

(11.5x7.5mm)

Nb of candidates per 12-inch wafer: 728

96mm<sup>2</sup> Logic Dies Area:

(12.0x8.0mm)

• Nb of candidates per 12-inch wafer: 656

Filler Die Area: 14.2mm<sup>2</sup>

(7.9x1.8mm)

Nb of candidates per 12-inch wafer: 4,396

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

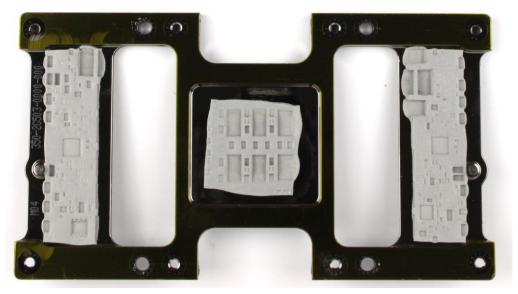

### Package Opening

Package Top View – Metal Frame Removed ©2018 by System Plus Consulting

Package Top View – Underfill removed and Right HBM Memory Removed ©2018 by System Plus Consulting

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

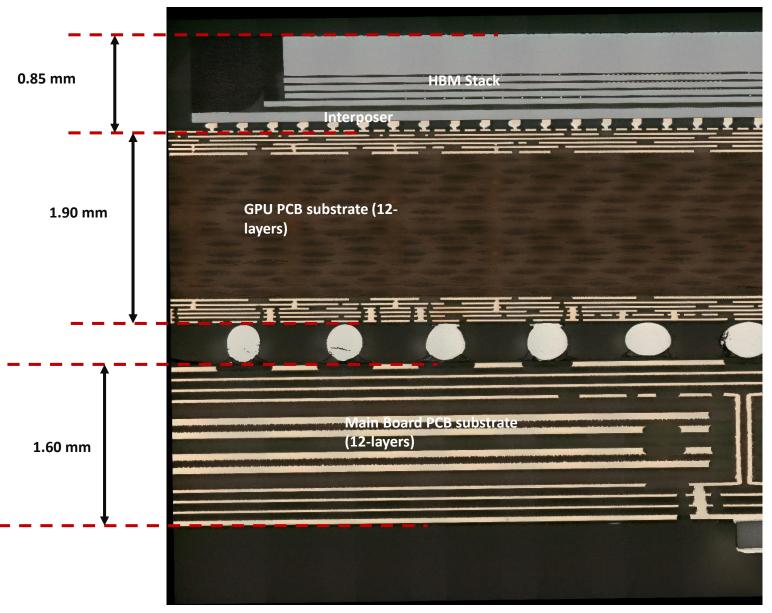

### **Board Cross-Section**

Board Cross-section plane ©2018 by System Plus Consulting

### Board Cross-Section – Laminate Substrate

3.25mm

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

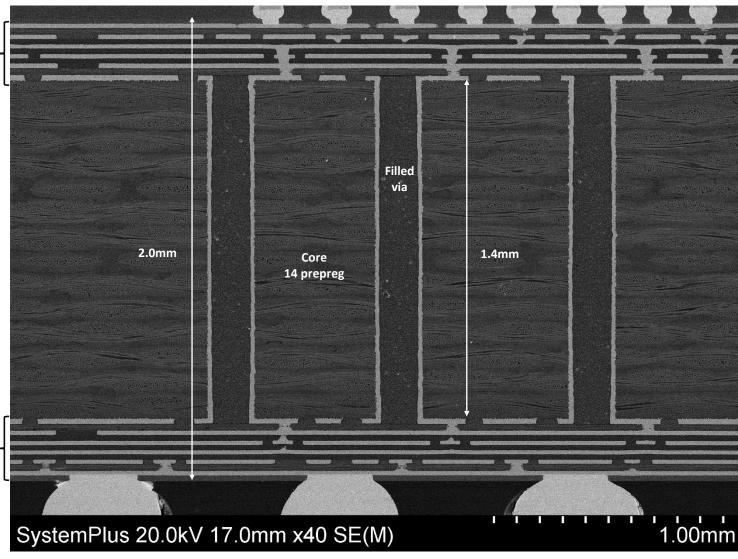

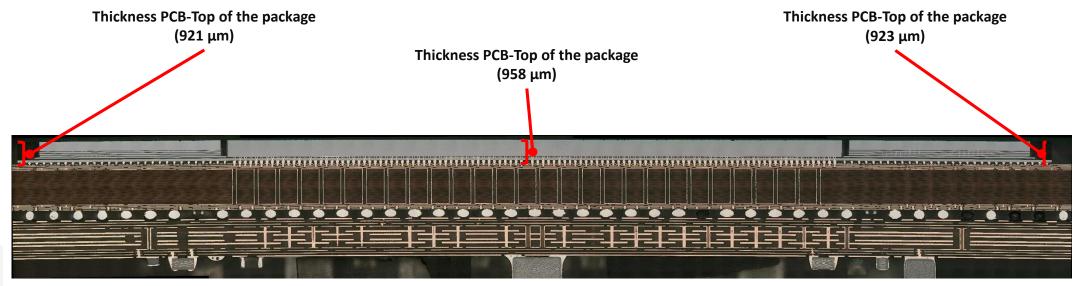

Package total thickness:

Metal frame thickness:

Substrate Cross-Section – Optical View ©2018 by System Plus Consulting

Laminate substrate thickness: 2<sub>m</sub>m 0.7mm

Laminate core thickness: 1.4mm

©2018 System Plus Consulting | NVIDIA Tesla V100 GPU 34

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

### Board Cross-Section – Laminate Substrate

6 copper layers

- The package laminate is a 12 layers HDI PCB.

- ✓ PCB thickness: 2mm

- Copper layers thickness: 18µm

6 copper ✓ Microvia diameter: 65µm layers

Substrate Cross-Section – SEM View ©2018 by System Plus Consulting

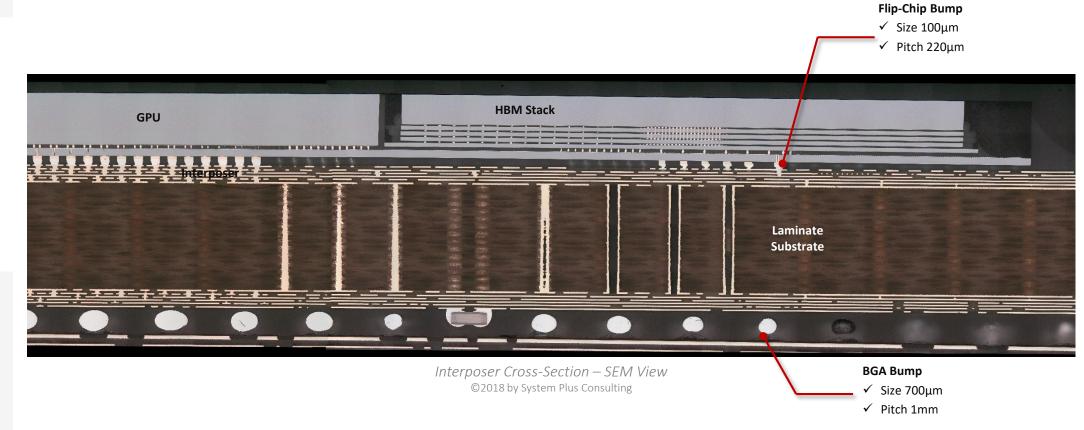

### Board Cross-Section – Interposer

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

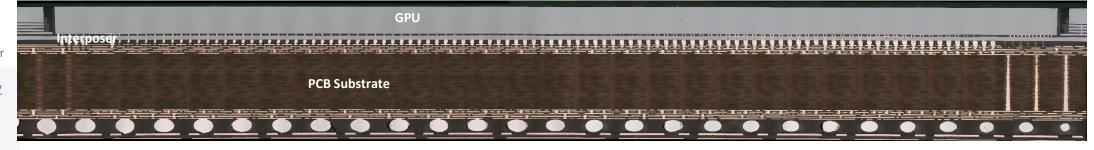

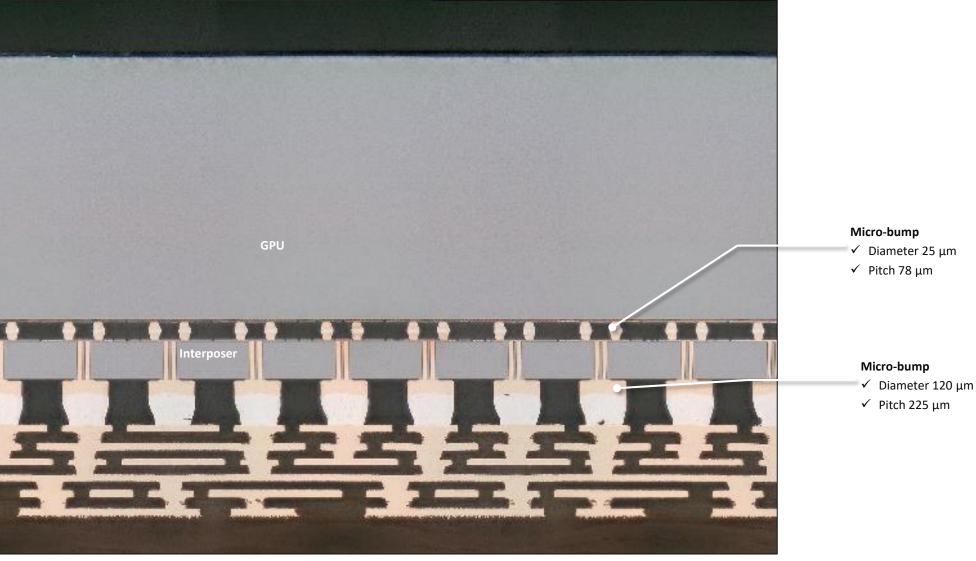

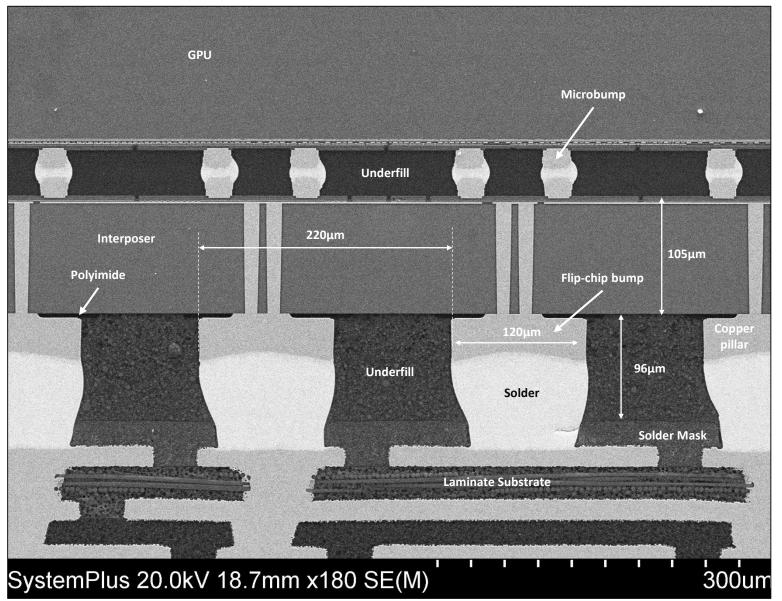

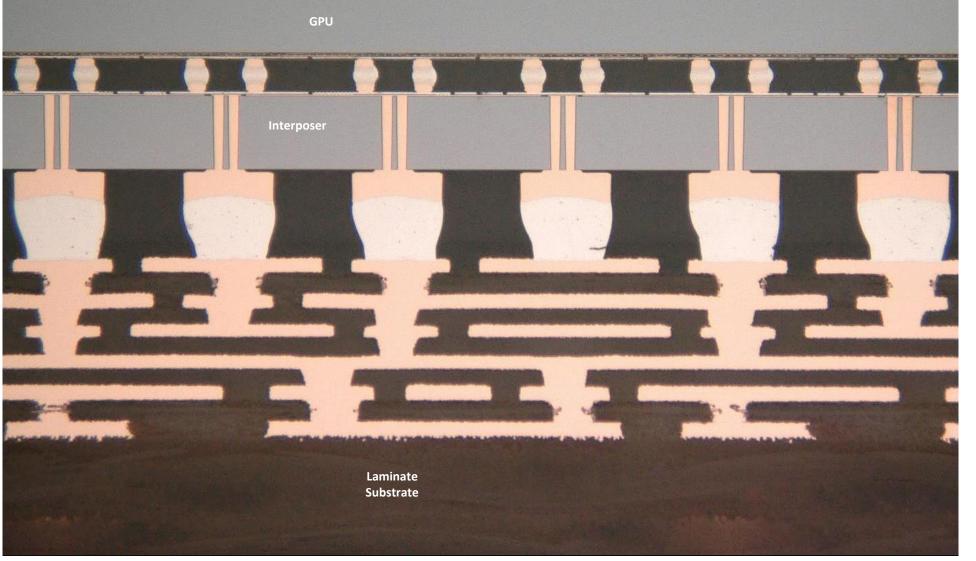

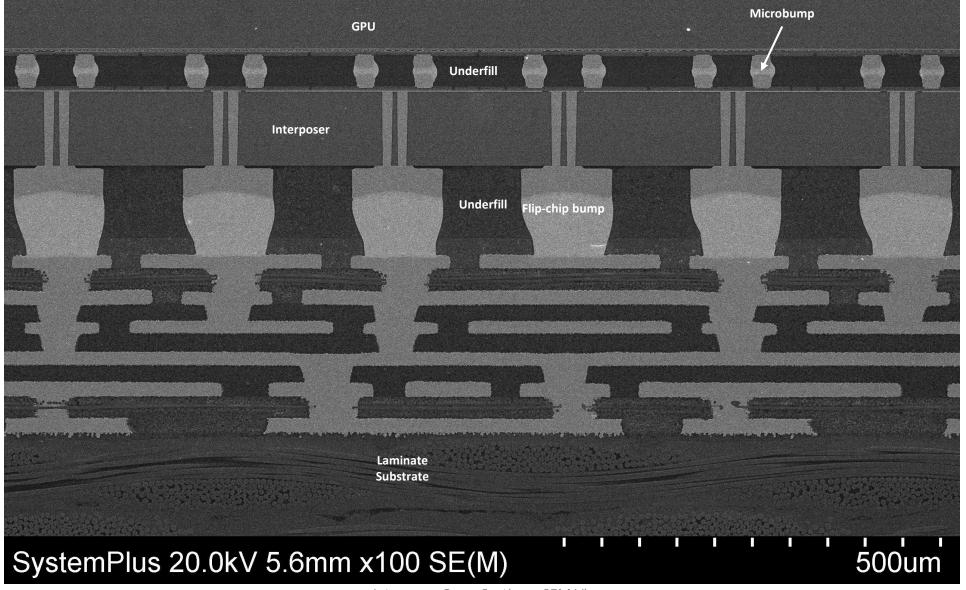

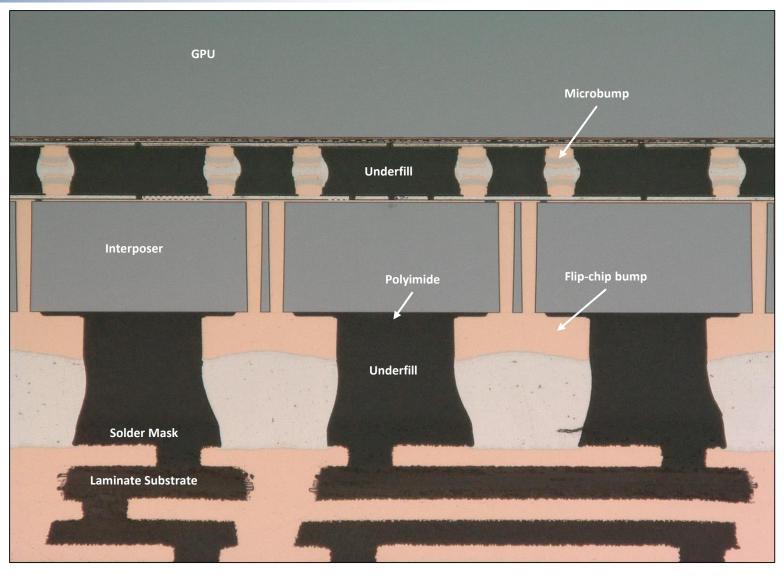

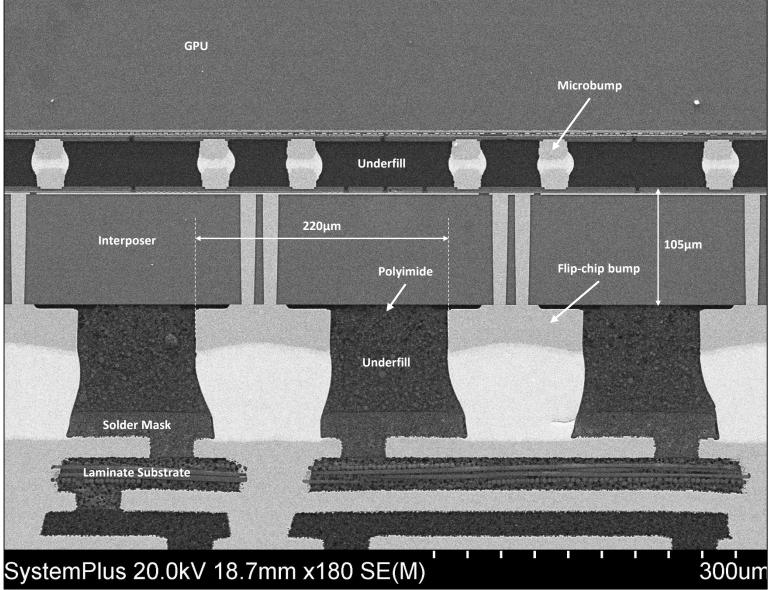

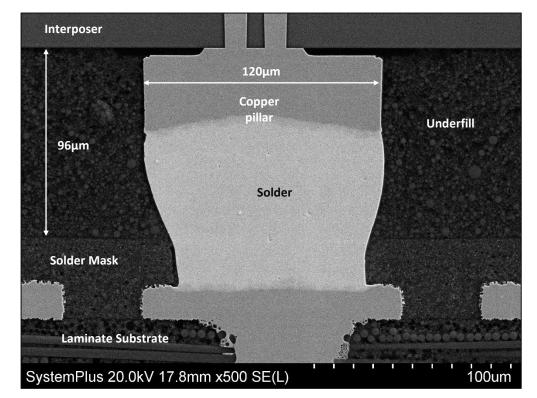

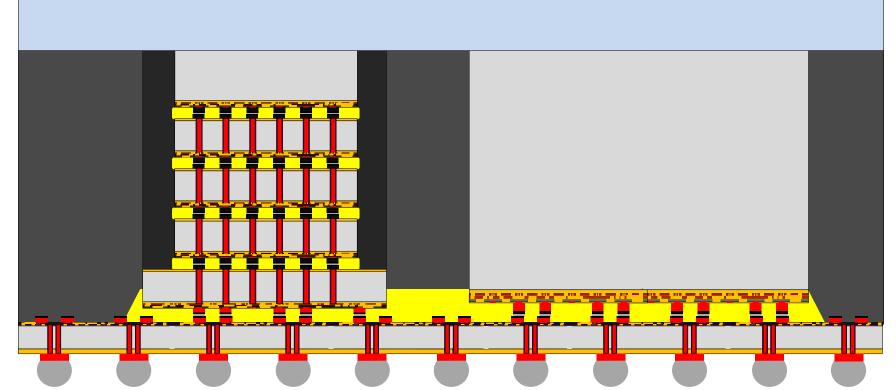

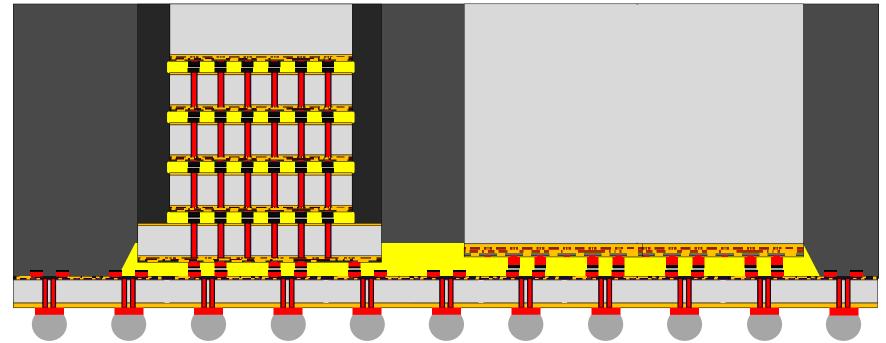

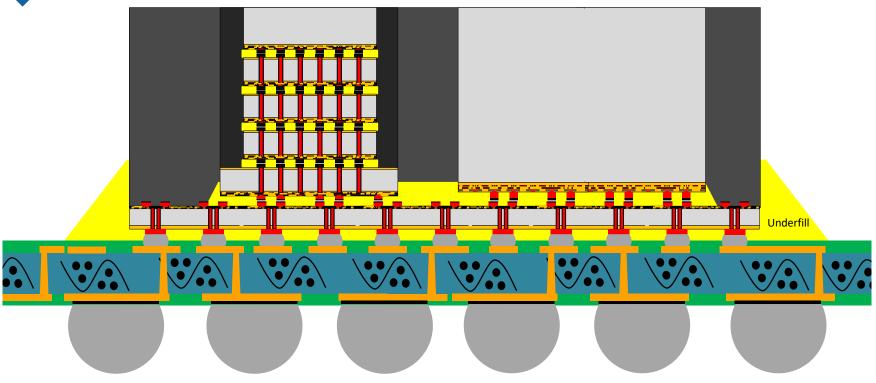

HBM stack and GPU die are bonded on an interposer which is flip-chipped to the PCB substrate.

BGA bump pitch: 1000μm

BGA ball diameter: 700μm

Flip-Chip bump pitch: 220μm

• Flip-Chip bump diameter: 120μm

### **Board Cross-Section**

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

### **Board Cross-Section**

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

Package Cross-Section – Optical View ©2018 by System Plus Consulting

• Warpage Estimation: 40 μm

### Samsung 1GB HBM2 – Driver Die View & Dimensions

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

12.4 mm

Die Area: 102.9 mm<sup>2</sup>

(12.4x8.3 mm)

Nb of PGDW

per 12-inch wafer: 604

Pad number: 116

Bridge Bumps Number:

2,400

Bridge Bumps Area:

6.76 mm<sup>2</sup> (6.04 x 1.12 mm)

Bridge Bumps Fill Factor:

6.5 %

Bumps Number: 1,143

## Samsung 1GB HBM2 – Driver Bumps

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

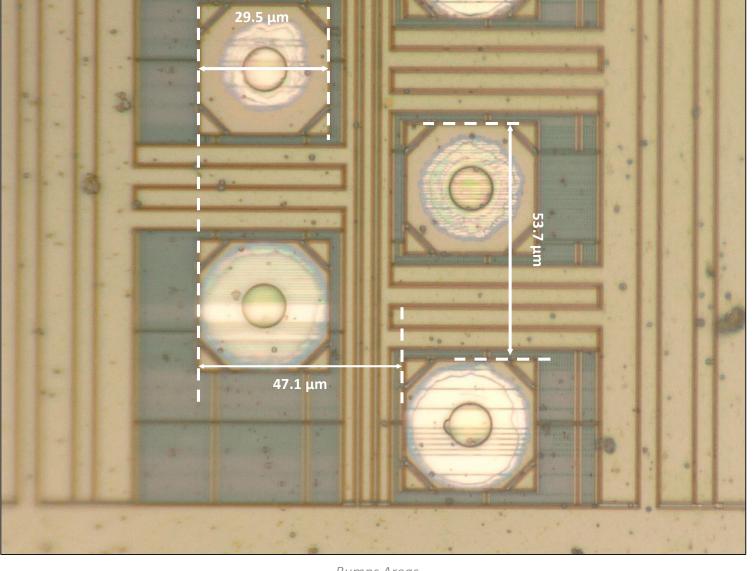

Die Overview ©2018 by System Plus Consulting

μBump pitch: 47.1 μm

μBump diameter: 29.5 μm

### Samsung 1GB HBM2 – DRAM Die View and Dimensions

11.5mm

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

Die Overview ©2018 by System Plus Consulting

86mm<sup>2</sup> Die Area:

(11.5x7.5mm)

Nb of PGDW per 12-inch wafer: 728

Pad number: 126

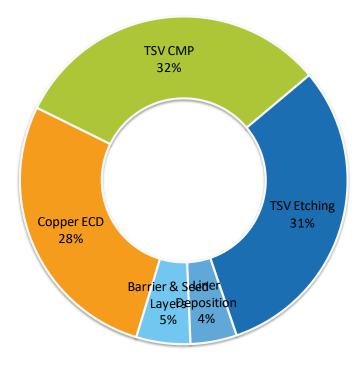

TSV number: 4,830

## Samsung 1GB HBM2 – DRAM Die Marking

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

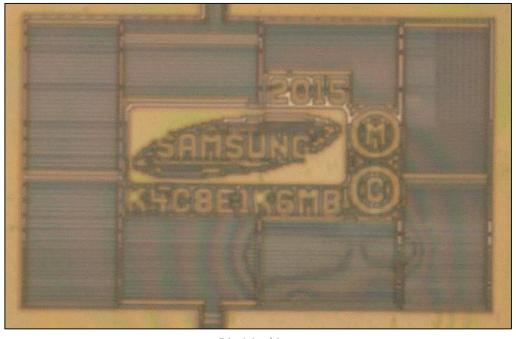

Die Marking ©2018 by System Plus Consulting

The die marking includes the logo of Samsung and:

K4C8E1K6MB

2015

## Samsung 1GB HBM2 – DRAM Die – μBumps & TSVs

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

Die Overview

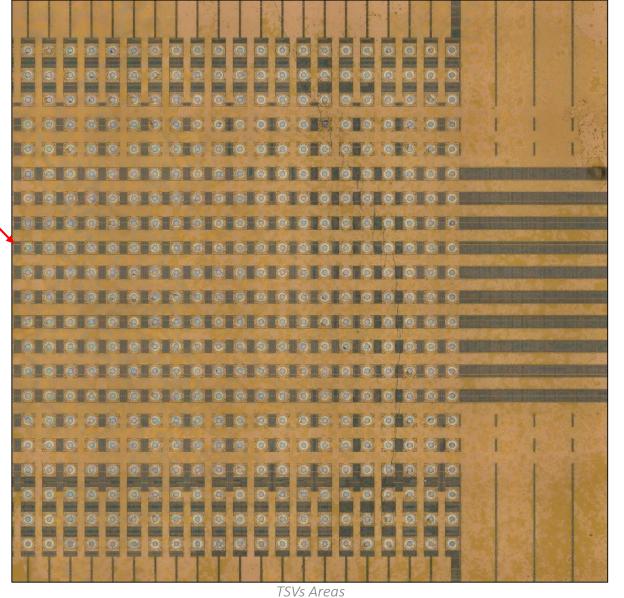

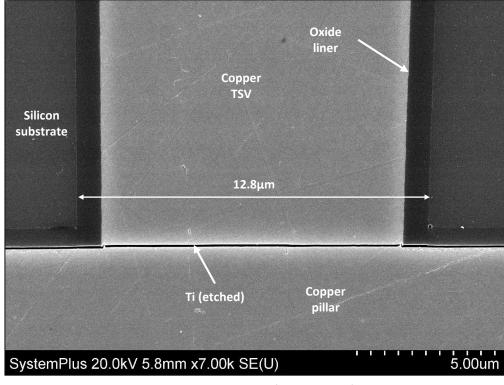

• TSVs are located at the center of the dies.

©2018 by System Plus Consulting

# Samsung 1GB HBM2 – DRAM Die – μBumps & TSVs

Overview / Introduction

Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

**Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

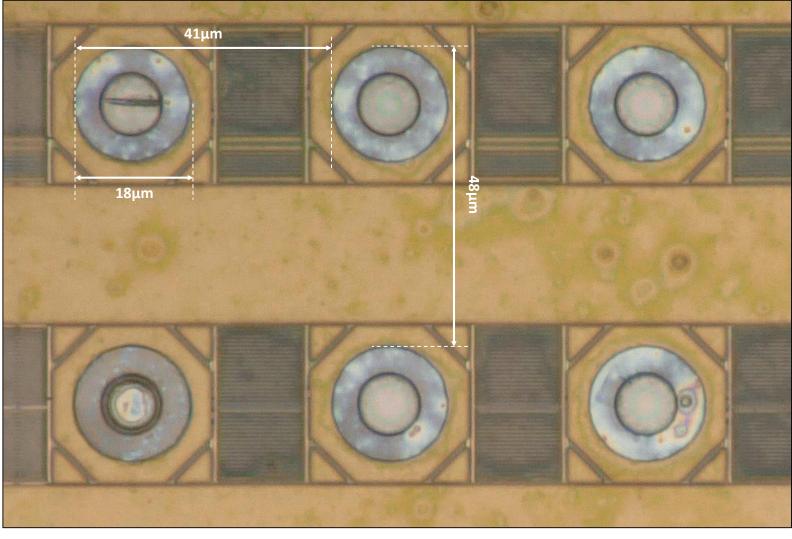

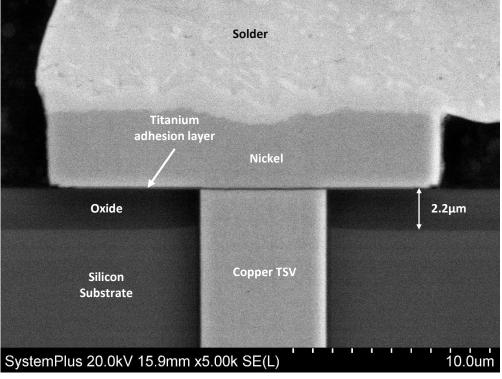

μBump & TSV pitch: 41μm

μBump diameter: 18μm

TSVs Areas ©2018 by System Plus Consulting

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- ► Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### Manufacturing Process Flow

#### Cost Analysis

Selling Price Analysis

#### Feedback

About System Plus

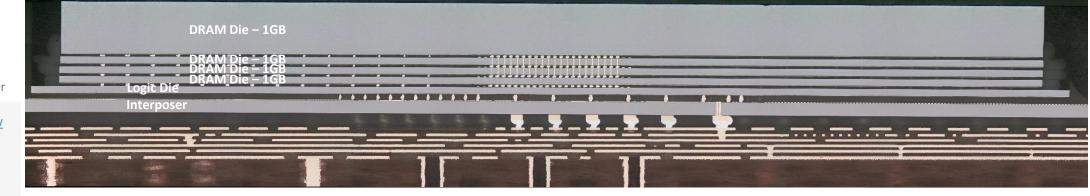

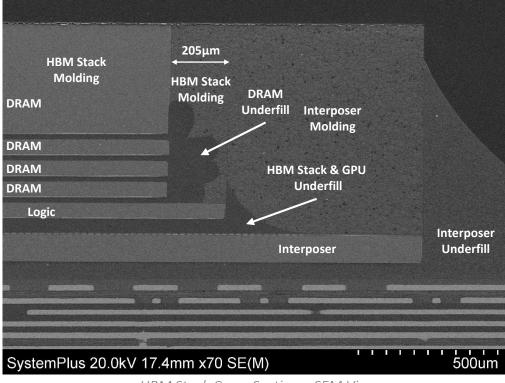

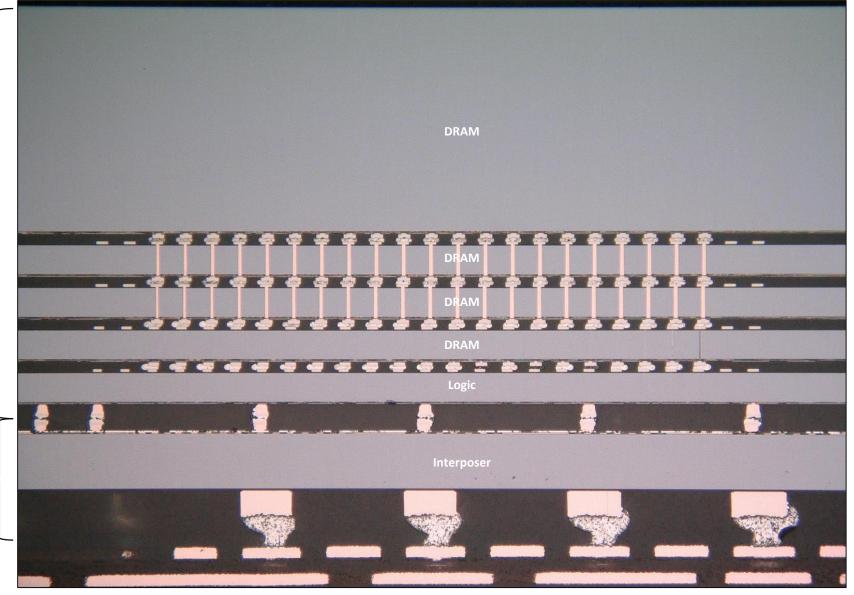

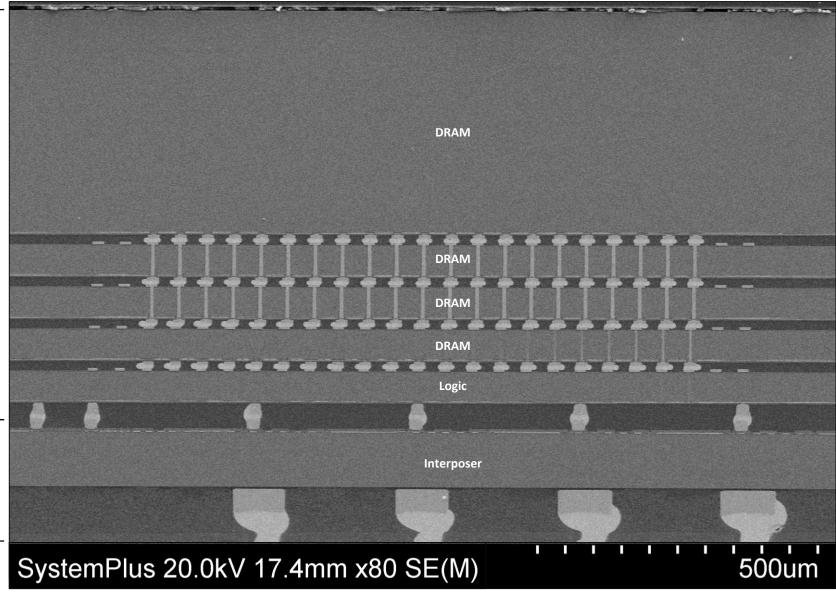

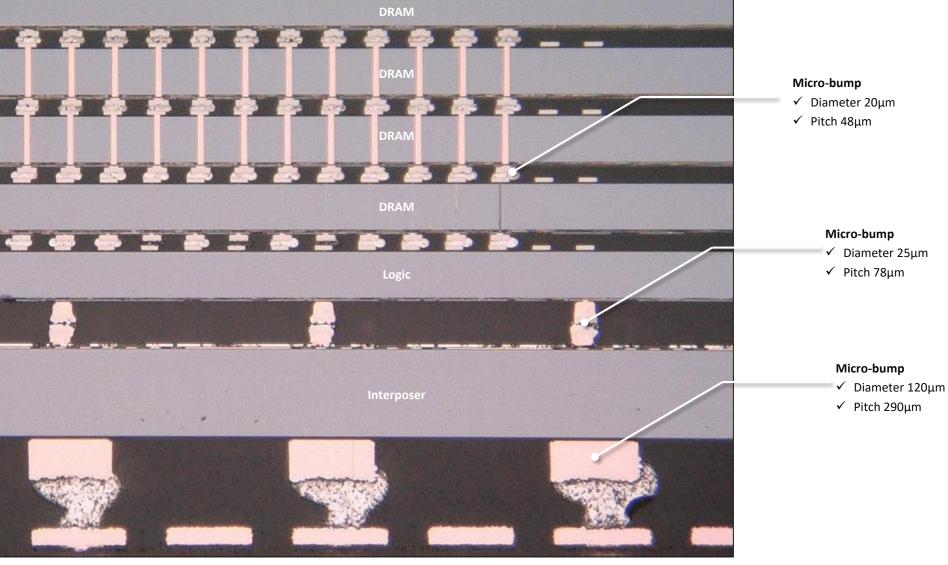

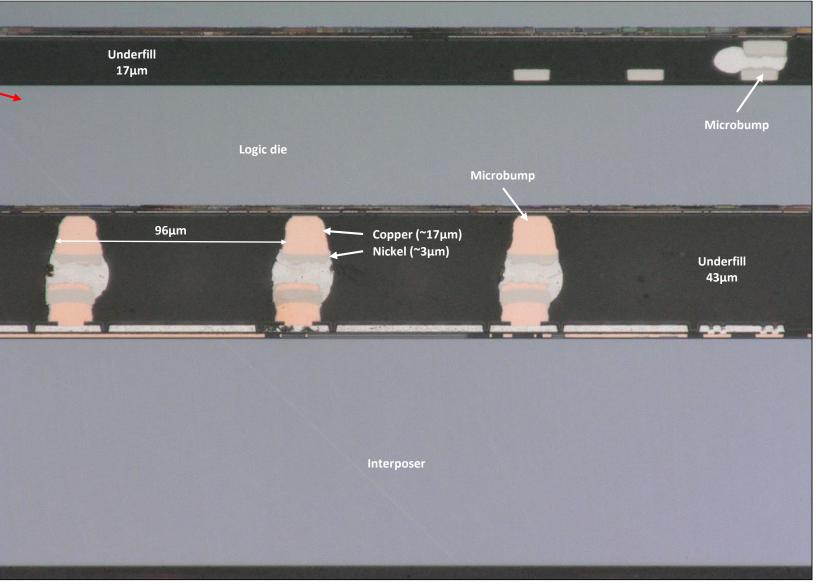

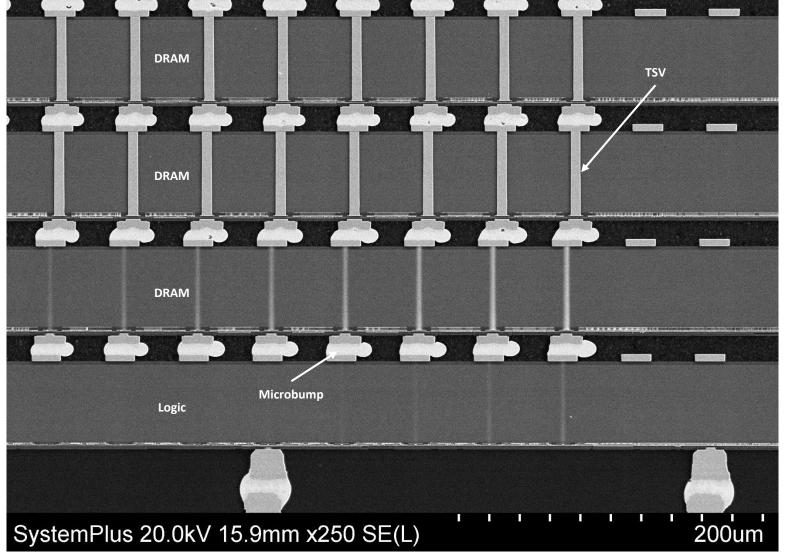

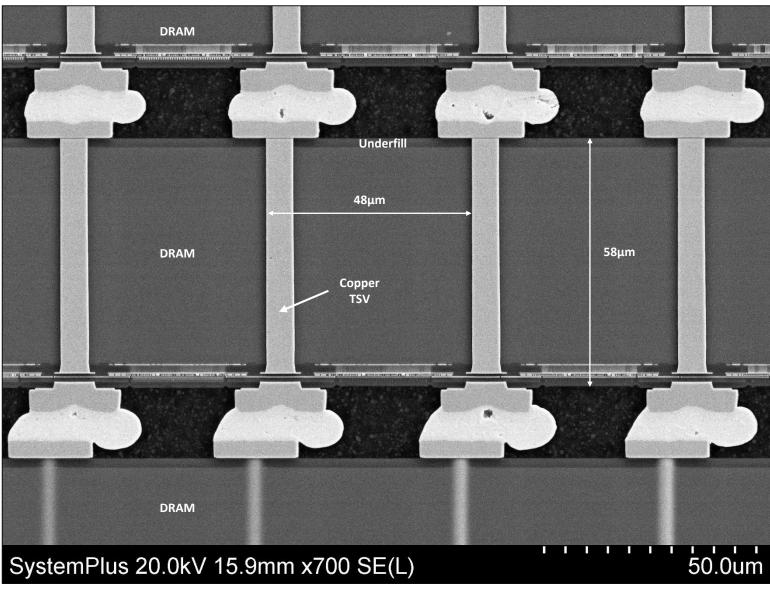

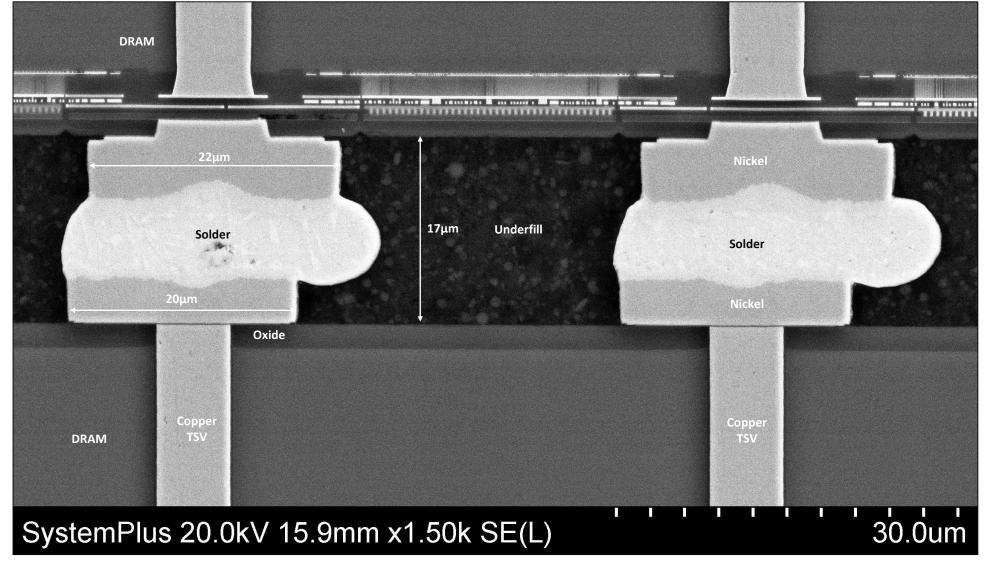

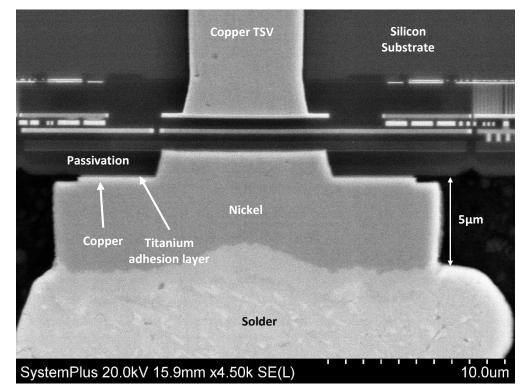

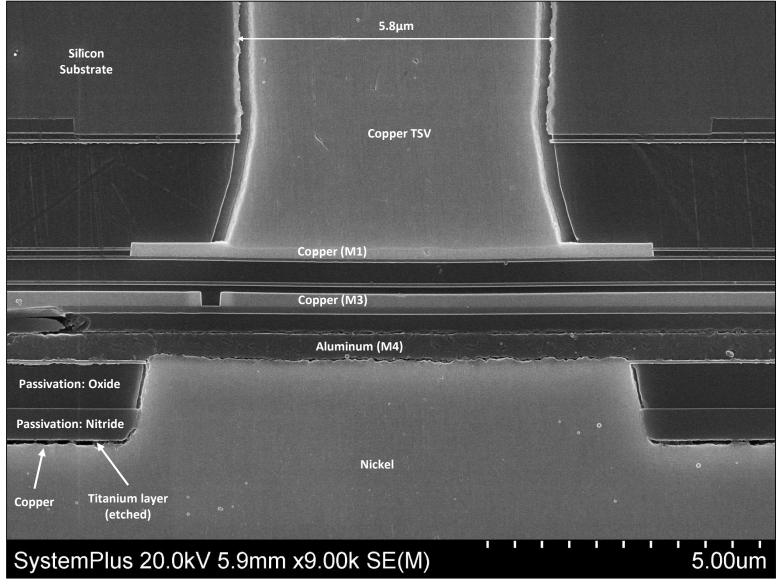

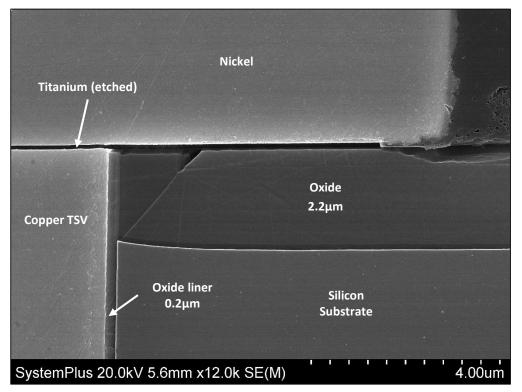

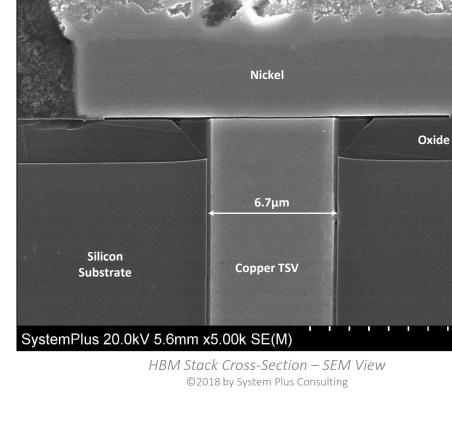

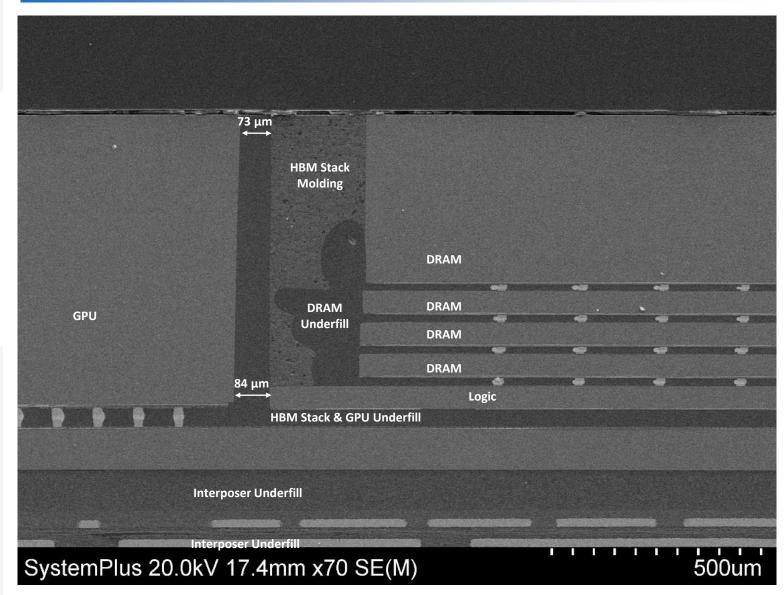

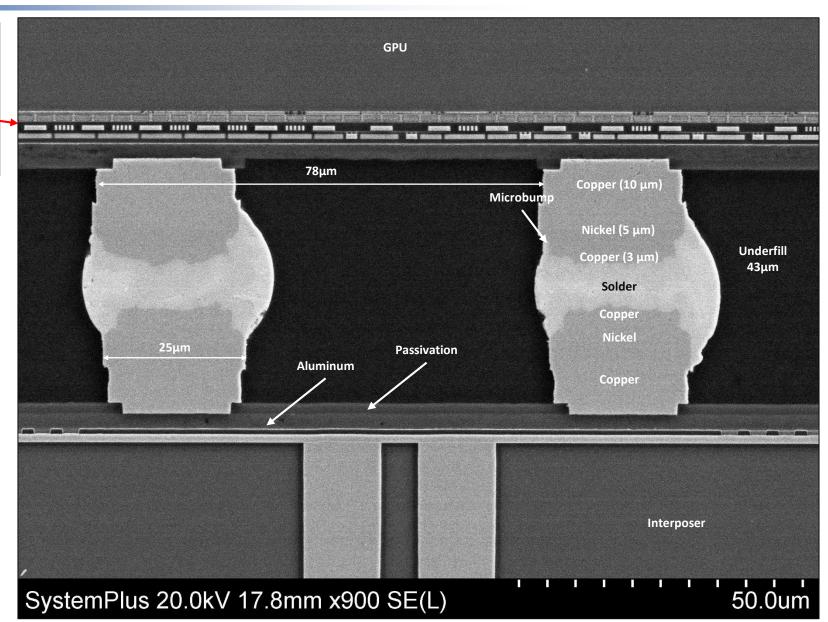

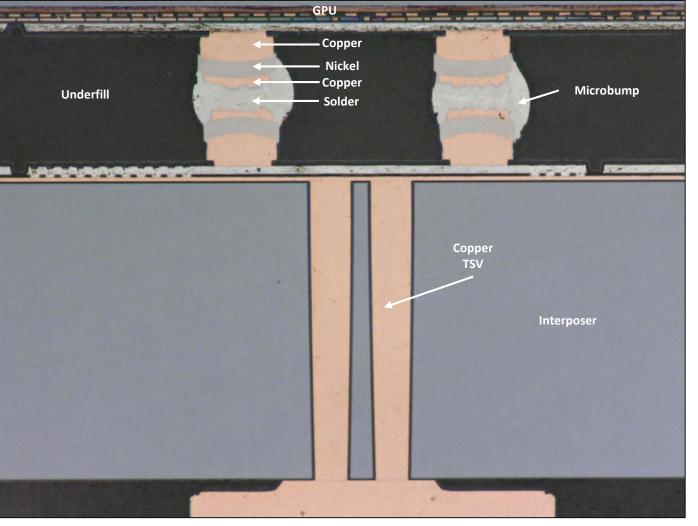

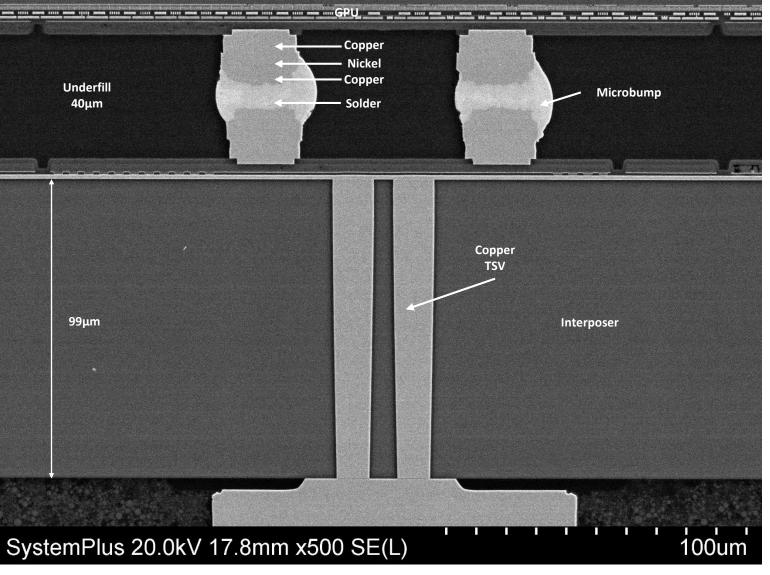

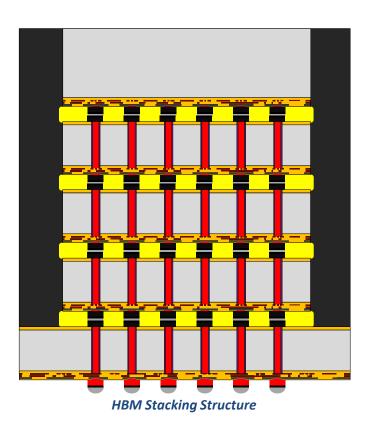

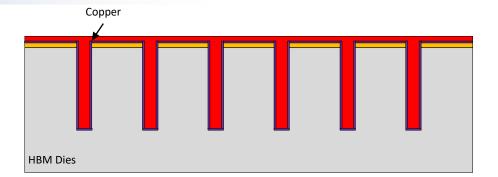

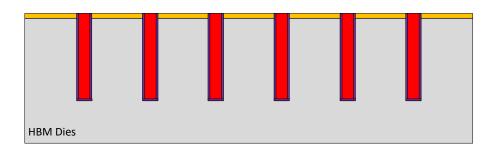

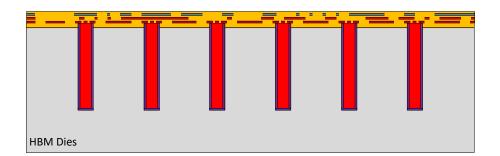

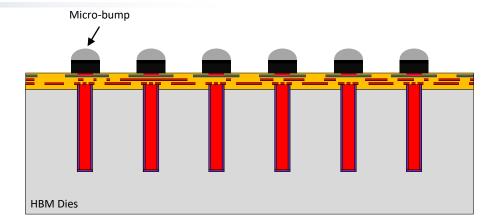

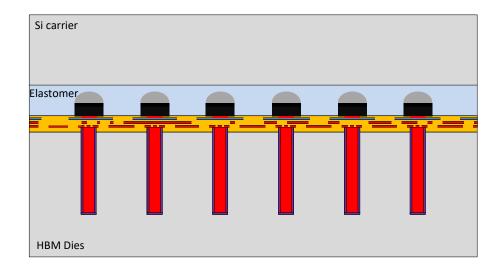

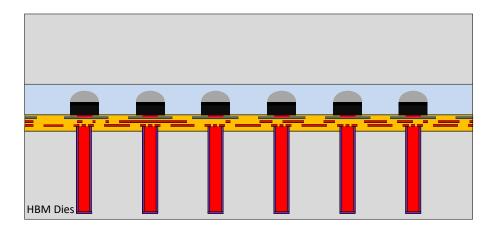

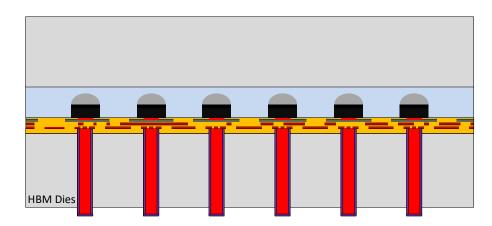

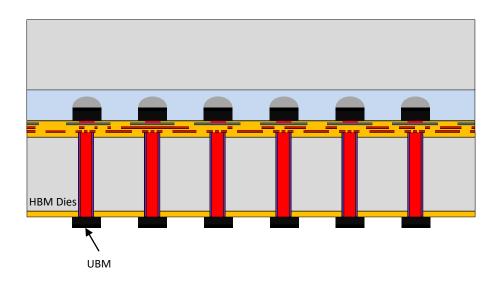

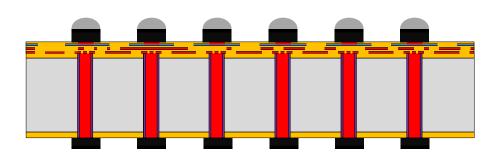

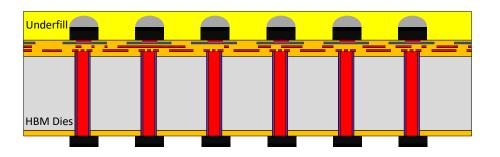

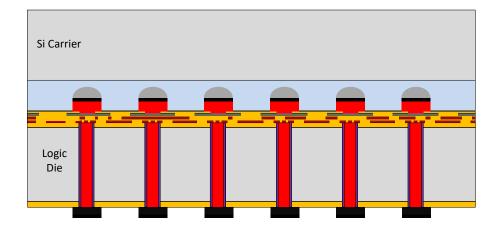

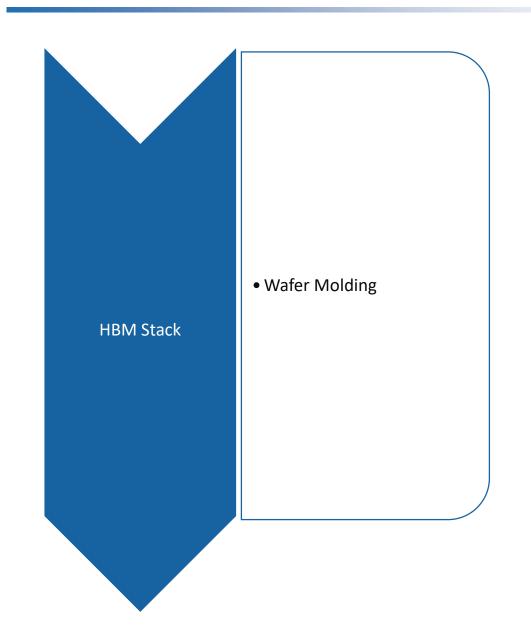

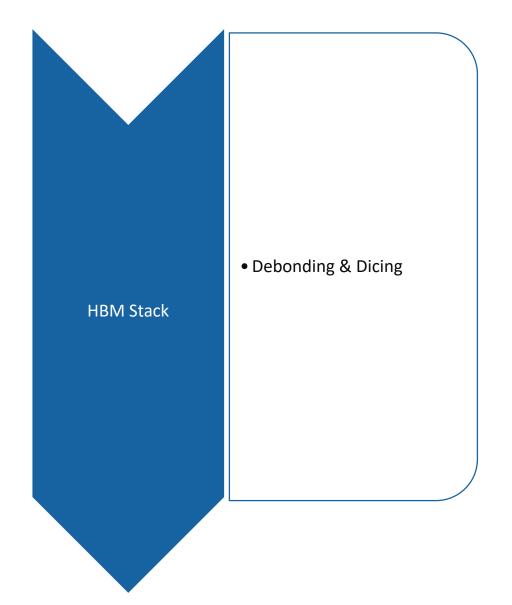

### Package Cross-Section – HBM2 Stack

- HBM stacks are flip-chipped on the interposer at the wafer-level though microbumps.

- HBM stacks include 5 dies: 4 1GB DRAM + 1 logic (buffer) die

HBM Stack Cross-Section – Optical View ©2018 by System Plus Consulting

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- Cross-Section HBM Stack

- GPU Die

- Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

HBM Stack Cross-Section - SEM View ©2018 by System Plus Consulting

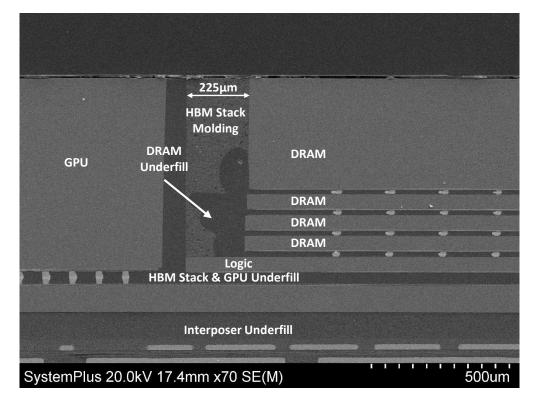

- The HBM stack is molded on the side.

- The side mold is 205-225µm wide.

- DRAM dies do not share exactly the same size, they are diced before being bonded together.

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- ► Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

#### **HBM Stack**

4x DRAM Die + 1x Logic Die TSV and microbumps connection

#### Interposer

TSV, redistribution layers and microbumps connections

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- ► Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

#### **HBM Stack**

4x DRAM Die + 1x Logic Die TSV and microbumps connection

#### Interposer

TSV, redistribution layers and microbumps connections

HBM Stack Cross-Section - SEM View ©2018 by System Plus Consulting

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- ► Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

HBM Stack Cross-Section – Optical View ©2018 by System Plus Consulting

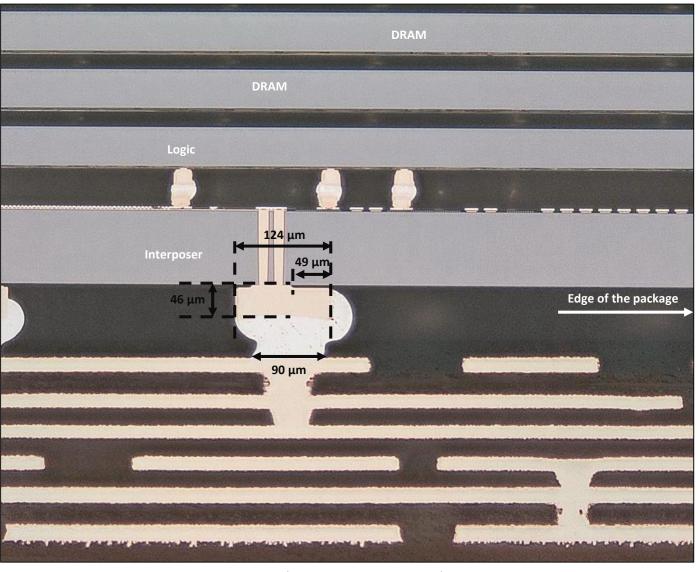

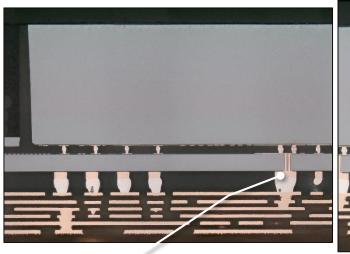

### Package Cross-Section — Substrate — Interposer

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- ► Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

**Cost Analysis**

Selling Price Analysis

Feedback

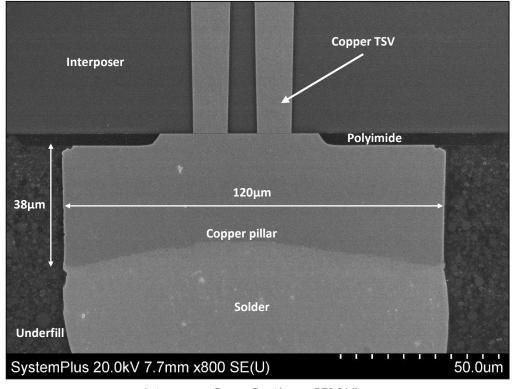

- Under the HBM memory, the bump are larger than under the GPU.

- We assume that the bumps are tweaks to help manage the warpage.

- The bump and the polyimide extends 25 µm in the edge direction.

HBM Stack Cross-Section – Optical View ©2018 by System Plus Consulting

## Package Cross-Section – Interposer – HBM2 Stack

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- ► Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

DRAM

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- ► Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- ► Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

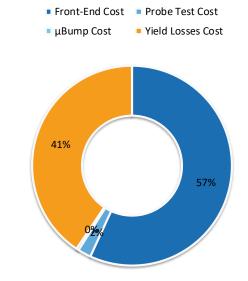

- HBM dies thickness (excepted top die): 56µm

- HBM stack TSV & microbumps pitch: 48µm

- Underfill thickness: 17μm

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- ► Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

**Cost Analysis**

Selling Price Analysis

Feedback

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### Manufacturing Process Flow

Cost Analysis

Selling Price Analysis

Feedback

HBM Stack Cross-Section – SEM View ©2018 by System Plus Consulting

HBM Stack Cross-Section – SEM View ©2018 by System Plus Consulting

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- ► Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

HBM Stack Cross-Section – SEM View ©2018 by System Plus Consulting

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- ► Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

10.0um

### NVIDIA GV100 – GPU Die View and Dimensions

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

25.65 mm

828.5 mm<sup>2</sup> Die Area: (32.3 x 25.7 mm)

Nb of PGDW per 12-inch wafer: 64

GPU-HBM Bumps Area: 4 x 7.32 mm<sup>2</sup>

(6.10 x 1.20 mm)

GPU-HBM Bumps Number: 2,352

GPU-HBM Bumps Fill Factor: 3.5 %

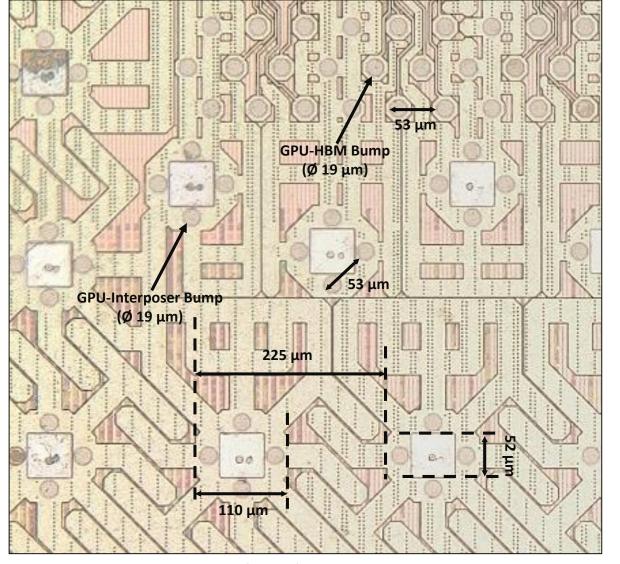

### NVIDIA GV100 – GPU Die Bumps

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

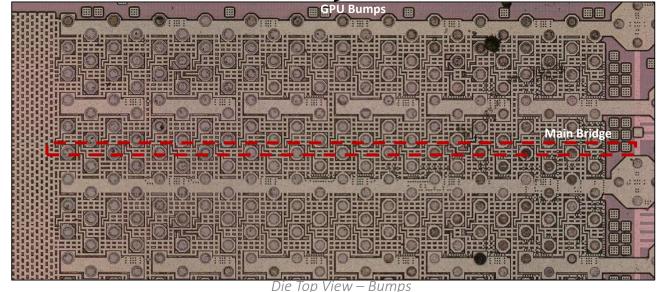

Die Overview ©2018 by System Plus Consulting

GPU-HBM bumps are located at four sites on the die.

53 μm Bump pitch:

Bump diameter: 19 μm

For the probe testing, each Al pad are opened.

Die Top View – Bumps ©2018 by System Plus Consulting

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

### Package Cross-Section – GPU

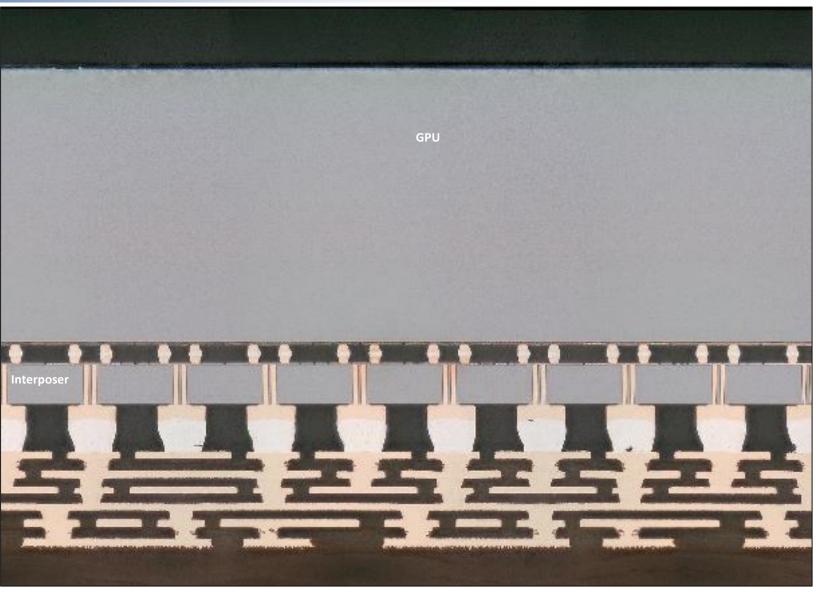

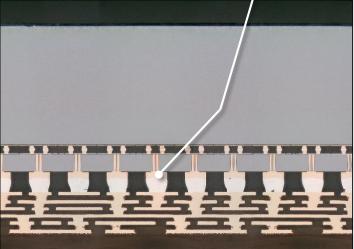

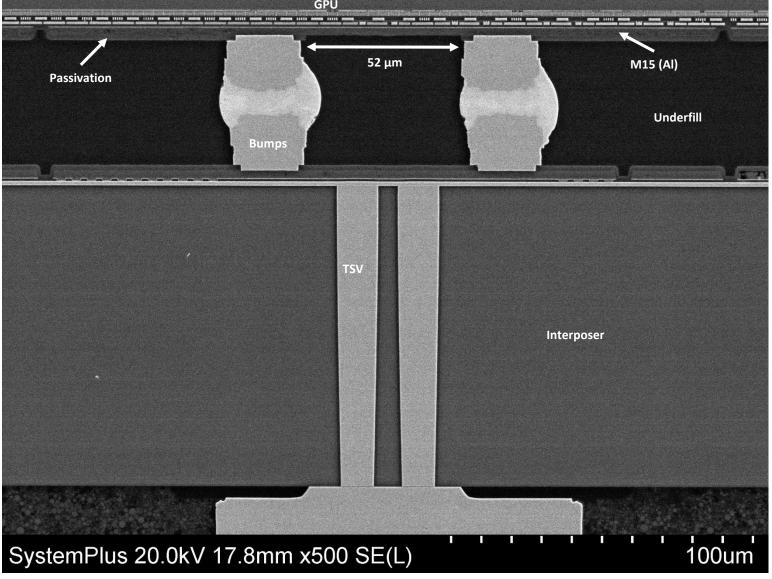

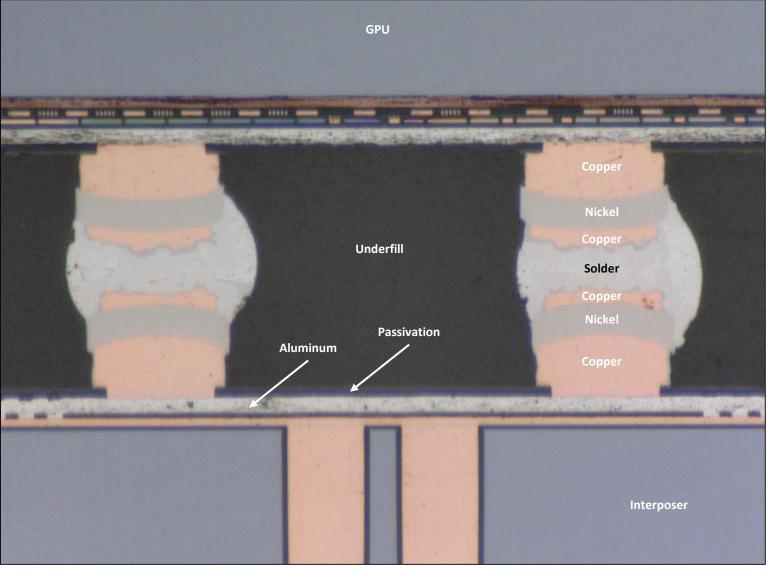

The GPU die is flip-chipped on the interposer at the wafer-level though microbumps.

GPU Cross-Section – Optical View ©2018 by System Plus Consulting

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- GPU Die

- Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

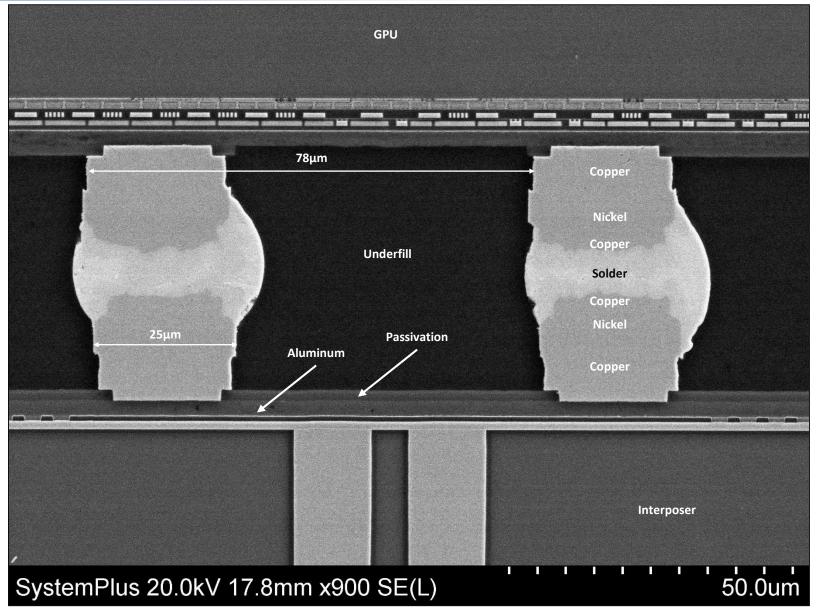

### Package Cross-Section — GPU

- The GPU and the HBM stack package are placed side by side in an underfill.

- The space between the dies are  $70 - 80 \mu m$  wide.

### Package Cross-Section – GPU

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- ► Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### Manufacturing Process Flow

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

#### **GPU**

1x GPU Die \_\_

TSV and microbumps connection

### Interposer

TSV, redistribution layers and microbumps connections

### Package Cross-Section – GPU

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- ► Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### Manufacturing Process Flow

Cost Analysis

Selling Price Analysis

Feedback

GPU Cross-Section – Optical View ©2018 by System Plus Consulting

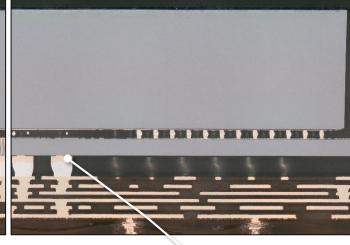

## Package Cross-Section — Substrate — Interposer

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

#### Overview / Introduction

#### Company Profile & Supply Chain

#### **Physical Analysis**

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- Cross-Section HBM Stack

- GPU Die

- Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

### Package Cross-Section — Substrate — Interposer

Interposer Cross-Section – SEM View ©2018 by System Plus Consulting

#### Micro-bump

- ✓ Diameter 120 µm

- ✓ Pitch 225 µm

- ✓ Left Width 41 µm

- ✓ Right Width 31 µm

#### Micro-bump

- ✓ Diameter 120 µm

- ✓ Pitch 225 µm

- ✓ Left Width 24 µm

- ✓ Right Width 49 µm

Interposer Cross-Section – SEM View ©2018 by System Plus Consulting

#### Micro-bump

- ✓ Diameter 120 µm

- ✓ Pitch 225 µm

- ✓ Left Width 50 µm

- ✓ Right Width 28 µm

- Under the GPU, three type of bumps are used.

- The bumps could be regrouped into two group: One in stress region and one in High power region.

- In the stress region, depending on the position of the edge, the bumps is extended in the edge direction.

- In the high power region, the bumps are smaller.

- We assume that the bumps are tweaks to help manage the warpage.

## Package Cross-Section – Interposer – GPU

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- GPU Die

- Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- GPU Die

- Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

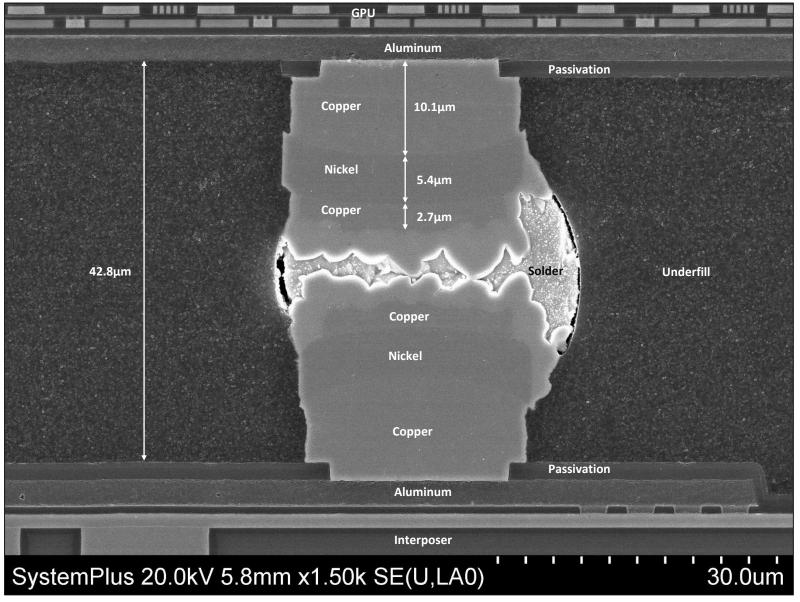

### Die Cross-Section –GPU

Die Top View – Bumps ©2018 by System Plus Consulting

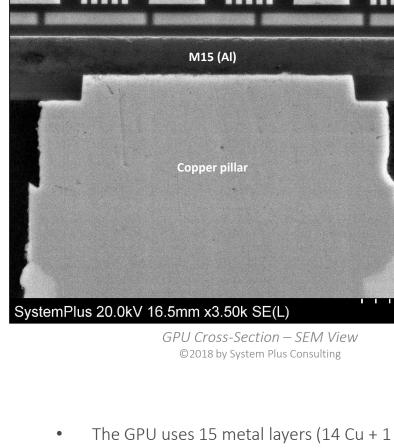

The passivation on top of aluminum pads are opened to provide a spot to perform the wafer probe testing.

Interposer Cross-Section – SEM View ©2018 by System Plus Consulting

### Die Cross-Section – GPU

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

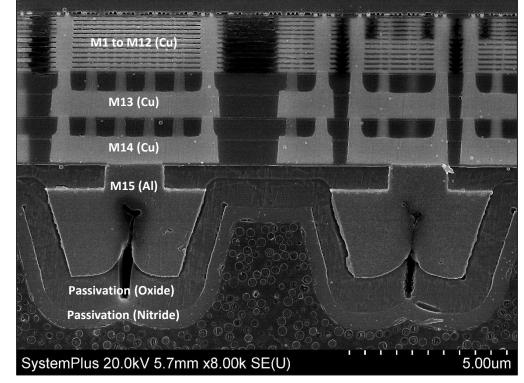

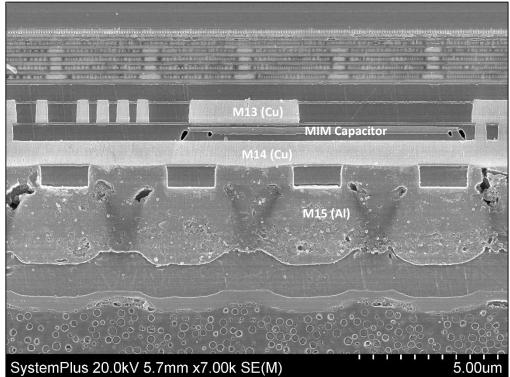

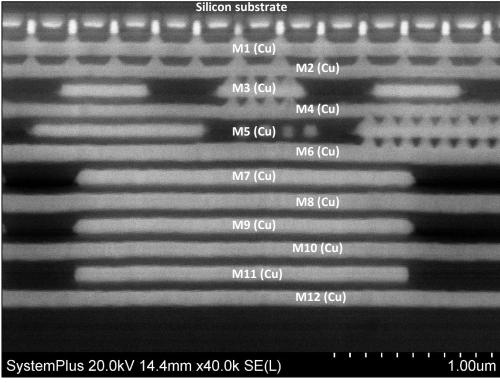

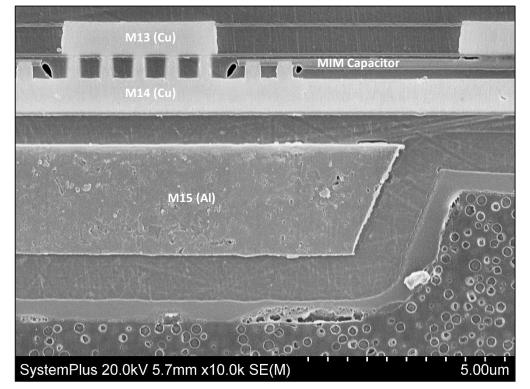

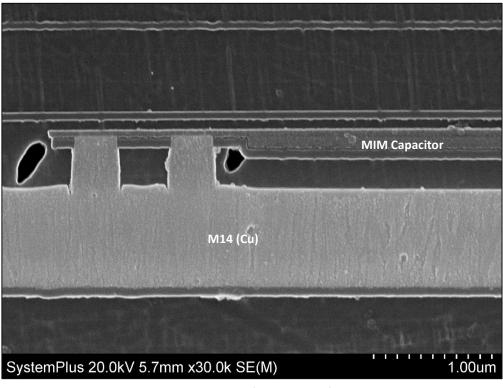

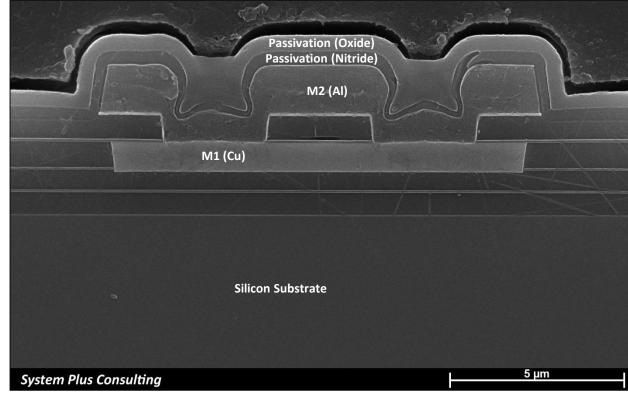

The GPU uses 15 metal layers (14 Cu + 1 Al)

GPU Cross-Section – SEM View ©2018 by System Plus Consulting

10.0um

### Die Cross-Section – GPU

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

GPU Cross-Section – SEM View ©2018 by System Plus Consulting

### Die Cross-Section – GPU

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

About System Plus

GPU Cross-Section – SEM View ©2018 by System Plus Consulting

MIM capacitors are present between M13 and M14.

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

### **Manufacturing Process Flow**

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

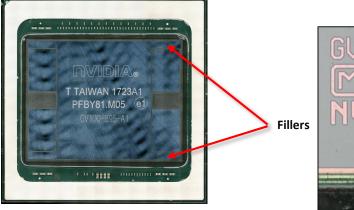

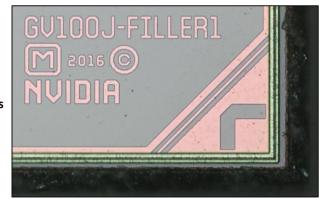

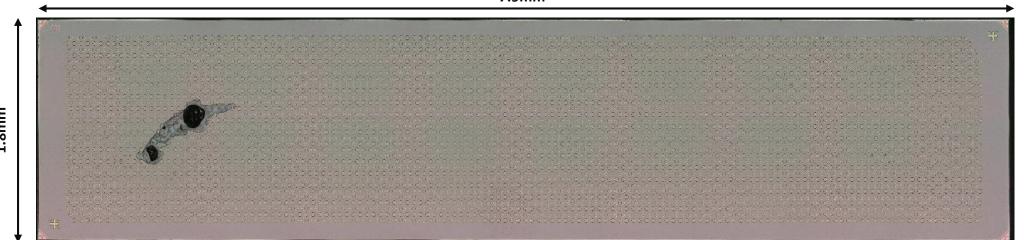

### Package Cross-Section – Filler

14.22mm<sup>2</sup>

(7.9x1.8mm)

Nb of PGDW per 12-inch wafer: 4,396

Die Area:

Die Marking ©2018 by System Plus Consulting

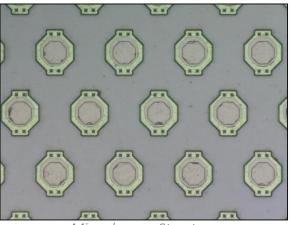

Micro bumps Structure ©2018 by System Plus Consulting

#### 7.9mm

Die Overview ©2018 by System Plus Consulting

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

### Package Cross-Section – Filler Cross-Section

The fillers use 2 metal layers and micro bumps connections.

Filler Cross-Section – SEM View ©2018 by System Plus Consulting

# NVIDIA GV100 – Interposer Die View and Dimensions

#### Overview / Introduction

### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- Interposer Die

- o Cross-Section Interposer

# **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

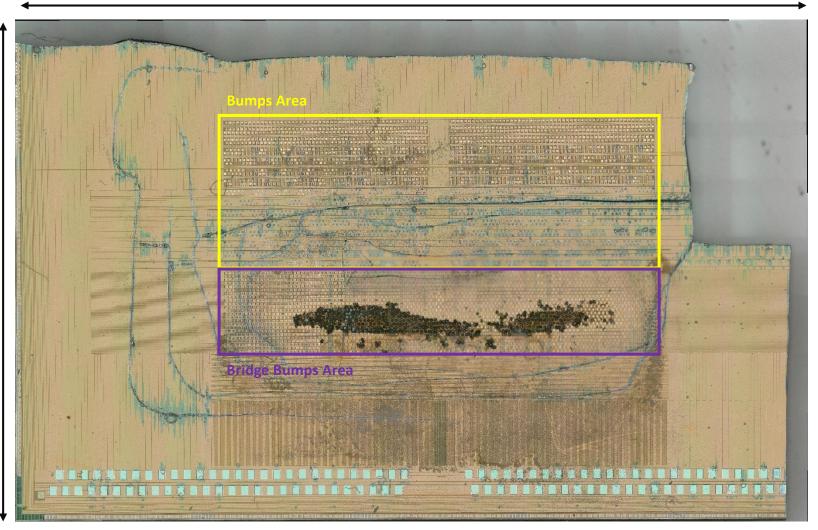

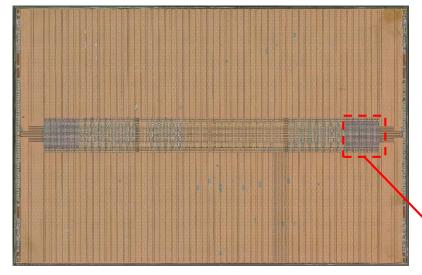

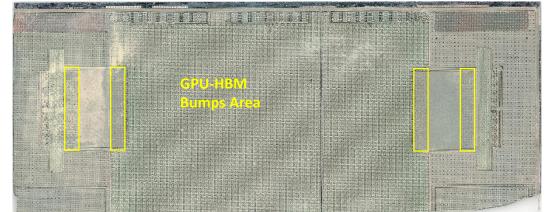

43.1 mm

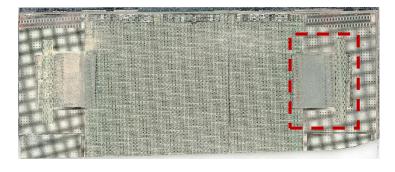

1,452 mm<sup>2</sup> Die Area: (43.1 x 33.7 mm)

Nb of PGDW per 12-inch wafer: 36

GPU-HBM Bumps Area: 8 x 7.32 mm<sup>2</sup> (6.10 x 1.20 mm)

**GPU-HBM Bumps Number:** 2,352

GPU-HBM Bumps Fill Factor: 4.0 %

Die Overview ©2018 by System Plus Consulting

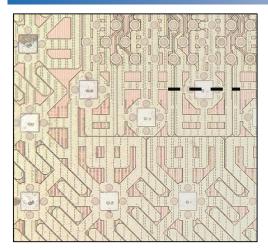

# NVIDIA GV100 – Interposer Die Overview

#### Overview / Introduction

### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- GPU Die

- o Cross-Section GPU

- o Filler Die

- Cross-Section Filler

- Interposer Die

- o Cross-Section Interposer

# Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

43.1 mm

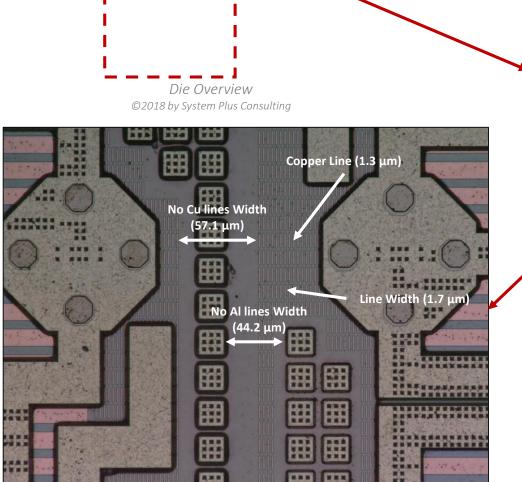

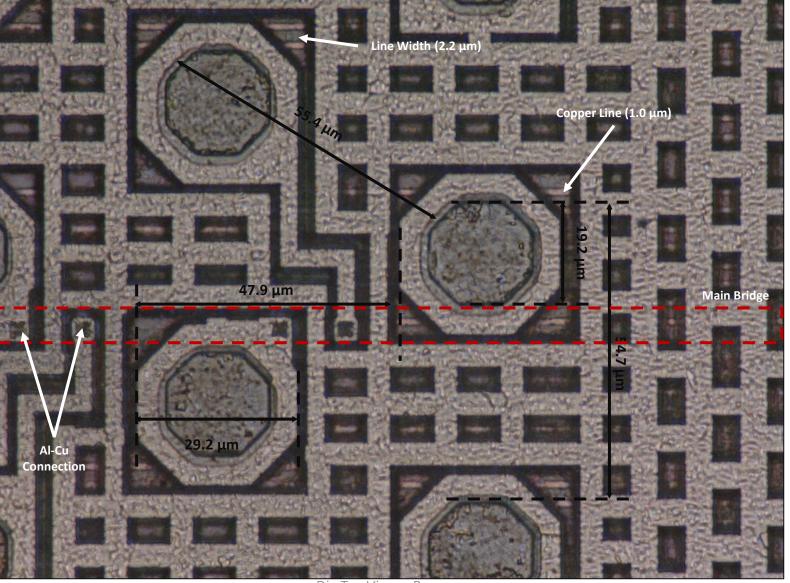

### **Reticle Stitching** Location

- The die is about 1.5 times large than the full reticle size.

- The second generation of CoWoS process (CoWoS-2) use a two-mask stitching photolithography to fabricate such large interposer.

- In this way, TSMC is able to pack more transitors in a CoWoS package besides the device shrink by Moore's law.

**Reticle Field Outline** 25.66 x 33.7 mm

Die Overview ©2018 by System Plus Consulting

# NVIDIA GV100 – Interposer Die Overview

The state of the s

#### Overview / Introduction

### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- o Cross-Section Interposer

#### **Manufacturing Process Flow**

**Cost Analysis**

Selling Price Analysis

Feedback

**About System Plus**

Die Overview ©2018 by System Plus Consulting

No Copper or aluminum lines cross the reticle stitching area.

# NVIDIA GV100 – Interposer Die Bumps

#### Overview / Introduction

### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- Interposer Die

- o Cross-Section Interposer

# **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

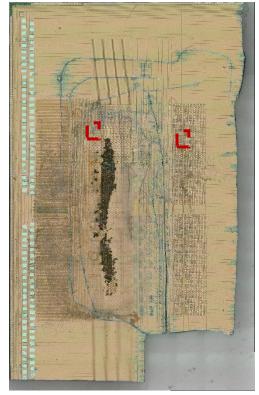

Die Overview ©2018 by System Plus Consulting

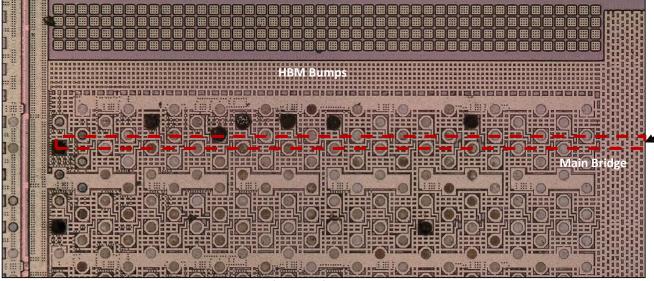

The bridge bumps are misaligned between the GPU and the HBM.

Die Top View – Bumps ©2018 by System Plus Consulting

### Company Profile & Supply Chain

Overview / Introduction

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- ▶ Interposer Die

- o Cross-Section Interposer

# **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

# NVIDIA GV100 – Interposer Die Bumps

Die Top View – Bumps ©2018 by System Plus Consulting

Die Top View – Bumps ©2018 by System Plus Consulting

©2018 by System Plus Consulting

# NVIDIA GV100 – Interposer Die Bumps

### Overview / Introduction

### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- ▶ Interposer Die

- o Cross-Section Interposer

# **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

**About System Plus**

Die Top View – Bumps ©2018 by System Plus Consulting

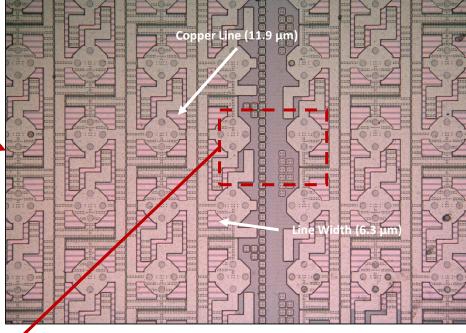

Bump pitch: 55 μm

Bump diameter: 19 μm

#### Overview / Introduction

### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- Cross-Section Interposer

#### Manufacturing Process Flow

**Cost Analysis**

Selling Price Analysis

Feedback

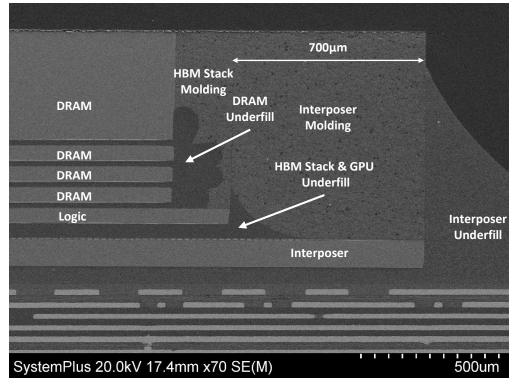

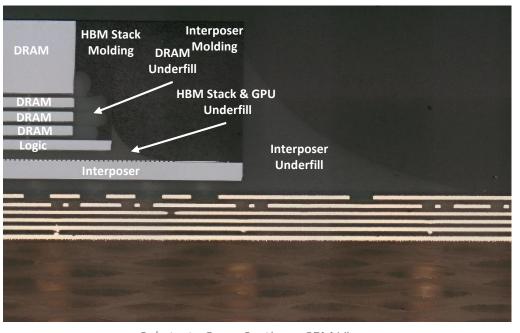

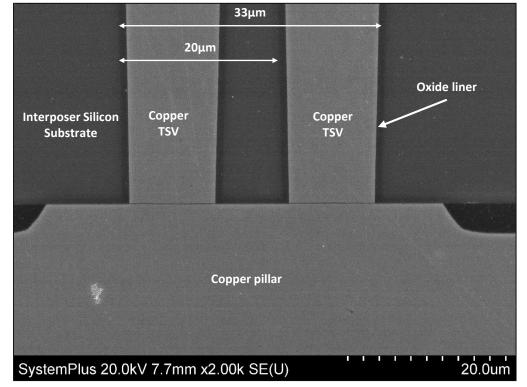

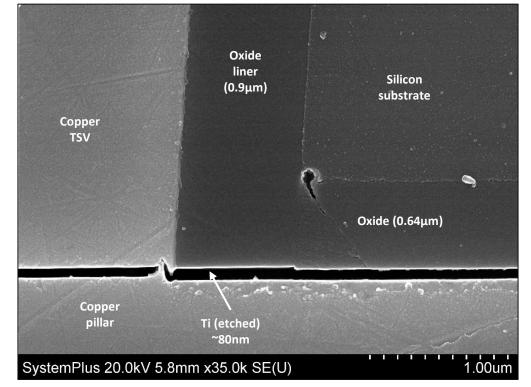

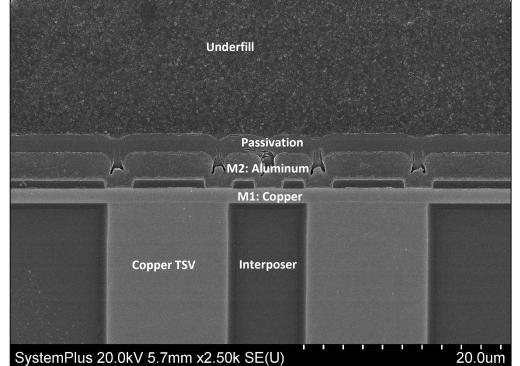

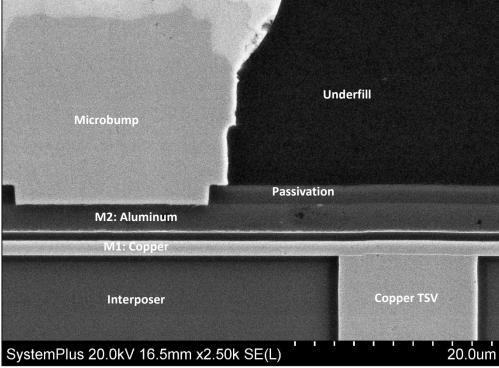

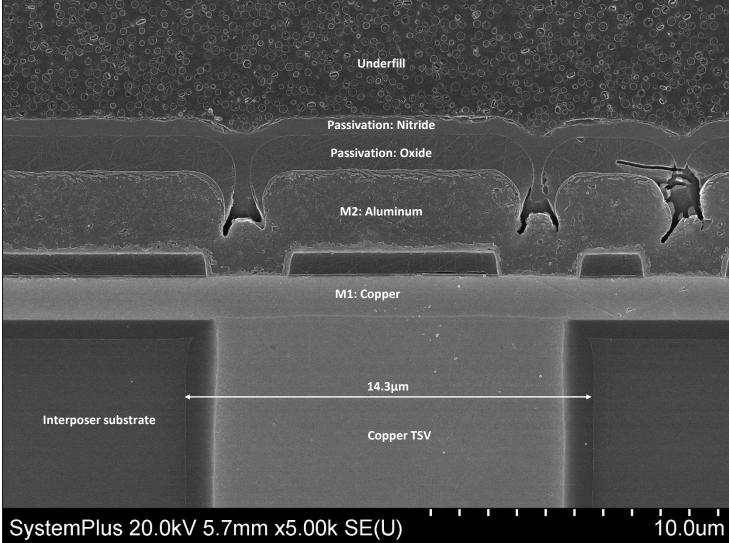

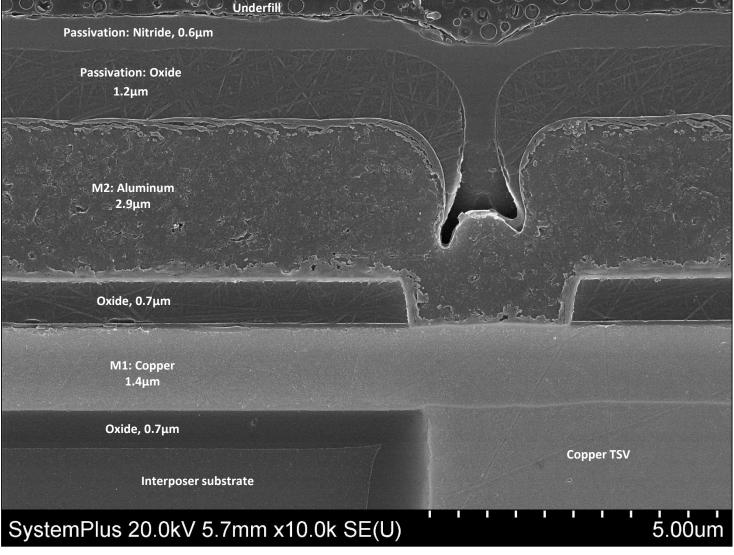

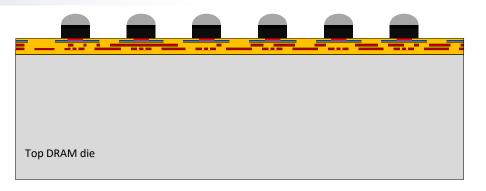

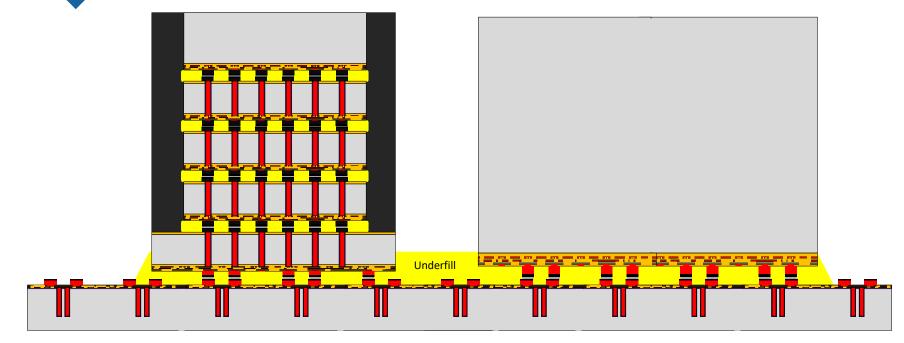

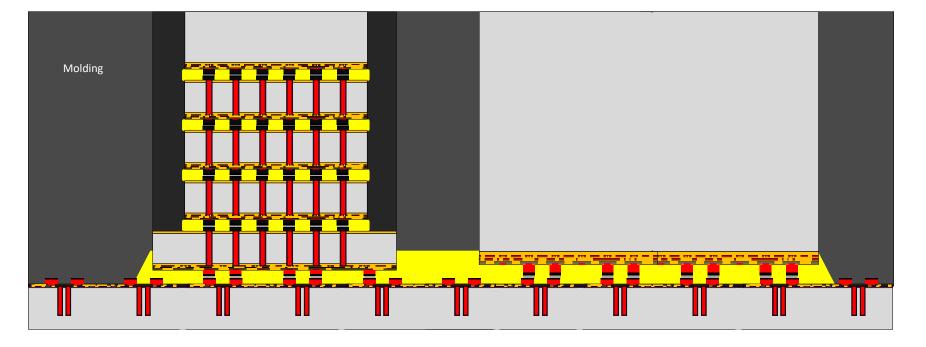

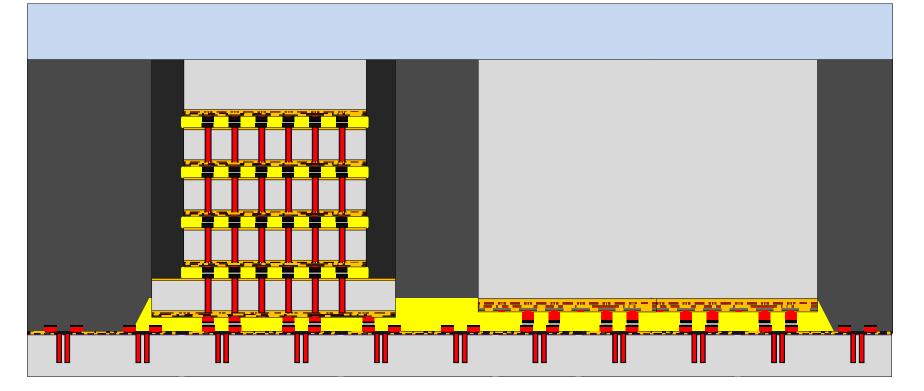

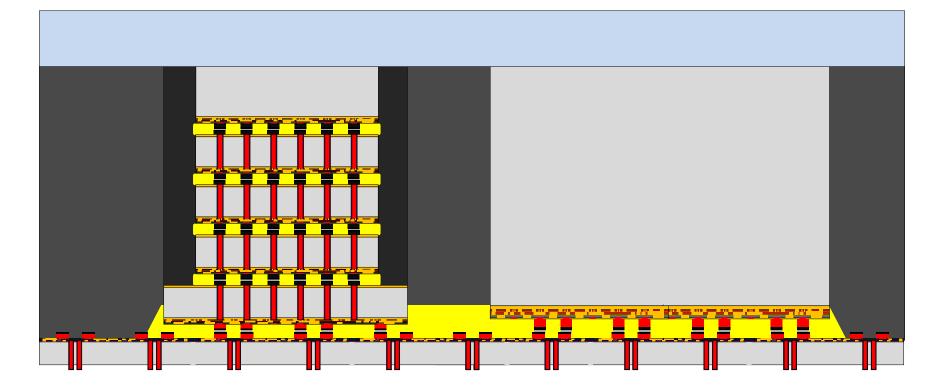

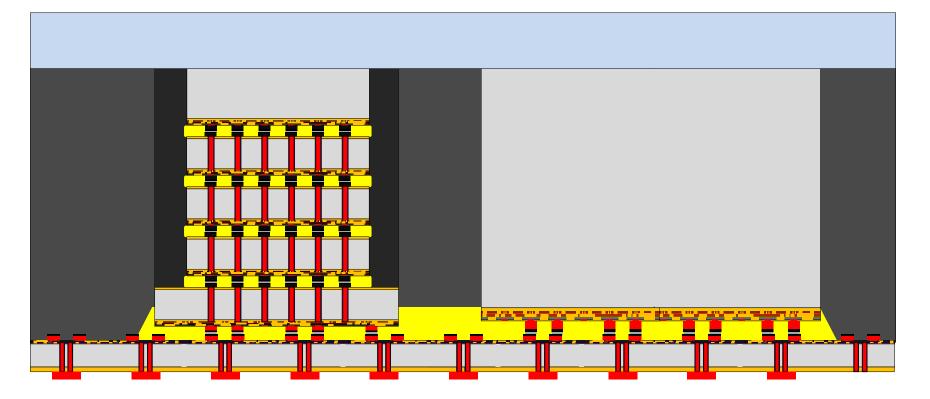

- The interposer with GPU and HBM Stacks is molded and grinded.

- 3 different underfills are used:

- Under the interposer

- Under GPU & HBM stack

- Under the DRAM dies in the HBM stack.

Substrate Cross-Section – SEM View ©2018 by System Plus Consulting

### Overview / Introduction

### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- Cross-Section Interposer

# Manufacturing Process Flow

Cost Analysis

Selling Price Analysis

Feedback

### Overview / Introduction

### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- Cross-Section Interposer

# **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

#### Overview / Introduction

### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- o DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- Cross-Section Interposer

# **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

#### Overview / Introduction

### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- o Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- Cross-Section Interposer

# **Manufacturing Process Flow**

**Cost Analysis**

Selling Price Analysis

Feedback

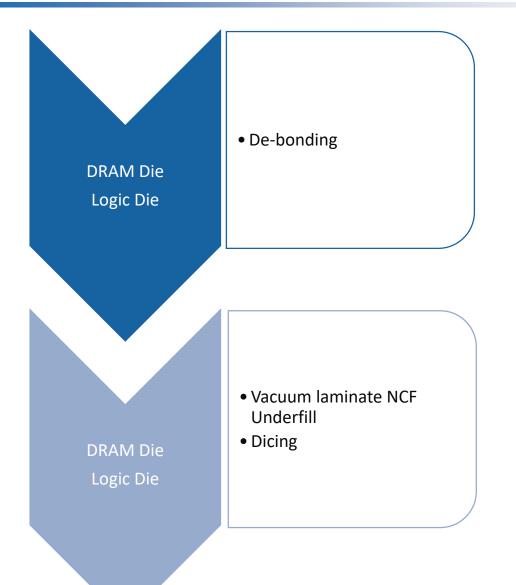

- Interposer thickness: 105µm

- Interposer bump pitch: 220µm

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Summary

- o Graphic Card Teardown

- o Package

- o Dies Size

- o Package Opening

- Substrate Cross-Section

- DRAM Dies

- o Cross-Section HBM Stack

- o GPU Die

- o Cross-Section GPU

- o Filler Die

- o Cross-Section Filler

- o Interposer Die

- ▶ Cross-Section Interposer

# **Manufacturing Process Flow**

Cost Analysis

Selling Price Analysis

Feedback

Interposer Cross-Section – Optical View ©2018 by System Plus Consulting

- Interposer copper pillar diameter: 120µm

- Underfill thickness: 96µm

#### Overview / Introduction

### Company Profile & Supply Chain

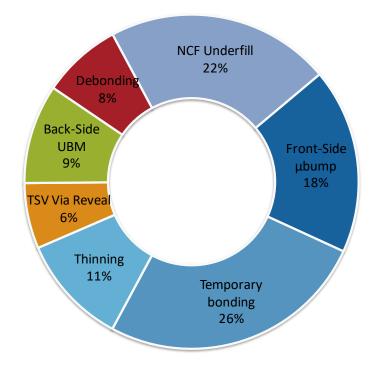

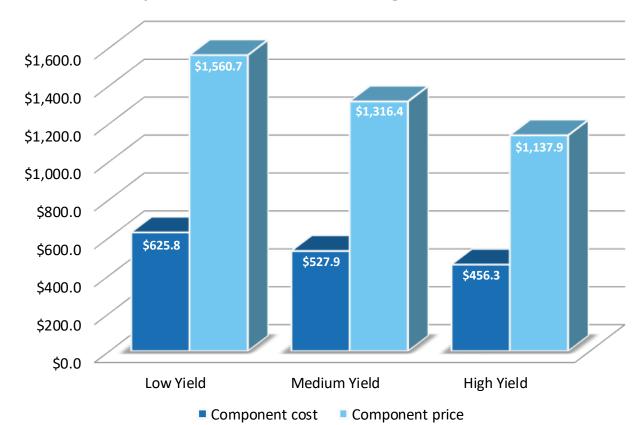

#### Physical Analysis