22 bd Benoni Goullin 44200 NANTES - FRANCE

## Versions of the Report

| Version                | Date       | Updates                                                         |  |

|------------------------|------------|-----------------------------------------------------------------|--|

| Preliminary            | 17/12/2020 | o Initial release of preliminary report                         |  |

| Technology<br>Analysis | 31/12/2020 | o Initial release of Technology Analysis report                 |  |

| Full Report<br>V1      | 15/01/2021 | o Initial release of Technology Analysis & Cost Analysis Report |  |

|                        |            |                                                                 |  |

## Table of Contents

| 0           | Executive :  | Summary                      |     |

|-------------|--------------|------------------------------|-----|

| 0           | Reverse Co   | osting Methodology           |     |

| mpany Pr    | ofile        |                              | 9   |

| 0           | Apple        |                              |     |

| 0           | Apple M1     | Architecture and Performance |     |

| nysical Ana | lysis        |                              | 16  |

| 0           | Apple Mad    | Mini Teardown                | 17  |

| 0           | Apple M1     | Package                      | 24  |

|             | ✓ P          | ackage Views                 |     |

|             | ✓ P          | ackage X-RAY Images          |     |

|             | ✓ P          | ackage Cross Section 1       |     |

|             | ✓ P          | ackage Cross Section 2       |     |

|             | ✓ P          | ackage Process               |     |

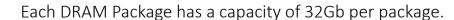

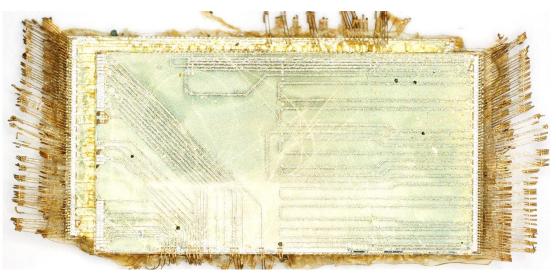

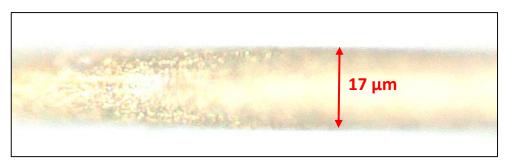

| 0           | DRAM Ana     | llysis                       | 85  |

|             | ✓ P          | ackage Views                 |     |

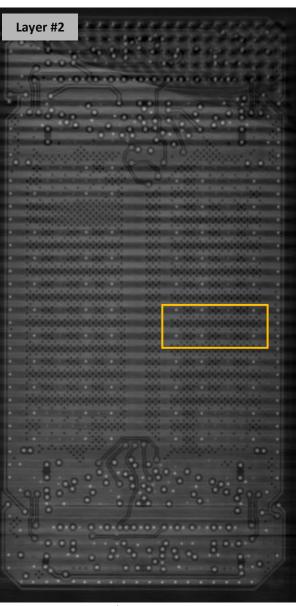

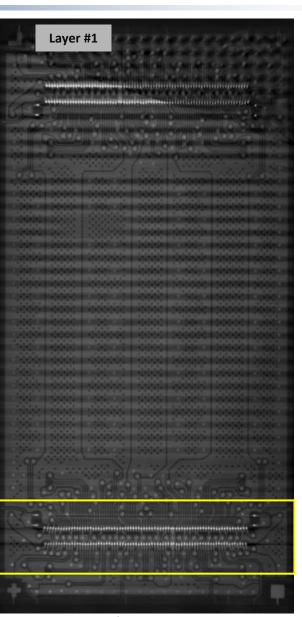

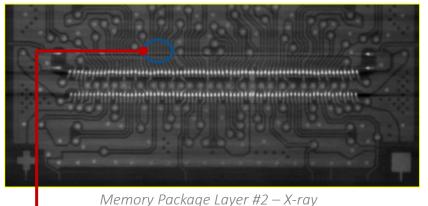

|             | ✓ P          | ackage X-RAY Images          |     |

|             | √ D          | RAM Package Cross Section    |     |

|             | √ D          | RAM Package Opening          |     |

|             | √ D          | RAM Die View                 |     |

|             | √ D          | RAM Die Cross Section        |     |

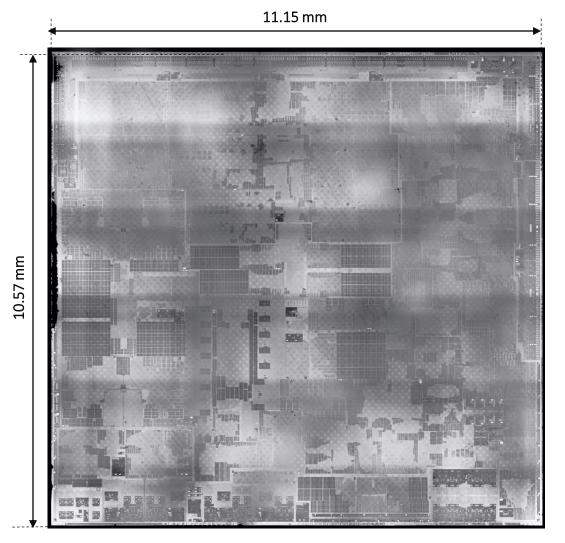

| 0           | Apple M1 Die |                              | 106 |

|             | √ D          | ie Views & Dimensions        |     |

|             | √ D          | ie Delayering                |     |

|             | ✓ D          | ie Cross Section             |     |

| OL (TEM     | Analysis)_   |                              | 118 |

134

| Manufacturir     | 150                             |     |

|------------------|---------------------------------|-----|

|                  |                                 |     |

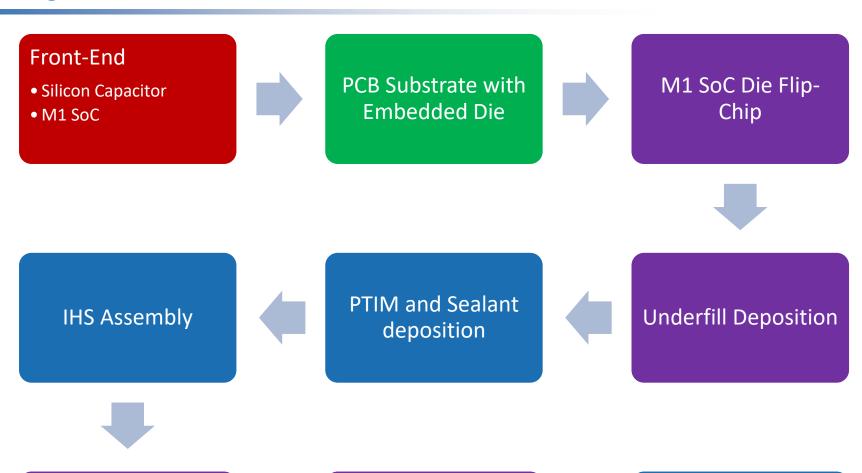

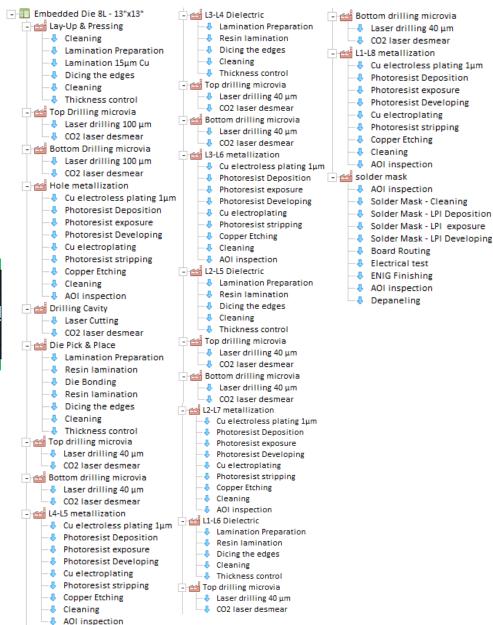

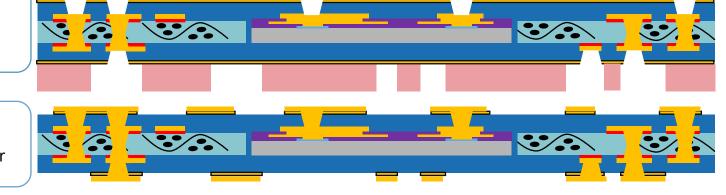

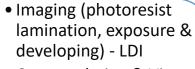

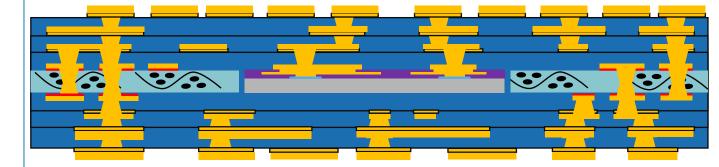

| 0                | Apple M1 Processor Process Flow |     |

| 0                | DRAM Memory Front End           |     |

| 0                | Embedded Die Process Flow       |     |

| 0                | Package Assembly Process Flow   |     |

| Cost Analysis    |                                 | 166 |

|                  |                                 |     |

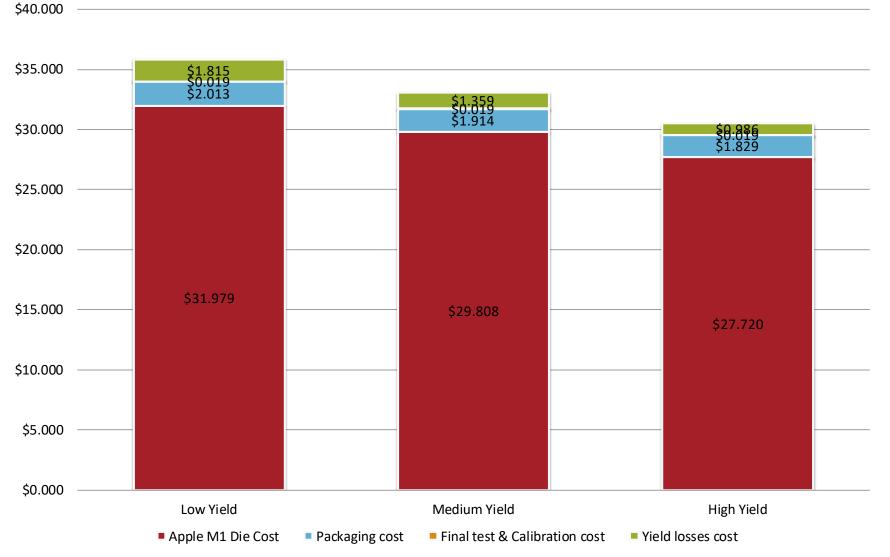

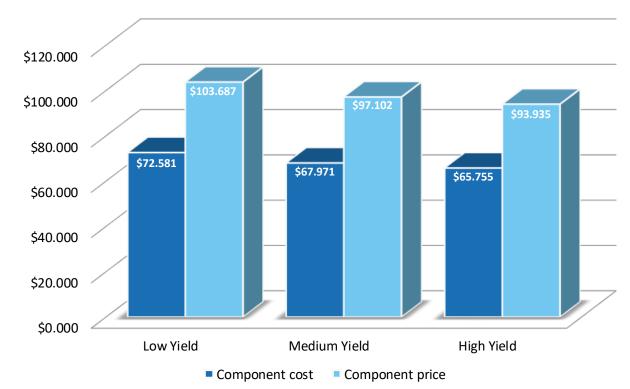

| 0                | Yields & Hypotheses             |     |

| 0                | M1 Processor Wafer and Die Cost |     |

| 0                | DRAM Wafer and Die Cost         |     |

| 0                | DRAM Component Cost& Price      |     |

| 0                | Embedded Die packaging Cost     |     |

| 0                | Package Assembly Cost           |     |

| 0                | Component Cost& Price           |     |

|                  |                                 |     |

| <u>Feedbacks</u> |                                 | 187 |

| SystemPlus C     | 189                             |     |

|                  |                                 |     |

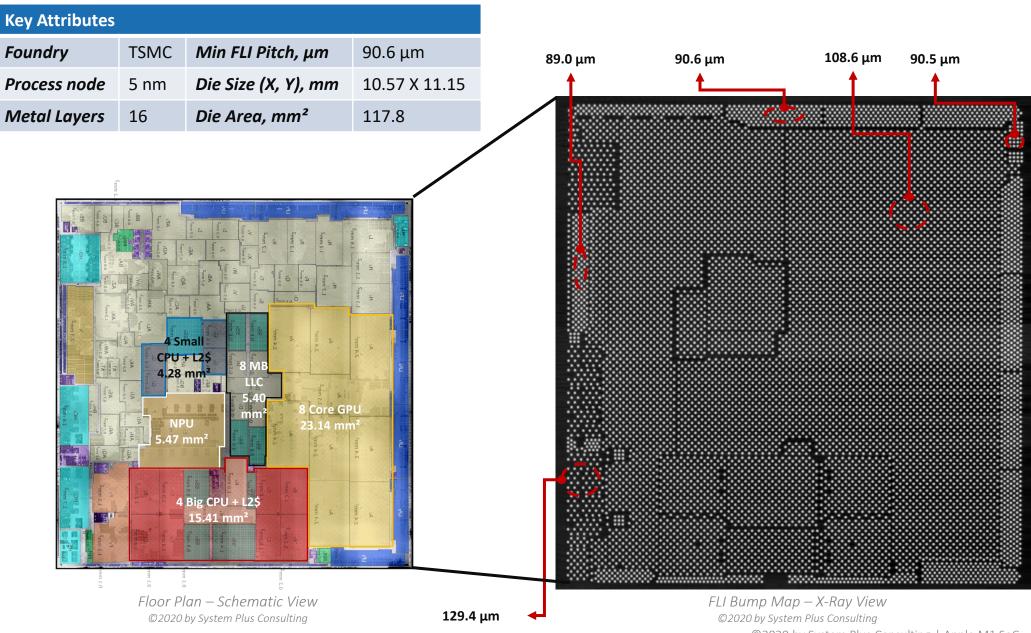

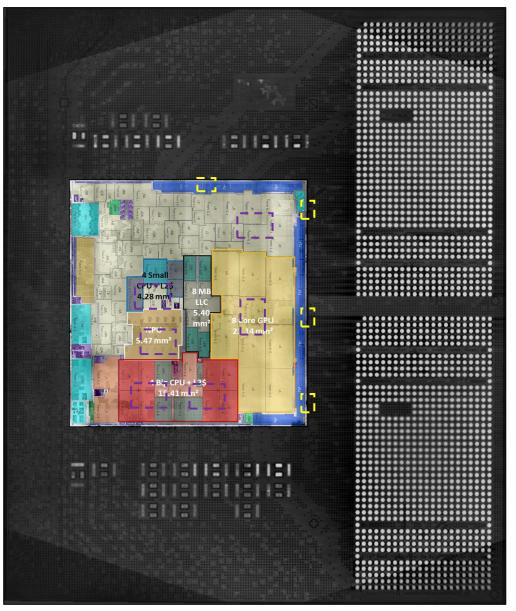

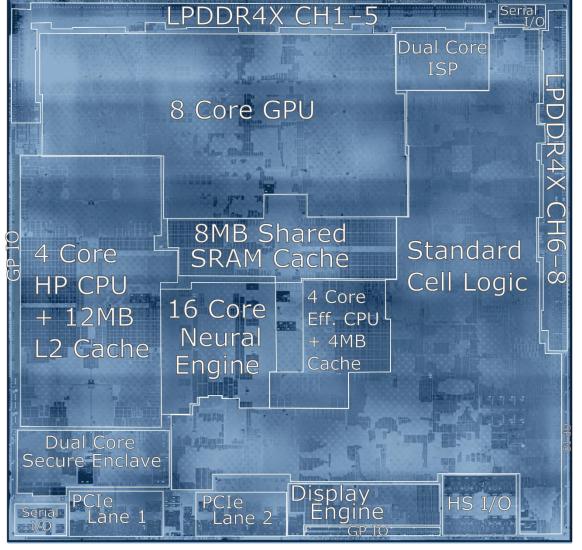

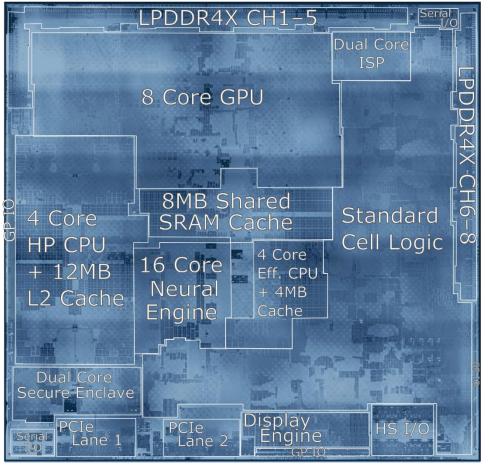

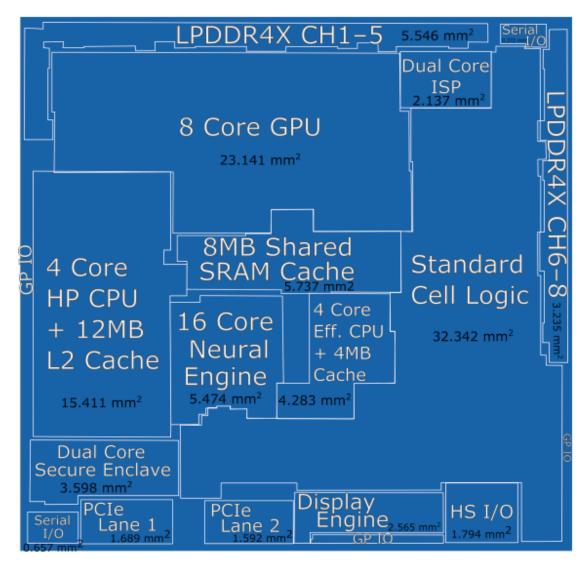

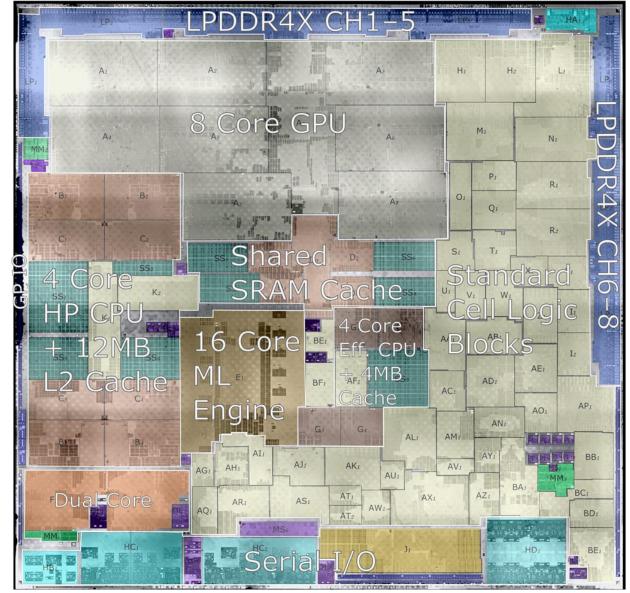

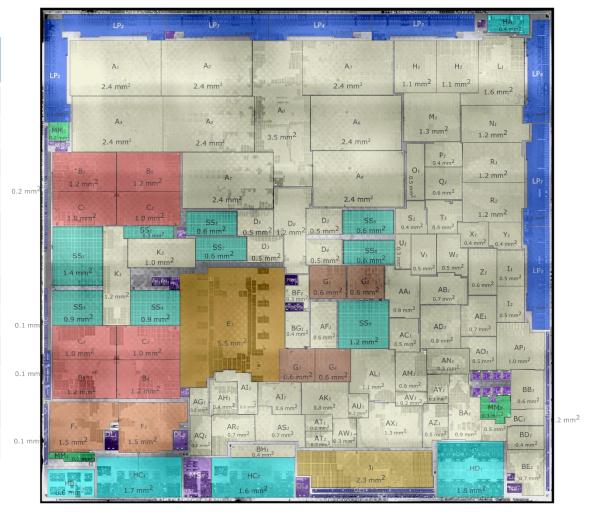

Floor Plan

## OVERVIEW METHODOLOGY

### **Executive Summary**

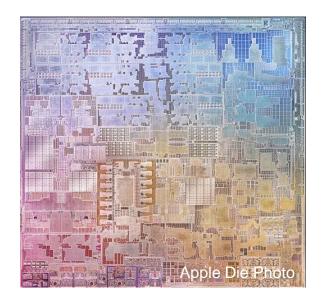

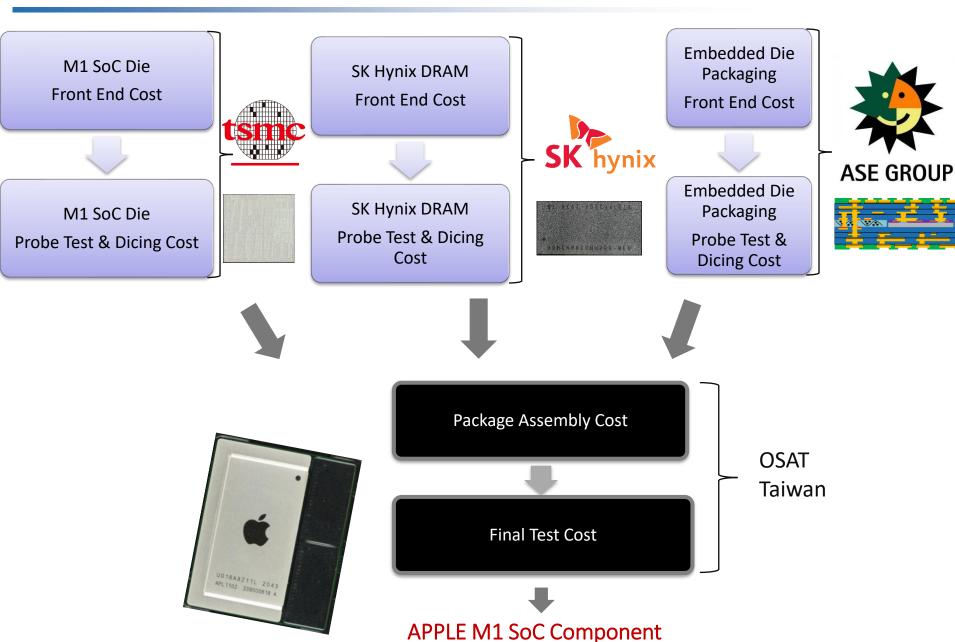

This full reverse costing study has been conducted to provide insight on technology data, manufacturing cost and selling price of the Apple M1 System-on-Chip (SoC).

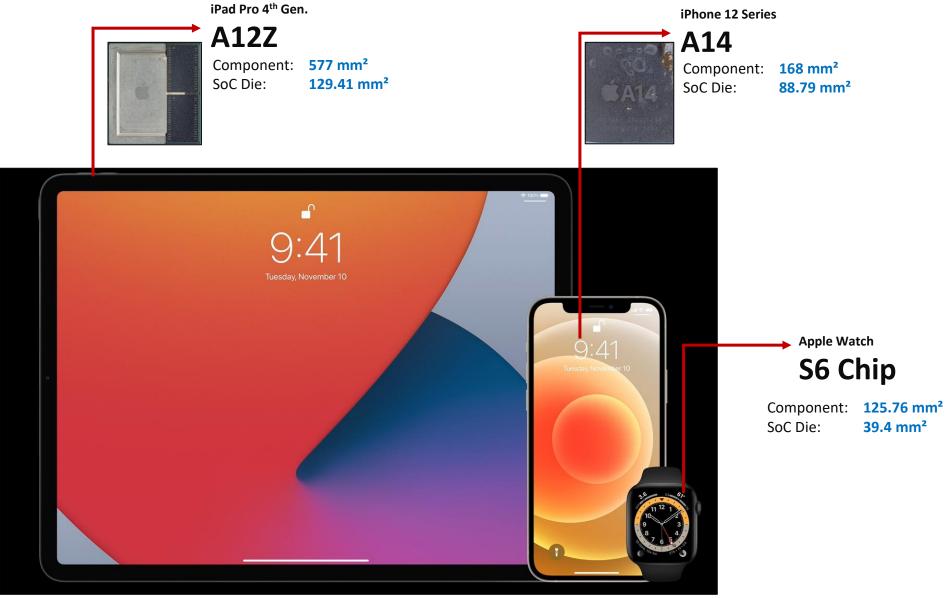

Back in 2010, Apple managed to get ride of Samsung's Processor to use its own developed ARM core-based processor, the A4. Still produced by Samsung, this was the first of the series to integrate an ARM Cortex-A8 in the iPhone Series. Still developing its own processor, Apple is now supplying the processor from TSMC since 2014. Now coupled with its packaging services including integrated Fan-Out (inFO) technology, TSMC is the only processor supplier for Apple.

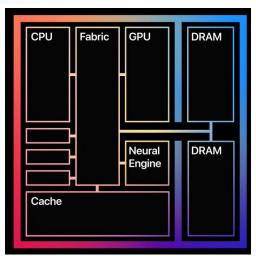

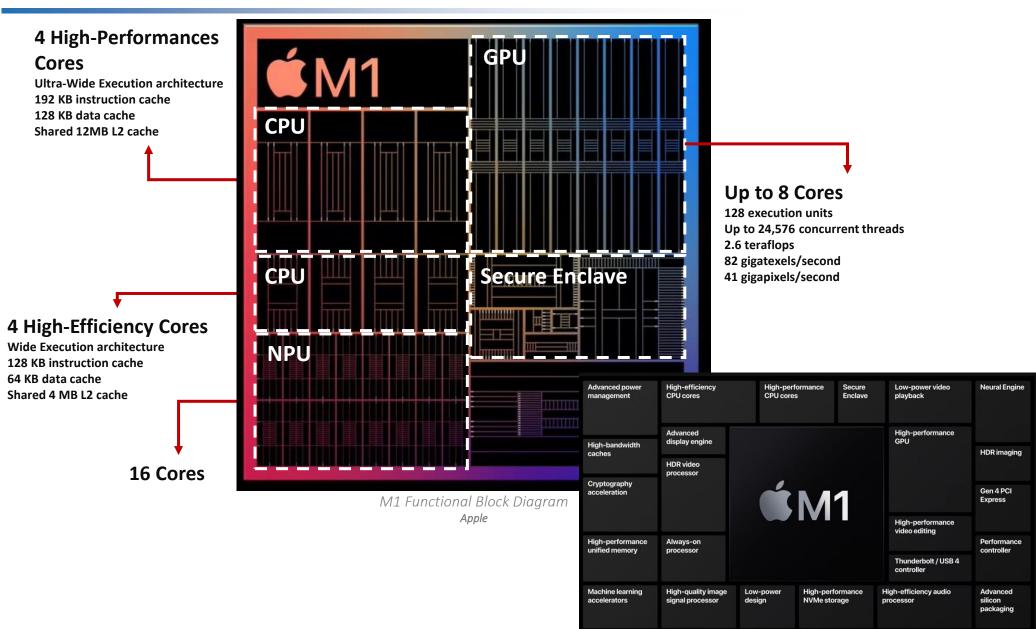

Two new Apple Macbook models as well as the Mac mini are now powered by an Apple in-house SoC design, the M1. The transition from Intel x86 processors is creating shockwaves felt throughout the processor and computer world. This new and first SoC for Mac features 4-CPU high-performance cores, 4-CPU high-efficiency cores and 8-GPU cores. The tight software-hardware integration inside Apple enabled a compact, efficient processor for personal computer that outcompetes many premium microprocessors. 16 billion transistors using TSMC 5nm process are used to build it.

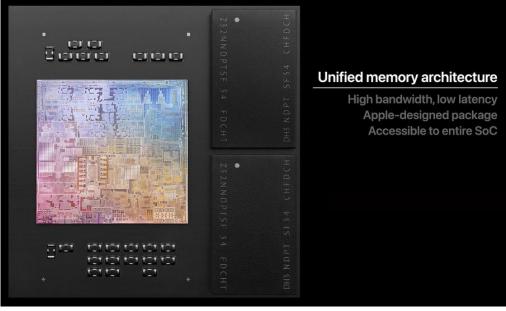

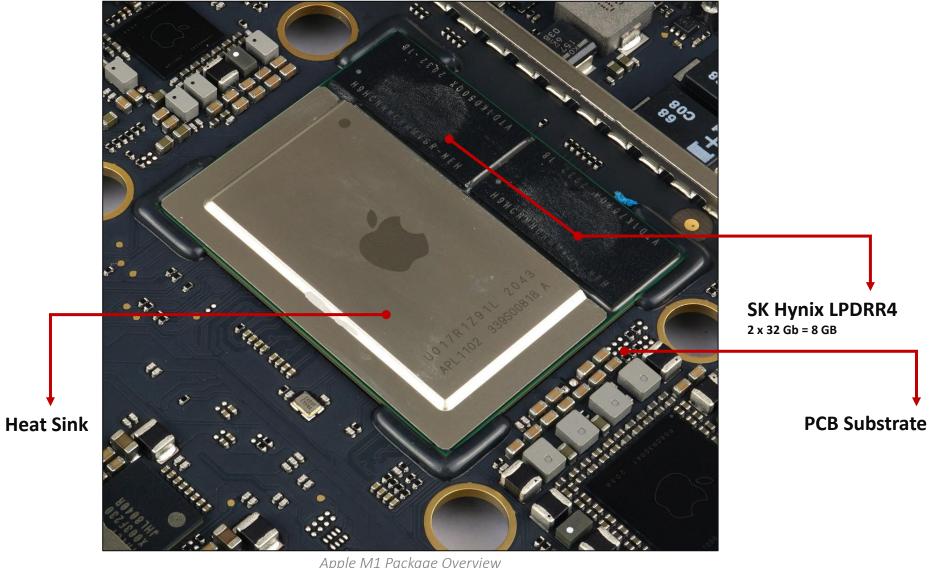

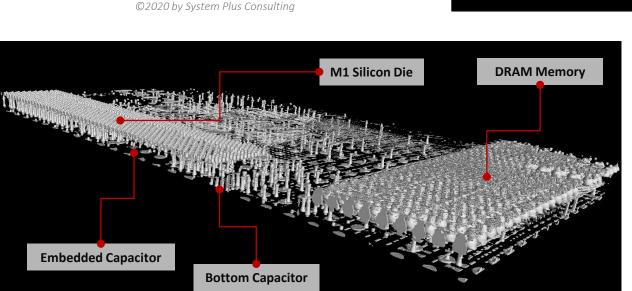

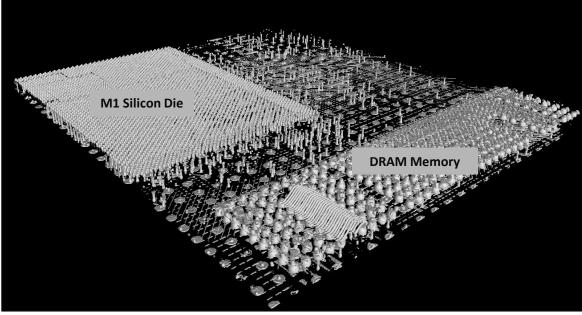

On the SoC side, it appears that the die area of the M1 has been optimized for functionality rather than SRAM cache. There is limited on-chip cache, taking cues from mobile SoC designs relying on the universal memory architecture (UMA) concept and external LPDDR4X DRAM. Significant die area is devoted to standard cell functions, which indicate that Apple is leveraging inhouse chip design to optimize hardware for the operating system. On the packaging side, the same structure is used for Apple A12X and A12Z, with the integration of the DRAM on the SoC substrate, and embedded silicon capacitors in the substrate.

To reveal all the details for this new exceptional SoC, this report features multiple analyses: Floor plan analysis to understand the high-level chip architecture with IP block area contribution measurements, Front-End construction analysis to reveal the most interesting features of the new TSMC 5nm process, Back-End construction analysis for packaging structure. It also features a detailed study of the die analyses, and cross-sections. In addition to a complete construction analysis using SEM cross-sections, material analyses and delayering, the front-end analysis uses high-resolution TEM cross-section to expose the high mobility channel of the 5nm process and the back-end analysis uses CT-Scan (3D X-Ray) to reveal the layout structure of the package. It contains a complete cost analysis and a selling price estimation of the component.

#### Overview / Introduction

- Executive Summary

- o Reverse Costing Methodology

- o Glossary

Company Profile & Supply Chain

Physical Analysis

FloorPlan

FEOL (TEM Analysis)

Feedbacks

## Executive Summary – Floor Plan Analysis

Overview / Introduction

- Executive Summary

- o Reverse Costing Methodology

- o Glossary

Company Profile & Supply Chain

Physical Analysis

FloorPlan

FEOL (TEM Analysis)

Feedbacks

**About System Plus**

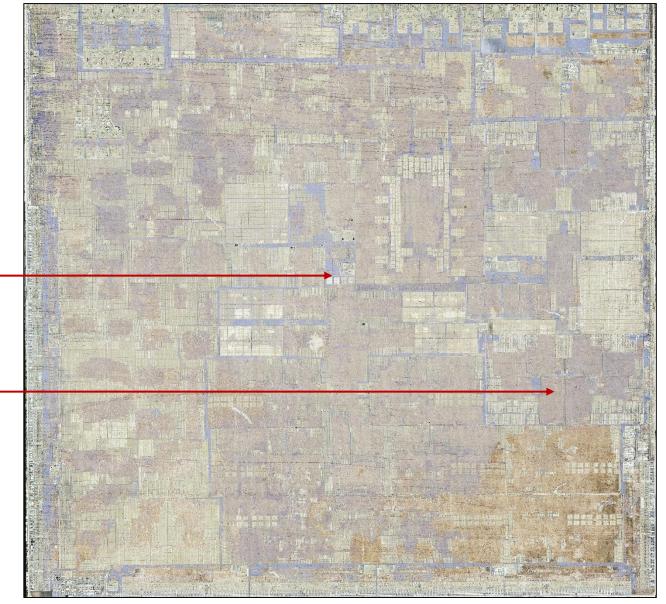

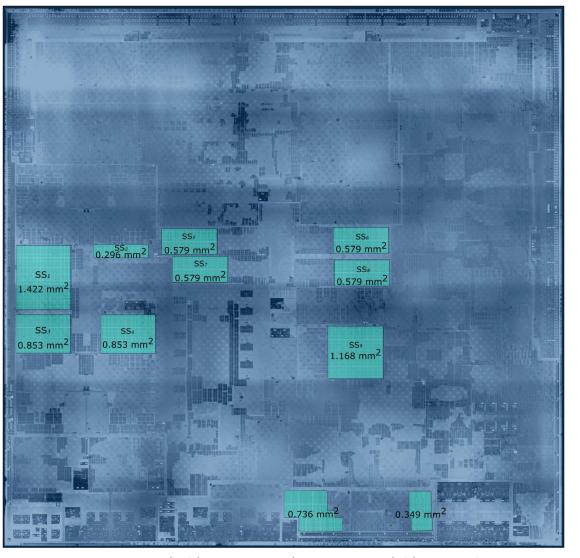

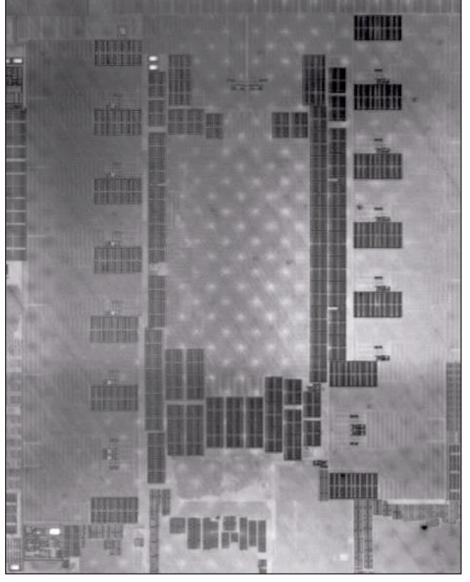

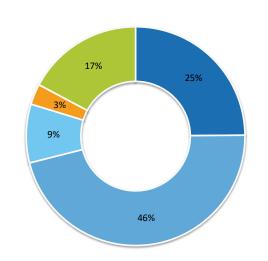

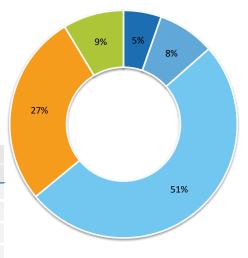

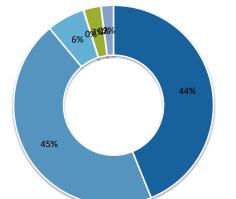

This floorplan analysis of the Apple M1 system-on-chip is intended to provide critical insights into the chip architecture.

The M1 is the first Apple in-house design for deployment to their personal computer line after many years and iterations of the mobile AX products (most recently A14).

Confirming the Apple marketing material, the M1 SoC contains these major IP blocks:

- Four "Firestorm" high-performance CPU cores

- Four "Icestorm" power efficient CPU cores

- Eight GPU cores

- Machine learning core "Neural Engine"

- Dual core secure processor "Secure Enclave"

- PCI Express high speed serial interfaces (X2)

- Display engine

Taking many queues from the mobile architecture, the M1 limits on-chip SRAM to a great extent. The total of L2 SRAM arrays is estimated to be 27.8 MB. The unified memory architecture (UMA) allows sharing of the LPDDR4X DRAM between the monolithic CPU and GPU cores. The incorporation of the DRAM on a common BGA substrate with the M1 silicon is similar in concept to typical mobile application processors (APU). However, the APU for mobile products typically deploys the LPDDR variant in a package-on-package configuration over the APU. The M1 package is more suited to higher performance and higher power consumption applications such as desktops and laptops since heat sinks can be directly applied to the M1 SoC.

## **Executive Summary**

Overview / Introduction

- o Executive Summary

- Reverse Costing Methodology

- o Glossary

Company Profile & Supply Chain

Physical Analysis

FloorPlan

FEOL (TEM Analysis)

Feedbacks

**About System Plus**

The reverse costing analysis is conducted in 3 phases:

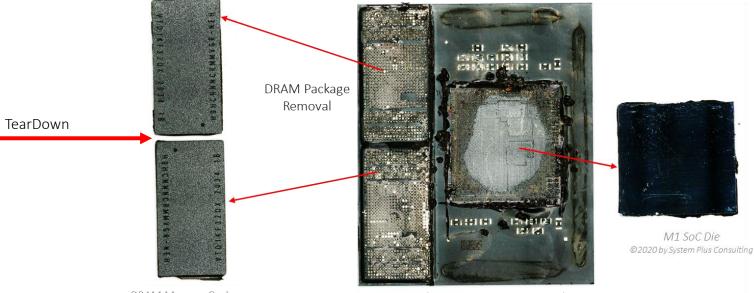

Teardown analysis

Package is analyzed and measured

The dies are extracted in order to get overall data: dimensions, main blocks, pad number and pin out, die marking

Setup of the manufacturing process.

Costing analysis

Setup of the manufacturing environment Cost simulation of the process steps

Selling price

Supply chain analysis Analysis of the selling price

## Glossary

#### Overview / Introduction

- o Executive Summary

- o Reverse Costing Methodology

- Glossary

Company Profile & Supply Chain

**Physical Analysis**

FloorPlan

FEOL (TEM Analysis)

<u>Feedbacks</u>

| Acronym | Definition                              |

|---------|-----------------------------------------|

| IC      | Integrated Circuit                      |

| IHS     | Integrated Heat Spreader                |

| BGA     | Ball Grid Array                         |

| CMOS    | Complementary Metal–Oxide–Semiconductor |

| CPU     | Central Processing Unit                 |

| CUF     | Capillary Underfill                     |

| DRAM    | Dynamic Random Access Memory            |

| G&A     | General & Administrative                |

| GPU     | Graphics Processor Unit                 |

| IHS     | Integrated heat spreader                |

| PCB     | Printed Circuit Board                   |

| PGDW    | Potential Good Dies per Wafer           |

| PTH     | Plated through hole                     |

| R&D     | Research and Development                |

| SEM     | Scanning Electron Microscope            |

| Si      | Silicon                                 |

| SiO2    | Silicon Oxide                           |

| TIM     | Thermal Interface Material              |

## COMPANY PROFILE

#### Overview / Introduction

#### Company Profile & Supply Chain

Apple

o Apple M1 Architecture & Performance

Physical Analysis

FloorPlan

FEOL (TEM Analysis)

Feedbacks

**About System Plus**

## Company Profile – Apple

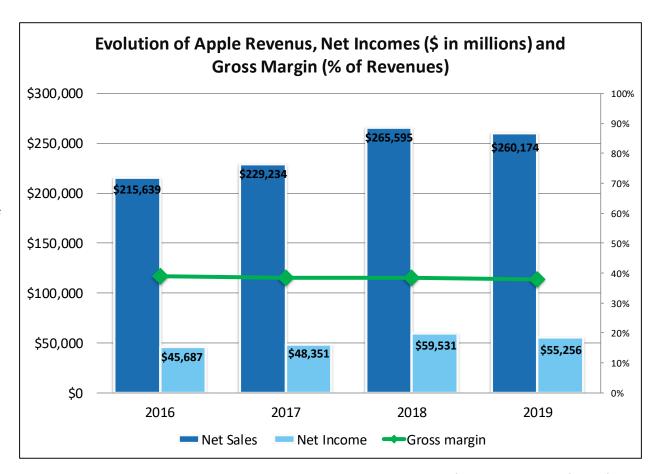

2020 Apple Financial Highlights:

\$275 Billion Sales revenues:

Gross margin: 38.2 %

\$57 Billion Net income:

#### **Employees:**

- o Date of Establishment

- **√** 1976

- o Headquarter:

- ✓ Cupertino, California, USA

- ✓ 137,000 employees worldwide (as of 28 September 2019).

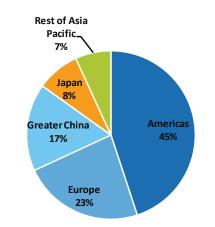

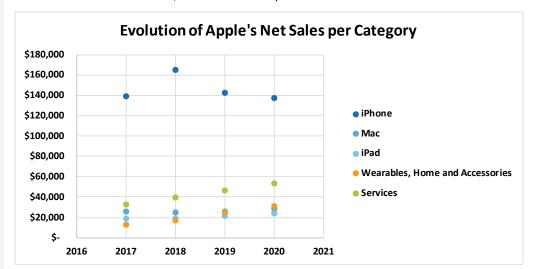

#### **Apple's Net Sales Worldwide**

Apple 2020- Financial Results

## Company Profile – Apple

#### Overview / Introduction

#### Company Profile & Supply Chain

Apple

Apple M1 Architecture & Performance

#### **Physical Analysis**

FloorPlan

FEOL (TEM Analysis)

**Feedbacks**

About System Plus

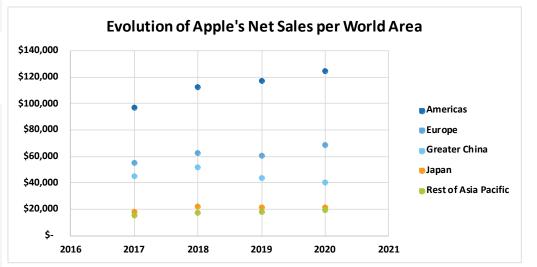

America's net sales increase each year with a slope higher than in Europe. In Japan and Rest of Asia Pacific, the tendency is flat.

- Mac net sales increased in 2020 due to higher net sales of MacBook Pro.

- In 2021, the Apple M1 will potently help to increase the number of the Mac sales.

- Services net sales increased due to higher sells from the App store and cloud services.

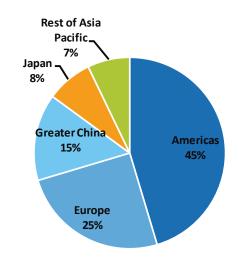

#### **Apple's Net Sales Worldwide (2020)**

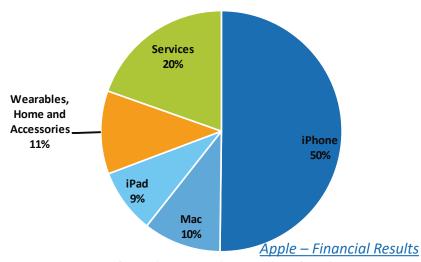

### Apple's Net Sales (2020)

## Company Profile – Apple Processors

#### Overview / Introduction

Company Profile & Supply Chain

Apple

o Apple M1 Architecture & Performance

Physical Analysis

FloorPlan

FEOL (TEM Analysis)

Feedbacks

## Apple M1 Architecture

#### Overview / Introduction

#### Company Profile & Supply Chain

- o Apple

- ► Apple M1 Architecture & Performance

Physical Analysis

FloorPlan

FEOL (TEM Analysis)

Feedbacks

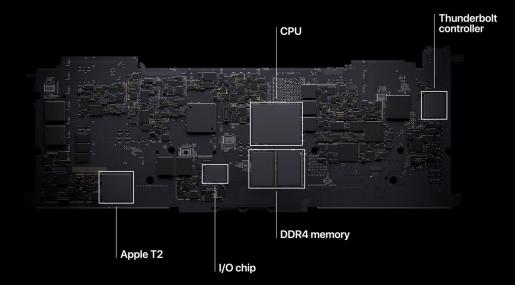

Mac Discrete Implementation Apple

- In the M1, all discrete function (Secure Element, Interface Controller, GPU, ..) are integrated in only one SoC.

- As the memory chip is integrated on the same PCB substrate as the SoC, the system benefit from high-speed processing with High Bandwidth.

M1 Functional Block Diagram

Unified Architecture Implementation

## Apple M1 Architecture

#### Overview / Introduction

#### Company Profile & Supply Chain

- o Apple

- ▶ Apple M1 Architecture & Performance

Physical Analysis

FloorPlan

FEOL (TEM Analysis)

Feedbacks

## Apple M1 Performances

#### Overview / Introduction

#### Company Profile & Supply Chain

- o Apple

- ▶ Apple M1 Architecture & Performance

Physical Analysis

FloorPlan

FEOL (TEM Analysis)

Feedbacks

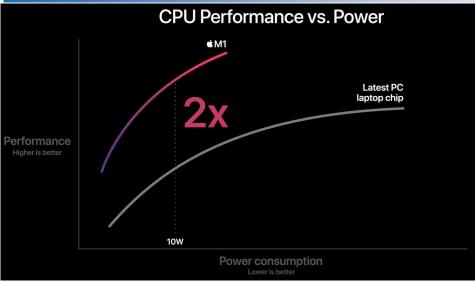

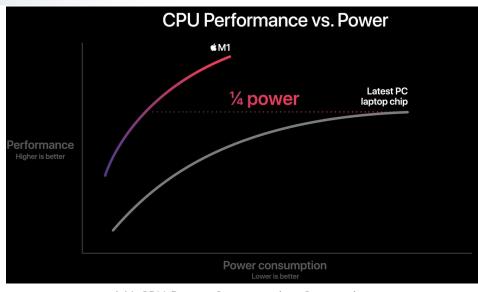

M1 CPU Performance Comparison Apple

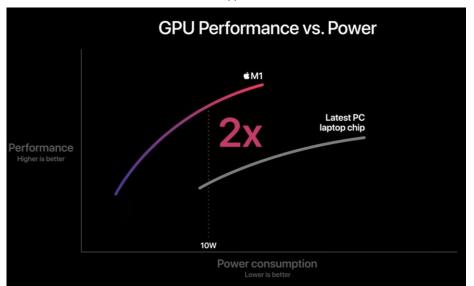

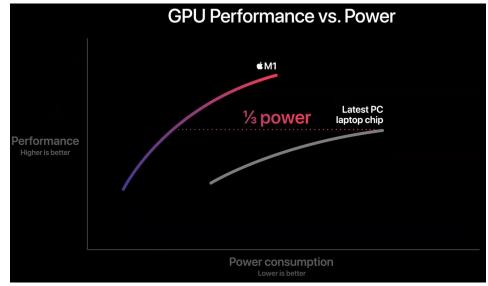

M1 GPU Performance Comparison Apple

M1 CPU Power Consumption Comparison Apple

M1 GPU Power Consumption Comparison Apple ©2020 by System Plus Consulting | Apple M1 SoC 15

## **PHYSICAL** ANALYSIS

## Apple Mac Mini Overview

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

## Apple Mac Mini TearDown

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

Report Ref.: SP20608

Apple Mac Mini Back View ©2020 by System Plus Consulting

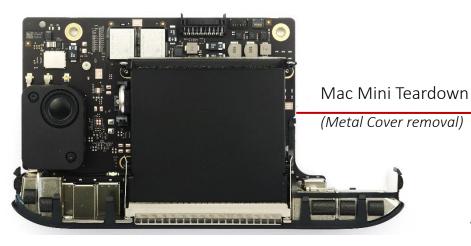

Mac Mini Teardown

(backside cover removal)

Mac Mini Teardown

(PCB) Board removal)

Apple Mac Mini Back View ©2020 by System Plus Consulting

Apple Mac Mini Board ©2020 by System Plus Consulting

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

#### FEOL (TEM Analysis)

#### Feedbacks

#### About System Plus

#### Report Ref.: SP20608

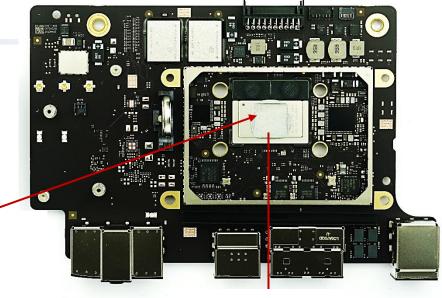

## Apple Mac Mini TearDown

Apple Mac Mini Board ©2020 by System Plus Consulting

Apple Mac Mini Board ©2020 by System Plus Consulting

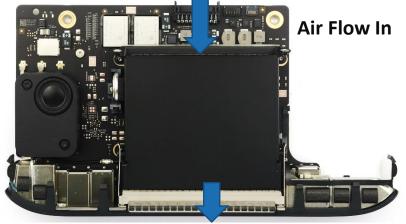

Air Flow In

Air Flow out

Apple Mac Mini Board- Heatsink ©2020 by System Plus Consulting

Apple Mac Mini Board ©2020 by System Plus Consulting

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

## Apple Mac Mini TearDown

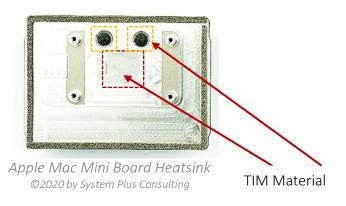

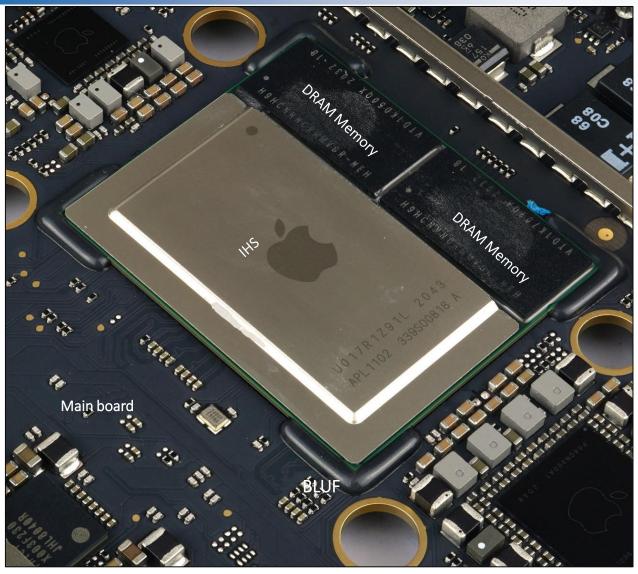

TIM Material Removal

Thermal Interface material (TIM) is used as an interface between:

- the metal cover/heatsink and the Apple M1 Component.

- Between the DRAM Memory and heatsink.

There are two different types of TIM used on the DRAM and on the IHS.

The TIM maximizes heat dissipation.

Apple Mac Mini Board – Top View ©2020 by System Plus Consulting ©2020 by System Plus Consulting | Apple M1 SoC 20

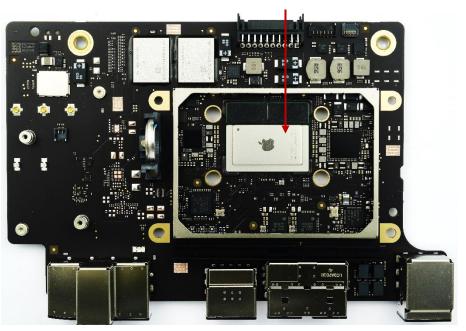

## Apple Mac Mini TearDown

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

Apple Mac Mini Board ©2020 by System Plus Consulting

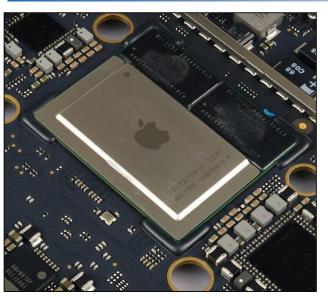

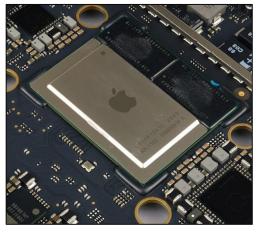

Apple M1 Package ©2020 by System Plus Consulting ©2020 by System Plus Consulting | Apple M1 SoC 21

## Apple Mac Mini TearDown

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

Apple M1 Package Overview ©2020 by System Plus Consulting

# **PHYSICAL ANALYSIS** Packaging

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

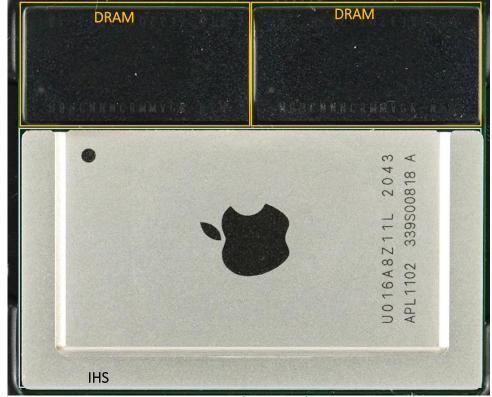

## M1 Package Views & Dimensions

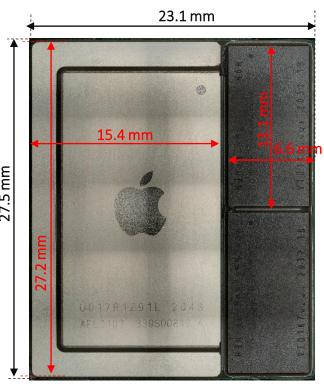

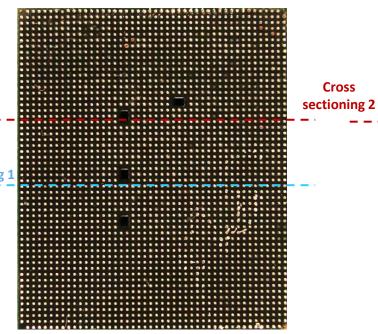

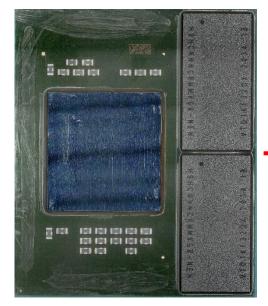

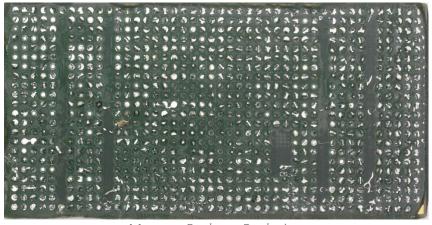

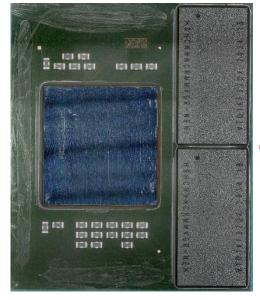

M1 Package: SiP BGA 2,502

Ball Pitch: 0.5 mm

Dimensions: 27.5 x 23.1 mm

Package Front View ©2020 by System Plus Consulting

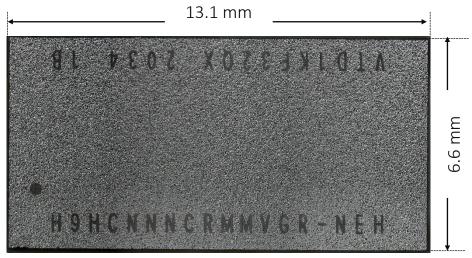

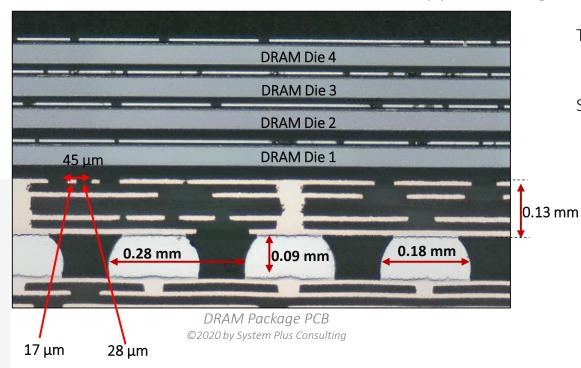

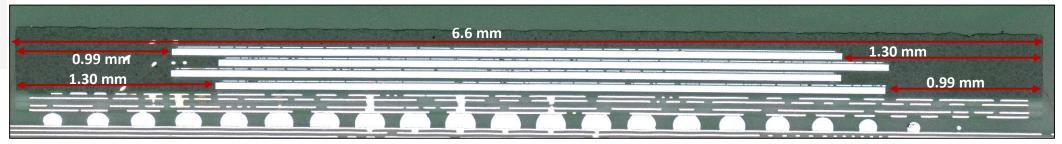

- DRAM Package

- Dimensions: 13.1 x 6.6 mm

- IHS Package

- Dimensions: 27.2 x 15.4 mm

"Package Back View ©2020 by System Plus Consulting

## M1 Package Views & Dimensions

#### Overview / Introduction

## Company Profile & Supply Chain

#### **Physical Analysis**

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### <u>FloorPlan</u>

FEOL (TEM Analysis)

**Feedbacks**

About System Plus

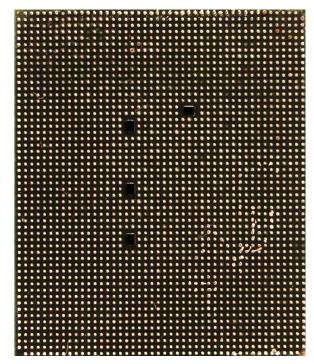

Package Back View

© 2020 by System Plus Consulting

#### Overview / Introduction

## Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- Package CrossSection

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### <u>FloorPlan</u>

FEOL (TEM Analysis)

**Feedbacks**

About System Plus

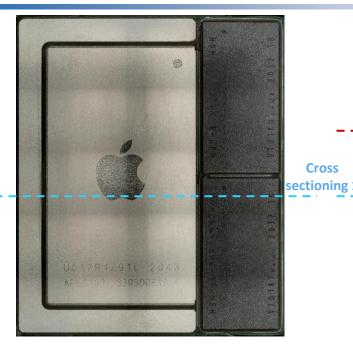

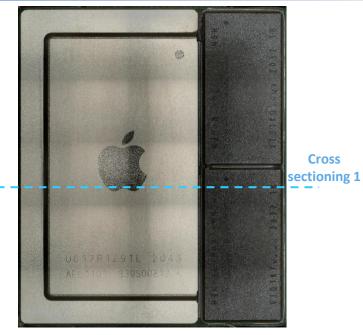

## M1 Package Overview

Packaging overview — Optical View ©2020 by System Plus Consulting

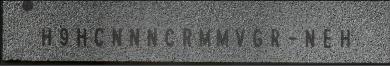

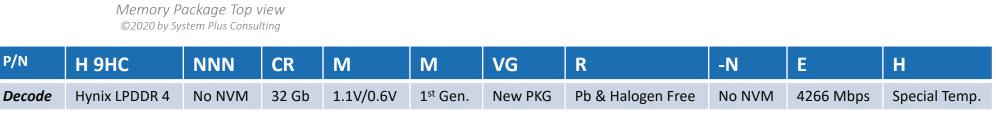

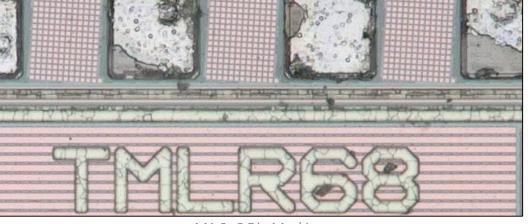

#### Package Marking

- U017R1Z91L Trace code

- APL1102 Product Code

- 2043 Packaging information (year 2020, week 43)

- 339S00818 A

## Package Disassembly – X-Ray

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

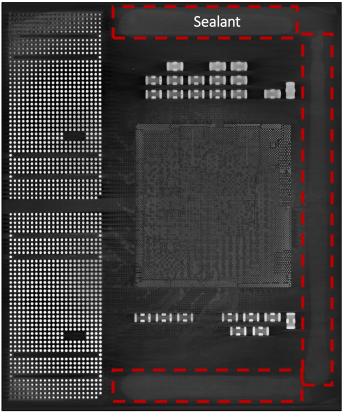

*IHS Bottom View – X-Ray View* ©2020 by System Plus Consulting

Packaging Top View w/IHS off - X-Ray View ©2020 by System Plus Consulting

| IHS Attributes             | Measurements     |

|----------------------------|------------------|

| IHS Form Factor            | 15 x 27          |

| IHS Foot Width             | 1.94 mm          |

| IHS Edge to PKG Edge, Min  | 100 μm           |

| IHS to DRAM                | 483 μm           |

| Sealant Width (N/S/E) (mm) | (2.07/0.99/1.77) |

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

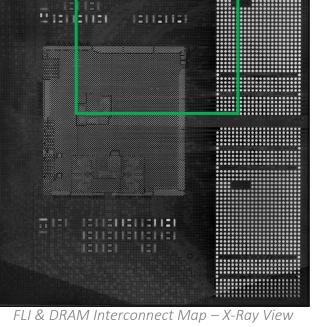

BGA and DTC Interconnect Map – X-Ray View ©2020 by System Plus Consulting

- The M1 has the corners depop'd. BLUF is just deposited at the corner of the component.

- 6 BGA's de-pop'd for each DTC.

DTC Interconnect Map – X-Ray View ©2020 by System Plus Consulting

- DTC Ball Number:

- DTC Ball pitch: 87.7 μm

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

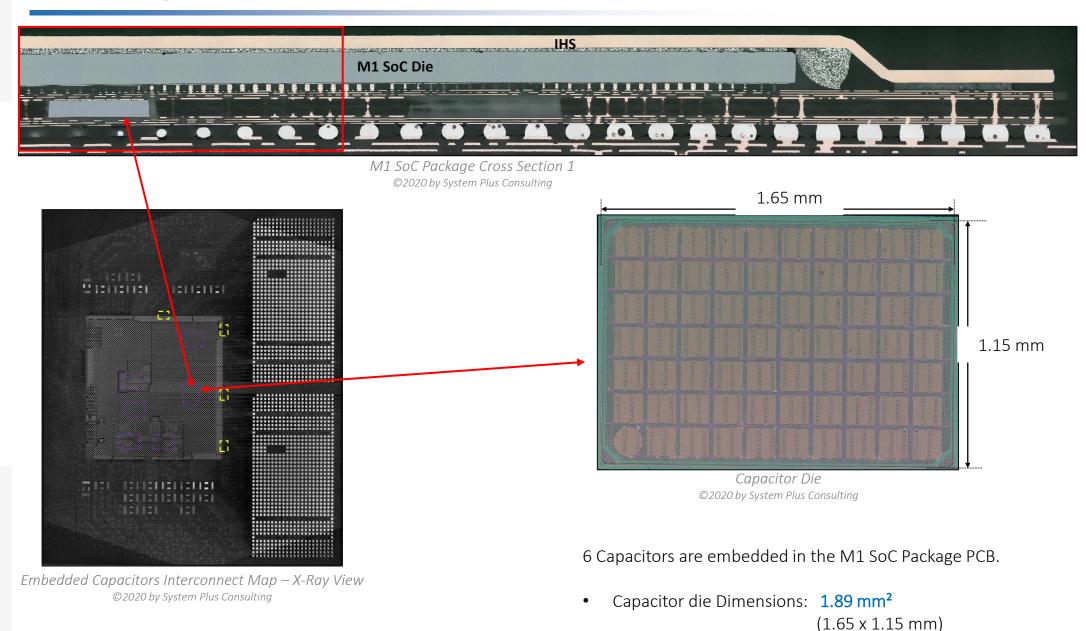

Embedded Capacitors Interconnect Map – X-Ray View ©2020 by System Plus Consulting

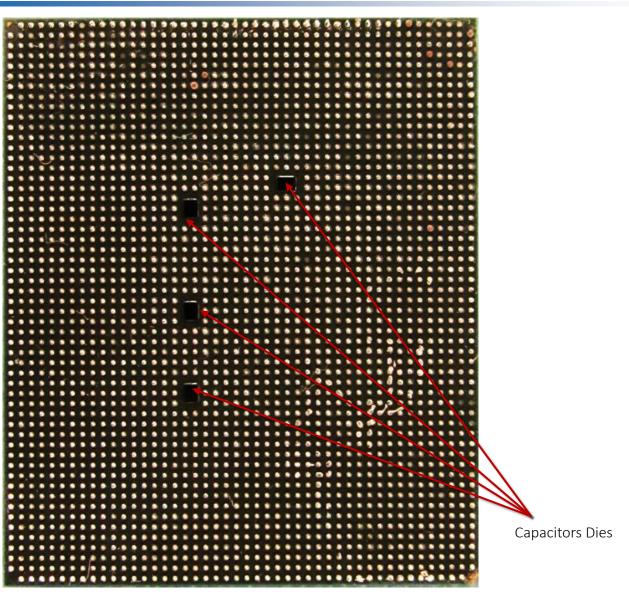

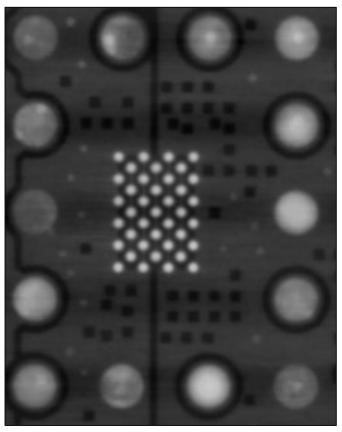

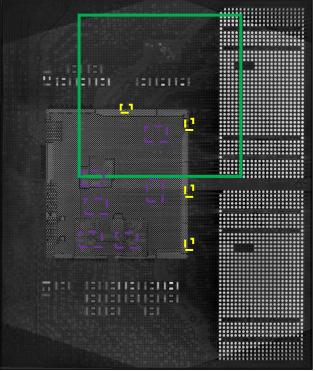

The M1 has 6 embedded silicon capacitor. The first pad of the capacitor is round whereas the others are rectangular.

Embedded Capacitor Interconnect Map – X-Ray View ©2020 by System Plus Consulting

Embedded Cap. Pad Number: 70

Embedded Cap. Square Pad size: 0.0196 mm<sup>2</sup>

$(0.14 \times 0.14 \text{ mm})$

Embedded Cap. Pad pitch: 0.15 mm Min LTH to pad edge: 17.5 μm

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

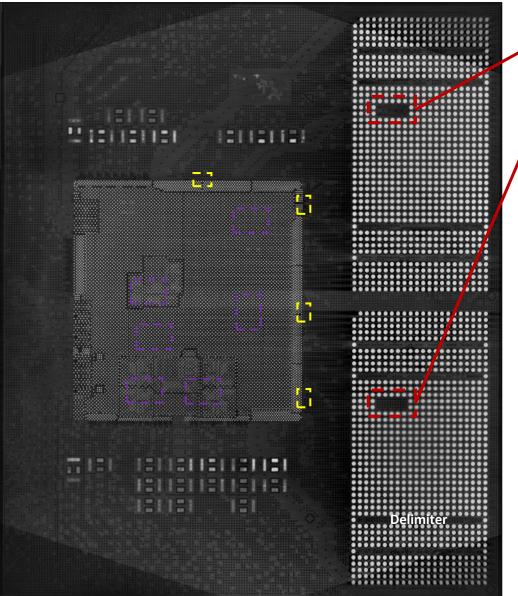

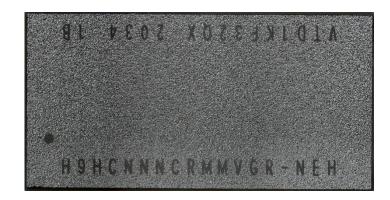

The DRAM BGA footprint has a de-pop for pin 1 and panel ID plating on the last layer of DRAM package.

|                     | M1                       | DRAM                                      |

|---------------------|--------------------------|-------------------------------------------|

| BGA Ball Number     | 2,502                    | 877                                       |

| BGA Pitch           | 0.5 mm                   | 0.28 mm                                   |

| BGA Rows            | 46 x 55                  | 22 x 44                                   |

| <b>De-pop</b>       | 28<br>(6/DTC & 1/corner) | 91<br>(20/Delimiter),<br>1/Pin 1 & 10/ID) |

| Embedded Cap Count  | 6                        | N/A                                       |

| DTC Count/BGA Pitch | 6/87.7 μm                | N/A                                       |

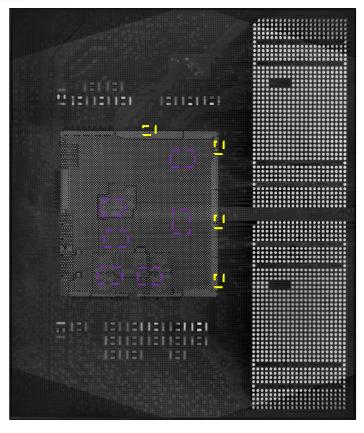

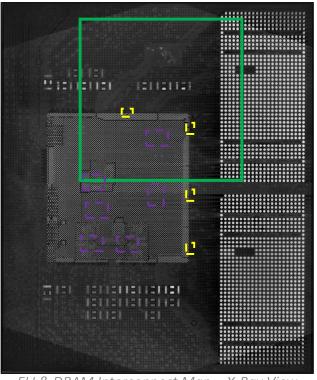

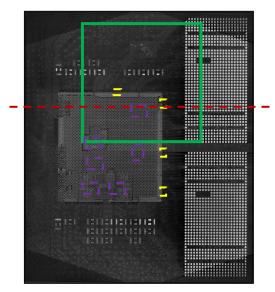

FLI & DRAM Interconnect Map – X-Ray View ©2020 by System Plus Consulting

## M1 FLI Map

#### Overview / Introduction

## Company Profile & Supply Chain

#### **Physical Analysis**

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- Package CrossSection

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### <u>FloorPlan</u>

FEOL (TEM Analysis)

**Feedbacks**

About System Plus

Report Ref.: SP20608

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

FLI & DRAM Interconnect Map – X-Ray View ©2020 by System Plus Consulting

FLI & DRAM Interconnect Map – X-Ray View ©2020 by System Plus Consulting

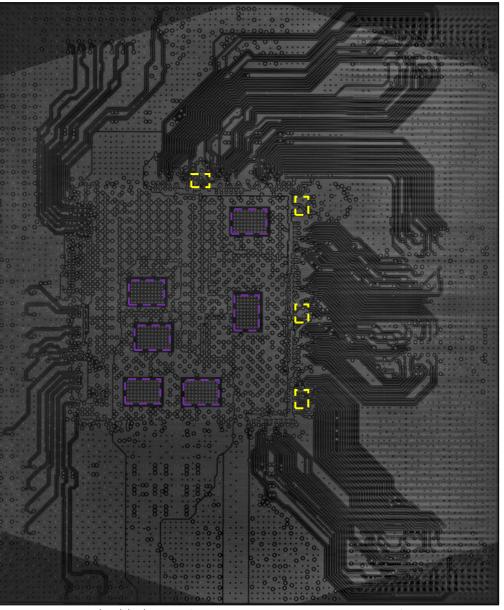

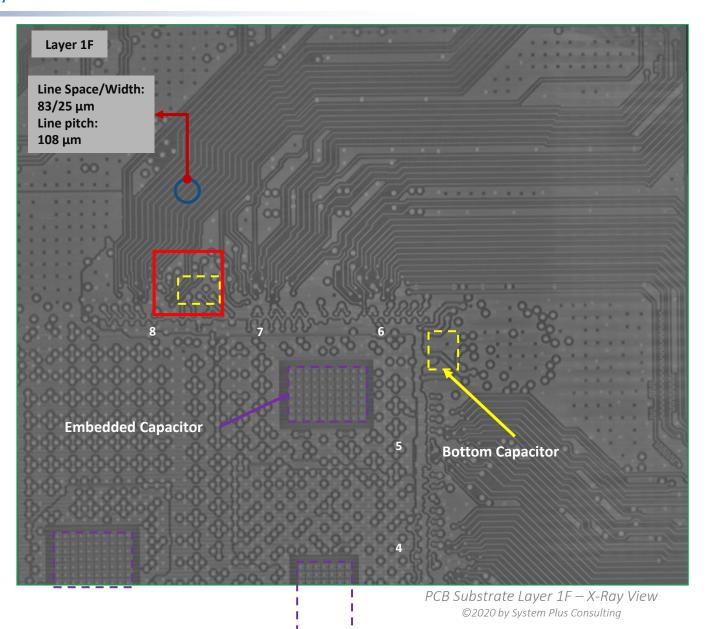

- Two embedded capacitors are under the big Core, one is under the GPU, the NPU and the small CPU.

- A last embedded capacitor is placed under the Dual Core ISP and the standard Cell.

- The bottom capacitor is placed directly under the LPDDR4X interface.

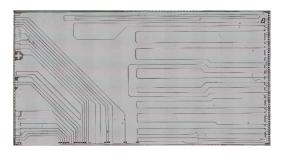

## M1 PCB Substrate – X-Ray

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

Report Ref.: SP20608

©2020 by System Plus Consulting

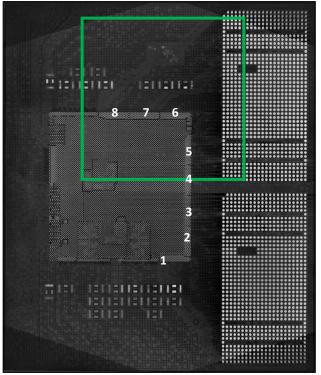

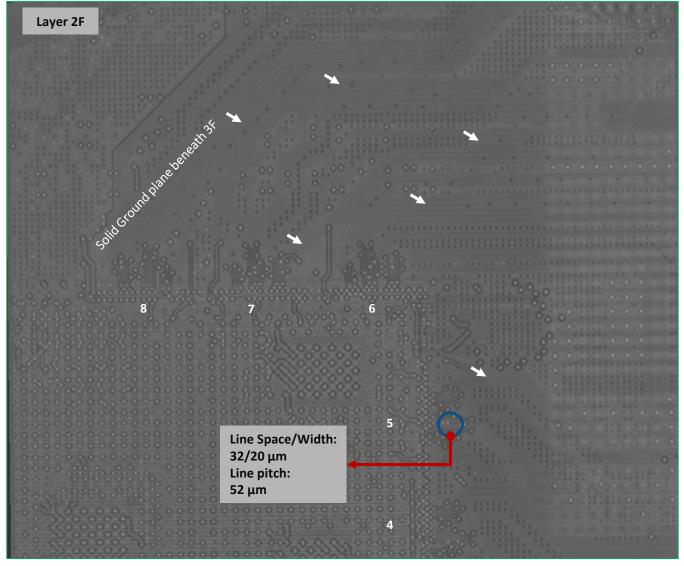

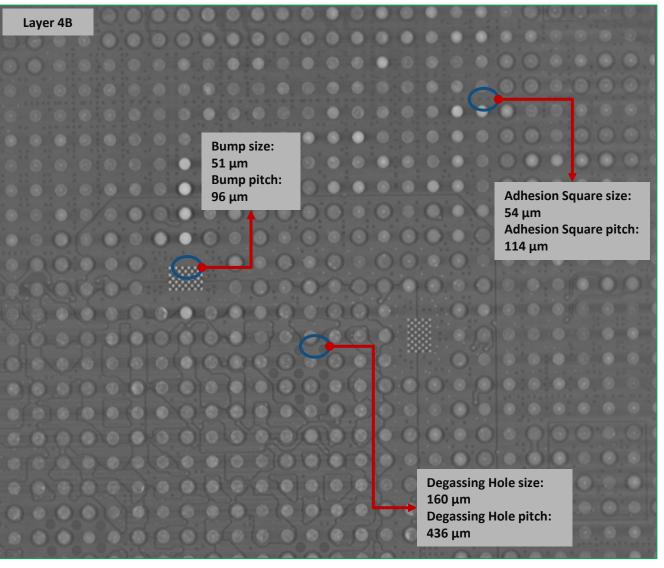

**Adhesion Square size:** 52 μm **Adhesion Square pitch:** 109 µm

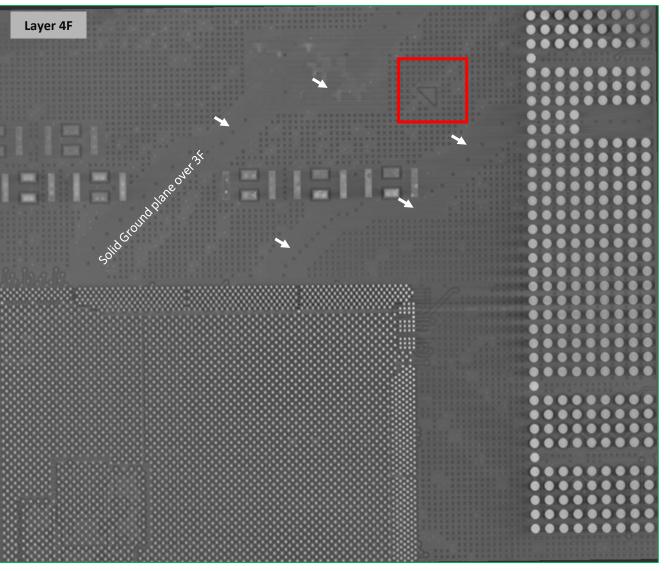

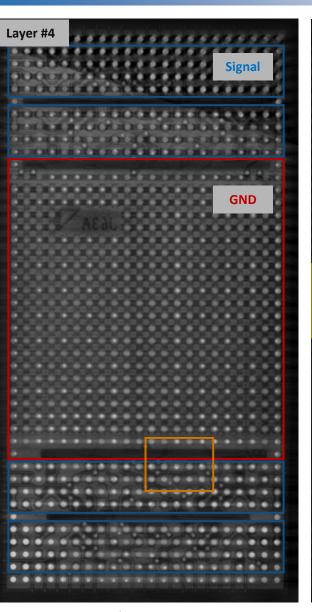

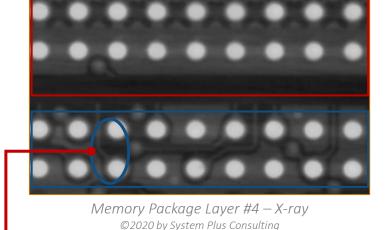

PCB Substrate Layer 4F - X-Ray View ©2020 by System Plus Consulting

The PCB has solid ground planes directly over 3F LPDDR Signal for full referencing which should help signal integrity. ©2020 by System Plus Consulting | Apple M1 SoC 33

## M1 PCB Substrate – X-Ray

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

FLI & DRAM Interconnect Map – X-Ray View ©2020 by System Plus Consulting

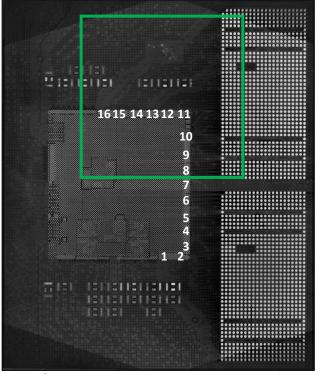

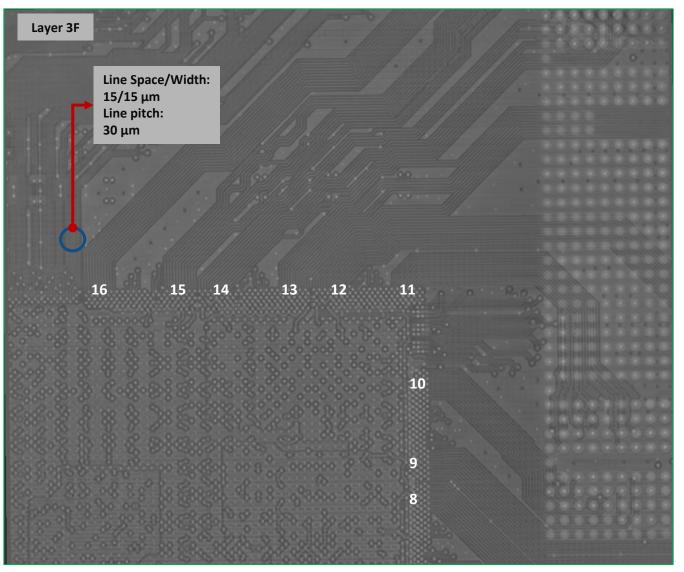

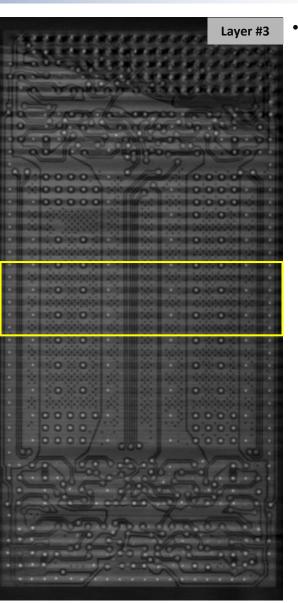

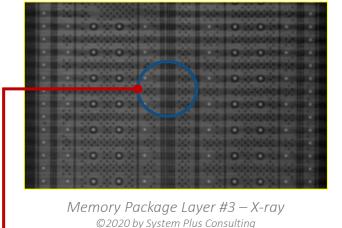

PCB Substrate Layer 3F - X-Ray View ©2020 by System Plus Consulting

PCB Substrate Layer 3F - X-Ray View ©2020 by System Plus Consulting

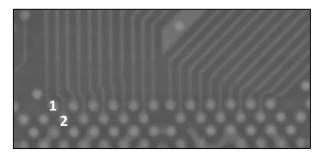

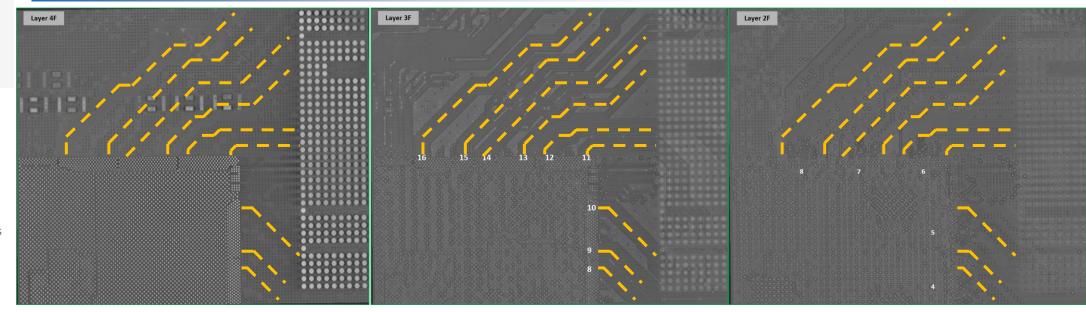

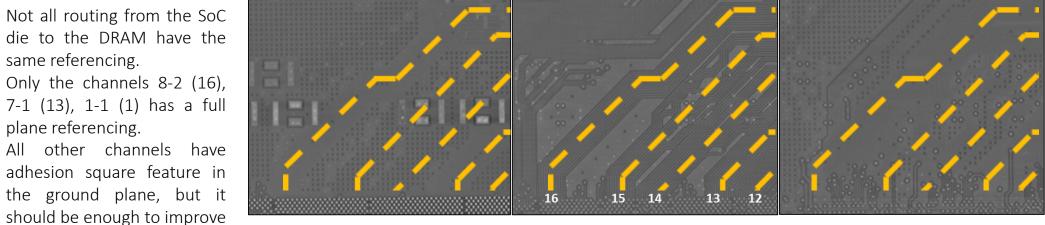

16 sets of 11 traces going from die to the DRAMs. 176 total traces. Set to each DRAM PKG, 88 total/DRAM. On the LPDDR area on the die, 2 rows are used for routing. ©2020 by System Plus Consulting | Apple M1 SoC 34

## M1 PCB Substrate – X-Ray

#### Overview / Introduction

## Company Profile & Supply Chain

#### **Physical Analysis**

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- Package CrossSection

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### <u>FloorPlan</u>

FEOL (TEM Analysis)

**Feedbacks**

FLI & DRAM Interconnect Map — X-Ray View © 2020 by System Plus Consulting

- 8 sets of 11 traces exiting through each side of the SoC from the LPDDR IP block.

- The PCB has solid ground planes directly below 3F LPDDR Signal for full referencing which should help signal integrity.

PCB Substrate Layer 2F — X-Ray View ©2020 by System Plus Consulting

### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

#### FEOL (TEM Analysis)

#### Feedbacks

## M1 PCB Substrate – X-Ray

same referencing.

plane referencing.

the signal integrity.

PCB Substrate Layer Full Plane Referencing — X-Ray View ©2020 by System Plus Consulting

PCB Substrate Layer Full Plane Referencing – X-Ray View ©2020 by System Plus Consulting

101101101

8 17 6

der terrerrerrer

## Overview / Introduction

## Company Profile & Supply Chain

## Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

### Feedbacks

#### About System Plus

TELLET LELLET TEL FLI & DRAM Interconnect Map – X-Ray View ©2020 by System Plus Consulting

2121121121

### Overview / Introduction

### Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- Cross Section 1

- o Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

### Feedbacks

FLI & DRAM Interconnect Map – X-Ray View ©2020 by System Plus Consulting

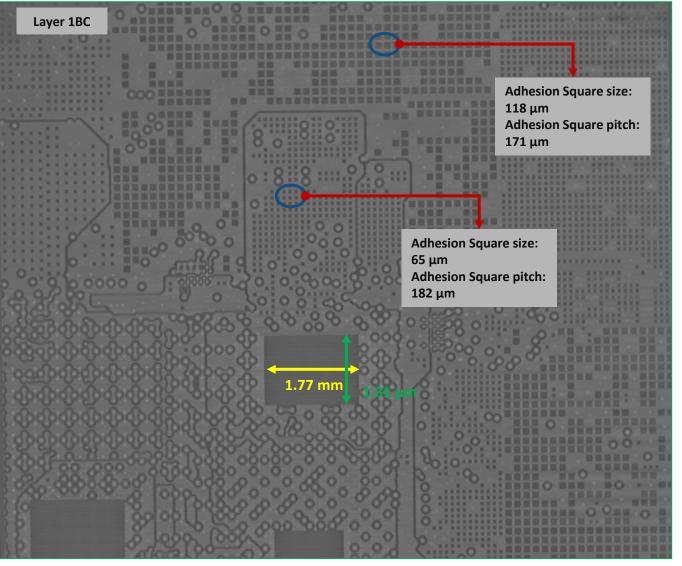

- The layer 1BC is not used for routing. Only small lines are trace for LTHmicro-via interconnection.

- Two type of adhesion feature are implemented in the bottom PCB.

PCB Substrate Layer 1BC - X-Ray View ©2020 by System Plus Consulting

### Overview / Introduction

## Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

### Feedbacks

FLI & DRAM Interconnect Map – X-Ray View ©2020 by System Plus Consulting

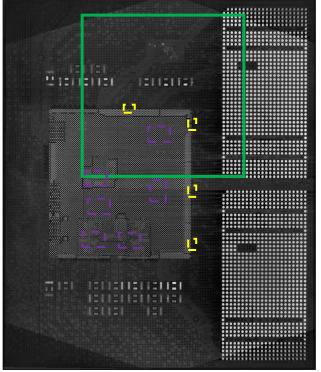

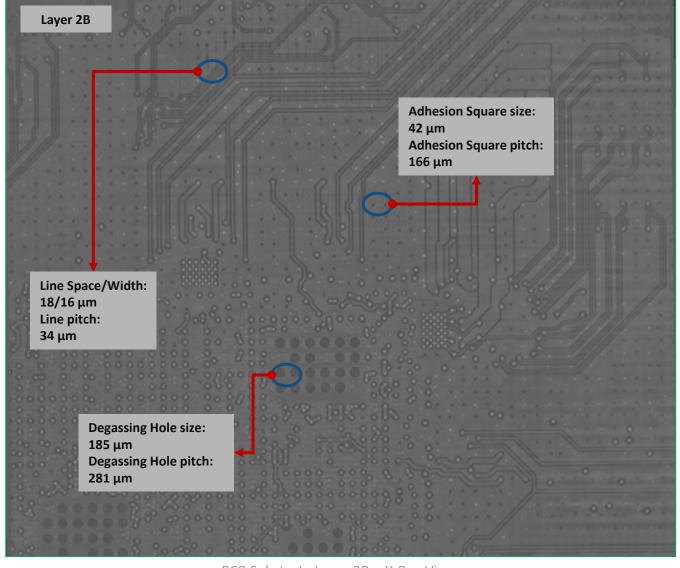

- The layer 2B is used for routing.

- Widespread adhesion features are implemented in this layer of the bottom PCB along with large degassing hole below the Silicon capacitor substrate.

PCB Substrate Layer 2B - X-Ray View ©2020 by System Plus Consulting

## Overview / Introduction

### Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

### Feedbacks

FLI & DRAM Interconnect Map – X-Ray View ©2020 by System Plus Consulting

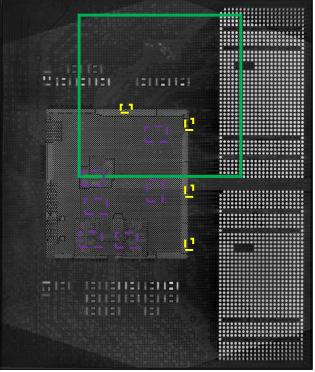

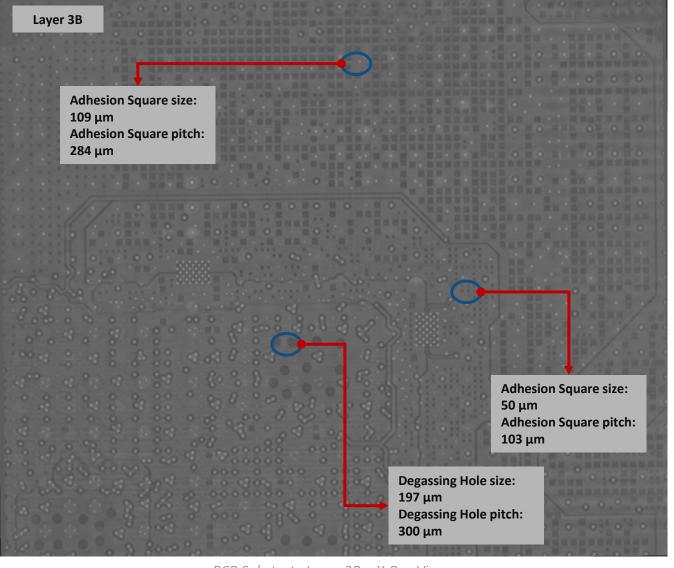

- The layer 3B is not used for routing.

- Two type of adhesion feature are implemented in the bottom PCB.

- The orientation of the degassing hole suggests a built-up process.

PCB Substrate Layer 3B - X-Ray View ©2020 by System Plus Consulting

## Overview / Introduction

## Company Profile & Supply Chain

## Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

FLI & DRAM Interconnect Map – X-Ray View ©2020 by System Plus Consulting

PCB Substrate Layer 4B - X-Ray View ©2020 by System Plus Consulting

# M1 Package Overview- X-Ray

## Overview / Introduction

### Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

Report Ref.: SP20608

FLI & DRAM Interconnect Map - X-Ray View ©2020 by System Plus Consulting

Package overview – X-Ray View ©2020 by System Plus Consulting

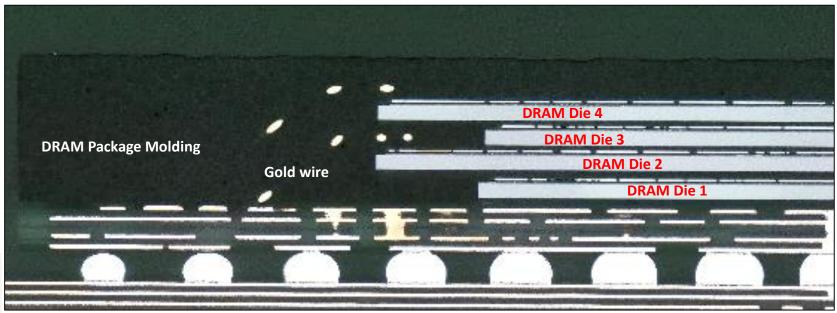

The DRAM memory uses two line of wire bonding at the North and South side of the component. Additional wire bonding (2/side) are placed at the East and West side of the component

### Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

#### FEOL (TEM Analysis)

#### Feedbacks

## About System Plus

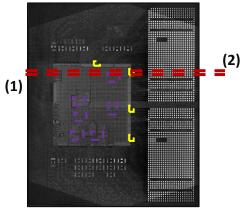

# M1 Package Cross-Section - X-Ray

©2020 by System Plus Consulting

Si. Capacitor

Package Cross-Section (1) – X-Ray View ©2020 by System Plus Consulting FLI & DRAM Interconnect Map – X-Ray View

Package Cross-Section (2) – X-Ray View ©2020 by System Plus Consulting

# M1 Package Cross-Section - X-Ray

## Overview / Introduction

# Company Profile & Supply Chain

### **Physical Analysis**

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- Package Views

- o Package X-RAY

- Package CrossSection

- Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### <u>FloorPlan</u>

FEOL (TEM Analysis)

**Feedbacks**

About System Plus

Report Ref.: SP20608

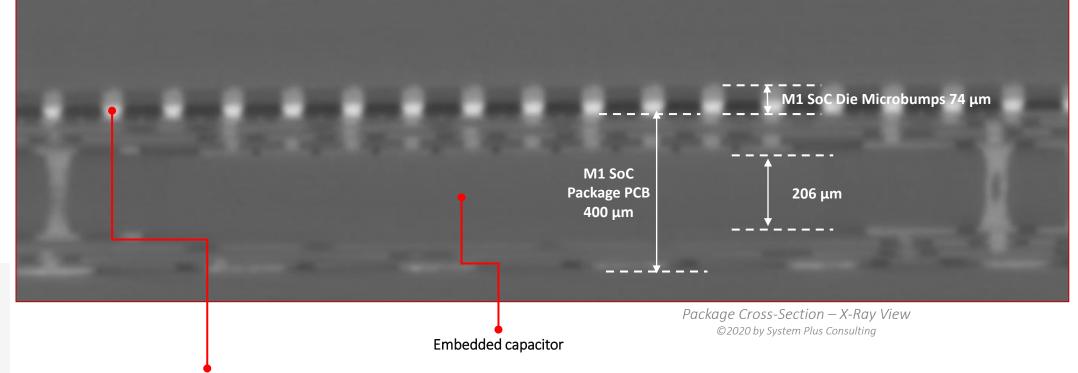

Package Cross-Section — X-Ray View

©2020 by System Plus Consulting

Package Cross-Section — X-Ray View

©2020 by System Plus Consulting

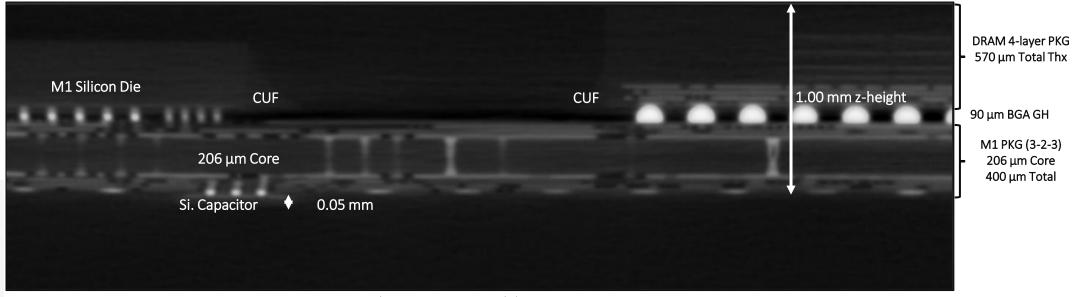

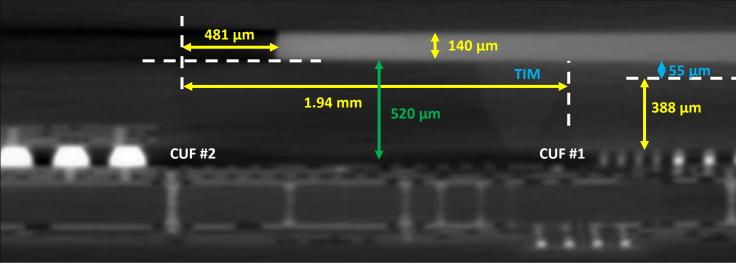

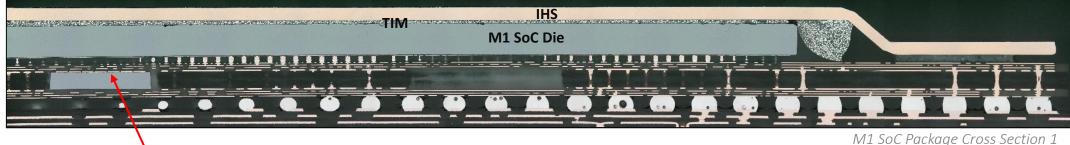

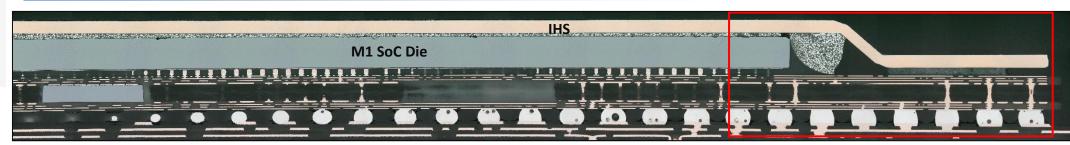

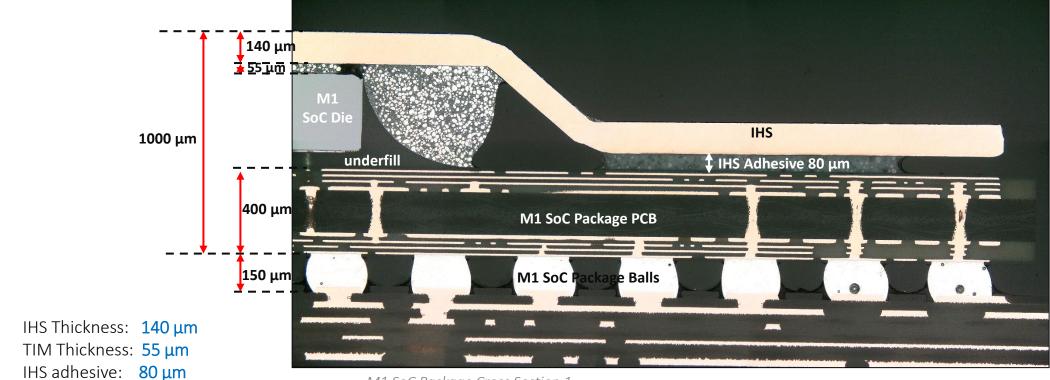

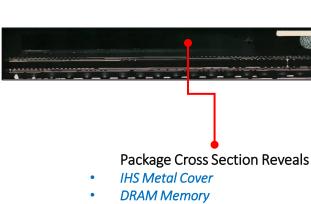

- IHS Thickness: 140 μm

TIM BLT: 55 μm

- The M1 SoC die was attached and CUF's prior to the DRAM. The gap between the M1 SoC and the DRAM is large enough to avoid the overlap of the CUFs.

- Dispense location was likely between the two DRAMs.

- The IHS could not necessarily placed last.

# M1 Package Cross-Section - X-Ray

## Overview / Introduction

### Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

### Feedbacks

**About System Plus**

Report Ref.: SP20608

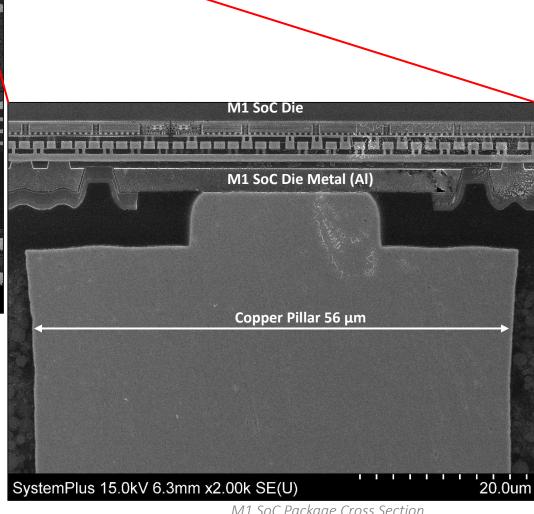

Package Cross-Section – X-Ray View ©2020 by System Plus Consulting

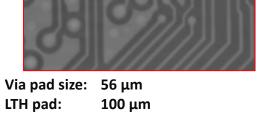

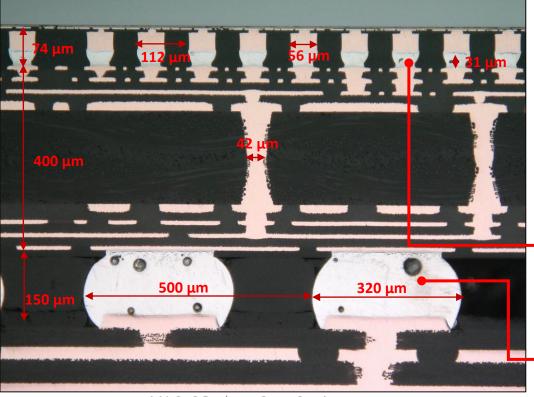

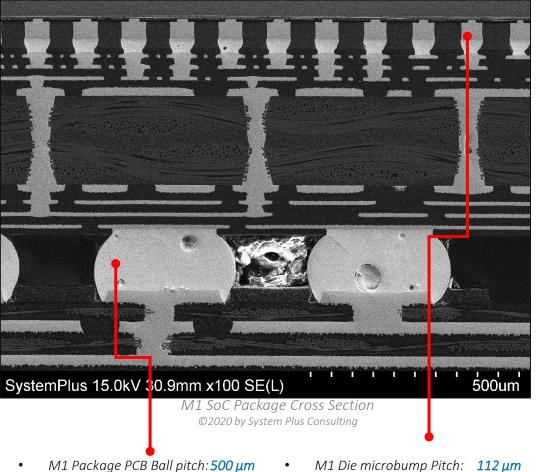

M1 Die microbump Pitch:

Microbump Diameter:

112 μm 56 μm

# M1 Package Opening

## Overview / Introduction

## Company Profile & Supply Chain

#### **Physical Analysis**

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- Package Opening

- Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

Report Ref.: SP20608

©2020 by System Plus Consulting

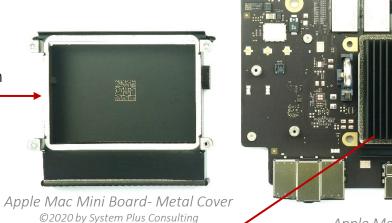

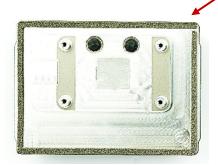

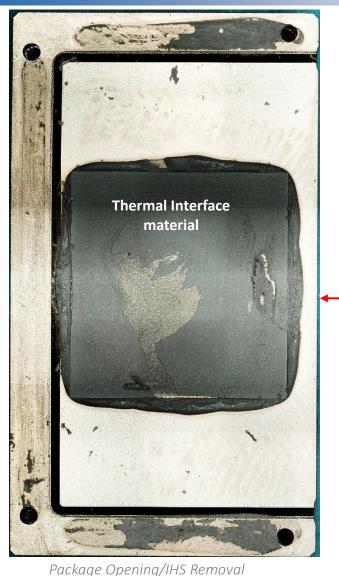

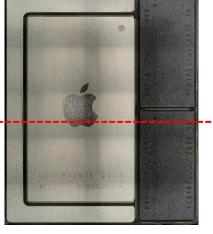

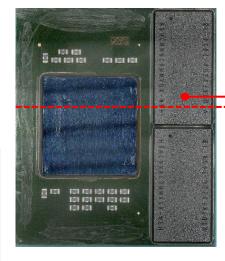

Metal Cover (IHS) Removal

Package Opening/ Metal cover removal ©2020 by System Plus Consulting

Thermal Interface material (TIM) is used as an interface between the M1 SoC Die and the top metal cover to maximize heat dissipation.

### Company Profile & Supply Chain

### **Physical Analysis**

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- Package Opening

- Cross Section 1

- Cross Section 2

- o M1 Package Process

#### o DRAM

- Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

### Report Ref.: SP20608

# M1 Package Opening

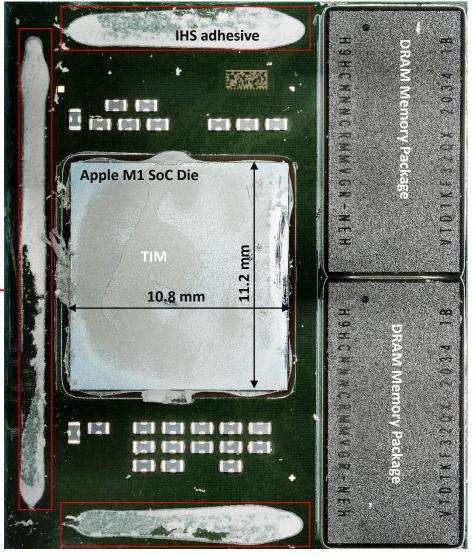

Package Opening/ Metal cover and TIM removal @2020 hy System Plus Consulting

Package Opening ©2020 by System Plus Consulting

Package Opening ©2020 by System Plus Consulting

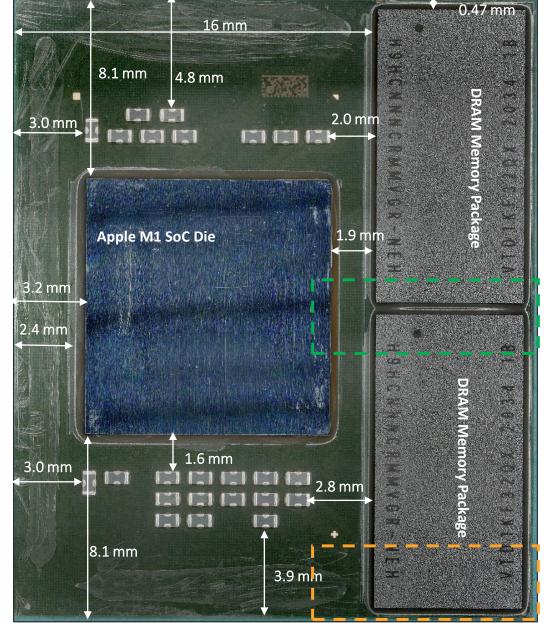

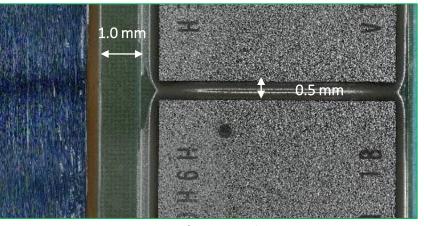

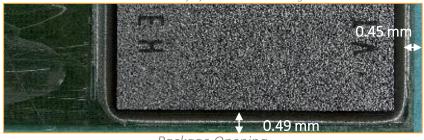

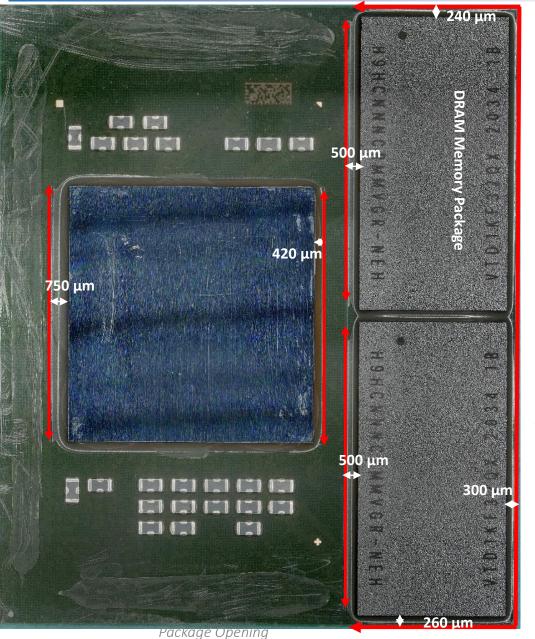

- The M1 packages contains 24 passive capacitors positioned on the front side of the M1 SoC Package PCB.

- Passive Components on PCB: 24 (0402) Capacitors.

## Component to Edge:

| • | Top DRAM to package substrate :                 | 0.47 mm |

|---|-------------------------------------------------|---------|

| • | Bottom DRAM to Package substrate edge:          | 0.49 mm |

| • | DRAM Package to Package substrate edge(x-Axis): | 0.45mm  |

| • | M1 SoC Die to Package substrate edge (x axis):  | 3.2 mm  |

| • | M1 SoC Die to Package substrate edge (y axis):  | 8.1 mm  |

## Component to Component

DRAM Package to DRAM Package: 0.5 mm DRAM Package to M1 SoC Die: 1.9 mm

# M1 Package Opening

## Overview / Introduction

## Company Profile & Supply Chain

### **Physical Analysis**

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- Package Opening

- Cross Section 1

- Cross Section 2

- M1 Package Process

#### o DRAM

- o Package Views

- Package X-RAY

- o Package Cross Section

- o Package Opening

- Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

Report Ref.: SP20608

@2020 hy System Plus Consulting

solder resist

Solder resist is deposited to limit underfill diffusion.

SoC Die to solder resist dam left: 750 μm SoC Die to solder resist dam right: 420 µm

DRAM Package to solder resist dam y axis top:  $240 \mu m$ DRAM Package to solder resist dam y axis bottom: 260 μm DRAM Package to solder resist dam x axis left: 500 μm DRAM Package to solder resist dam x axis right: 300 μm

# Package Opening

## Overview / Introduction

## Company Profile & Supply Chain

## Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- Package Opening

- o Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

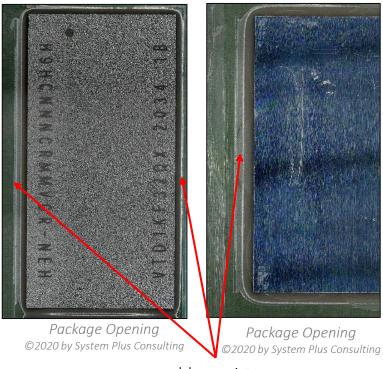

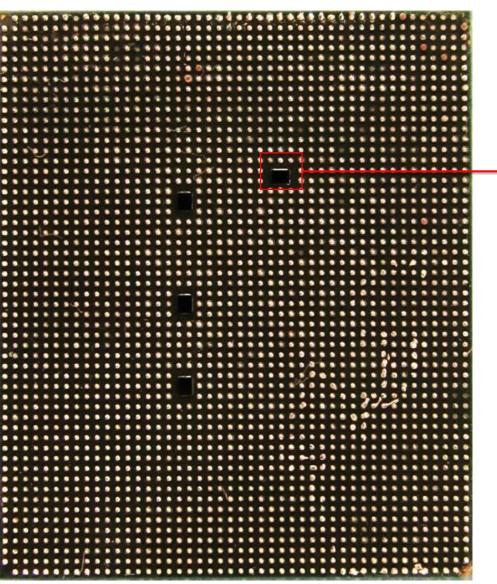

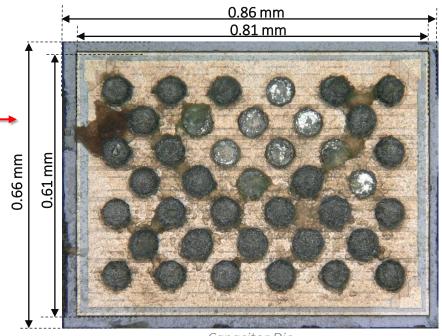

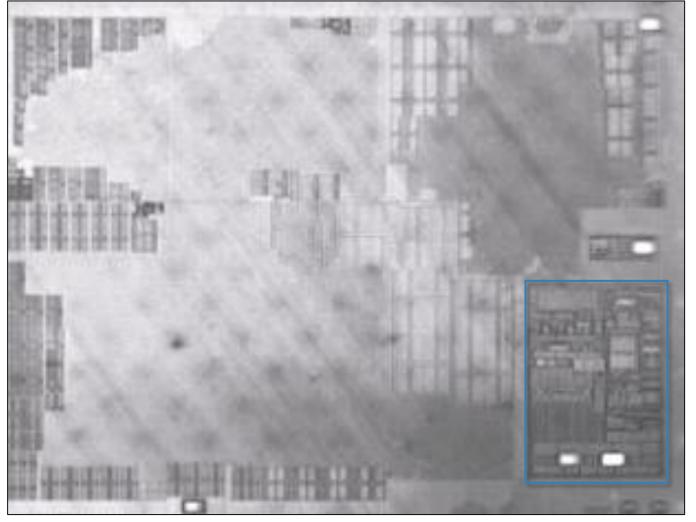

4 Capacitor dies are integrated on the Package PCB.

Capacitor Die ©2020 by System Plus Consulting

Die Dimensions: 0.61 x 0.81 mm

Balls:

Package Back View ©2020 by System Plus Consulting

### Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- Cross Section 1

- o Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

#### FEOL (TEM Analysis)

#### Feedbacks

#### About System Plus

## Report Ref.: SP20608

# M1 Package Cross-Section

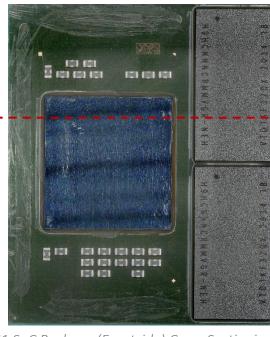

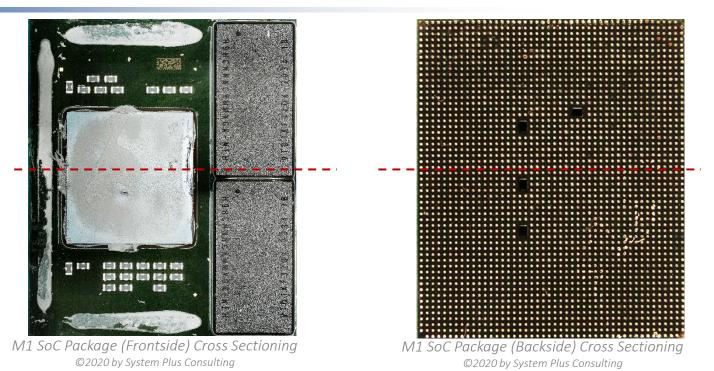

M1 SoC Package (Frontside) Cross Sectioning 1 ©2020 by System Plus Consulting

M1 SoC Package (Backside) Cross Sectioning ©2020 by System Plus Consulting

M1 SoC Package (Frontside) Cross Sectioning 2 ©2020 by System Plus Consulting

# **DRAM Package** M1 SoC Die

## Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- Cross Section 1

- o Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

#### Feedbacks

#### About System Plus

Report Ref.: SP20608

# M1 Package Cross-Section 1

M1 SoC Package (Frontside) Cross Sectioning 1 ©2020 by System Plus Consulting

M1 SoC Package (Backside) Cross Sectioning ©2020 by System Plus Consulting

# M1 Package Cross-Section 1

# Overview / Introduction

### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

## Feedbacks

#### About System Plus

Report Ref.: SP20608

©2020 by System Plus Consulting

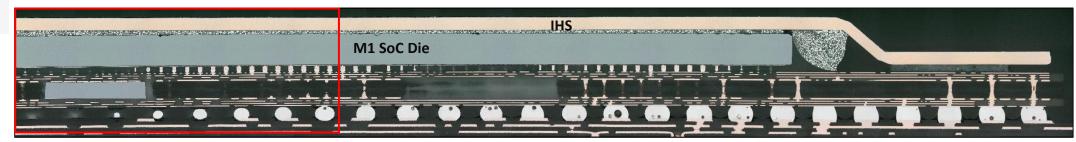

- Embedded capacitor

- The IHS covers the M1 SoC Die and not the DRAM Memory Package.

- A TIM Material is placed between the M1 SoC Die that potentially produces heat and the IHS metal cover to enhance the thermal coupling between the die and the IHS.

- Capacitors are embedded in the M1 SoC Package.

### Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- Cross Section 1

- o Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

### FloorPlan

## FEOL (TEM Analysis)

### Feedbacks

## About System Plus

## Report Ref.: SP20608

# M1 Package Cross-Section 1

M1 SoC Package Cross Section 1 ©2020 by System Plus Consulting

M1 SoC Package Cross Section 1 ©2020 by System Plus Consulting

# Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- Cross Section 1

- Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- Package CrossSection

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### <u>FloorPlan</u>

#### FEOL (TEM Analysis)

#### **Feedbacks**

#### About System Plus

M1 Package Cross-Section 1

### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

Feedbacks

About System Plus

# M1 Package Cross-Section 1

M1 SoC Package Cross Section 1 ©2020 by System Plus Consulting

TIM Material

100 µm

2000

M1 SoC Package Cross Section 1 ©2020 by System Plus Consulting

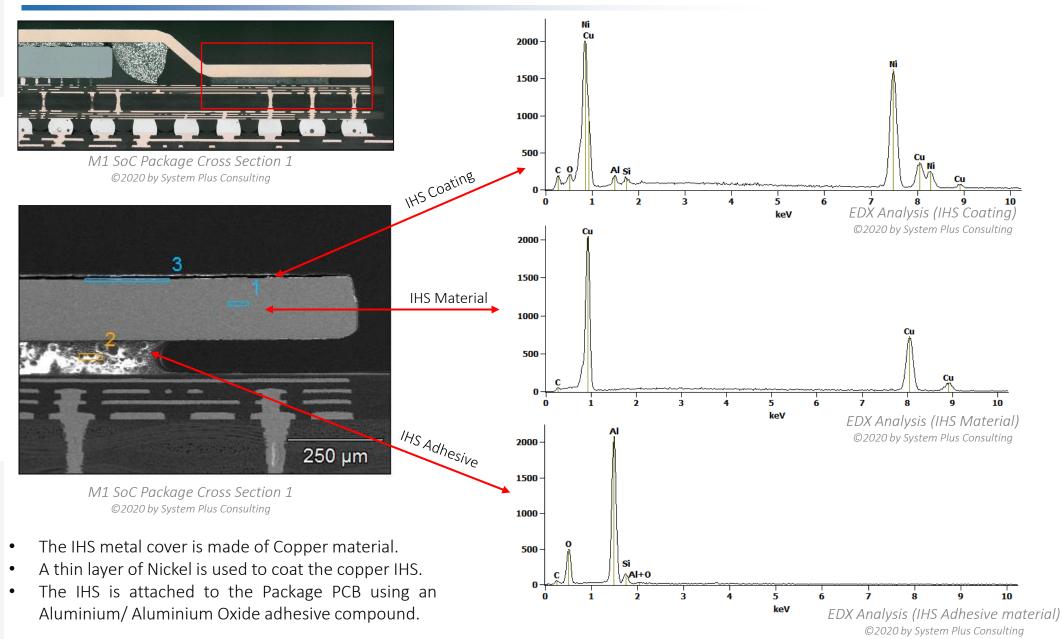

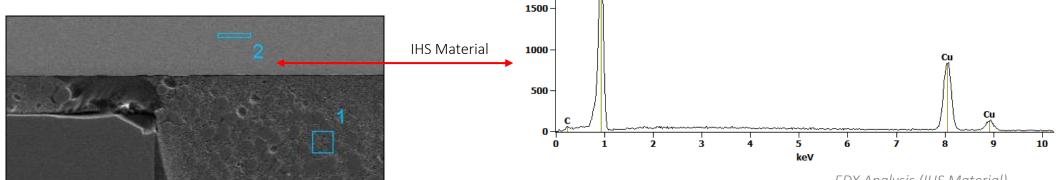

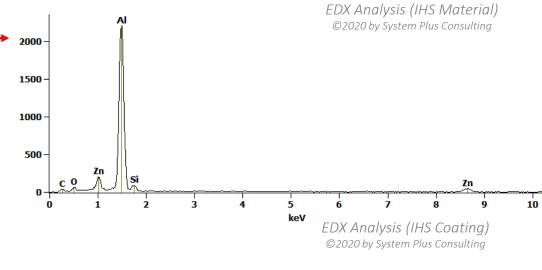

- The IHS metal cover is made of Copper material.

- The Thermal interface material (TIM) is made of an aluminium based compound with Zn traces.

# M1 Package Cross-Section 1

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

### Feedbacks

#### About System Plus

©2020 by System Plus Consulting | Apple M1 SoC 56

### Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

**About System Plus**

Report Ref.: SP20608

# M1 Package Cross-Section 1

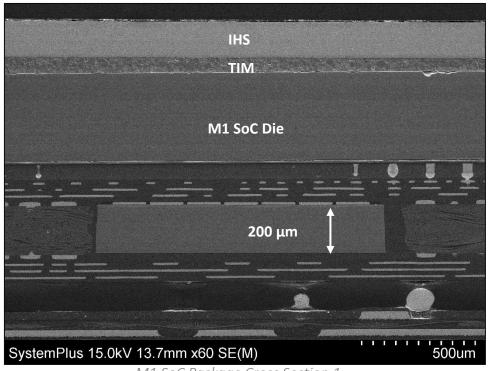

The embedded capacitor is directly connected to the PCB using a large copper pillar.

M1 SoC Package Cross Section 1 ©2020 by System Plus Consulting

M1 SoC Package Cross Section 1 ©2020 by System Plus Consulting

M1 SoC Package Cross Section 1 ©2020 by System Plus Consulting ©2020 by System Plus Consulting | Apple M1 SoC 57

### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- Cross Section 1

- o Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

Report Ref.: SP20608

# M1 Package Cross-Section 1

M1 SoC Package Cross Section 1 ©2020 by System Plus Consulting

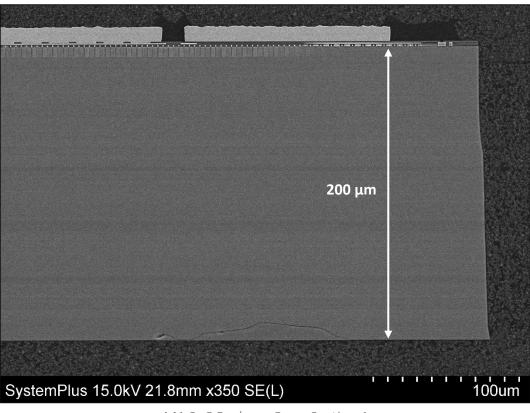

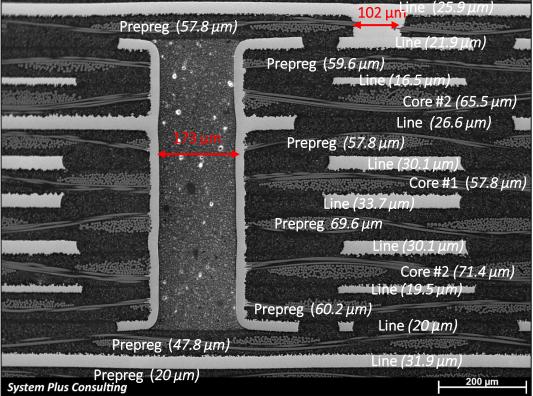

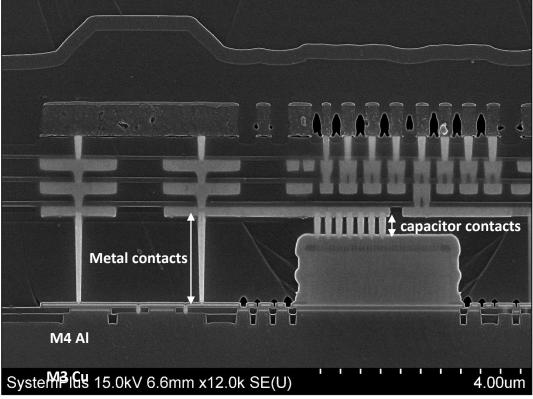

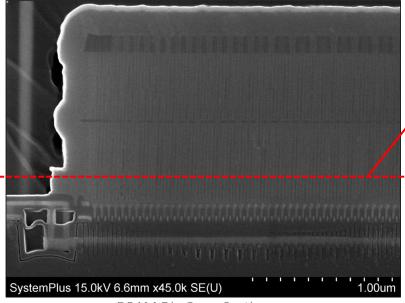

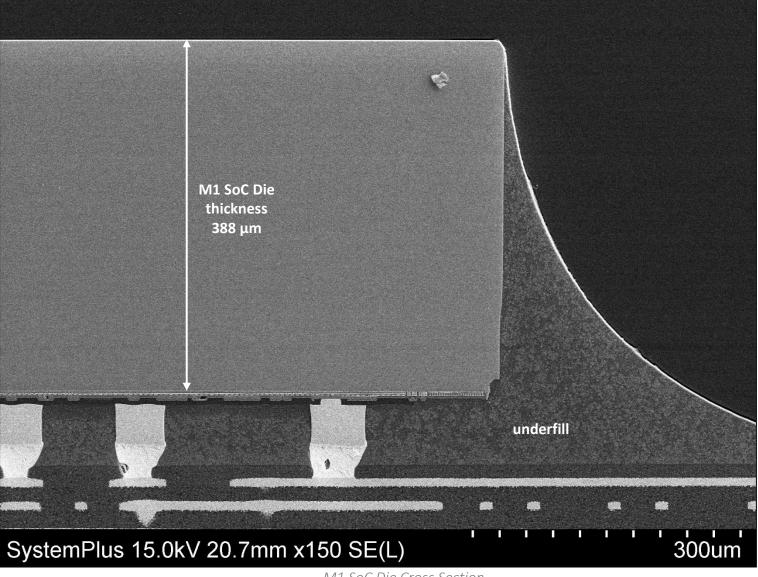

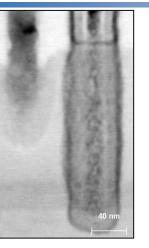

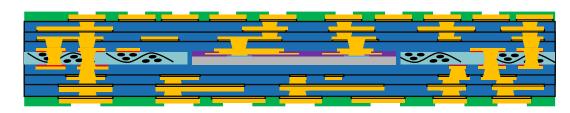

- Die thickness : 200 μm

- The die process uses 2 Copper metal layers (2 Cu)

- A large copper pillar is used to join the capacitor to the package PCB.

### Company Profile & Supply Chain

### **Physical Analysis**

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- Package Opening

- Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

### Report Ref.: SP20608

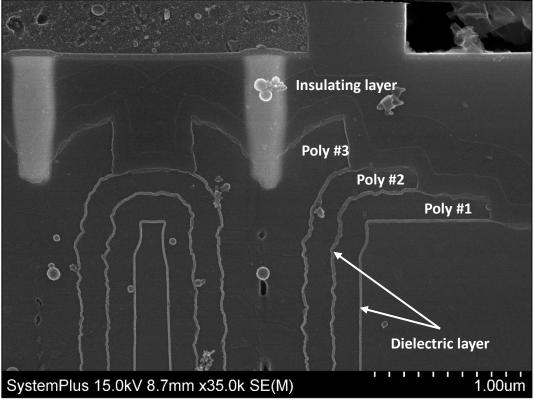

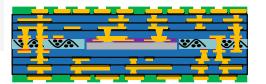

# M1 Package Cross-Section 1

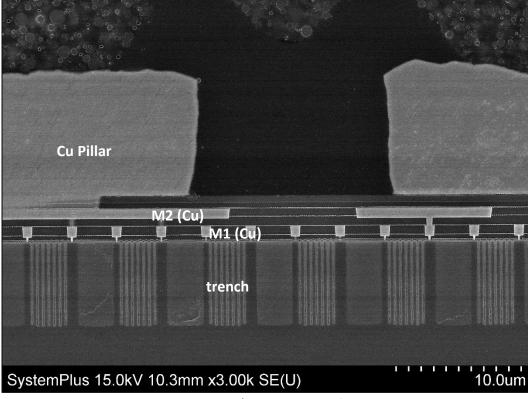

M1 SoC Package Cross Section 1 ©2020 by System Plus Consulting

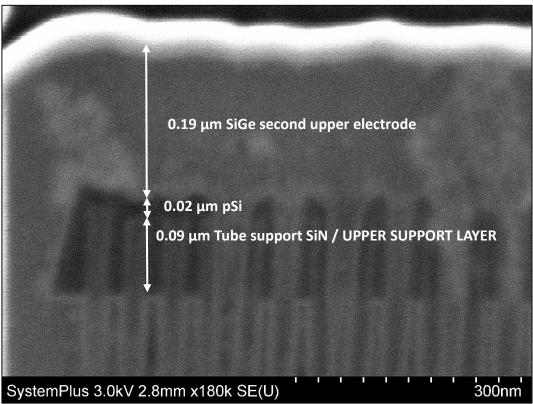

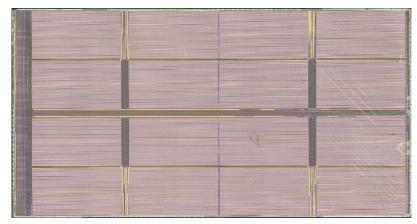

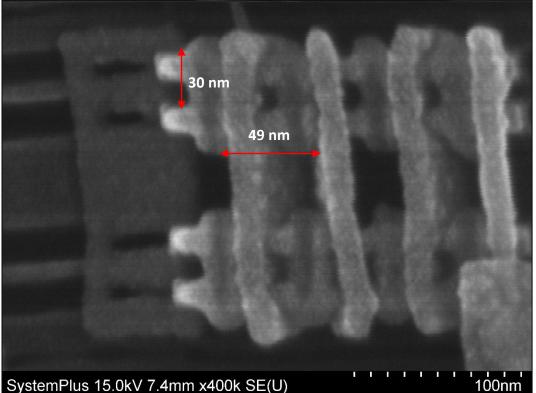

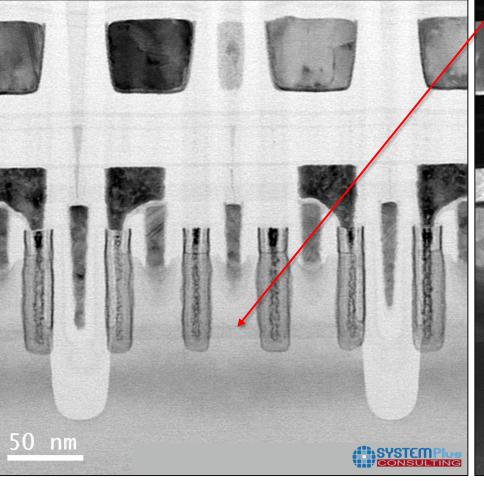

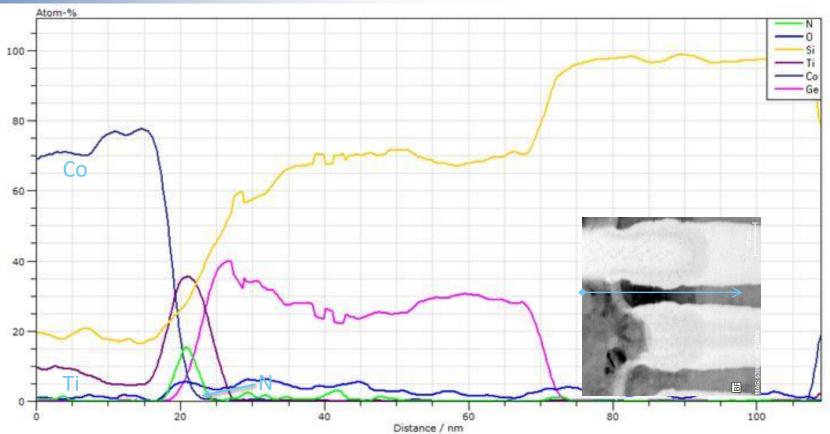

M1 (Cu) SiN layer oxide Poly #4 (21 nm) Poly #3 (21 nm) Poly #2 (27 nm) Poly #1 (27 nm) oxide **Silicon Substate** 500nm SystemPlus 15.0kV 6.6mm x100k SE(U)

M1 SoC Package Cross Section 1 ©2020 by System Plus Consulting

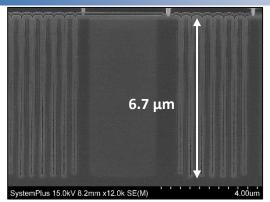

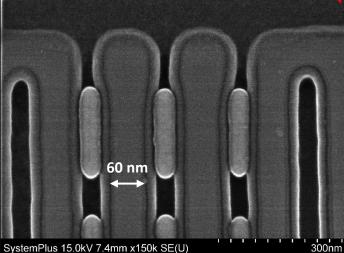

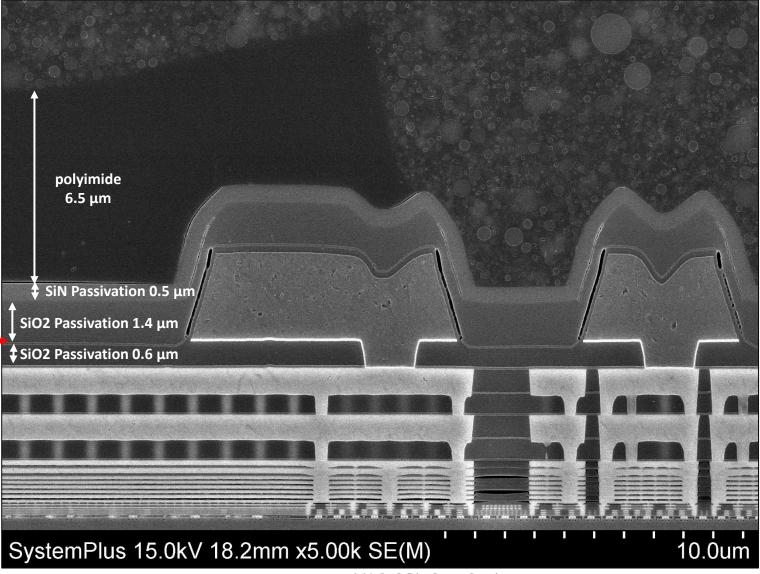

- Trench Depth: 6.7 µm

- 4 layers of polysilicon material are deposited into the trench.

- A dielectric material is deposited between two polysilicon material.

- The trench is then filled with an oxide material.

## Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

## FloorPlan

## FEOL (TEM Analysis)

#### Feedbacks

#### About System Plus

Report Ref.: SP20608

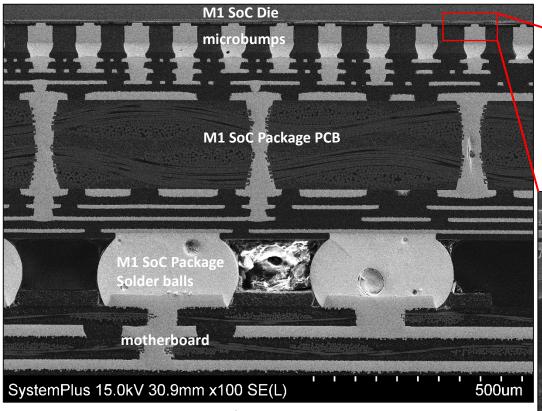

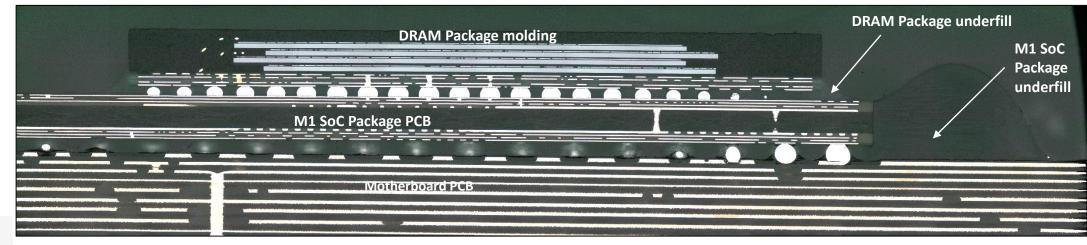

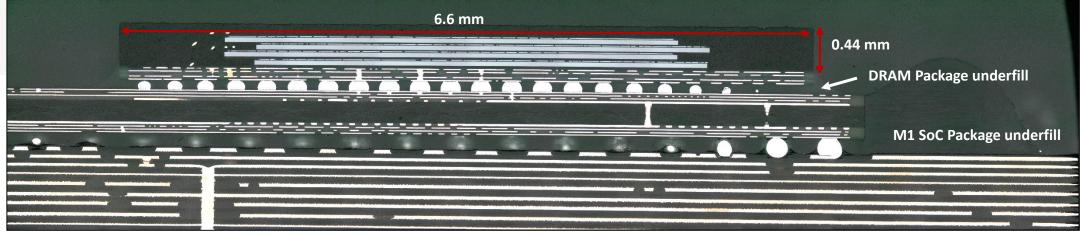

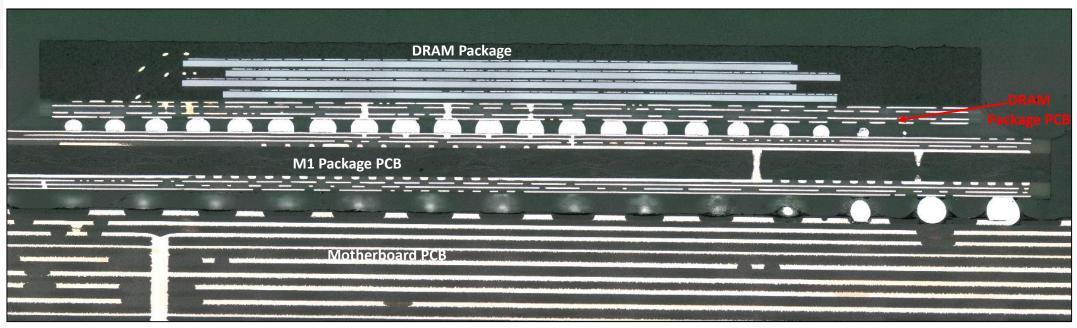

# M1 Package Cross-Section 2

**DRAM Package** and the state of t M1 Package PCB

# M1 Package Cross-Section 2

## Overview / Introduction

# Company Profile & Supply Chain

### **Physical Analysis**

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- Package CrossSection

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

### **Feedbacks**

#### About System Plus

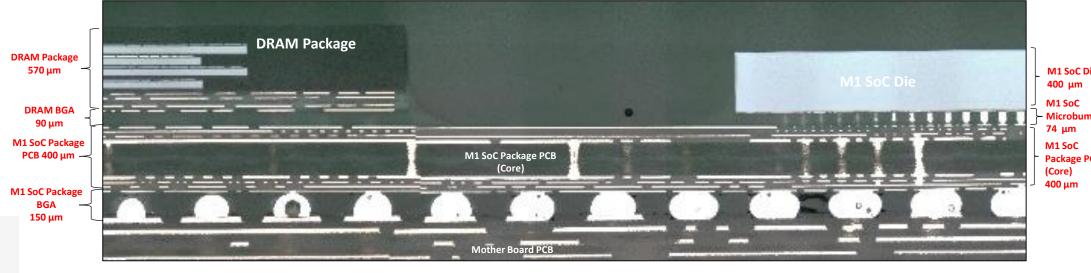

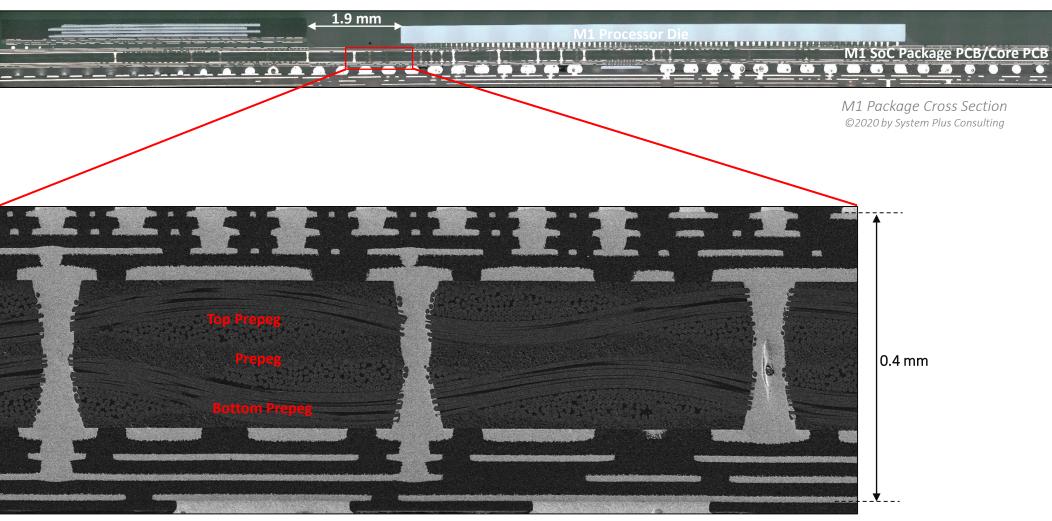

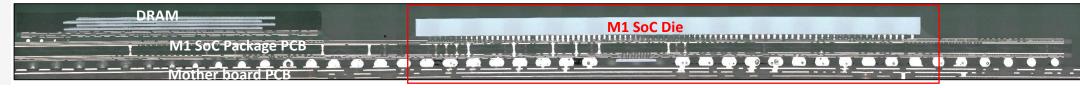

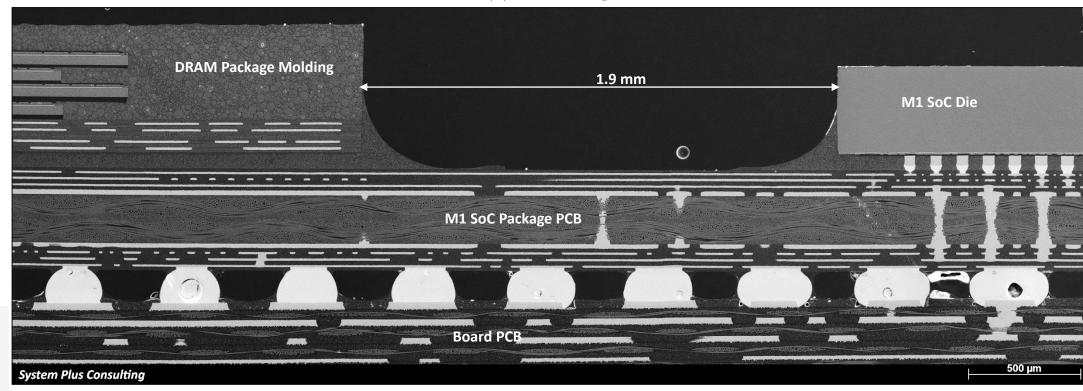

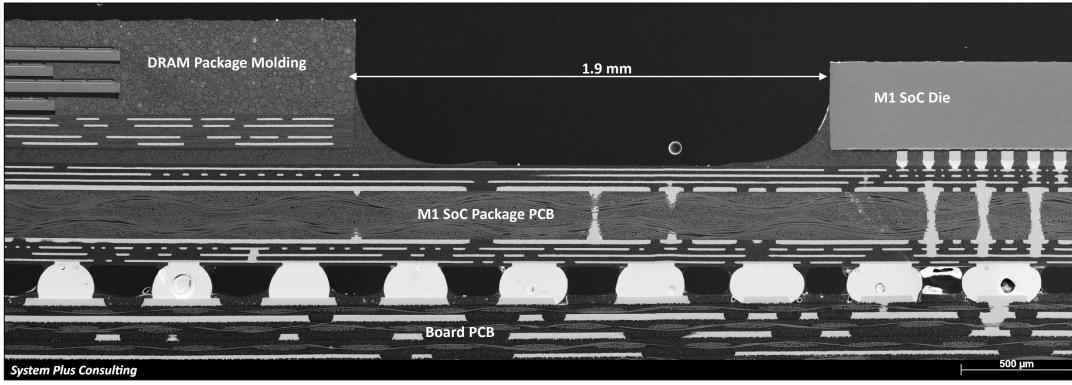

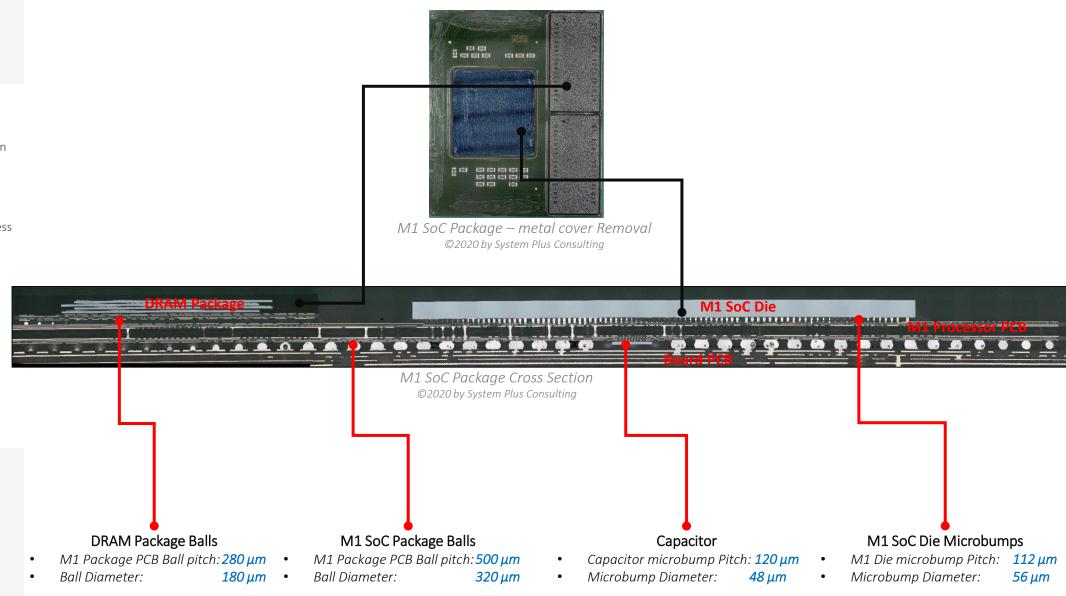

DRAM Package

M1 SoC Die

IVI Package PCB

Mother board PCB

M1 SoC Package Cross Section

©2020 by System Plus Consulting

### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

#### Feedbacks

## About System Plus

Report Ref.: SP20608

# M1 Package Cross-Section 2- MotherBoard

M1 SoC Package Cross Section ©2020 by System Plus Consulting

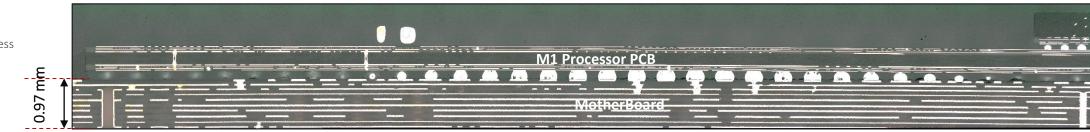

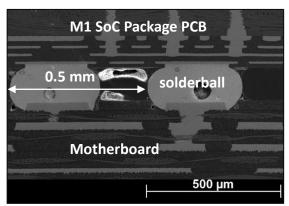

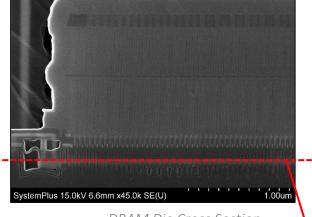

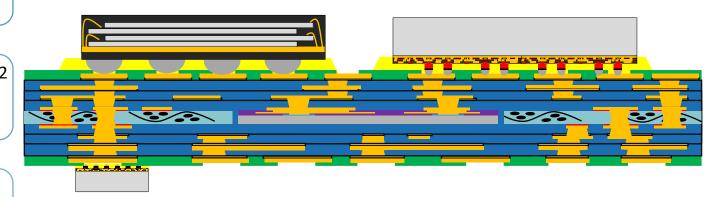

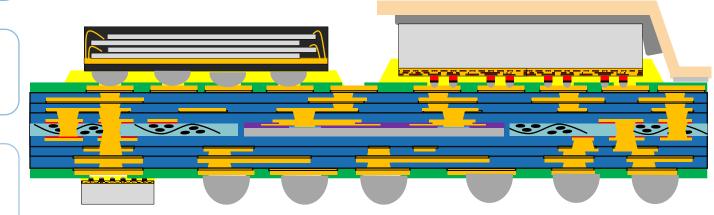

- The M1 SoC Package is placed on a 12-layer PCB (Motherboard)substrate.

- Motherboard PCB Thickness: 0.97 mm

### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

### Feedbacks

#### About System Plus

### Report Ref.: SP20608

# M1 Package Cross-Section 2- MotherBoard

# M1 Package Cross-Section 2- MotherBoard

## Overview / Introduction

### Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- Views & Dimension

- o Package X-RAY

- o Package Opening

- Cross Section 1

- Cross Section 2

- o M1 Package Process

#### o DRAM

- Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

#### FEOL (TEM Analysis)

#### Feedbacks

#### About System Plus

Report Ref.: SP20608

M1 SoC Package Cross Section ©2020 by System Plus Consulting

Motherboard PCB Cross Section

©2020 by System Plus Consulting

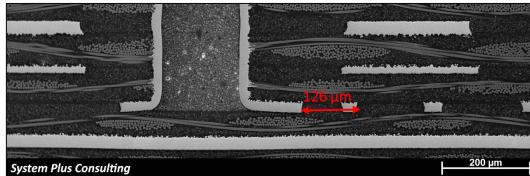

Measured Line/Space Pitch: 126 μm

Smallest Line 28 μm

Motherboard PCB Cross Section

# M1 Package Cross Section 2 – Core PCB

## Overview / Introduction

### Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

### Feedbacks

#### About System Plus

Report Ref.: SP20608

M1 Package PCB Cross Section ©2020 by System Plus Consulting

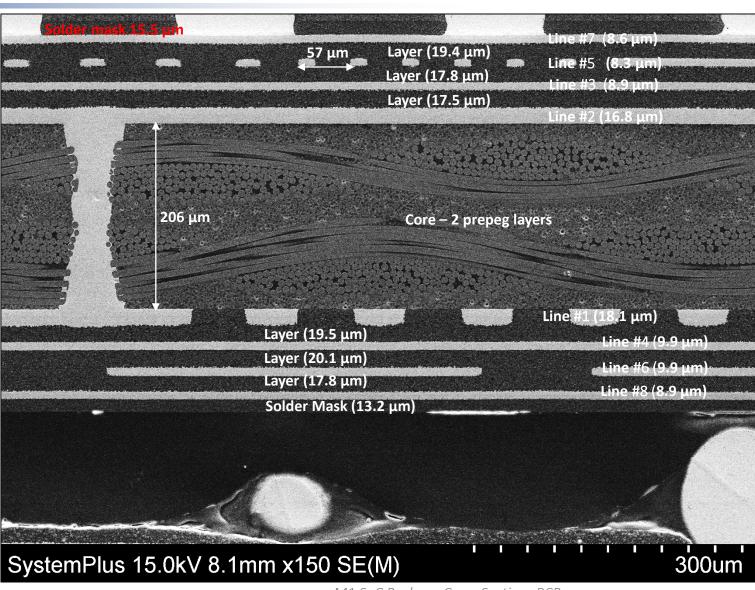

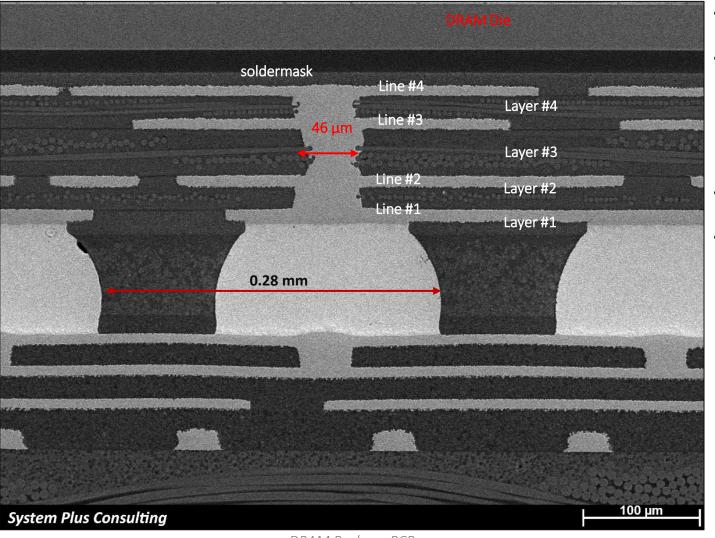

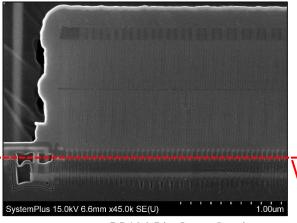

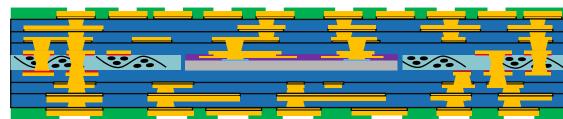

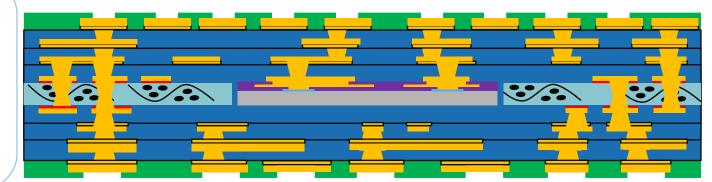

- The Apple M1 SoC package includes substrate with 8 Copper layers.

- Substrate thickness: 0.4 mm

### Company Profile & Supply Chain

### **Physical Analysis**

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- Views & Dimension

- Package X-RAY

- Package Opening

- Cross Section 1

- Cross Section 2

- o M1 Package Process

#### o DRAM

- Package Views

- o Package X-RAY

- o Package Cross Section

- Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- Die Delayering

- o Die Cross Section

#### FloorPlan

#### FEOL (TEM Analysis)

### Feedbacks

## About System Plus

Report Ref.: SP20608

# M1 Package Cross Section 2 – M1 Package PCB

- PCB Copper MicroVia Diameter: 40 μm

- Measured Line/Space Pitch : 57 μm

- Smallest Line 18 μm

The PCB Package is joined to the mother board using solder balls.

M1 SoC Package Cross Section-PCB ©2020 by System Plus Consulting

# M1 Package Cross Section 2- M1 Package PCB

## Overview / Introduction

### Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

Report Ref.: SP20608

FLI & DRAM Interconnect Map – X-Ray View

©2020 by System Plus Consulting

M1 SoC Package Cross Section ©2020 by System Plus Consulting

©2020 by System Plus Consulting

©2020 by System Plus Consulting

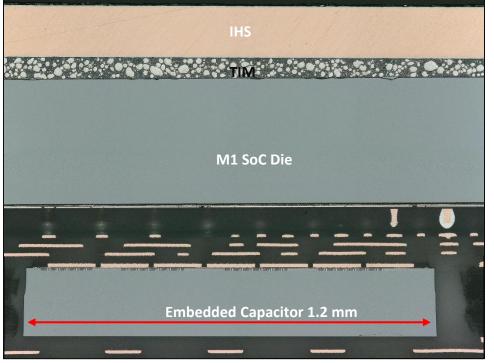

Four Capacitors are integrated on the backside of the M1 SoC Package PCB.

M1 SoC Package Backside

## Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

### Report Ref.: SP20608

# M1 Package Cross Section 2- Package PCB

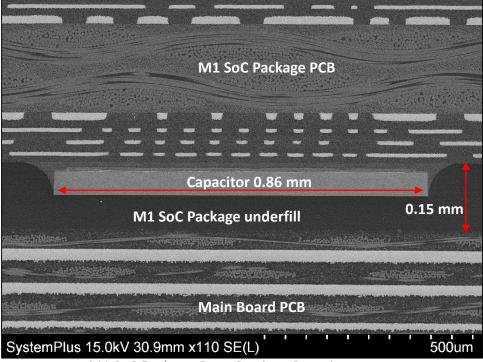

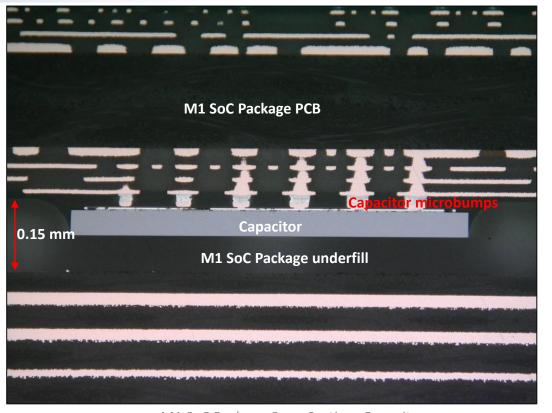

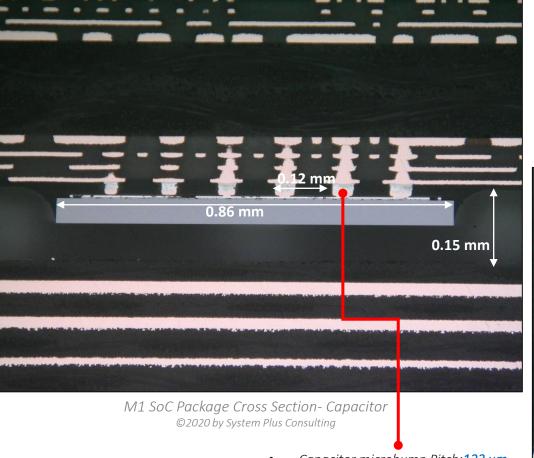

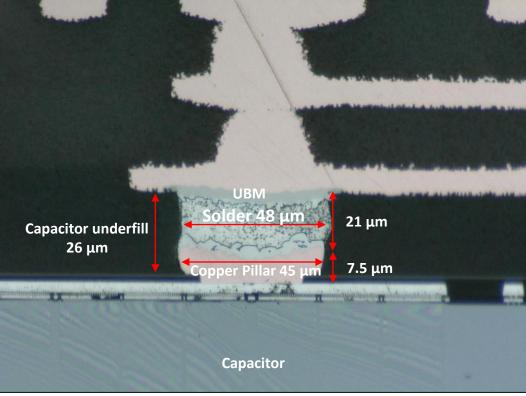

- The capacitors are joined to the M1 SoC Package PCB using microbumps.

- The capacitor is placed in flip chip position and joined to the PCB by a reflow process.

M1 SoC Package Cross Section- Capacitor ©2020 by System Plus Consulting

# M1 Package Cross Section 2- Package PCB

### Overview / Introduction

## Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

Feedbacks

About System Plus

Report Ref.: SP20608

Capacitor microbump Pitch: 123 µm

Microbump Diameter: 48 μm The copper pillar is in direct contact with the capacitor top metal layer.

Microbumps Pitch: 120 μm Copper pillar diameter: 45 μm Solder Ball diameter: 48 μm Capacitor Underfill thickness: 26 μm

## Company Profile & Supply Chain

### **Physical Analysis**

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

#### Feedbacks

#### About System Plus

### Report Ref.: SP20608

# M1 Package Cross Section 2- Package PCB

M1 SoC Package Cross Section- Capacitor ©2020 by System Plus Consulting

M1 SoC Package Cross Section- Capacitor ©2020 by System Plus Consulting

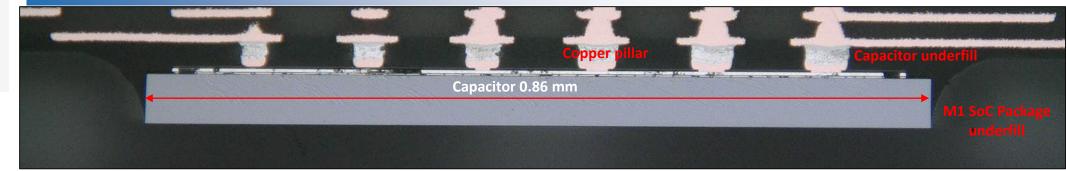

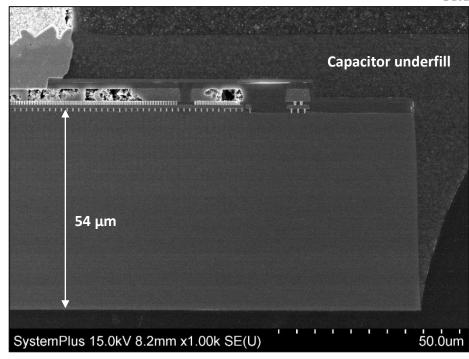

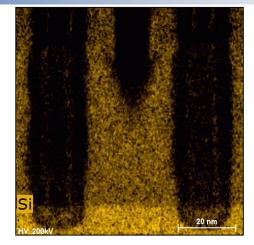

- The capacitors are placed on the M1 SoC Package PCB face down, the capacitors are connected to the PCB using micro bumps.

- Capacitor thickness: 54 μm

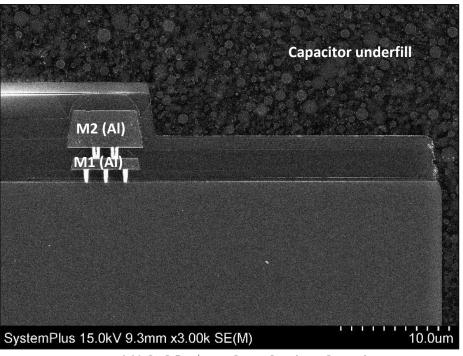

- The capacitor Die process uses 2 Aluminium metal layers.

## Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- Views & Dimension

- Package X-RAY

- Package Opening

- Cross Section 1

- Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- Package Cross Section

- o Package Opening

- Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

### Feedbacks

## About System Plus

### Report Ref.: SP20608

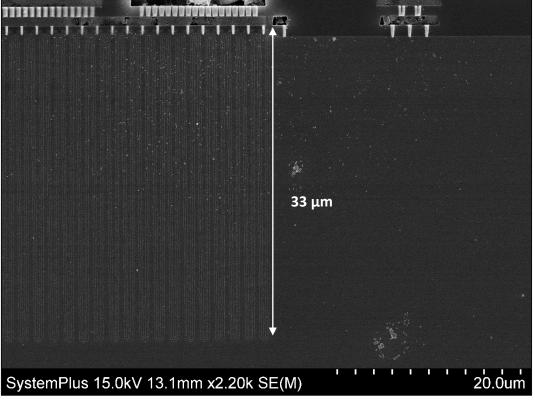

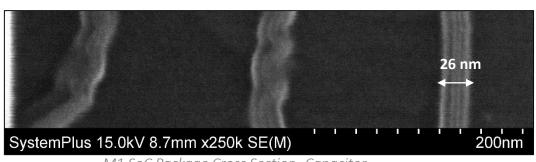

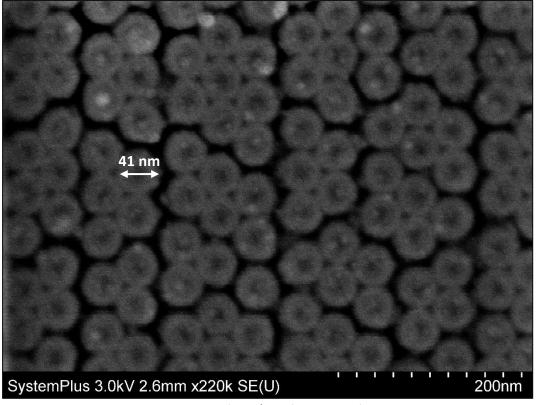

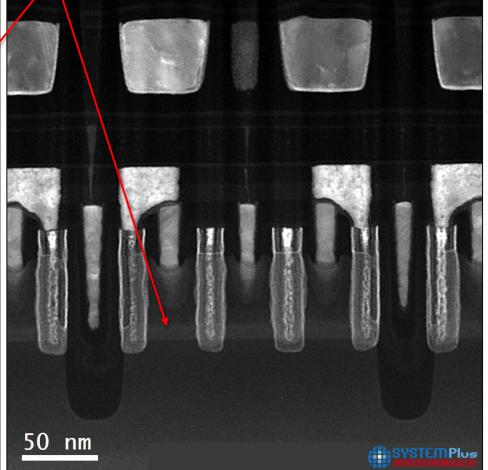

# M1 Package Cross Section 2- Package PCB

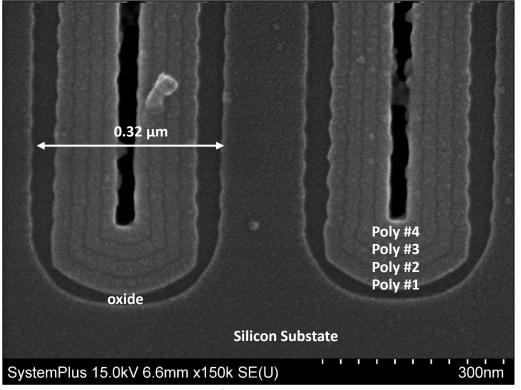

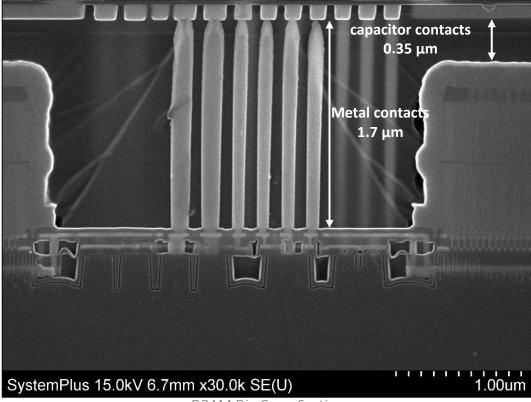

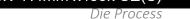

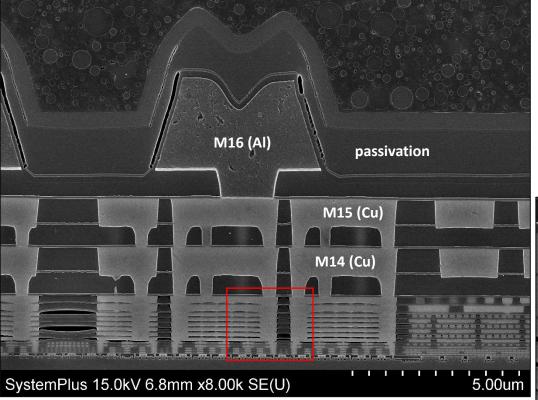

- Trench thickness: 33 um

- Si is etched to form a deep trench. Polysilicon is deposited and a dielectric layer is deposited between two polysilicon materials.

- Dielectric layer: 26 nm

- The capacitor process uses 3 polysilicon layers.

M1 SoC Package Cross Section- Capacitor ©2020 by System Plus Consulting

# M1 Package Cross Section 2

#### Overview / Introduction

### Company Profile & Supply Chain

### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

## FEOL (TEM Analysis)

#### Feedbacks

#### About System Plus

Report Ref.: SP20608

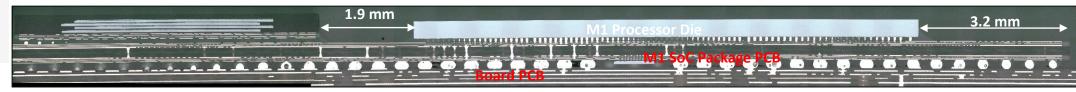

M1 SoC Package Cross Section ©2020 by System Plus Consulting

- Distance between DRAM Package and M1 Die: 1.9 mm

- M1 SoC Die distance to PCB edge: 3.2 mm

#### Company Profile & Supply Chain

#### **Physical Analysis**

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

#### o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

#### o M1 SoC Die

- o Die Views

- o Die Marking

- Die Delayering

- o Die Cross Section

#### FloorPlan

#### FEOL (TEM Analysis)

#### Feedbacks

#### About System Plus

Report Ref.: SP20608

### M1 Package Cross Section 2

M1 SoC Package Cross Section ©2020 by System Plus Consulting

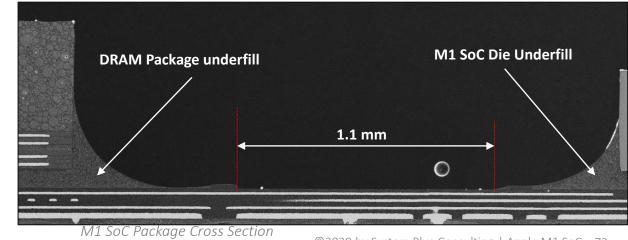

Distance between DRAM Package and M1 Die:

1.9 mm

- Distance between DRAM underfill and M1 SoC Die underfill: 1.1 mm

- The M1 SoC die was attached to the package PCB prior to the DRAM Package. The gap between the M1 SoC and the DRAM is large enough to avoid the overlap of the CUFs.

### M1 Package Cross Section 2

#### Overview / Introduction

# Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- Package CrossSection

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

#### FEOL (TEM Analysis)

#### **Feedbacks**

#### About System Plus

Report Ref.: SP20608

M1 SoC Package Cross Section

©2020 by System Plus Consulting

M1 SoC Package Cross Section

©2020 by System Plus Consulting

M1 SoC Package Cross Section ©2020 by System Plus Consulting

# M1 Package Cross Section 2

#### Company Profile & Supply Chain

Overview / Introduction

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

#### FEOL (TEM Analysis)

#### Feedbacks

#### **About System Plus**

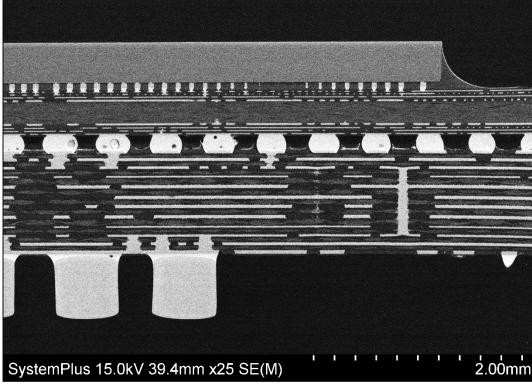

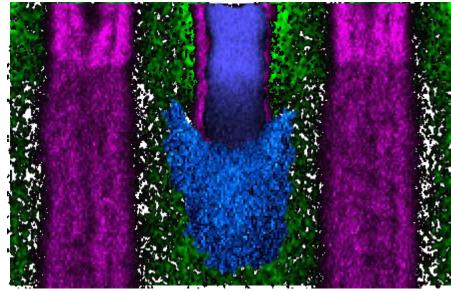

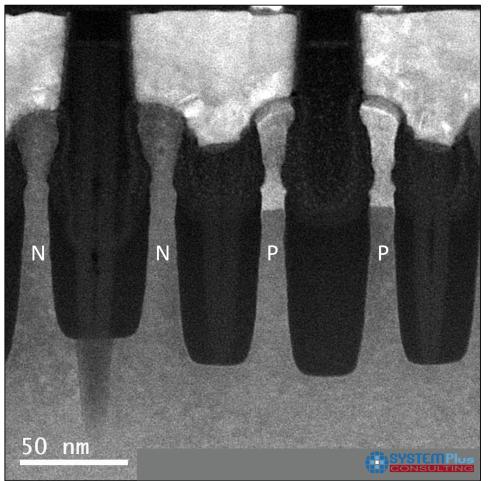

M1 **Processor** Die M1 SoC Die underfill M1 SoC PCB **Passive** capacito 2.00mm SystemPlus 15.0kV 39.4mm x25 SE(M)

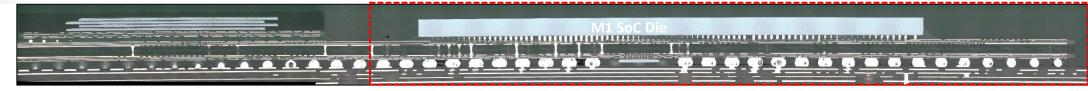

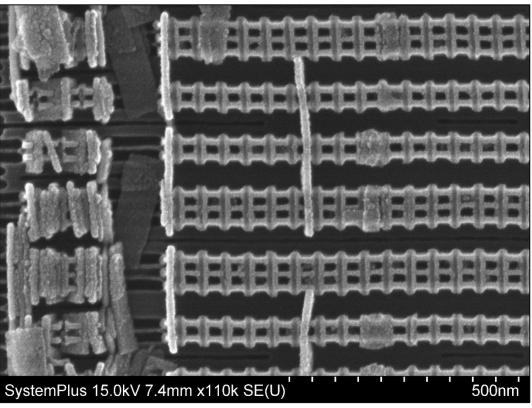

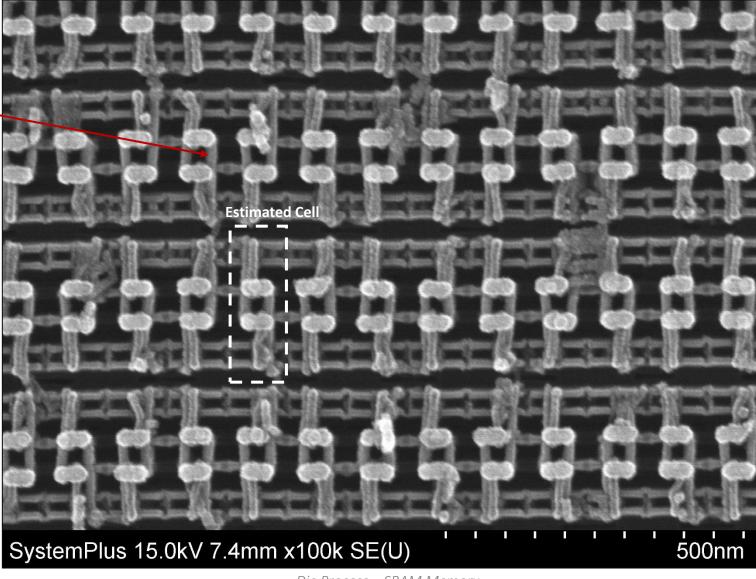

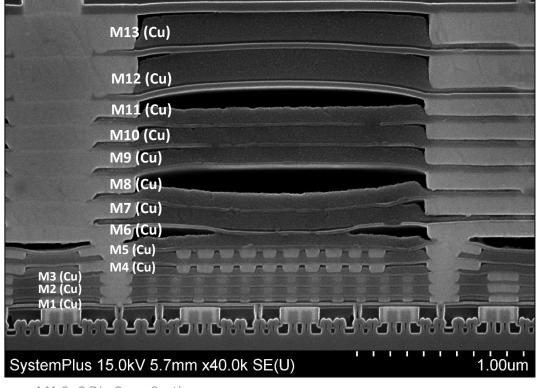

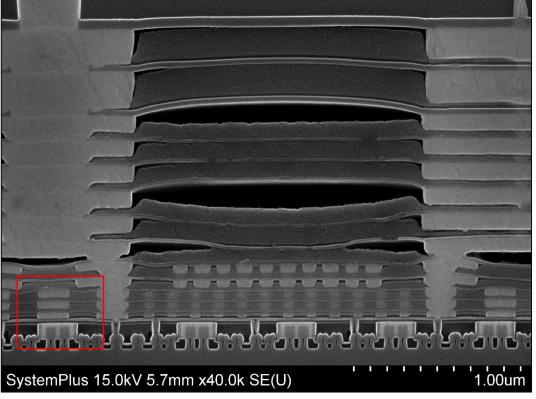

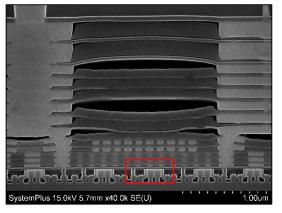

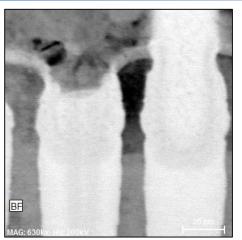

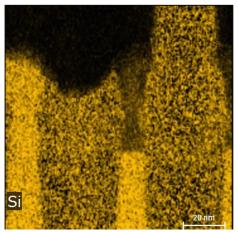

The M1 SoC die is placed in face down on the PCB substrate.

M1 SoC Package Cross Section ©2020 by System Plus Consulting

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

### M1 Package Cross Section 2

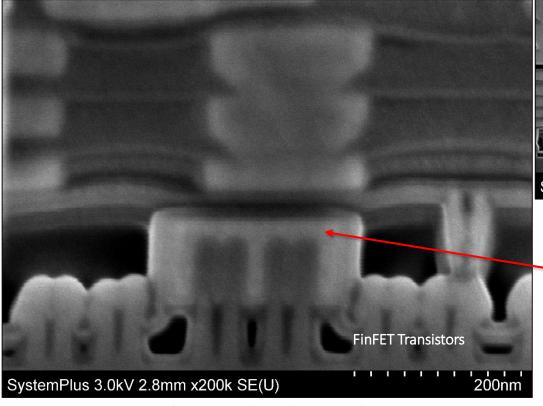

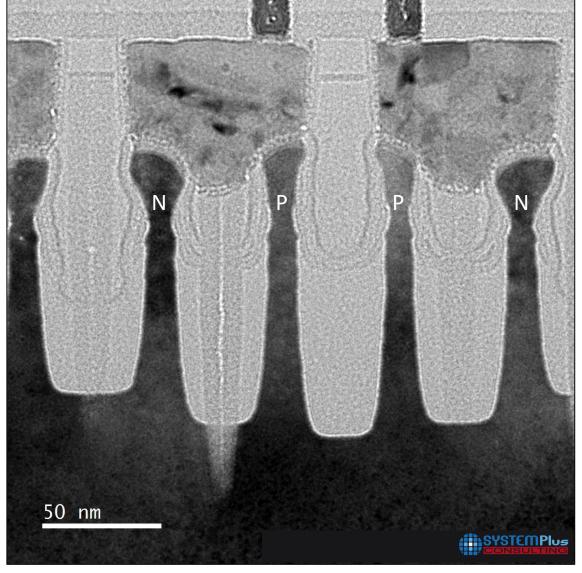

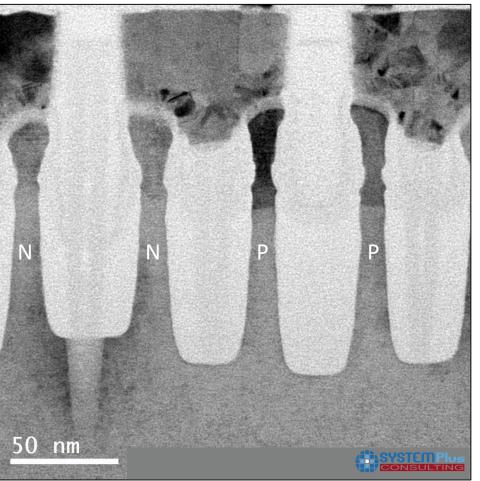

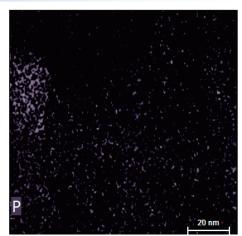

- The M1 SoC die is placed in flip chip position on to the PCB substrate.

- Microbumps connect the M1 die to the M1 Package PCB.

M1 die microbump pitch: 112 μm M1 Package PCB Ball pitch: 500 μm

M1 SoC Package Cross Section ©2020 by System Plus Consulting

*M1 Die microbump Pitch:* 112 μm Microbump Diameter: 56 μm

M1 Package PCB Ball pitch: 500 μm Ball Diameter: 320 µm

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- Die Delayering

- o Die Cross Section

#### FloorPlan

#### FEOL (TEM Analysis)

Feedbacks

About System Plus

Report Ref.: SP20608

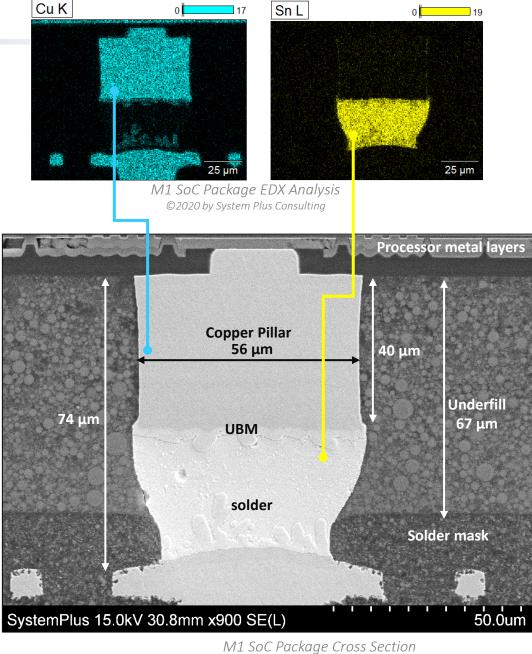

### M1 Package Cross Section 2

- Ball Diameter: 320 um

- Microbump Diameter: 56 μm

- Copper pillar diameter: 56 μm Underfill thickness: 67 μm

- The microbump solder uses a Tin (Sn) compound solder paste.

©2020 by System Plus Consulting

# M1 Package Cross Section 2

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

**About System Plus**

M1 SoC Package Cross Section ©2020 by System Plus Consulting

The copper pillar is in direct contact with the M1 SoC Die top metal layer.

M1 SoC Package Cross Section ©2020 by System Plus Consulting

©2020 by System Plus Consulting | Apple M1 SoC 78

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

#### FEOL (TEM Analysis)

#### Feedbacks

#### About System Plus

#### Report Ref.: SP20608

### M1 Package Cross Section 2

M1 SoC Package Cross Section ©2020 by System Plus Consulting

M1 SoC Package Cross Section ©2020 by System Plus Consulting

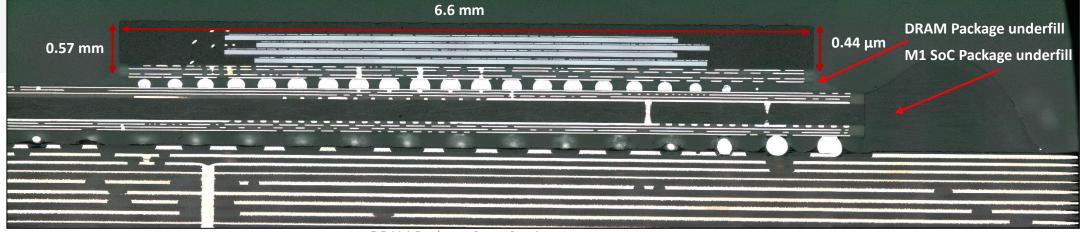

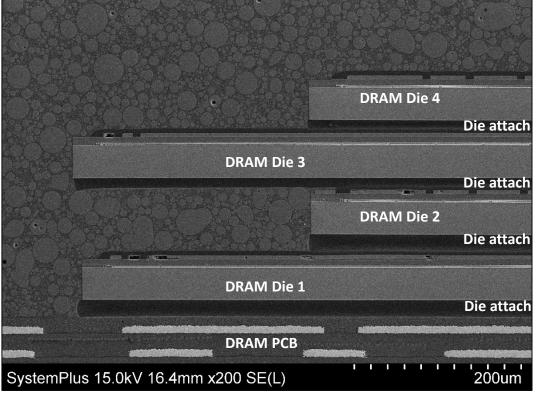

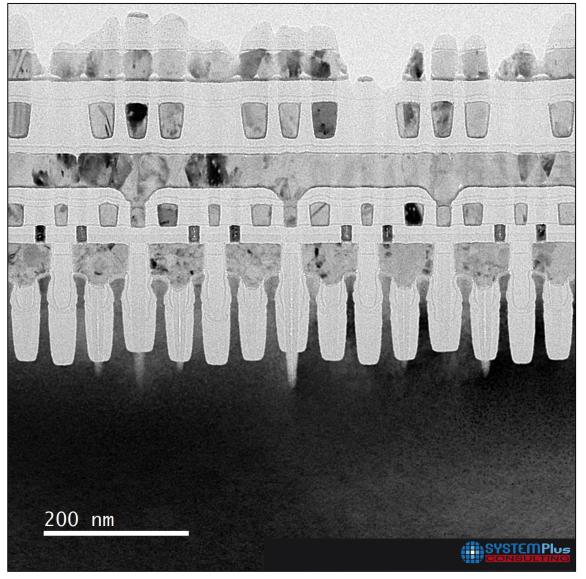

- DRAM Package is mounted on M1 SoC Package PCB.

- Two different types of underfill are used for the DRAM Package and for the M1 SoC Package PCB.

### M1 Package Cross Section 2

#### Overview / Introduction

#### Company Profile & Supply Chain

#### Physical Analysis

- o Apple Mac Mini Teardown

- o Apple M1 Package Analysis

- o Views & Dimension

- o Package X-RAY

- o Package Opening

- o Cross Section 1

- Cross Section 2

- o M1 Package Process

- o DRAM

- o Package Views

- o Package X-RAY

- o Package Cross Section

- o Package Opening

- o Die Views

- o Die Cross Section

- o M1 SoC Die

- o Die Views

- o Die Marking

- o Die Delayering

- o Die Cross Section

#### FloorPlan

FEOL (TEM Analysis)

Feedbacks

About System Plus

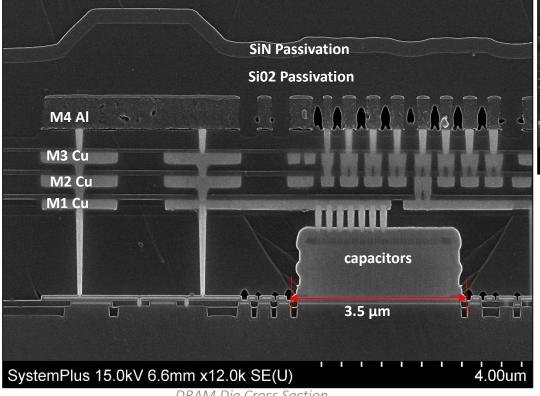

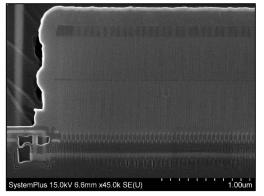

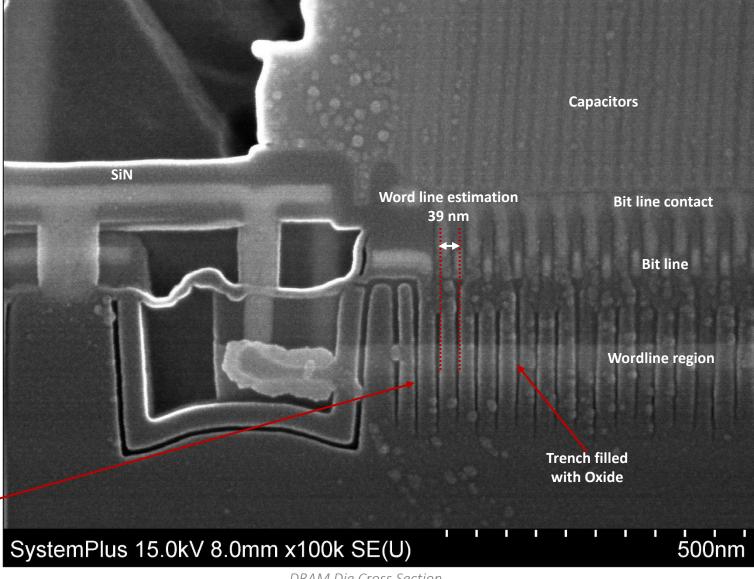

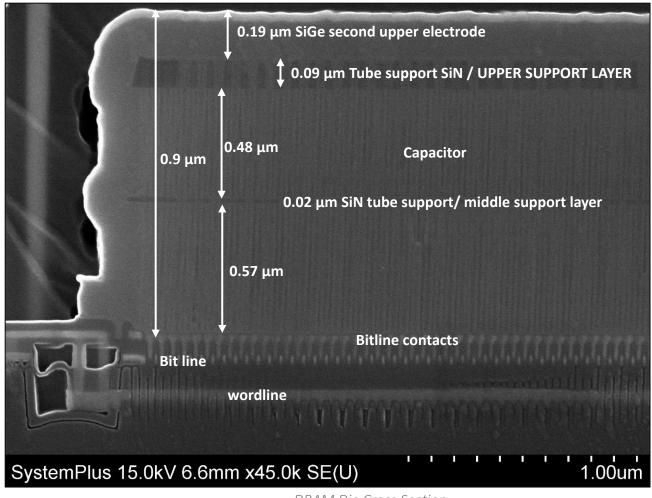

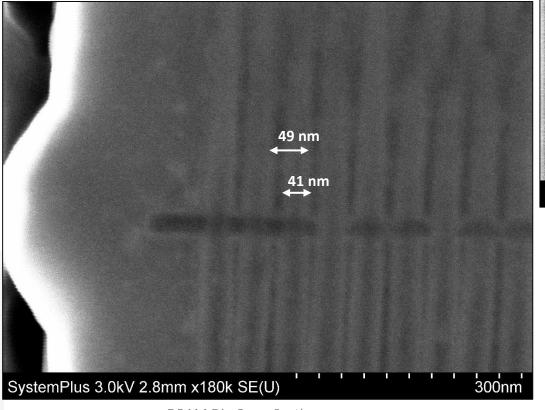

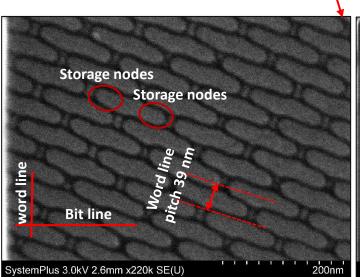

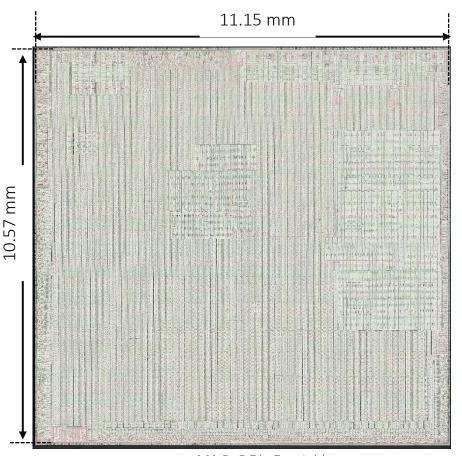

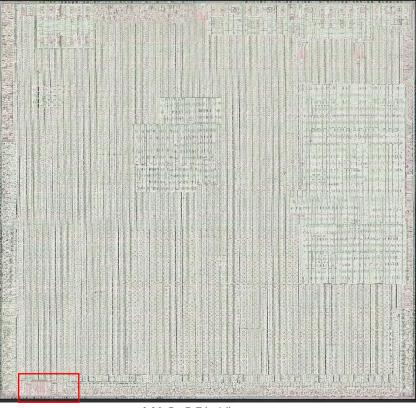

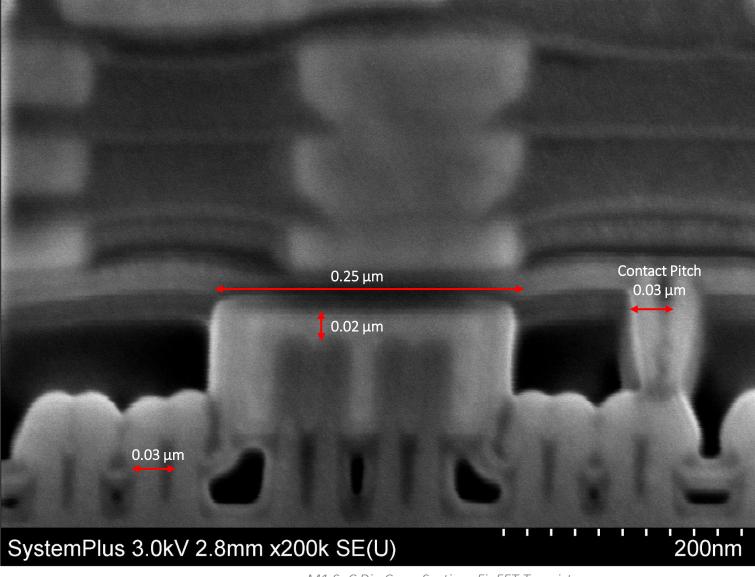

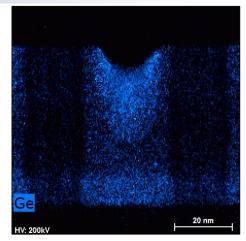

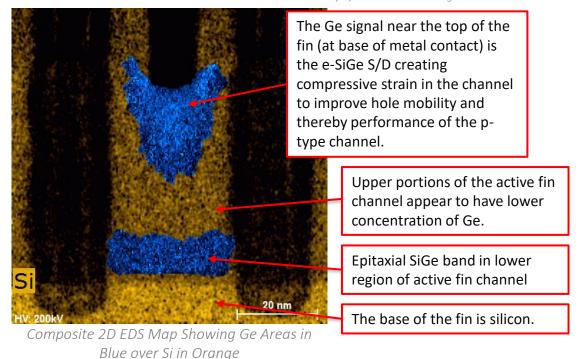

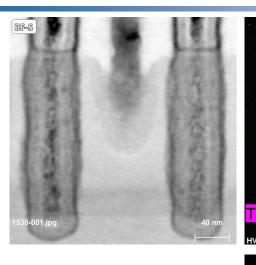

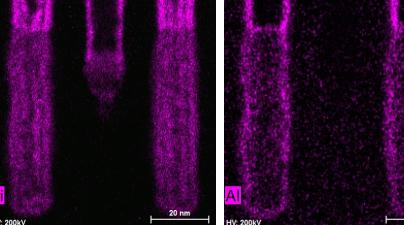

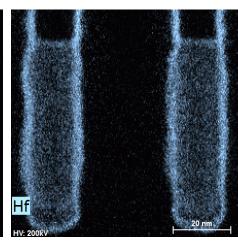

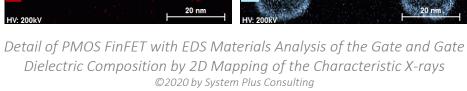

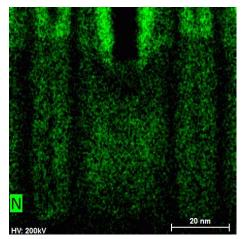

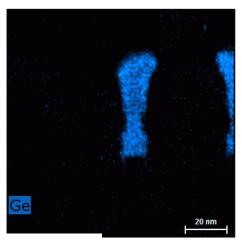

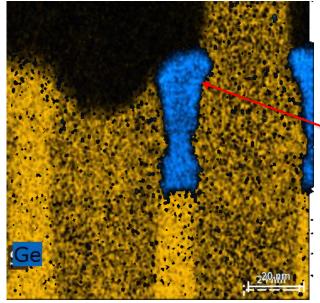

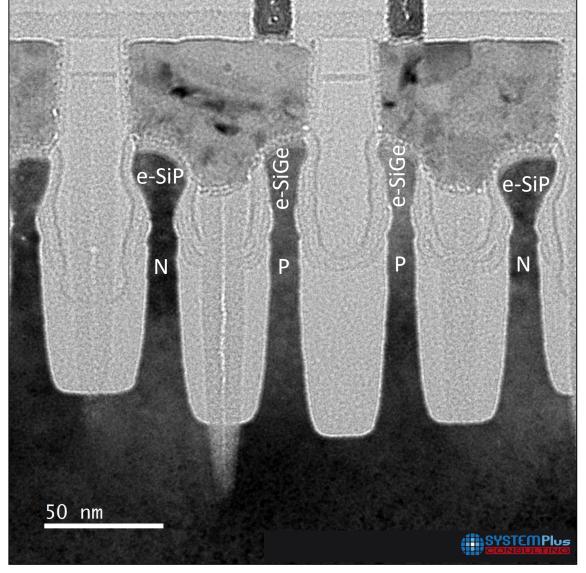

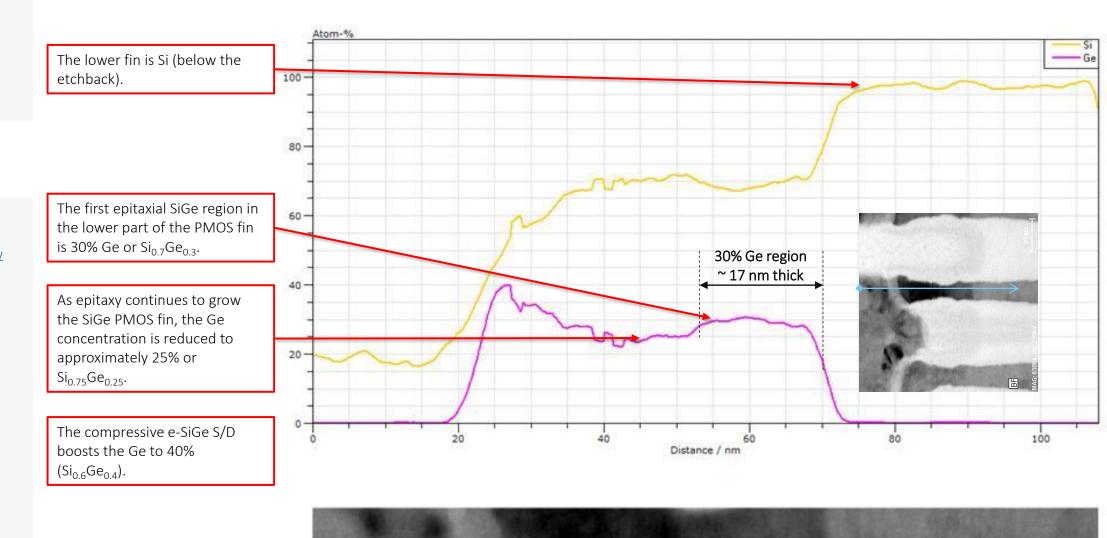

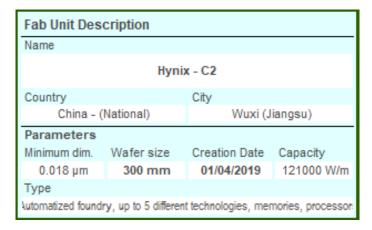

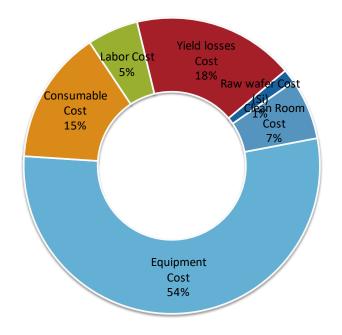

0.12 mm 0.44 mm 0.28 mm .18 mm 0.09 mm System Plus Consulting