## Design Techniques for High-Speed Low-Power Wireline Receivers

by

Arash Zargaran-Yazd

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### DOCTOR OF PHILOSOPHY

in

The Faculty of Graduate Studies

(Electrical and Computer Engineering)

#### THE UNIVERSITY OF BRITISH COLUMBIA

(Vancouver)

July 2013

© Arash Zargaran-Yazd 2013

## Abstract

High-speed data transmission through wireline links, either copper or optical based, has become the backbone for modern communication infrastructure. Since at multi-Gb/s data rates the transmitted signal is attenuated and distorted by the channel, sophisticated analog front-end and/or digital signal processing are required at the receiver (RX) to recover data and clock from the received signal.

In this thesis, both analog- and digital-based receivers are investigated, and power-reduction techniques are exploited at both system- and circuit-levels. A speculative successive-approximation register (speculative/SAR) digitization algorithm is proposed for use at the receiver front-end of digital receivers that combines equalization and data recovery with the digitization step at the front-end analog-to-digital converter (ADC). Furthermore, an architecture for quadrature clock generation is proposed which is of use in both analog and digital receivers. Then, an analog clock and data recovery (CDR) architecture suitable for high data rates (e.g., beyond 10 Gb/s) is proposed that utilizes a wideband data phase generation technique to facilitate mixer-based phase detection. The CDR architecture is implemented and experimentally validated for a 12.5 Gb/s system. Finally, a mixed-mode hardware-efficient CDR architecture is proposed that exploits both analog

#### Abstract

and digital design techniques to reach a robust operation suited for long-haul optical link communications. Proof-of-concept prototypes of the proposed RX architectures are designed and implemented in 65 nm and 90 nm CMOS processes. The prototypes are successfully tested. Note that although individual performance merits of the each prototype may not necessarily outperform that of the state-of-the-art, however, the prototypes confirm the feasibility of the proposed structure. Furthermore, the proposed architectures can be used at higher data rates particularly if more advanced technologies with higher device transit frequency,  $(f_T)$ , is used.

## **Preface**

I, Arash Zargaran-Yazd, am the principle contributor of all chapters. Professor Shahriar Mirabbasi who supervised the research has provided technical consultation and editing assistance on the manuscript. Hooman Rashtian and Kamyar Keikhosravy have respectively contributed to the design of VCO and comparator of the prototype chip presented in Chapter 6. As described below, some of the chapters in this thesis have been written based on the following published work.

#### Conference papers:

A. Zargaran-Yazd, S. Mirabbasi, and R. Saleh, "A 10 Gb/s low-power SerDes receiver based on a hybrid speculative/SAR digitization technique," in ISCAS, may 2011, pp. 446 –449  $\rightarrow$ Chapter 3

A. Zargaran-Yazd and S. Mirabbasi, "A 25 Gb/s full-rate CDR circuit based on quadrature phase generation in data path," in ISCAS, May 2012, pp. 317–320  $\rightarrow$ Chapters 4, and 5

#### Journal papers:

A. Zargaran-Yazd and S. Mirabbasi, "Low-power design technique for decision-feedback equalisation in serial links," *Electronics Letters*,

vol. 48, no. 17, pp. 1042–1044, 2012  $\rightarrow$ Chapter 2

A. Zargaran-Yazd, K. Keikhosravy, H. Rashtian, and S. Mirabbasi, "Hardware-efficient phase-detection technique for digital clock and data recovery," *Electronics Letters*, vol. 49, no. 1, pp. 20 -22, 3 2013  $\rightarrow$ Chapter 6

A. Zargaran-Yazd and S. Mirabbasi, "12.5-Gb/s full-rate CDR with wideband quadrature phase shifting in data path," Circuits and Systems II: Express Briefs, IEEE Transactions on, vol. 60, no. 6, pp. 297–301, 2013  $\rightarrow$ Chapter 5

| Αb                   | stra                           | <b>ct</b> ii                                |  |  |  |

|----------------------|--------------------------------|---------------------------------------------|--|--|--|

| Pro                  | eface                          | e iv                                        |  |  |  |

| Tal                  | ble o                          | of contents                                 |  |  |  |

| Lis                  | t of                           | tables                                      |  |  |  |

| Lis                  | t of                           | figures                                     |  |  |  |

| $\operatorname{Lis}$ | t of                           | acronyms                                    |  |  |  |

| Lis                  | List of symbol definitions xix |                                             |  |  |  |

| Ac                   | Acknowledgments                |                                             |  |  |  |

| Dedication           |                                |                                             |  |  |  |

| 1                    | Intr                           | oduction                                    |  |  |  |

|                      | 1.1                            | Motivation                                  |  |  |  |

|                      | 1.2                            | Serial-link data transmission and reception |  |  |  |

|                      | 1.3                            | Clocking schemes in serial links 6          |  |  |  |

|                      | 1.4                            | Power efficiency of wireline TX and RX 9    |  |  |  |

|   | 1.5 | Summary of objectives and contributions     | 11 |

|---|-----|---------------------------------------------|----|

|   | 1.6 | Organization of thesis                      | 12 |

| 2 | Low | y-power equalization                        | 14 |

|   | 2.1 | Channel as a low-pass filter                | 14 |

|   | 2.2 | Inter-symbol interference                   | 16 |

|   | 2.3 | Channel equalization                        | 20 |

|   |     | 2.3.1 Continues-time linear equalizer       | 21 |

|   |     | 2.3.2 FIR filter                            | 22 |

|   | 2.4 | Decision feedback equalization              | 24 |

|   |     | 2.4.1 Conventional analog DFEs              | 25 |

|   |     | 2.4.2 Loop-unrolled DFE                     | 28 |

|   | 2.5 | Proposed adaptive slicing technique         | 28 |

|   | 2.6 | Comparison of power-equalization efficiency | 31 |

|   | 2.7 | Chapter summary                             | 34 |

| 3 | Low | y-power DSP-based RX                        | 36 |

|   | 3.1 | Quantifying power efficiency in RX          | 37 |

|   | 3.2 | ADC performance requirements                | 39 |

|   | 3.3 | Speculative/SAR digitization algorithm      | 41 |

|   | 3.4 | Implementation of the proposed algorithm    | 45 |

|   |     | 3.4.1 Necessity of SAR cycles               | 51 |

|   | 3.5 | Power/resolution trade-off in ADC and DAC   | 53 |

|   | 3.6 | Measurement results and comparison          | 54 |

|   | 3.7 | Chapter summary                             | 58 |

| 4 | Qua | adrature clock generation in RX                                                    | 59  |

|---|-----|------------------------------------------------------------------------------------|-----|

|   | 4.1 | Ring oscillators                                                                   | 60  |

|   | 4.2 | LC oscillators                                                                     | 62  |

|   |     | 4.2.1 Differential LC oscillators                                                  | 62  |

|   |     | 4.2.2 Quadrature LC oscillators                                                    | 63  |

|   | 4.3 | Phase noise and power trade-off                                                    | 63  |

|   |     | 4.3.1 Phase noise in LC VCO                                                        | 65  |

|   |     | 4.3.2 Phase noise of ring oscillator                                               | 66  |

|   |     | 4.3.3 $\mathcal{L}(\Delta\omega)$ -power-area trade-off in ring and LC oscillators | 66  |

|   | 4.4 | Proposed quadrature clock generator                                                | 67  |

|   | 4.5 | Enhancing the power efficiency of QCG                                              | 70  |

|   | 4.6 | Jitter in QCG block                                                                | 79  |

|   |     | 4.6.1 Maximizing voltage swing                                                     | 79  |

|   |     | 4.6.2 Noise of actives and passives in inverter stage                              | 83  |

|   | 4.7 | Chapter summary                                                                    | 85  |

| 5 | Ana | alog CDR in high-speed links                                                       | 87  |

|   | 5.1 | Line codes in serial links                                                         | 87  |

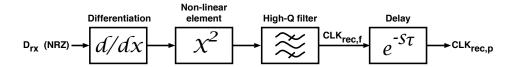

|   | 5.2 | Clock recovery using high-Q filter                                                 | 88  |

|   | 5.3 | Monolithic high-Q clock recovery                                                   | 90  |

|   | 5.4 | PLL-based clock recovery                                                           | 91  |

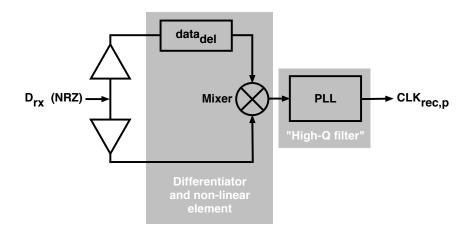

|   | 5.5 | Frequency doubling for mixer-based PD                                              | 94  |

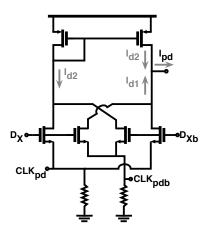

|   | 5.6 | Implementation of mixer-based PD                                                   | 95  |

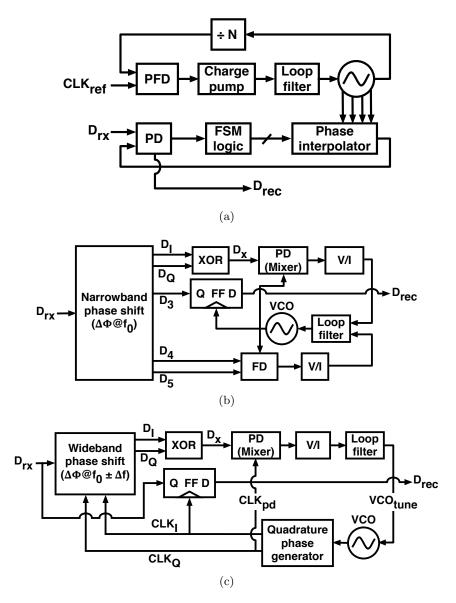

|   | 5.7 | The proposed CDR architecture                                                      | 97  |

|   | 5.8 | Design of system-level parameters                                                  | 100 |

|                  |                | 5.8.1 Loop filter                                      |

|------------------|----------------|--------------------------------------------------------|

|                  |                | 5.8.2 System-level performance                         |

|                  | 5.9            | Calibration phase interpolator                         |

|                  | 5.10           | Performance of QCG block                               |

|                  | 5.11           | Experimental results                                   |

|                  | 5.12           | Chapter summary                                        |

| 6                | Har            | lware-efficient eye monitoring technique for clock and |

|                  | data           | recovery                                               |

|                  | 6.1            | Digital clock recovery methods                         |

|                  | 6.2            | Proposed CDR technique                                 |

|                  | 6.3            | Measurement results                                    |

|                  | 6.4            | Chapter summary                                        |

| 7                | Con            | clusion                                                |

|                  | 7.1            | Research contributions                                 |

|                  | 7.2            | Performance comparison                                 |

|                  | 7.3            | Future work                                            |

| Bi               | bliog          | caphy                                                  |

| $\mathbf{A}_{]}$ | ppen           | dix                                                    |

| $\mathbf{A}$     | $\mathbf{Add}$ | itional circuit schematics                             |

|                  | A.1            | Comparator                                             |

|                  | Δ 2            | Digital to analog converter 150                        |

# List of tables

| 3.1 | Performance Summary and Comparison 57                             |

|-----|-------------------------------------------------------------------|

| 5.1 | Values of loop parameters                                         |

| 5.2 | Performance Summary and Comparison                                |

| 6.1 | PHASE DETECTION TRUTH TABLE FOR THE ARRANGEMENT SHOWN IN FIG.6.1B |

| 7.1 | SELECTION OF CDR ARCHITECTURE BASED ON CHANNEL                    |

|     | LOSS 134                                                          |

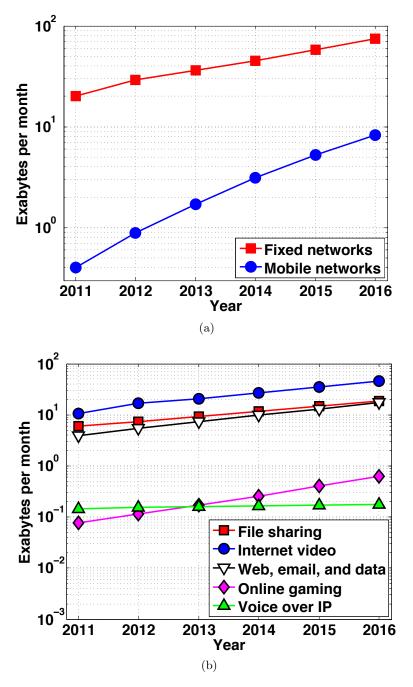

| 1.1 | Trend of global IP traffic based on type of network (a), and    |    |

|-----|-----------------------------------------------------------------|----|

|     | the traffic trend based on type of usage (b). Plotted based     |    |

|     | on data provided in [1]                                         | 2  |

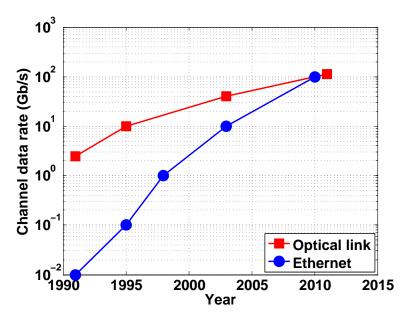

| 1.2 | Historical trend of channel data rates in optical link and Eth- |    |

|     | ernet standards                                                 | 4  |

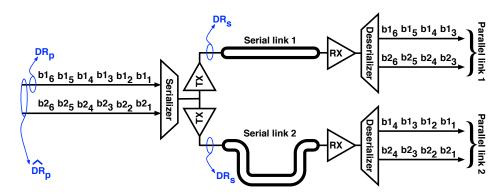

| 1.3 | Visual comparison of the zero skew allowance in parallel links  |    |

|     | versus arbitrary skew allowance in serial links                 | 5  |

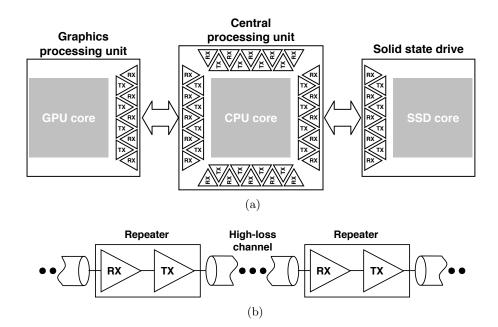

| 1.4 | Typical usage of TX-RX pairs in backplanes and mother-          |    |

|     | boards (a), and usage of TX-RX pairs as repeaters in long-      |    |

|     | haul optical communication (b)                                  | 6  |

| 1.5 | Classification of clocking schemes in serial links              | 7  |

| 1.6 | Illustration of various clocking schemes in serial links        | 8  |

| 1.7 | Trend in power efficiency FoM for TX and RX                     | 10 |

| 1.8 | Block diagram showing the outline and breakdown of the thesis.  | 13 |

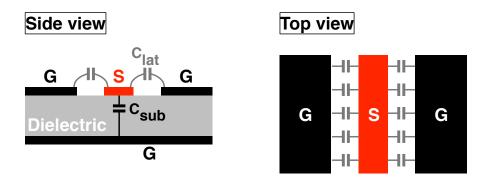

| 2.1 | Side and top views of a CPW PCB trace                           | 15 |

| 2.1 | Side and top views of a C1 w 1 CB trace                         | 10 |

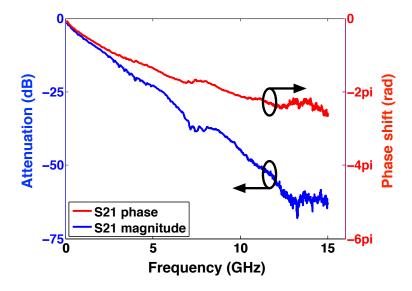

| 2.2 | Frequency response of a 10 inch CPW FR4 channel                 | 17 |

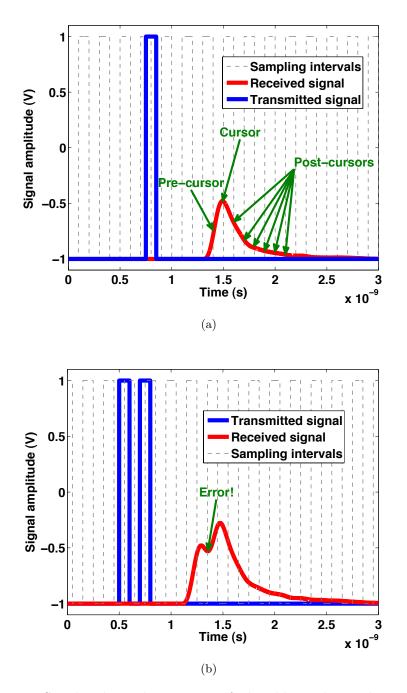

| 2.3 | Simulated impulse response of a band limited FR4 channel $$ .   | 18 |

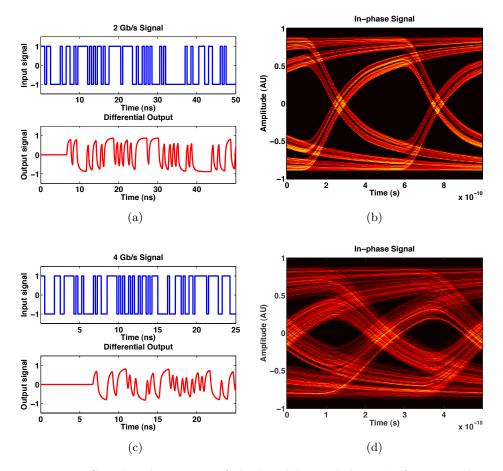

| 2.4 | Eye diagram of 2Gb/s, and 4Gb/s received data patterns          | 19 |

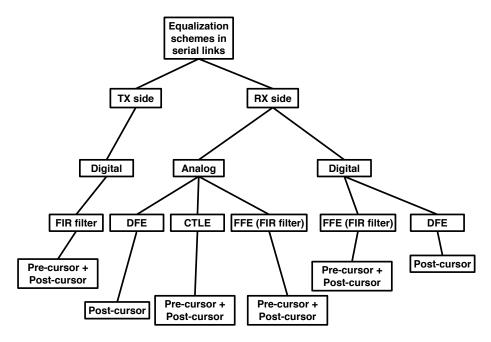

| 2.5  | Classification of equalizers used in high speed links                       | 20 |

|------|-----------------------------------------------------------------------------|----|

| 2.6  | Continues-time linear equalizer and its frequency response                  | 21 |

| 2.7  | Equalization using a finite impulse response filter at TX and               |    |

|      | RX                                                                          | 23 |

| 2.8  | A 3-tap ADFE (a), and a $(1+2)$ -tap LUDFE, i.e., the first                 |    |

|      | tap is unrolled (b)                                                         | 26 |

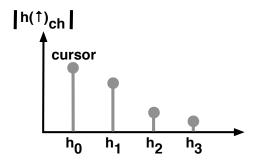

| 2.9  | Illustration of the impulse response of a $h_0 + h_1 z^{-1} + h_2 z^{-2} +$ |    |

|      | $h_3 z^{-3}$ channel                                                        | 27 |

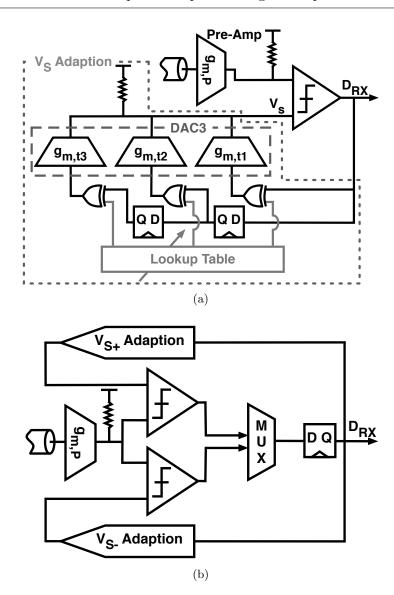

| 2.10 | ASDFE technique (a). The gray lines indicate low-speed sig-                 |    |

|      | nals. SASDFE architecture (b)                                               | 29 |

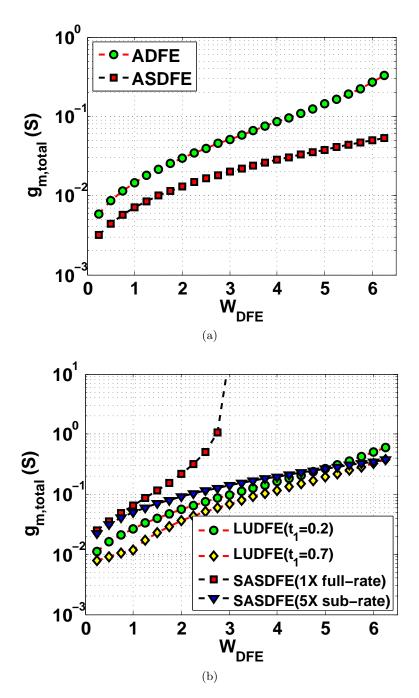

| 2.11 | Comparison of $g_{m,total}/W_{DFE}$ trade-off between ADFE and              |    |

|      | ASDFE (a), and between LUDFE and SASDFE (b)                                 | 32 |

| 2.12 | Graphical illustration of the block(s) addressed in Chapter 2.              | 34 |

| 3.1  | Simplified block diagram of an ADC-based RX                                 | 37 |

| 3.2  | Power consumption versus sampling frequency for ADC's pub-                  |    |

|      | lished in literature from 1997 to 2012                                      | 38 |

| 3.3  | Illustration of speculative and SAR digitization steps for two              |    |

|      | different data patterns                                                     | 41 |

| 3.4  | The hybrid speculative/SAR digitization algorithm implemented $$            |    |

|      | as a finite state machine                                                   | 42 |

| 3.5  | Block diagram of the proposed DSP-based RX                                  | 44 |

| 3.6  | Schematic of the divide-by-5 circuit                                        | 46 |

| 3.7  | Detailed block diagram of each channel in RX                                | 48 |

| 3.8  | Timing diagram of the five time-interleaved channels                        | 49 |

| 3.9  | Distribution of the recovered data of each channel, $b_{CHX}$ , to |    |

|------|--------------------------------------------------------------------|----|

|      | other channels                                                     | 51 |

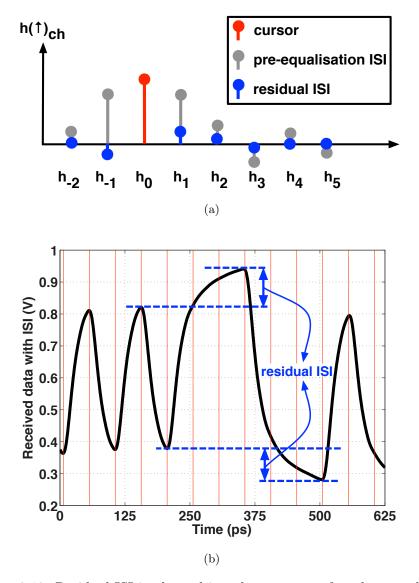

| 3.10 | Residual ISI in channel impulse response after the speculative     |    |

|      | digitization step (a), and the effect of residual ISI in changing  |    |

|      | data levels (b)                                                    | 52 |

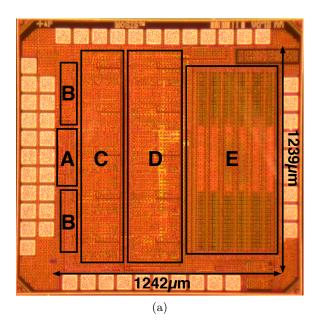

| 3.11 | The die micrograph of the prototype implemented in 65-nm           |    |

|      | CMOS (a), and the measured eye diagram of the recovered            |    |

|      | 10 Gb/s data (b)                                                   | 56 |

| 3.12 | Graphical illustration of the block(s) addressed in this Chap-     |    |

|      | ter 3                                                              | 58 |

| 4.1  | Schematic of a quadrature ring oscillator                          | 60 |

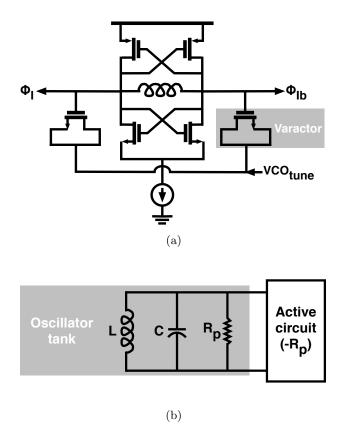

| 4.2  | Schematic of an LC VCO (a), and canceling the parasitic            |    |

|      | resistance of inductor, $R_p$ , in LC tank using an active element |    |

|      | (b)                                                                | 62 |

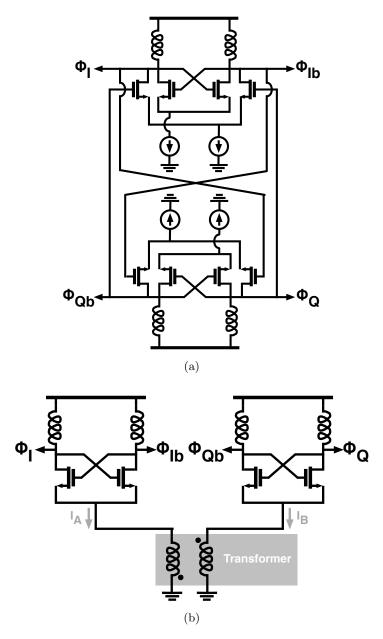

| 4.3  | Quadrature clock generation using two current-coupled LC           |    |

|      | oscillators (a), and another method of coupling using a trans-     |    |

|      | former (b)                                                         | 64 |

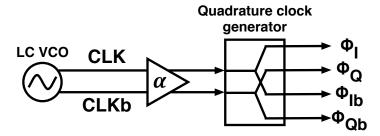

| 4.4  | Quadrature clock generation using coupling a differential VCO      |    |

|      | to the quadrature phase generation block                           | 67 |

| 4.5  | Unilateral coupling through current injection into the QPS         |    |

|      | ring                                                               | 68 |

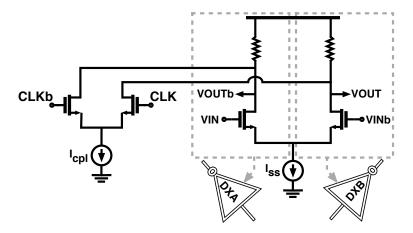

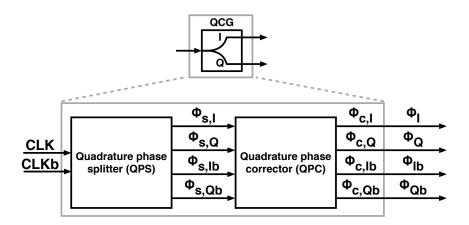

| 4.6  | Quadrature clock generator                                         | 69 |

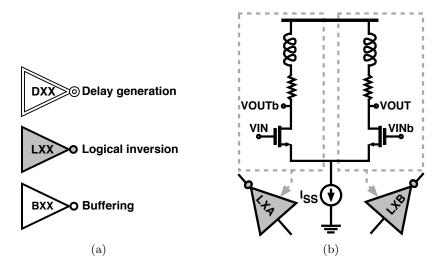

| 4 | .7  | (a) Legend indicating the type and function of inverters used         |    |

|---|-----|-----------------------------------------------------------------------|----|

|   |     | in QPS and QPC sub-blocks. (b) Format of CML half-inverters           |    |

|   |     | used in QPS and QPC                                                   | 70 |

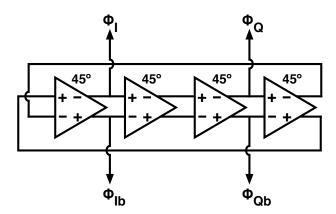

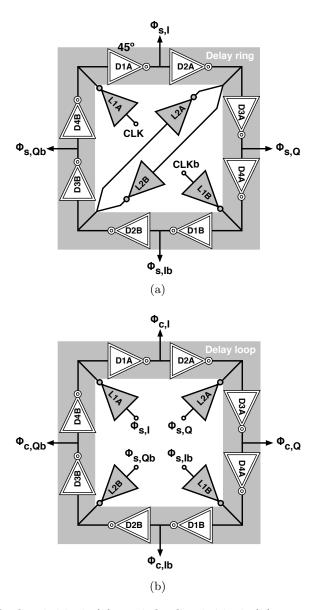

| 4 | .8  | QPS sub-block (a), and QPC sub-block (b) in $8\times45^\circ$ config- |    |

|   |     | uration                                                               | 71 |

| 4 | .9  | AC representation of the half CML inverter                            | 72 |

| 4 | .10 | Simplified model used for delay calculation                           | 72 |

| 4 | .11 | Speed versus power efficiency of an n-channel device in 90nm          |    |

|   |     | CMOS                                                                  | 74 |

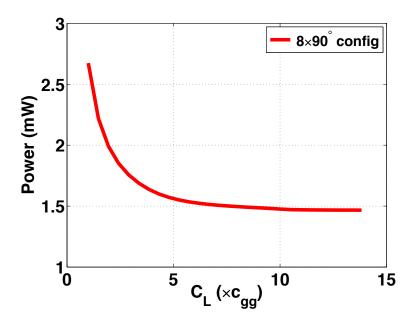

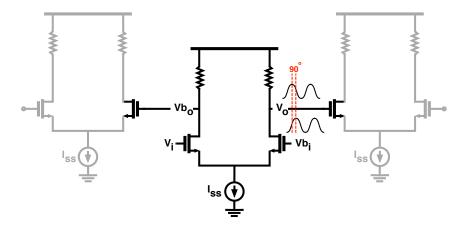

| 4 | .12 | QPS sub-block (a), and QPC sub-block (b) in $8\times90^\circ$ config- |    |

|   |     | uration                                                               | 76 |

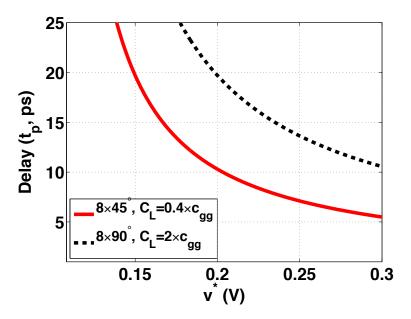

| 4 | .13 | Delay of inverter as a function of $v^*$                              | 77 |

| 4 | .14 | Power consumption of the inverter as a function of $v^*$              | 78 |

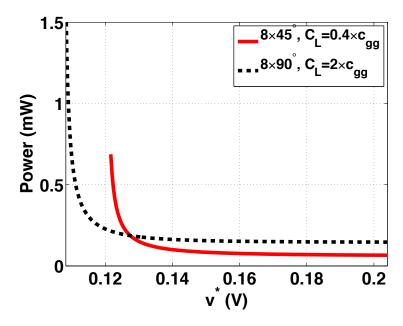

| 4 | .15 | Effect of using a discrete load capacitance, $C_L$ , on power con-    |    |

|   |     | sumption per inverter stage                                           | 78 |

| 4 | .16 | DC-coupled connection between the inverter stages                     | 80 |

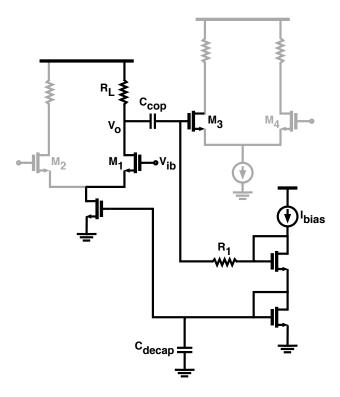

| 4 | .17 | AC-coupled connection between the inverter stages                     | 82 |

| 4 | .18 | Graphical illustration of the block(s) addressed in this Chap-        |    |

|   |     | ter 4                                                                 | 85 |

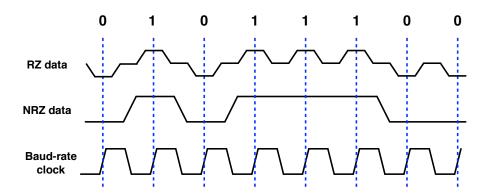

| 5 | .1  | Comparison of RZ data, NRZ data, and the baud rate clock.             | 88 |

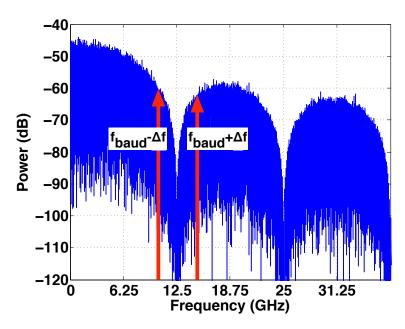

| 5 | .2  | The harmonics around $f_{baud}$ in the spectrum of NRZ data,          |    |

|   |     | which are used to extract the baud-rate clock                         | 89 |

| 5 | .3  | Block diagram showing the concept of high-Q filter based              |    |

|   |     | clock recovery                                                        | 90 |

| 5.4  | Block diagram of the monolithic high-Q CDR 91                          |

|------|------------------------------------------------------------------------|

| 5.5  | Phase-Interpolator-based CDR (a), conventional method of               |

|      | generating multiple data phases using delay elements, for              |

|      | mixer-based phase detection (b), wideband quadrature data              |

|      | phase generation in the proposed CDR (c) 92                            |

| 5.6  | Schematic of the mixer used as phase detector 96                       |

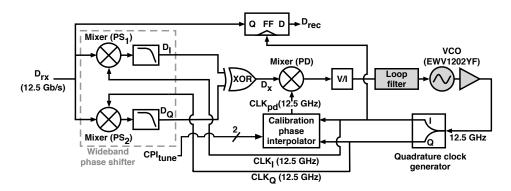

| 5.7  | Detailed block diagram of the proposed CDR 97                          |

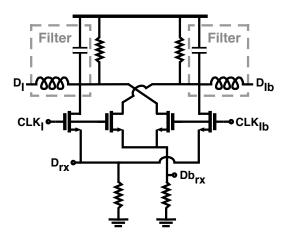

| 5.8  | Schematic of the phase shifting mixer                                  |

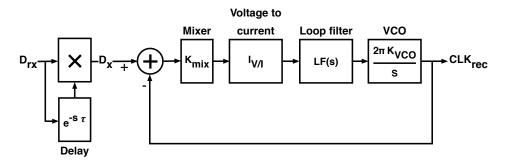

| 5.9  | Linearized model of the proposed CDR 100                               |

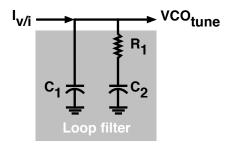

| 5.10 | Type II, order 2 loop filter, as used in the proposed CDR $102$        |

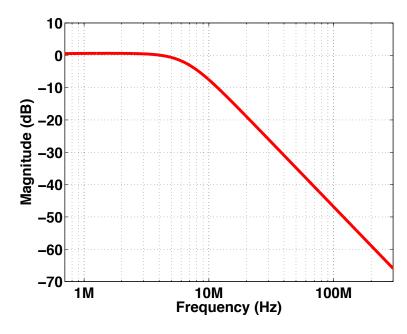

| 5.11 | Frequency response of the closed loop CDR                              |

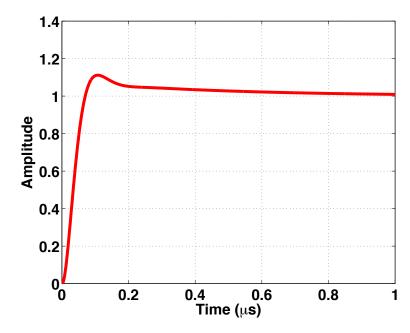

| 5.12 | Step response of the CDR                                               |

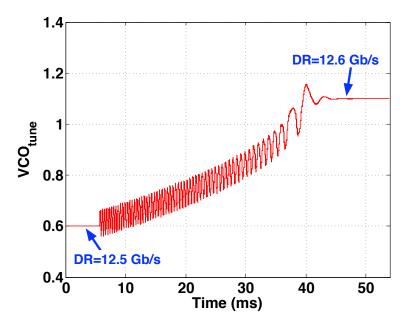

| 5.13 | Frequency locking behavior of the CDR when the DR is switched          |

|      | from 12.5 Gb/s to 12.6 Gb/s                                            |

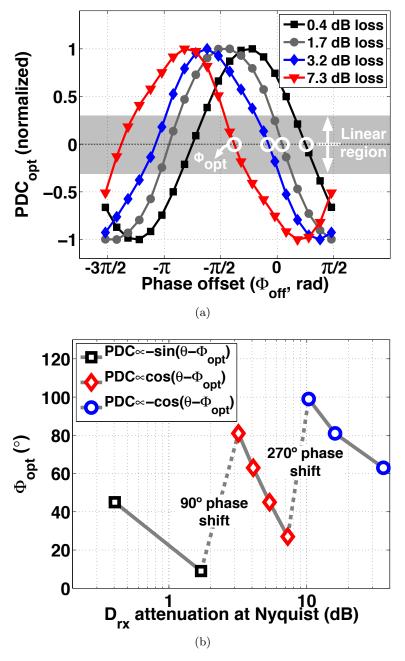

| 5.14 | Normalized $PDC_{opt}$ as a function of $\Phi_{off}$ (a). Variation in |

|      | $\Phi_{opt}$ due to various amounts of channel loss (b) 108            |

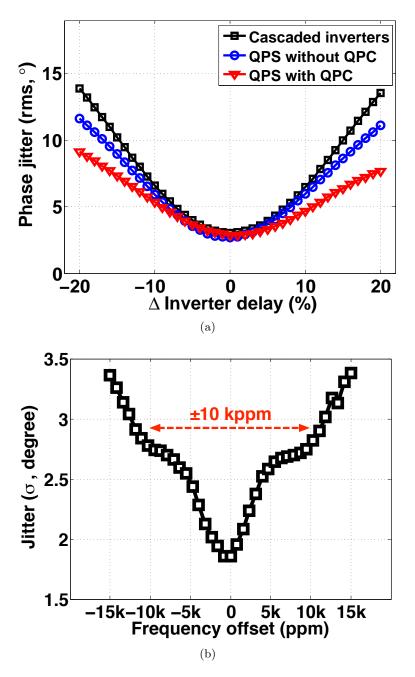

| 5.15 | Phase jitter in generated clock phases as a function of inverter       |

|      | delay variation (a). Jitter performance of QCG versus offset           |

|      | from $f_0$ (b)                                                         |

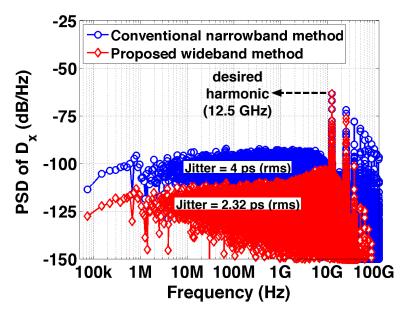

| 5.16 | Comparison of power spectral densities of $D_X$                        |

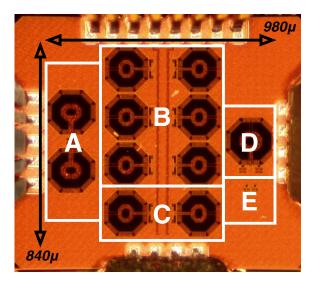

| 5.17 | Die micrograph of the prototype chip implemented in 90-nm              |

|      | CMOS                                                                   |

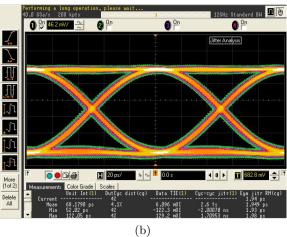

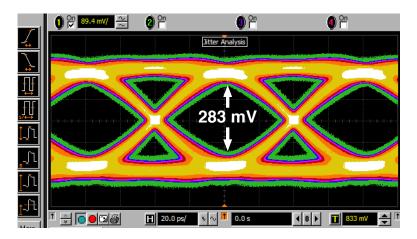

| 5.18 | Measured eye diagram of the recovered data 112                         |

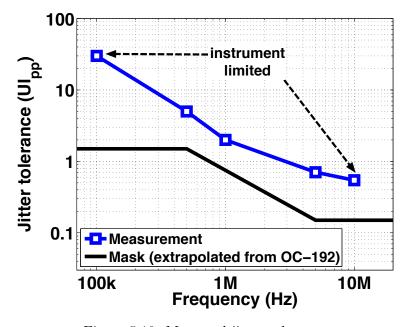

| 5 19 | Measured iitter tolerance                                              |

| 5.20 | Graphical illustration of the block(s) addressed in this Chap- |

|------|----------------------------------------------------------------|

|      | ter 5                                                          |

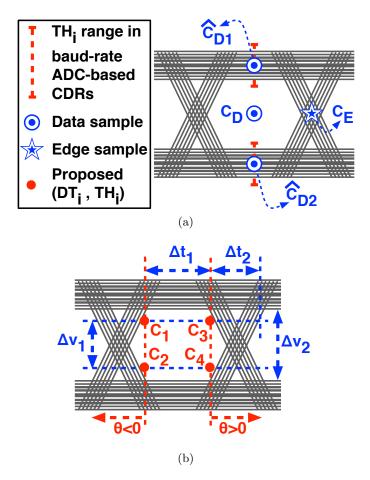

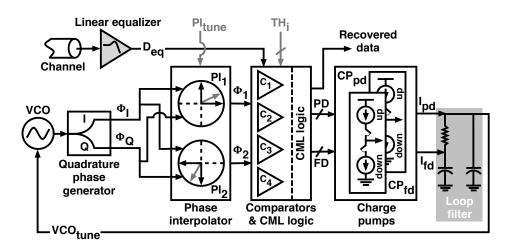

| 6.1  | The arrangement of $DT_i$ and $TH_i$ for comparators in binary |

|      | and ADC-based CDRs (a), and the arrangement in proposed        |

|      | CDR (b)                                                        |

| 6.2  | The proposed CDR architecture; shaded blocks and signals       |

|      | are off-chip                                                   |

| 6.3  | Phase detection characteristic (a), and frequency detection    |

|      | characteristic of the proposed CDR (b)                         |

| 6.4  | Schematic of phase interpolators                               |

| 6.5  | Die photo of the prototype chip implemented in 90-nm CMOS.127  |

| 6.6  | Graphical illustration of the block(s) addressed in this Chap- |

|      | ter 6                                                          |

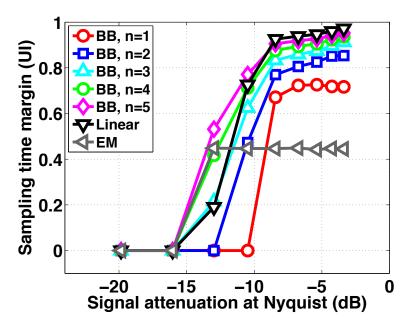

| 7.1  | Comparison of the performance of bang-bang CDR, Linear         |

|      | CDR, and eye monitoring CDR                                    |

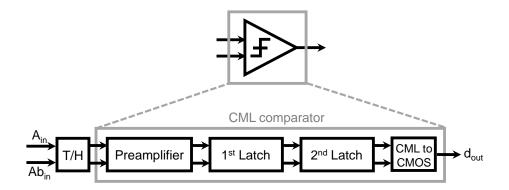

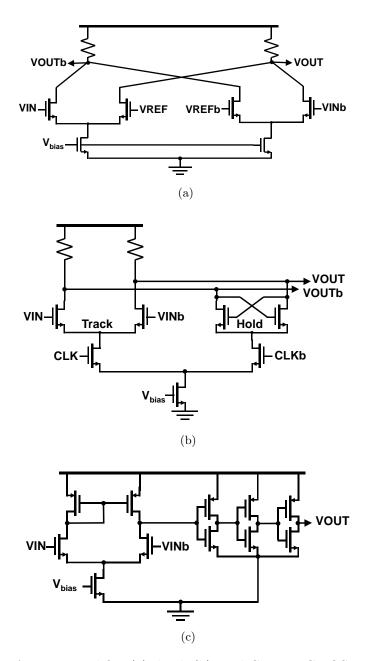

| A.1  | Block diagram of the CML comparator                            |

| A.2  | Preamplifier (a), latch (b), and CML-to-CMOS circuits 151      |

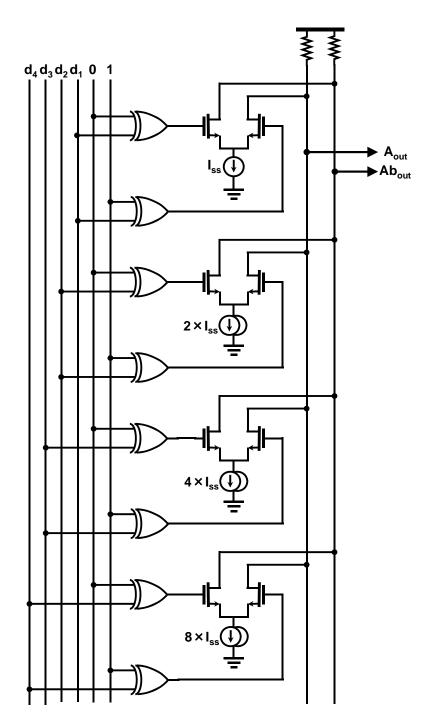

| A 3  | Schematic of a 4-bit current steering DAC 152                  |

# List of acronyms

ADC analog to digital converter

ADFE analog decision feedback equalizer

ASDFE adaptive slicer decision feedback equalizer

**BER** bit error rate

CDR clock and data recovery

$\mathbf{CPW}$  coplanar wave guide

CTLE continuous time linear equalizer

**DAC** digital to analog converter

**DFE** decision feedback equalizer

**DLL** delay locked loop

**DR** data rate

**DSP** digital signal processing

FD frequency detector

FFE feed forward equalizer

**FIR** finite impulse response

IC integrated circuit

**IP** internet protocol

**ISI** inter symbol interference

LUDFE loop unrolled decision feedback equalizer

MUX multiplexer

$\mathbf{NRZ}$  non return to zero

PCB printed circuit board

**PD** phase detector

**PDC** phase detector characteristic

**PI** phase interpolator

PLL phase locked loop

PSD power spectral density

QCG quadrature clock generator

**QPC** quadrature phase corrector

**QPS** quadrature phase splitter

RX receiver

SAR successive approximation register

SASDFE speculative adaptive slicer decision feedback equalizer

**SERDES** serializer deserializer

TRX transceiver

TX transmitter

**UI** unit interval

${f VCO}$  voltage controlled oscillator

XO crystal oscillator

## List of symbol definitions

A signal amplitude

$\mathbf{c_{dd}}$  total drain capacitance

$\mathbf{c_{gd}}$  gate drain capacitance

$\mathbf{c_{gg}}$  total gate capacitance

$\mathbf{c_{gs}}$  gate source capacitance

$\mathbf{c_{lat}}$  lateral capacitance

$\mathbf{c_{sub}}$  capacitance to substrate

$\mathbf{C_L}$  load capacitance

**CLKH** full-rate clock

CLKL sub-rate clock

$\mathbf{CLK_{rec}}$  recovered clock

$\mathbf{D_{eq}}$  equalized data

$\mathbf{D_{rec}}$  recovered data

$\mathbf{D_{rx}}$  received data

$\mathbf{D_x}$  XORed data

$\mathbf{f_0}$  nominal frequency

**f**<sub>bw</sub> 3-dB bandwidth frequency

$\mathbf{f_T}$  unity gain frequency of transistor

g<sub>m</sub> transistor transconductance

$I_{cpl}$  coupling current

$\mathbf{I_d}$  drain current

$\mathbf{I_{ss}}$  tail current

L inductance

**Q** quality factor

$\mathbf{r_o}$  output resistance of transistor

$\mathbf{R_T}$  termination resistance

$\mathbf{t_p}$  propagation time

$\mathbf{v_{cursor}}$  absolute cursor voltage

$\mathbf{v_{gs}}$  transistor gate source voltage

$V_o$  output voltage

$\mathbf{v_{od}}$  transistor overdrive voltage

$\mathbf{v_{sw}}$  peak voltage swing

$\mathbf{v_{th}}$  transistor threshold voltage

$\lambda$  channel length modulation factor

$\theta$  phase error

$\phi_{\mathbf{I}}$  in-phase signal component

$\phi_{\mathbf{Ib}}$  in-phase inverted signal component

$\phi_{\mathbf{q}}$  quadrature-phase signal component

$\phi_{\mathbf{q}\mathbf{b}}$  quadrature-phase inverted signal component

$\mathcal{L}$  phase noise

$\omega$  angular frequency

$\omega_{\mathbf{n}}$  natural angular frequency

$\tau$  time constant

## Acknowledgments

First and foremost, I want to thank my academic advisor, Professor Shahriar Mirabbasi, for being my mentor and friend, and for the numerous hours that he spent guiding me to become a better researcher. I was always amazed by his intelligence and ability to quickly apprehend the design idea that I had come up with, point out its shortcomings, and suggest neat modifications. Without his help, advice, and kindness, reaching this stage would have been impossible for me.

I am thankful to professors Alen Hu, Marek Syrzycki, Peyman Servati, and Steve Wilton for serving on my Ph.D. examination committee, and providing me with valuable comments to my research and thesis.

I want to thank my lab mates, Mohammad Beikahmadi, Kamyar Keikhosravy, Hooman Rashtian, Ahmadreza Farsaei, Pouya Kamalinejad, Nima Taherinejad, and Parisa Behnamfar for all the technical discussions, and the fun moments which I had with them.

My heart is full of gratitude for my mother, farther, and sister who gave me hope and encouragement throughout my adventurous journey towards the Ph.D. degree. They passionately shared all the pains, excitements, frustrations, and eventually the ultimate fruit with me. I am truly indebted to them. My sister, she kept calling me "Doctor" for the past several years, which stressed me out every single time I heard that word! as I knew there was a difficult path in front of me. However, it also reminded me how they had bet all their hopes over my success, which in turn made me more determined.

Finally, I am thankful to Nazafarin, for her love and support. She patiently tolerated the not-so-fun Ph.D. candidate Arash, when I had to stay in the lab all night to test a chip, or spend the whole weekend to write a paper. I am so grateful to her.

# Dedication

To my parents

## Chapter 1

## Introduction

#### 1.1 Motivation

Fueled in part by the growing trend of cloud-based computation and storage, and high-speed wireless data access, the global demand for communication bandwidth has continued to unprecedentedly increase. It is expected that by 2016, the global annual data traffic will reach 1.3 zettabytes per year  $(10^{21} \text{ bytes per year})$  or 110.3 exabytes per month  $(10^{18} \text{ bytes per month})$ . Such data traffic would be equivalent to transferring all movies ever made in history every 3 minutes [1]. Figure 1.1a shows the speculated trend in global internet protocol (IP) traffic growth for fixed and mobile networks. Figure 1.1b categorizes the total IP traffic based on the type of usage. It can be observed that the data traffic is expected to increase by roughly two orders of magnitude by 2016, over a decade period. Figure 1.2 shows the historical trend of data rates in both optical links and Ethernet standards. Note that the data rates in these standards are mostly set based on the trend of the bandwidth demand as illustrated in Fig. 1.1a, rather than by the speed limits of the available monolithic integrated circuit (IC) technologies. According to Fig. 1.2, to address the trend in global bandwidth demand, the most recent standards call for data rates up to 100 Gb/s in the

Figure 1.1: Trend of global IP traffic based on type of network (a), and the traffic trend based on type of usage (b). Plotted based on data provided in [1].

backbone wireline channels. While the higher cost of optical modules and challenges in integration with a monolithic transmitter (TX) and receiver (RX) increases the overall cost of optical data transmission as compared to electrical transmission, optical mediums have been historically preferred in high-speed standards. This is primarily due to the lower high-frequency loss of an optical medium compared to a metal-based medium (e.g., copper cables). However, as illustrated in Fig. 1.2, the data-rate gap between optical and electrical (Ethernet) links has been continuously reduced in the recent years. One major motivation for such trend is the vital role that the cost factor plays in commercial applications. However, technically this can be explained by the advancements in the wireline transmitter and receiver designs which enable high-speed data transmission over lossy and low-cost electrical channels. Among the TX and RX, the design of a wireline RX can be more challenging due to the distortion of data in the channel. Addressing some of the most important trade-offs and challenges specific to the RX is the goal of this research.

### 1.2 Serial-link data transmission and reception

The infrastructure of modern wireless and wireline communication systems is composed of multiple backplanes, each of which having several chips on them. The connection between different boards and chips is realized through a series of package I/Os, as well as vias, stubs, connectors and copper traces drawn on printed circuit boards (PCBs). The ever increasing Ethernet traffic and prevalence of multicore CPU architectures calls for a substantial increase

Figure 1.2: Historical trend of channel data rates in optical link and Ethernet standards.

in the speed of board-to-board and chip-to-chip data transfer. Although the data is usually transmitted in parallel format within ICs, serial links have become the optimum design choice for connection between chips and boards at multi-Gb/s data rates. The stringent requirements of allowable skew between different channels of parallel data bus and the small tolerable clock jitter limit the application of parallel data transmission to lower speed links.

There are two aspects of a serial link that differentiate it from a parallel link (also known as a "bus"). First, as annotated in Fig. 1.3, a serial link is a single transmission channel with a line data rate,  $DR_s$ , that is multiple of the individual line data rate  $DR_p$  in a parallel link, and can be written as

$$DR_s = \widehat{DR_p} = n_p \times DR_p \tag{1.1}$$

Figure 1.3: Visual comparison of the zero skew allowance in parallel links versus arbitrary skew allowance in serial links.

where  $\widehat{DR_p}$  and  $n_p$  are the total data rate of a parallel link, and the number of transmission channels (lines) in the parallel link, respectively. The conversion from multiple channels to a single channel running at a faster data rate is performed using a serializer. The data on a serial link can be converted to a parallel format through a describing.

Second, a group of data lines in a parallel link are logically differentiated from a group of serial links through the difference in skew tolerance among the channels in each of the groups. As shown in Fig. 1.3, by definition, there is typically a very small (i.e., a fraction of unit interval) tolerance for skew among the channels in the former group. However, in serial links, there can be an arbitrary skew among the channels. The freedom in skew, and a smaller physical footprint of a serial link as compared to a parallel link have proved advantageous in high-speed data transmission from both cost and design standpoints.

Figures 1.4a and 1.4b show two common forms of serial data transmission. In Fig. 1.4a, the transmitter and receiver pairs are typically located in the

Figure 1.4: Typical usage of TX-RX pairs in backplanes and motherboards (a), and usage of TX-RX pairs as repeaters in long-haul optical communication (b).

boundaries of chips which need to talk to other chips located on the motherboards and backplanes. Figure 1.4b shows another form of usage in which each TX-RX pair form a repeater chip. Such repeaters are placed in certain locations along a high loss channel, as in long-haul links. An example of such use of TX-RX pairs is in submarine communication cables.

### 1.3 Clocking schemes in serial links

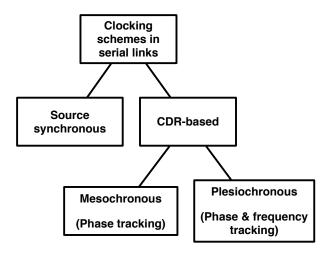

While data transmission and reception in serial links can be categorized based on many aspects, characterization based on the clocking scheme is especially useful for system-level design. Figure 1.5 classifies the clocking

Figure 1.5: Classification of clocking schemes in serial links.

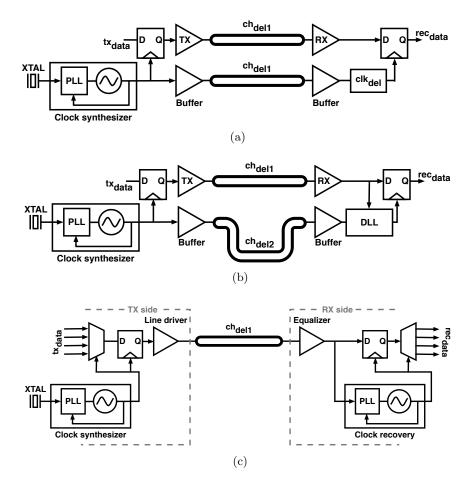

schemes in serial links. In the source synchronous scheme (Fig. 1.6a), the clock is forwarded along with data from TX to RX. The clock path and data paths are designed to have equal propagation delays. This insures that the relative phase offset between data and clock remains constant as they travel through the matched channels. An active or passive delay element producing the delay value  $clk_{del}$  is used at RX to align the sampling edge of the clock to the middle of the data eye. There are two drawbacks associated with this clocking scheme: First, it is challenging to maintain a constant  $clk_{del}$  among process, voltage, and temperature (PVT) corners. Second, it might be challenging or unfeasible to maintain the delay match between the data and clock channels due to the area constrains imposed by other blocks and transceivers. Also, the channel incurs different propagation delays for the data which has broadband frequency characteristic, and the relatively narrowband clock.

Figure 1.6: Source synchronous (a), Mesochronous (b), and Plesiochronous (c) clocking schemes in serial links.

A clock and data recovery (CDR) based clocking schemes can be either Mesochronous, or Plesiochronous. In the Mesochronous scheme (Fig. 1.6b), clock is still forwarded to RX; however, there is no matching constraint for the delay of data channel,  $ch_{del1}$ , relative to the delay of the clock channel,  $ch_{del2}$ . Therefore, while the clock frequency at RX and TX match, RX needs a mechanism to recover the correct phase of the sampling clock based on the received data. Such task is usually performed through a delay-locked loop

(DLL).

In the Plesiochronous scheme (Fig. 1.6c), only data is sent to RX. Hence, both TX and RX have their own local clocks. The TX and RX clocks are both synthesized locally using a phase-locked loop (PLL). However, TX PLL utilizes a local crystal oscillator (XO) as the reference, while RX uses the received data as the reference for the clock synthesis PLL. This allows for arbitrary, yet limited, phase and frequency offset between RX and TX clocks. Therefore, a Plesiochronous TX-RX pair is more flexible to be used in applications that do not allow for a separate clock route, or wherever a perfect match between  $ch_{del1}$  and  $ch_{del2}$  is not possible. While such clocking scheme doesn't have the disadvantages mentioned for the source synchronous method, it comes at the price of complexity and area/power overhead that CDR imposes on RX. Designing power efficient CDRs at multi Gb/s speeds is an active area of research.

### 1.4 Power efficiency of wireline TX and RX

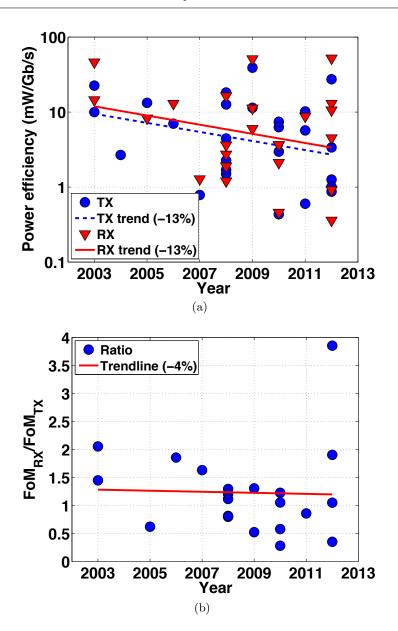

To motivate this work and investigate techniques for enhancing the overall power efficiency of a serial link, it is helpful to compare the power consumption of TX versus that of RX. A commonly used figure-of-merit (FoM) for wireline systems is the power efficiency of the link<sup>1</sup> which is measured in mW/(Gb/s) and provides a mean to compare the efficiency of TX, RX, or the overall transceiver (TRX). The associated FoMs are denoted as  $FoM_{TX}$ ,  $FoM_{RX}$ , or  $FoM_{TRX}$ , respectively. Figure 1.7a compares the power effi-

<sup>&</sup>lt;sup>1</sup>Or similarly, power efficiency of a stand-alone TX or RX.

Figure 1.7: Trend in power efficiency FoM for TX  $(FoM_{TX})$  and RX  $(FoM_{RX})$  (a), and the trend of  $\frac{FoM_{RX}}{FoM_{TX}}$  (b). For more information regarding the data plotted in Figs. 1.7a and 1.7b please refer to [2–24], and [2–17], respectively. Note that some of the references either report more than one TX-RX, or report power consumptions for several data rates.

ciency of TX and RX architectures which have been published in the past decade. The trendline of both  $FoM_{TX}$  and  $FoM_{RX}$  demonstrate a reduction of -13% per year. Also, the average power consumption for the RX block is approximately 15% more than that of the TX block. Note that Fig. 1.7a illustrates results from literature that report either individual TX or RX, or a TRX. Figure 1.7b shows the ratio  $\frac{FoM_{RX}}{FoM_{TX}}$  for the published work that present a TRX where the power for RX and TX blocks are individually reported. As the trendline in this figure demonstrates, power consumption of RXs are on average 25% more than that of the TX. This trend is almost flat over time which indicates that the RX is typically expected to consume a larger portion of the overall link power budget. Additionally, given that a large portion of TX power consumption is due to the requirement of driving a 25  $\Omega$  impedance (50  $\Omega$  channel || 50  $\Omega$  termination) with a certain voltage swing dictated by the standard, the power budget of the TX is more constrained. Therefore, in this research we focus on the RX.

### 1.5 Summary of objectives and contributions

The main research objectives of this work are as follows:

• Designing a digitization algorithm to address the specific requirements of low-power multi-Gb/s wireline RX. Currently, the major obstacle in designing digital high-speed serial link receivers is the power consumption of the front-end baud-rate ADC. The power consumption and area of a generic full-flash ADC makes its integration into the receiver a challenging task. To address this issue, we have developed

a speculative/SAR ADC which can operate at speeds comparable to a full-flash ADC, while consuming less power.

- Designing and analyzing the performance and power consumption of an injection-locked quadrature clock generator. Such block is an integral part of CDRs that require a quadrature-phase clock in a addition to the in-phase clock component. Optimizing the power dissipation of this block is discussed from both circuit-level and system-level perspectives.

- Proposing and developing an analog receiver architecture that utilizes

a mixer-based phase detection mechanism to achieve relatively low

power consumption at data rates beyond 10 Gb/s. The CDR comprises

the proposed quadrature clock generator.

- Design of a hardware-efficient mixed-mode eye monitoring technique for clock and data recovery. The design addresses the power consumption issue from system-level.

### 1.6 Organization of thesis

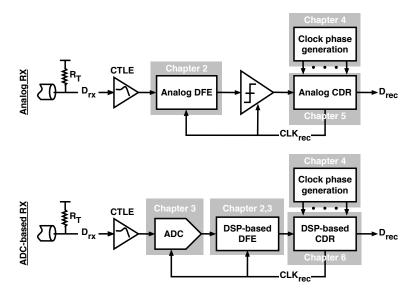

Figure 1.8 demonstrates the receiver blocks that are addressed in chapters of this thesis. Below is the description and breakdown:

Chapter 2 focuses on equalization in both analog and digital RX.

Chapter 3 discusses a digitization algorithm for ADC-based RX.

Figure 1.8: Block diagram showing the outline and breakdown of the thesis.

<u>Chapter 4</u> presents an architecture for quadrature clock generation, and the associated power consumption optimization.

<u>Chapter 5</u> presents an analog architecture for clock and data recovery, employing the proposed clock generation technique.

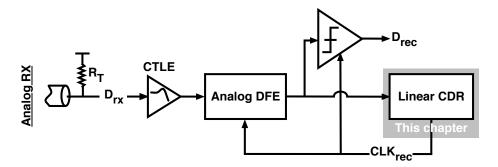

<u>Chapter 6</u> presents a mixed-mode CDR architecture that partitions the RX blocks into analog and digital domains.

Chapter 7 concludes this thesis and discusses the potential future work.

## Chapter 2

# Low-power equalization

The continues scaling of integrated circuits has increased the speed of the on-chip signal processing. However, the data transmission channels (i.e. copper wires in printed circuit boards) have roughly stayed the same. Long gone are the days where the transmission channels were considered ideal over the bandwidth of signal. In this chapter, first the mechanism of data distortion due to a lossy channel is described. Then, various methods of data equalization are introduced. Finally, this Chapter focuses on addressing the power consumption aspect of decision feedback equalization in high-speed serial links.

### 2.1 Channel as a low-pass filter

Due to dielectric loss, skin effects, and parasitic crosstalk with adjacent channels, the signal observes the channel as a low pass filter, which attenuates the high-frequency components of the transmitted signal, and also adds deterministic and random noises to it.

Figure 2.1 shows the top and side views of a simple one layer printed circuit board (PCB). The bottom layer is a grounded conductor (typically copper) to serve as a global ground, and provide noise isolation. Each layer

Figure 2.1: Side and top views of a CPW PCB trace.

of conductor is isolated from the next conductor layer through a dielectric. As Fig. 2.1 illustrates, the signal trace (S) is shielded from both sides using ground (G) traces. Such structure forms a coplanar wave guide (CPW) channel and is useful to reduce crosstalk among different signal traces. However, such isolation comes at the price of lateral parasitic capacitance,  $c_{lat}$ , on the signal line, which degrades the frequency response of the channel. Also, the parasitic capacitance to the grounded substrate,  $c_{sub}$ , results in additional signal loss. For the value of  $C_{sub}$  per unit area,  $c_{sub}$  we can write

$$c_{sub} \propto \frac{\epsilon}{d}$$

(2.1)

where  $\epsilon$  and d are the dielectric constant and thickness of dielectric, respectively. Therefore, based on 2.1, to reduce  $c_{sub}$ , we should either decrease  $\epsilon$  or increase d. Increasing d is not optimal as results in a thicker PCB, and decreasing  $\epsilon$  requires materials that considerably increase the cost of PCB.

#### 2.2 Inter-symbol interference

The Nyquist criterion states that if the relation given by

$$T \ge \frac{1}{2 \times W} \tag{2.2}$$

holds, a Nyquist pulse<sup>2</sup> can be transmitted through the channel without being distorted. Here, T is symbol (bit) duration and W is the channel bandwidth. However, while serial link data rates have considerably increased in the last decade (Fig. 1.2), the bandwidths of the links have not increased at the same rate and typically we have  $T \ll 1/(2W)$ . As the symbol duration is reduced below the limit defined by the Nyquist criterion, distortion-free data transmission becomes impossible. To explain the mechanism of data distortion, we briefly discuss the frequency response of channel.

Figure 2.2 shows the frequency and phase responses of a 10" CPW FR4 channel. The magnitude response of channel resembles that of a low-pass filter. As a result, the sharp edges in the transmitted waveform would be observed as rounded curves at the receive side [25].

The phase response indicates that depending on frequency, the various harmonics of broadband received data experience unequal propagation delays through the channel. This separates the frequency components of the data in time domain; hence, partially merging a bit to its pre-cursor and post-cursor bits. This issue, being described as Inter-symbol interference (ISI), degrades the quality of the data at the receive side of the channel. Higher data rates (i.e. shorter T), or lower channel bandwidth aggravate this prob-

<sup>&</sup>lt;sup>2</sup>As an example, a pulse that has a raised-cosine spectra.

Figure 2.2: Frequency response of a 10 inch CPW FR4 channel.

lem.

The channel's impulse response provides and intuitive perspective of how data gets distorted by the low-frequency characteristic of channel. To generate such impulse response, we can transmit an isolated '1' which is preceded and succeeded by a group of '0's and observe the output of channel. Figure 2.3a illustrates this concept. If we sample the impulse response of channel at each bit interval, the sample with largest amplitude is called *cursor*, and the samples with non-zero values before and after the cursor are called *precursor* and *post-cursor*, respectively [26]. Figure 2.3b shows how ISI shifts the amplitude of the cursor below the decision threshold, and thus bit error results.

The time-domain responses of the channel in Fig. 2.2 to 2Gb/s, and 4Gb/s NRZ data are shown in Fig.2.4. As shown in Fig.2.4b, and Fig.2.4d, the

Figure 2.3: Simulated impulse response of a band limited FR4 channel using a 0.1ns wide pulse (a), and distortion of the received signal beyond the detectable limits due to ISI (b)

Figure 2.4: Simulated response of the band-limited channel of Fig.2.2 along with the corresponding eye diagrams using  $2\mathrm{Gb/s}$  (a-b), and  $4\mathrm{Gb/s}$  (c-d) random data patterns.

channel non-idealities result in small vertical eye opening at the receiver side and this problem gets aggravated as data rate increases. This makes the data recovery task more complicated and increases the bit error rate (BER) of the receiver. Low-pass property of channel does not allow the channel's output to properly follow the abrupt changes of transmitted signal waveform. For a lossy channel without reflections, the smallest vertical

eye opening typically occurs when an isolated '0' or an isolated '1' is transmitted (i.e., ...00001000... or ...11110111...). Such cases determine the worst case voltage margin at RX sampler(s), which affects the bit error rate of the link. If the ISI is large enough, it can completely close the data eye and make the detection of the transmitted symbols without equalization impossible. As a result, Different types of equalization are used at both TX and RX to partially cancel ISI.

Figure 2.5: Classification of equalizers used in high speed links.

#### 2.3 Channel equalization

As signal distortion due to ISI is inevitable in high speed links, the data should be equalized either at TX, RX, or both TX and RX sides. This provides the subsequent blocks (e.g., clock recovery and data recovery) with an apprehensible signal. Figure 2.5, classifies the equalizers based on domain (analog versus digital), and side (TX versus RX) of implementation.

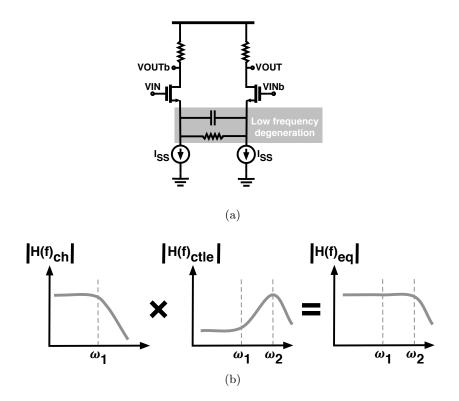

Figure 2.6: Schematic of typical implementation of continues-time linear equalizer (CTLE) (a), and compensation for low-pass characteristic of channel through low-frequency source degeneration (b).

#### 2.3.1 Continues-time linear equalizer

Figure 2.6a shows the schematic of a continuous-time linear equalizer (CTLE) which is commonly used at the front-end of RX to emphasize the high frequency components in the received data,  $D_{rx}$ , or equivalently de-emphasize the low frequency components in  $D_{rx}$ . In the CTLE of Fig. 2.6a which

utilizes resistive loads, low-frequency components in  $D_{rx}$  are attenuated through reducing the DC gain of the differential stage using source degeneration. Considering the simple channel in Fig. 2.6b with low pass frequency response and 3-dB bandwidth of  $\omega_1$ , the zero in the CTLE frequency response,  $|H(f)_{ctle}|$ , should be ideally located at  $\omega_1$  to flatten the overall equalized frequency response,  $|H(f)_{eq}|$ . Note that as  $|H(f)_{ctle}|$  can not sustain an increasing gain till infinite frequency, inevitably the magnitude response will fall at  $\omega_2$ , where  $|H(f)_{ctle}|$  has two poles. To provide a satisfactory equalization at a reasonable power consumption,  $\omega_2$  should be set such that

$$\frac{1}{2} \times DR < \omega_2 < \frac{2}{3} \times DR \tag{2.3}$$

where DR is the data rate in Gb/s [24].

#### 2.3.2 FIR filter

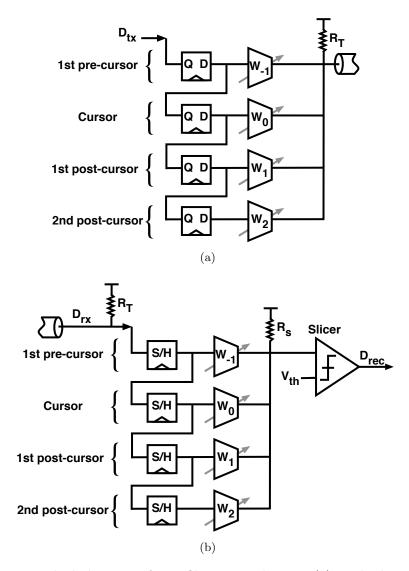

Figure 2.7a shows the block diagram of a finite impulse response (FIR) filter as used in TX to pre-emphasis the high frequency contents of transmitted data,  $D_{tx}$ . Flip flops (FFs) are used to delay the signal for one clock cycle or equivalently 1 unit interval (UI). Based on channel impulse response, a weight,  $W_i$  is applied to the digital data through an operational transconductance amplifier (OTA) stage. The overall combination of the FF and OTA form a filter tap. The taps which precede and succeed the main tap are called anti-causal taps and causal taps, respectively. Anti-causal taps (i.e.  $W_{-1}$ ) are used to cancel pre-cursor components in channel impulse re-

Figure 2.7: Block diagram of FIR filter as used in TX (a), and schematic of FIR filter as used in RX (b).

sponse; likewise, causal taps are used to cancel the post-cursor components. Although such filters are simple and inherently fast, their major drawback is degradation of signal-to-noise ratio (SNR) at the TX node due to the

limited swing of output stage. In other words, as in CTLE, high frequency components are emphasized at the price of de-emphasizing low-frequency components, which translates to a lower SNR.

Figure 2.7b shows the potential implementation of an FIR filter in analog domain at RX. Although feasible, FIR filters are rarely implemented in analog domain. One significant challenge in such implementation is noise enhancement in the sample and hold (S/H) chain. However, in DSP-based RX, where equalization is performed on the digitized data, FIR filters are commonly used before a decision feedback equalizer (DFE) to cancel pre-cursor taps of channel. Such FIR filters are commonly referred to as a feed-forward equalizer (FFE) [27].

#### 2.4 Decision feedback equalization

Decision feedback equalizers (DFEs) use the knowledge of previously recovered bits to estimate their effect on the current bit, and subtract the estimated distortion value from the received signal. DFE is a key component of high speed<sup>3</sup> wireline receivers, and plays a vital role in the emerging 40 to 100 Gb/s links [28]. In channels with a long impulse response tail, canceling the post-cursor inter-symbol interference using a DFE is a preferred choice over a feed-forward equalizer. Such design choice is based on the fact that unlike FFEs, DFEs do not enhance the noise, or deliberately attenuate high-frequency components of the received signal [29]. However, DFEs suffer from stringent requirement for timing closure in the feedback loop within 1

<sup>&</sup>lt;sup>3</sup>In this manuscript we refer to data rates > 10 Gb/s as "high speed".

unit interval. Depending on the speed and the amount of necessary postcursor ISI cancellation, the power consumption of the DFE block may not fit within the receiver's power budget [30]. Furthermore, given a certain technology, the implementation of DFE may not be feasible due to capacitive self-loading of devices. In this chapter, we propose a DFE implementation technique which relaxes the trade-off between the power consumption, the speed, and the amount of post-cursor ISI needed to be canceled.

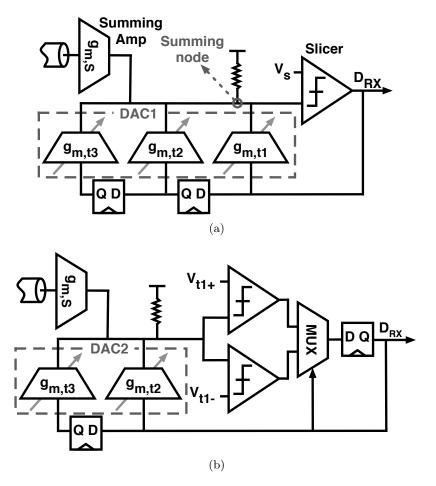

#### 2.4.1 Conventional analog DFEs

To make a decision, conventional analog DFEs (ADFEs) utilize a static slicing threshold equal to the voltage at the mid-point of the equalized data eye. Figure 2.8a shows a 3-tap ADFE where using DAC1, the ISI is subtracted from the distorted received signal at the summing node. The result is compared with the static slicing threshold voltage  $V_s$  to recover the data. Lets consider the channel of Fig. 2.9, whose transfer function is

$$H_{ch}(z) = h_0 + h_1 z^{-1} + h_2 z^{-2} + h_3 z^{-3}$$

(2.4)

In addition to the cursor  $h_0$ , the channel impulse response has three postcursor components, i.e.,  $h_1$  to  $h_3$ . Thus, the total amount of post-cursor ISI with respect to cursor can be written as

$$W_{DFE} = \frac{|h_1| + |h_2| + |h_3|}{|h_0|} \tag{2.5}$$

To force all post-cursor components to zero, the transconductance of the

Figure 2.8: A 3-tap ADFE (a), and a (1+2)-tap LUDFE, i.e., the first tap is unrolled (b). Although the signals and circuit blocks are fully differential, for simplicity, they are shown as single ended.

Figure 2.9: Illustration of the impulse response of a  $h_0 + h_1 z^{-1} + h_2 z^{-2} + h_3 z^{-3}$  channel.

summing amplifier,  $g_{m,S}$ , and total transconductance of the taps in DAC1,  $g_{m,DAC1}$ , have to be chosen such that:

$$g_{m,S} = \frac{A_1 \omega_{bw1} C_L}{1 - \underbrace{\left(\frac{A_1 \omega_{bw1}}{\omega_T / \gamma}\right)}_{term \ \alpha} \underbrace{\left(1 + \frac{2W_{DFE} V_{cursor}}{v_{od,t}}\right)}_{term \ \beta}}$$

(2.6)

$$g_{m,DAC1} = \frac{2g_{m,S}W_{DFE}V_{cursor}}{v_{od,t}}$$

(2.7)

where  $A_1\omega_{bw1}$ ,  $C_L$ ,  $\omega_T$ ,  $\gamma$ ,  $v_{od,t}$ , and  $V_{cursor}$  are the gain-bandwidth required to meet the timing closure at the summing node, input capacitance of the slicer, the unity-gain frequency of the input devices in the summing amplifier,  $c_{dd}/c_{gg}$  (i.e.,  $C_{drain}/C_{gate}$ ) of input devices, overdrive voltage of the tap devices, and the amplitude of the cursor, respectively. Allocating  $m\tau$ (m times the time constant of the summing node) for settling, the required bandwidth is  $\omega_{bw1} = m/(1UI - t_{del1})$ , where  $t_{del1}$  is the worst-case data propagation delay among taps (usually is the highest for the first tap). In Eq. 2.6,  $term \alpha$  is due to the self loading of the summing amplifier and  $term \beta$  introduces the effect of  $W_{DFE}$  on self loading of the summing amplifier. The total transconductance required for timing closure  $g_{m,total}$  is equal to  $g_{m,DAC1} + g_{m,S}$ .

#### 2.4.2 Loop-unrolled DFE

Compared to the shift-register flip-flops in Fig. 2.8a, the comparator has a higher propagation delay as it should resolve a small signal difference to the full swing. Thus, the overall timing margin for the entire loop is limited by the small timing margin of the first tap. One well-known remedy is the loop-unrolled DFE (LUDFE) architecture shown in Fig. 2.8b, in which the first tap is taken out of the critical path by having two comparators in parallel. However, this is achieved at the price of the added multiplexer (MUX) delay and the doubled  $C_L$ , which in turn may increase the overall required  $A_1\omega_{bw1}$  at the summing node [31]. Hence, considering channels with different first post-cursor  $h_1$  (or equivalently the weight of first DFE tap,  $t_1$ ), this approach does not necessarily decrease DFE's power penalty or enhance the timing margin. For the LUDFE shown in Fig. 2.8b, the term  $W_{DFE}$  in Eqs. 2.6 and 2.7 shall be replaced by  $W_{DFE} - (|h_1/h_0|)$ .

### 2.5 Proposed adaptive slicing technique

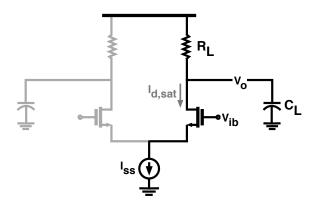

The proposed adaptive slicer DFE (ASDFE) technique is based on [32] and is shown in Fig. 2.10a. Here, instead of subtracting the post-cursor ISI from

Figure 2.10: ASDFE technique (a). The gray lines indicate low-speed signals. SASDFE architecture (b).

the signal itself and performing a bit decision using a static threshold, the slicer (comparator) threshold  $V_s$  is adaptively adjusted in each UI and the distorted signal coming from the channel is left unaltered. Based on the

knowledge of channel's impulse response and the previously recovered bits, the appropriate threshold is achieved through deviating  $V_s$  from the average of the worst-case '1' and the worst-case '0' voltages. Unlike ADFE and LUDFE that most of the capacitive loading is on the timing-critical summing node, the proposed approach allows for distributing the capacitance between the inputs of the slicer. In this technique, the need for a fast-settling summing amplifier is obviated as signal summation is replaced by threshold adaption. In ASDFE, a pre-amplifier having transconductance of  $g_{m,P}$  is used to drive the input capacitance of the slicer  $C_L$ . For  $g_{m,P}$ , and total transconductance of taps in DAC3,  $g_{m,DAC3}$ , we can write

$$g_{m,P} = \frac{A_1(m/1UI)C_L}{1 - \left(\frac{A_1(m/1UI)}{\omega_T/\gamma}\right)}$$

(2.8)

$$g_{m,DAC3} = \frac{W_{DFE} A_1 \omega_{bw3} C_L}{1 - \left(\frac{W_{DFE} A_1 \omega_{bw3}}{\omega_T / \gamma}\right)}$$

(2.9)

where terms with subscripts '1' and '3' refer to ADFE and ASDFE architectures, respectively. In Eq. 2.9 the required bandwidth to meet the timing closure,  $\omega_{bw3}$ , is slightly more than  $\omega_{bw1}$  due to additional delay of an XOR gate, i.e.,  $t_{del3} > t_{del1}$  (Fig. 2.10a).

Figure 2.10b shows the proposed speculative adaptive slicer DFE (SAS-DFE) architecture which is based on the two-way parallel implementation of the ASDFE technique. Here, in addition to adapting the comparator threshold based on the previously recovered bits as in ASDFE, the threshold of each of the two comparators is affected by the speculation based on

the two possible bit outcomes '0' or '1'. The threshold  $V_{s+}$  is based on a speculated value of '1' for the cursor. In the same manner, threshold  $V_{s-}$  is adjusted based on a speculated cursor value of '0'. The main motivation for having two ASDFE loops in parallel is to enable signal digitization, which is required by clock recovery (CR) algorithms such as Mueller-Muller [33]. For digitization,  $V_{s+}$  and  $V_{s-}$  are set below and above the corresponding speculated cursor voltage levels, respectively. While holding the sampled signal, the two thresholds are swept in opposite directions in consecutive search cycles similar to successive approximation ADC (SAR) [32]. However, unlike the SAR method, the proposed digitization method has a much smaller search domain and hence a significant speed advantage. Considering k number of search cycles, Eq. 2.8 can be modified for SASDFE architecture by using  $(k \times m)/1UI$ , as the pre-amplifier should settle before the first digitization cycle. Additionally, the capacitive load  $C_L$  is doubled. Finally, in Eq. 2.9 we have  $\omega_{bw4} = (k \times m)/(1UI - t_{del4})$ , where the term with subscript '4' refers to SASDFE. Note that the parallelism in SASDFE of Fig. 2.10b is equivalent to 1-tap loop unrolling; therefore, we typically have  $t_{del4} < t_{del3}$ .

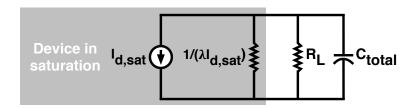

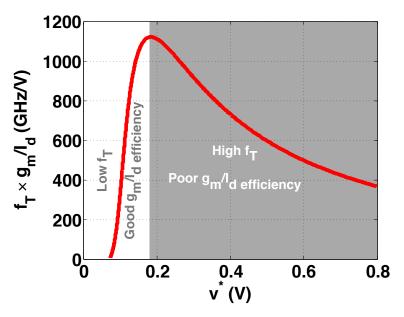

### 2.6 Comparison of power-equalization efficiency

Figure 2.11a compares the  $g_{m,total}/W_{DFE}$  trade-off between ADFE and AS-DFE. If we denote  $v^*$  as

$$v^* = \frac{2I_d}{g_m},\tag{2.10}$$

Figure 2.11: Comparison of  $g_{m,total}/W_{DFE}$  trade-off between ADFE and ASDFE (a), and between LUDFE and SASDFE (b).

then, considering that during the design process  $v^*$  is typically chosen to be a fixed value <sup>4</sup>, we would have

$$P_{total} \propto g_{m,total}$$

(2.11)

where  $P_{total}$  is the total power consumption. Therefore, while the vertical axis is in units of Siemens, it is also generally proportional to the overall power consumption.

In ADFE, the power penalty due to  $W_{DFE}$  increases considerably if the amount of post-cursor ISI that needs to be canceled is more than the  $V_{cursor}$ . Such power penalty can quickly dominate the RX power consumption. On the other hand, the ASDFE approach shows a more relaxed trade-off. Figure 2.11b shows the same comparison between LUDFE and SASDFE, both utilizing two slicers in parallel. The LUDFE graph is plotted for the two cases that the unrolled tap  $t_1$  (or equivalently the first post-cursor component  $h_1$ ) has values equal to 0.2 and 0.7 with respect to the cursor. Such  $|h_1/h_0|$ ratios are the prevalent extremes among serial links [35]. The SASDFE graphs are plotted for full-rate, and 5-way time-interleaved sub-rate architectures, where in both cases we have k = 5. As  $W_{DFE}$  increases, achieving timing closure in full-rate SASDFE quickly becomes power-inefficient and ultimately infeasible. However, the sub-rate SASDFE provides simultaneous equalization, data recovery and digitization of sampled signal with a power dissipation comparable to that of LUDFE at relatively high values of  $W_{DFE}$ .

<sup>&</sup>lt;sup>4</sup>In high-speed analog circuits typically we choose  $v^* \approx 0.2 \ V$  [34].

#### 2.7 Chapter summary

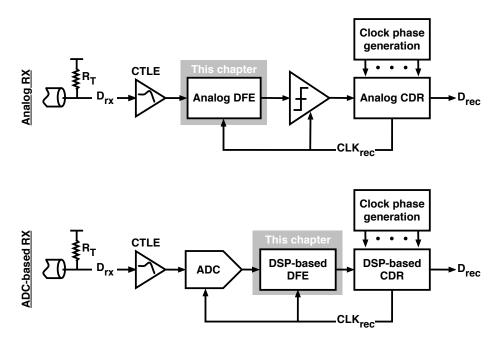

Figure 2.12: Graphical illustration of the digital and analog DFE blocks addressed in this chapter, and their interaction with other RX blocks.

With the emerging high-speed wireline data rates, canceling higher amounts of post-cursor ISI would be a necessity. As noted on Fig. 2.12, this chapter investigates the power penalty of canceling a certain amount of post-cursor ISI taps  $(W_{DFE})$  using DFE. From Fig. 2.12 it can be seen that the equalized signal is used for recovering the data and aligning the sampling edge of clock to the middle of data eye. While the analog and digital CDR architectures proposed in Chapters 5 and 6 do not include a DFE<sup>5</sup>, it should be noted that an under-equalized data eye can severely degrade the perfor-

$<sup>^5{\</sup>rm For}$  the purpose of measurements, high-frequency cables and probes are used to provide interface to the chip

mance of the CDR; this is further discussed in Chapter 7. In this Chapter, the sub-rate SASDFE architecture was proposed, which facilitates canceling significant amount of post-cursor ISI and simultaneous digitization of sampled data, while avoiding unreasonable power dissipation at RX front-end. In particular, in high-loss channels that ADFE or LUDFE based RXs may be impracticable due to excessive power consumption, ASDFE and sub-rate SASDFE designs provide a relaxed power-equalization trade-off. In Chapter 3, we propose a digital RX architecture which builds on the SASDFE.

## Chapter 3

# Low-power DSP-based RX

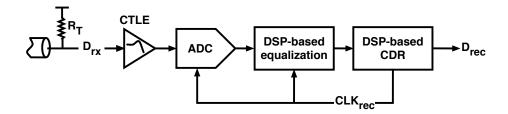

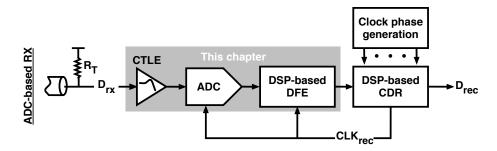

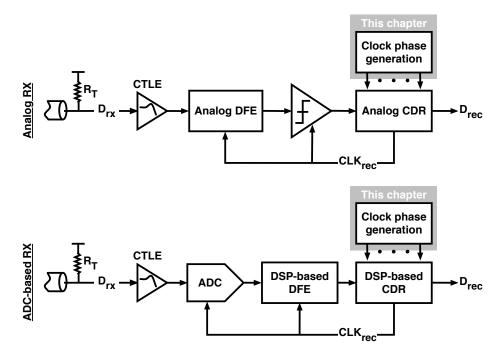

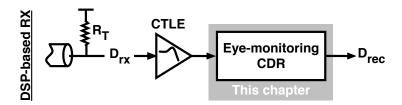

While CMOS scaling has been promising to enhance the performance of digital circuits, from an analog perspective, the performance of N-channel and P-channel devices has deteriorated in scaled CMOS technologies [34]. Hence, the trend of moving as much as signal processing tasks as possible from analog domain to digital domain is becoming more and more popular. Following this trend, advanced high-speed serializer/deserializer (SerDes) circuits are becoming more DSP-based to take advantage of improved functionality and flexibility of the digital clock and data recovery (CDR) and equalization [25, 27, 36, 37]. Figure 3.1 shows the simplified block-diagram of a DSP-based (ADC-based) wireline RX. Usually, a gain block precedes the ADC to adjust the swing of received signal based on the input range of ADC. Additionally, as explained in Chapter 2, the gain stage may act as CTLE to provide high-frequency peaking to partially compensate for ISI. The digitized signal provided by ADC is processed by succeeding DSP-based equalization and clock recovery blocks.

As wireline data rates increase in the multi-Gb/s range in the emerging standards, e.g., IEEE 802.3ba Ethernet standard, sophisticated feed-forward equalization and decision feedback equalization are needed to compensate

Figure 3.1: Simplified block diagram of an ADC-based RX.

for ISI. Such elaborate equalization translates into tens of FFE and DFE taps, that if implemented in analog domain, result in a large silicon area and a high power consumption beyond what can be afforded in a practical RX. Therefore, the evolution towards a digital architecture seems vital to enhance the power/area scalability, achieve bit error rates (BERs) equal to or better than  $10^{-12}$  under high channel loss [38], and simplify the migration of circuits to more advanced process technologies.

### 3.1 Quantifying power efficiency in RX

Although promising, the performance merits of DSP-based receivers is confined by metrics such as power consumption, speed, digitization resolution, and the impairments of the front-end ADC [25, 37]. Among these issues, the high power consumption of an ADC operating beyond 10 GS/s is a prohibiting factor to integrate one within an RX. Figure 3.2 shows<sup>6</sup> the trade-off between power consumption and sampling frequency,  $F_s$ , of different ADC architectures, which have been published in literature from 1997 to 2012. To provide a fair comparison, an FoM is defined for power consumption per

<sup>&</sup>lt;sup>6</sup>Plotted based on data from [39].

Figure 3.2: Power consumption versus sampling frequency for ADC's published in literature from 1997 to 2012.

conversion step and is defined as follows

$$FoM_{adc} = \frac{P_{adc}}{2^n \times F_s}$$

(fJ/conversion step) (3.1)

where n is the digitization resolution. Based on Fig. 3.2, the total power consumption,  $P_{adc}$ , of a 5-bit 10 GS/s ADC which samples the 10 Gb/s received data,  $D_{rx}$ , once every UI (i.e., baud-rate sampling), is given by

$$P_{adc} > 2^5 \times 10 \; (GHz) \times 500 \; (fJ/conversion step) = 160 \; (mW)$$

(3.2)

To realize the feasibility of using such ADC in the RX, we use a commonly used FoM for power efficiency of RX, which is given by

$$FoM_{RX} = \frac{P_{RX}}{DR} = \frac{P_{ctle} + P_{adc} + P_{eq} + P_{cdr}}{DR} \quad (mW/Gb/s)$$

(3.3)

where DR is the data rate, and  $P_{RX}$ ,  $P_{ctle}$ ,  $P_{eq}$ ,  $P_{cdr}$  are the power consumptions of RX, CTLE, FFE/DFE, and CDR. Therefore, the  $P_{adc}$  of 160 mW given in Eq. 3.2, results in  $FoM_{RX} > 16$  mW/Gb/s. While such power consumption can be tolerated in high-speed optical TX-RX pairs (Fig. 1.4b), it is not a viable option for chip-to chip communication where an array of TX-RX pairs is used (Fig. 1.4a).

Recently published work [40, 41] use interpolating-flash and pipeline ADC topologies for the front-end ADC to decrease the number of comparators from the  $2^n$  regime in full-flash n-bit ADCs [27, 42] to 17 [40] and 6 [41] comparators per sub-ADC for 5 bits of resolution, respectively. This is achieved at the price of limiting the speed of each sub-ADC to 2.5 GS/s [40] and 1.2 GS/s [41]. In this Chapter, we propose a hardware efficient low-power RX architecture which utilizes the SASDFE introduced in Chapter 2.

### 3.2 ADC performance requirements

The ADC topology and its digitization resolution depend on the speed, power, and BER requirements of RX. For multi-Gb/s receivers, usually flash topology is the feasible choice [27, 37, 42]. However, high power consump-

tion and capacitive loading of a flash ADC make its use in high-speed digital RX, and the move from conventional binary RX to ADC-based RX, debatable [36]. Recently, using SAR topology, promising performance has been achieved at speeds up to 24 GS/s [43] and 40 GS/s [44]. Nevertheless, such ADCs do not necessarily consume less power than a full-flash ADC [45]. As the maximum conversion rate of a single SAR ADC is still less than 100 MS/s [46], it should be highly interleaved (i.e.,  $160 \times$  in [43]) to reach sampling rates beyond 10 GS/s. Such immense level of interleaving results in high area overhead due to peripheral circuitry, and an elaborate calibration mechanism is needed to cancel the sub-ADC non-idealities to avoid pattern-noise in ADC array [47]. In our design, by using the proposed speculative digitization technique in the SAR ADC, we have limited the interleaving factor of the ADC to 5 for a 10 GS/s speed, in 65 nm CMOS. To determine the sampling frequency of the ADC, a trade-off should be made between  $P_{adc}$  and the amount of information provided to the clock recovery algorithm (i.e., more information is extracted from  $D_{rx}$  in an oversampling clock recovery scheme) [40]. In this work, as in [27], the overall ADC sampling and digitization rate is equal to the baud-rate to achieve a data recovery rate equal to the highest clock rate in the system. Hence, Mueller-Muller [33] algorithm would be a candidate for the clock recovery scheme.

There are several factors such as channel characteristics, and the signaling scheme that determine the resolution of ADC. In presence of higher amounts of ISI, the ADC resolution needs to be higher to allow for optimum equalization and clock recovery with the aid of the DSP core. Also, In multi-level

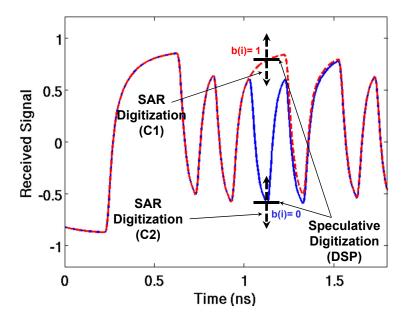

Figure 3.3: Illustration of speculative (solid lines) and SAR digitization steps (dashed lines) for two different data patterns. The two patterns differ in the received bit at time=1.1ns.

signaling schemes, the maximum number of signal levels that can be transmitted is confined by the receiver's ADC resolution [25].

### 3.3 Speculative/SAR digitization algorithm

Figure 3.3 shows two distorted 10 Gb/s patterns at the RX end of the channel, which only differ in the bit received at time=1.1 ns. Due to the lowpass nature of the channel, the received data can no longer maintain the original voltage levels which are represented by a '0' or a '1'. The high-frequency signal components are filtered out and hence, if a consecutive '0' and '1' pattern is transmitted, the difference in the values of ab(i) (i.e., analog value

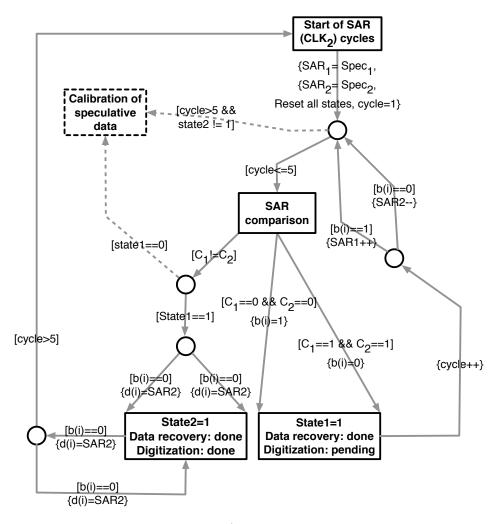

Figure 3.4: The hybrid speculative/SAR digitization algorithm implemented as a finite state machine. [] and {} indicate IF and DO statements, respectively.

of current sampled bit) and ab(i-1) are reduced compared to that at the TX side. The value of ab(i) depends on its preceding bits, as if the channel has a memory [26]. Hence, if a full-flash ADC is used in the AFE, only a few comparators will be decisive in digitizing ab(i) at each sampling cycle of ADC. This is due to the fact that ab(i) will not cross the threshold of the rest of the comparators. Through the hybrid speculative/SAR digitization algorithm of Fig. 3.4, we exploit channel's memory to quickly speculate the digitized value of each received bit based on the 4 previously recovered bits, and then use the conventional SAR digitization cycles to fine-tune the speculated value to yield d(i). As shown in the algorithm of Fig. 3.4, a finite state machine (FSM) uses the speculated value to narrow down the SAR search domain. The SAR step (dashed horizontal lines in Fig. 3.3) takes over the speculative step of the algorithm from the points specified by the two speculated values (solid vertical lines in Fig. 3.3). In this work, due to the fact that there are typically two separated domains based on either transmitting a '1' or a '0', two comparators  $(C_1 \text{ and } C_2)$  are used to perform the SAR cycles for each of the two cases b(i)=0 or b(i)=1. Breaking the SAR search domain into two separate paths enhances the speed of digitization and data recovery functions. As shown in Figs. 3.3 and 3.4, in the speculative step of the hybrid algorithm, the thresholds of comparators  $C_1$  and  $C_2$  are simultaneously adjusted at the beginning of each SAR sampling cycle. Note that the thresholds of  $C_1$  and  $C_2$  are chosen such that they fall below, and above the speculated analog values for b(i) = 1 and b(i) = 0, respectively. Interestingly, the proposed speculative/SAR digitization algorithm resembles the SASDFE architecture proposed in Chapter 2. Therefore, as explained in the

next Section, in the proposed hardware implementation, we merge the digitization and DFE loops to achieve hardware efficiency, and systematically reduce the power consumption.

Figure 3.5: Block diagram of the proposed RX. All clocks and analog signals are differential. The clock recovery loop is not integrated into the prototype chip.

#### 3.4 Implementation of the proposed algorithm

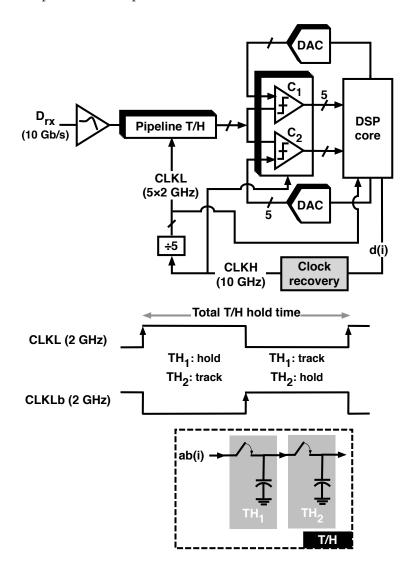

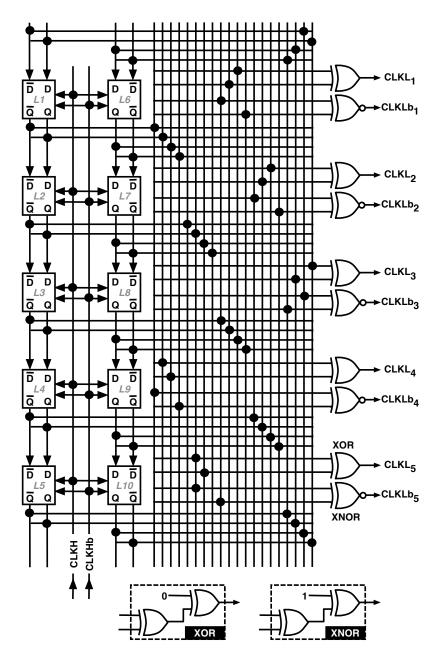

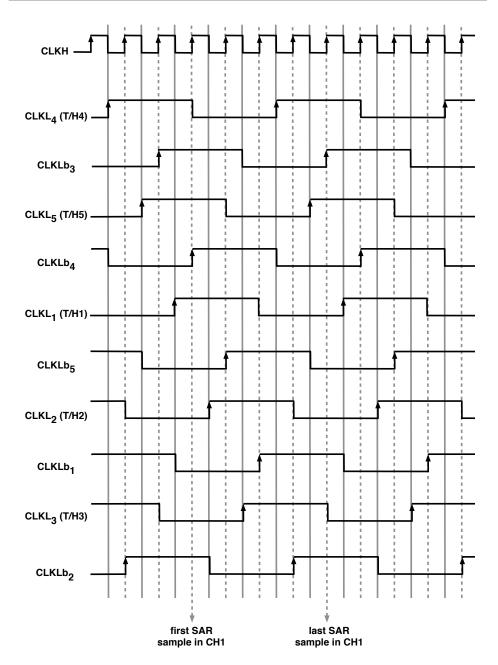

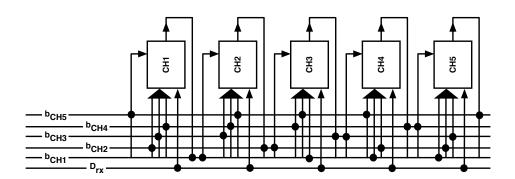

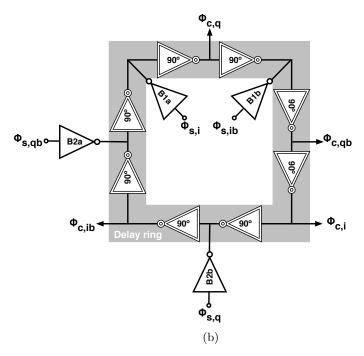

Figure 3.5 shows the block diagram of the proposed DSP-based RX, which is a modified version<sup>7</sup> of the SASDFE architecture proposed in Chapter 2. The RX is implemented as 5 time-interleaved channels. Following the termination and peaking block, the received data from the channel is sampled by a two stage track-and-hold (T/H). As shown in the timing diagram at the bottom of Fig. 3.5, the sampling time of T/H in each channel is controlled by one of the five phases<sup>8</sup> of the 2 GHz clock CLKL. The pipelined arrangement of T/H allows to keep the sampled analog signal ab(i) constant for 5 sampling cycles in  $C_1$  and  $C_2$  comparators, controlled by the 10 GHz clock CLKH. As shown in Fig. 3.6, the 5 phases of CLKL are generated by a divide-by-10 function applied to CLKH, followed by multiply-by-2 using XOR and XNOR gates. The delay ring is implemented using 10 latches. Unlike the conventional divide-by-5 circuits [48] that yield only three phases with 40% duty cycle, the proposed architecture of Fig. 3.6 achieves 5 phases (i.e. 10 differential phases) with 50% duty cycle. To minimize deterministic jitter in CLKL phases, inputs and outputs of all latches are equally loaded. Additionally, the frequency-doubling XOR and XNOR gates are implemented as shown in the bottom of Fig. 3.6 to yield equal propagation delays.

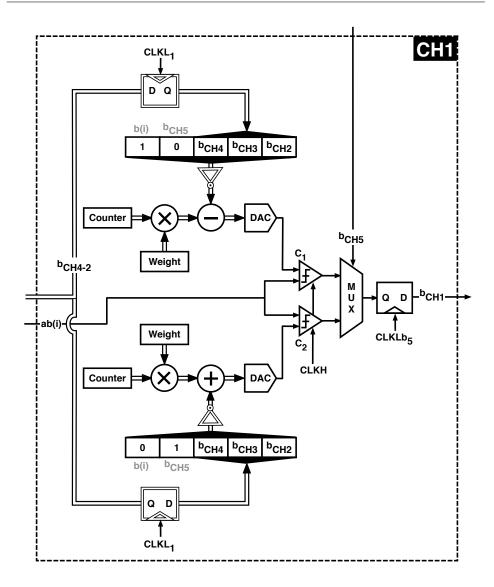

Following the T/H, the sampled data, ab(i), is equalized, recovered, and ultimately digitized by the SASDFE loop shown in Fig. 3.7. Note that,

<sup>&</sup>lt;sup>7</sup>While the principal of the operation is the same as Fig. 2.10b, the implementation of Fig. 3.7 is slightly modified to enable timing closure in the feedback loop.

<sup>&</sup>lt;sup>8</sup>5 phases single-ended, or equivalently 10 phases differential.

Figure 3.6: Schematic of the divide-by-5 circuit generating five differential phases of the 2 GHz clock CLKL, from the 10 GHz clock CLKH.

ab(i) is the received bit which has been distorted by the channel and has an analog nature, d(i) is the digitized value of ab(i), and  $b_{CHX}^{9}$  denotes the recovered bit from each channel, which is known to the receiver only after data recovery. Finally, b(i) refers to the most recent recovered bit, in the overall stream of recovered bits from the 5 channels. As shown in Fig. 3.7, each sub-ADC<sup>10</sup> has two comparators whose thresholds are adjusted using digital-to-analog converter (DAC). The comparators have a CML topology [49], and the DACs are implemented with a current-steering architecture [50]. The latches inside the comparators operate in a pipeline manner and are controlled by differential clock CLKH-CLKHb which is recovered from the received data<sup>11</sup>. As demonstrated in the timing diagram of Fig. 3.8, there are 5 SAR sampling cycles within the 500 ps time that T/H keeps ab(i) constant. Based on characterizing the channel, the thresholds of  $C_1$ and  $C_2$  are set in a manner to recover the data (i.e.,  $b_{CHX}$ ) in the first SAR cycle. The four remaining SAR cycles are performed to find the digitized value of ab(i), d(i), which is in turn used by the DSP-based clock recovery algorithms such as Mueller-Muller [33] to update the phase of CLKH. As explained in Chapter 2, adjusting the thresholds of  $C_1$  and  $C_2$  in each SAR cycle of the RX channel shown in Fig. 3.7 is equivalent to implementing a 4-tap DFE. Thus, the demonstrated implementation of the RX architecture is suitable for a channel that d(i) of the most recent sampled bit ab(i)is mostly influenced by the last four bits b(i-1), b(i-2), b(i-3), and

$<sup>^9</sup>$  "X" refers to the channel number.

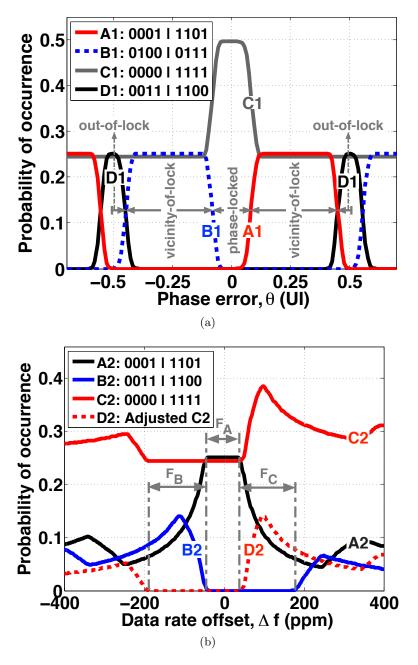

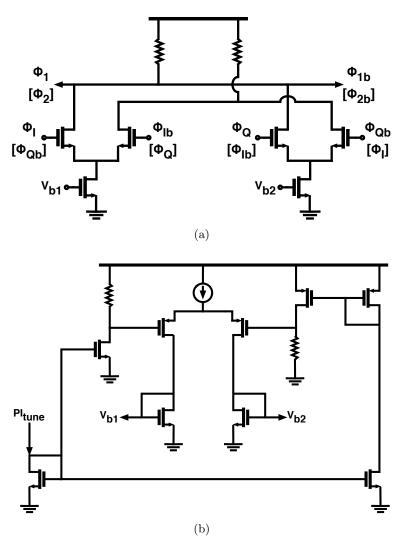

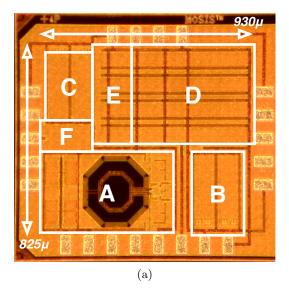

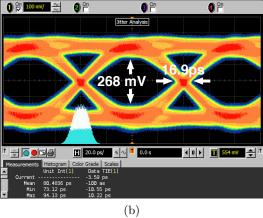

$<sup>^{10}</sup>$ the comparator pair  $C_1$  and  $C_2$  in each channel make a sub-ADC, while the top level ADC consists of 5 time-interleaved sub-ADCs.