- This moment in computing history

- <sup>02</sup> Silicon photonics to drive progress

- OB CPO and challenges

- <sup>04</sup> New ideas are needed

TEAM

2 OFFICES 2 PRODUCZS 125 EMPZOYEES 150 PATENTS

Boston

Mountain View

Passage

Envise

Nicholas Harris, PhD Founder, CEO

Thomas Graham Founder, CFO

Ritesh Jain VP, System Engineering

Steve Klinger VP, Product

Beth Keil VP, People

Darius Bunandar, PhD Founder. Chief Scientist

Richard Ho VP, HW Engineering

Ayon Basumallik, PhD VP, SW Engineering & ML

Sujatha Wagle VP, Supply Chain Ops

Bob Turner VP, Sales

# Spark Capital Matrix Partners Viking Global Hewlett-Packard Enterprise Massachusetts Institute of Technology Stanford University

\$300mm Raised

GV (Google Ventures)

Sequoia

# This moment in computing history.

Interconnect is being transformed.

**JIGHTMATTER**

#### Al and Generative Models

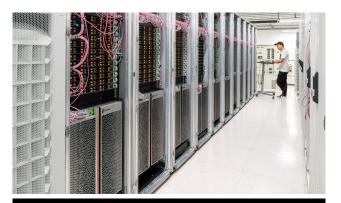

- Workloads spanning 10,000 accelerators running regularly

- Memory capacity, BW requirements exploding

- HBM and network I/O fighting for scarce shoreline

- Imbalanced memory, compute, networking → poor datacenter utilization

- Networking an increasing fraction of datacenter capex

- Al system costs are exploding; biggest companies spending billions

- Cost per user for Al workloads driving down cloud margins

JIGHTMATTER |

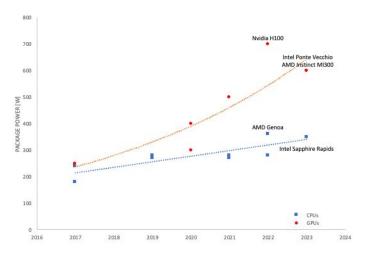

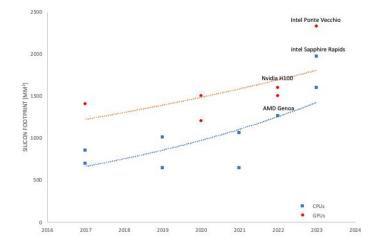

#### Dennard and Moore

- We're getting more transistors, but we can't use them

- From 300W to 800W in 6 years; spread these hot potatoes out

- Cost per chip ballooning

- Huge packages needed to increase single chip performance

- Water cooling is now standard in AI/HPC; immersion is next

### Packaging Defines Performance

- The competitive advantage of a chip company increasingly depends on its packaging capabilities.

- How many chiplets? Package body size? Max power delivery?

- Chip I/O bandwidth is capped by max TDP and package area.

# Silicon photonics as a tool to drive computing forward.

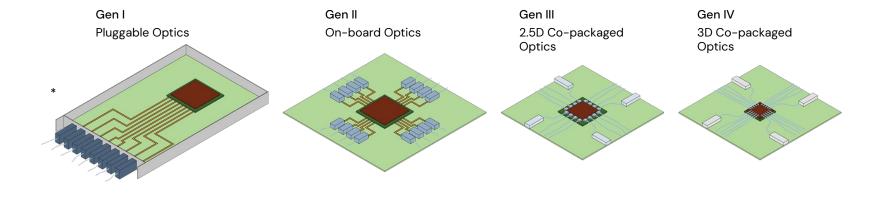

#### Optics Roadmap

Closer and closer to the chip

INCREASING BANDWIDTH, ENERGY EFFICIENCY

∠IGHTMATTER

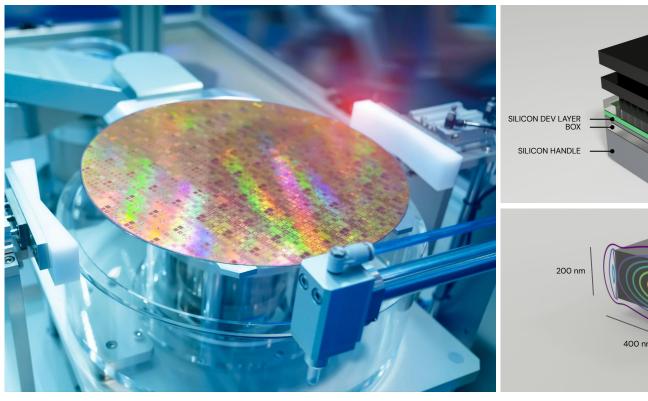

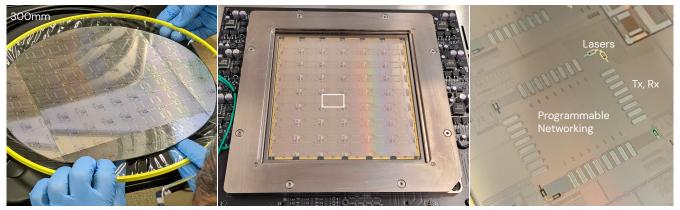

300mm CMOS Fab

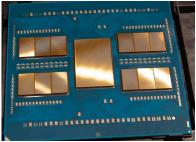

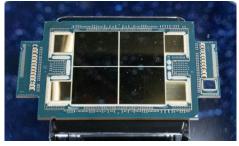

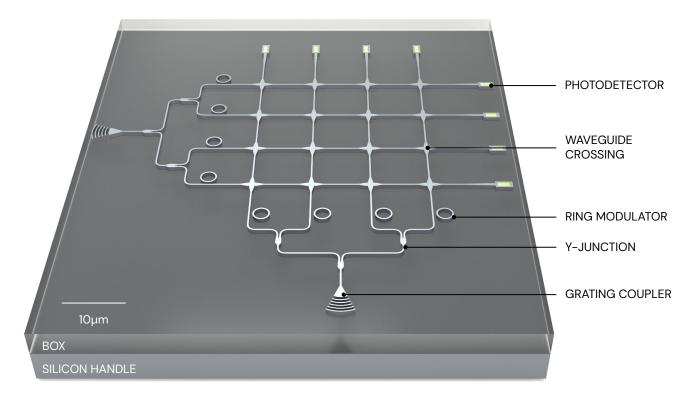

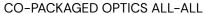

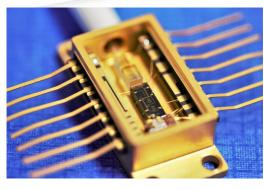

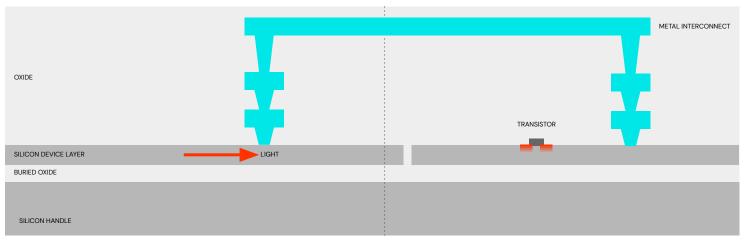

## What does silicon photonics look like?

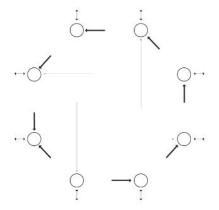

An example of a (random) photonic network

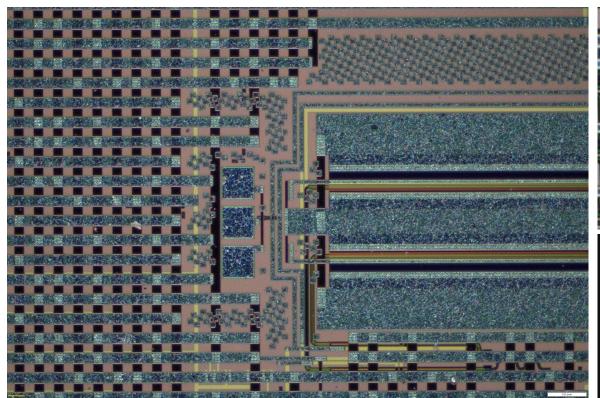

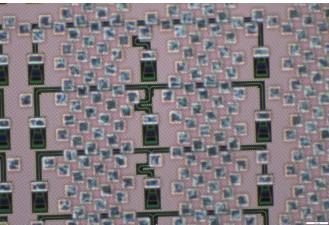

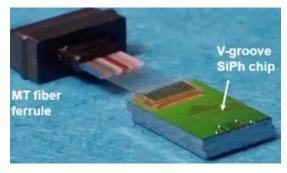

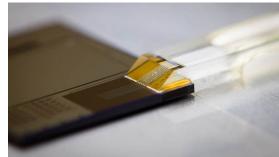

## What does silicon photonics look like?

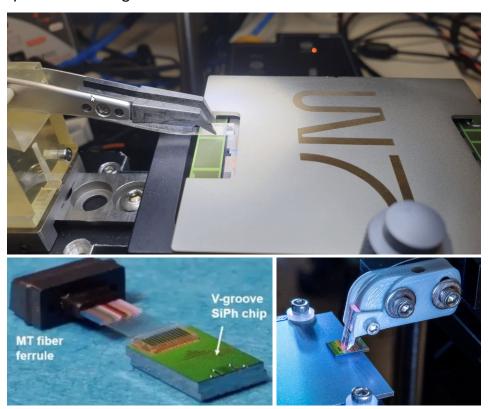

Photographs

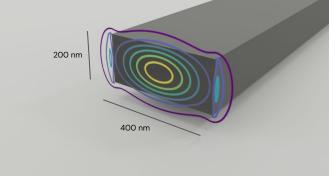

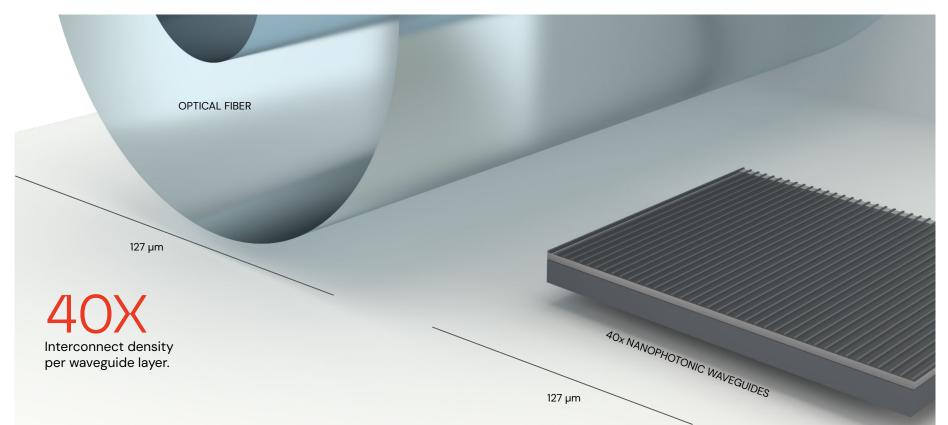

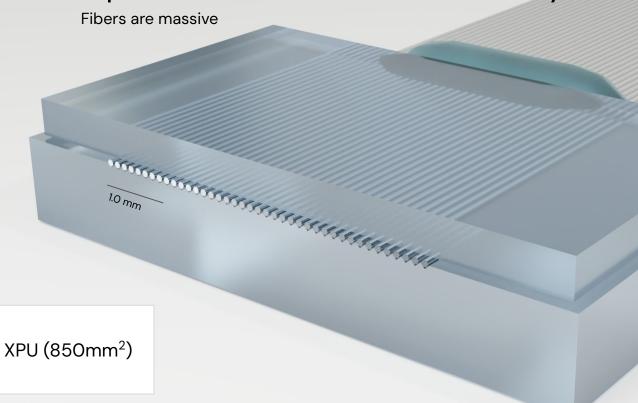

#### A Sense of Scale

Optical fibers versus nanophotonic waveguides

# CPO and challenges.

A call to action for the industry.

ZIGHTMATTER 15

PACKAGING IN-FIELD REPAIR

LASERS

FIXED NETWORK TOPOLOGIES

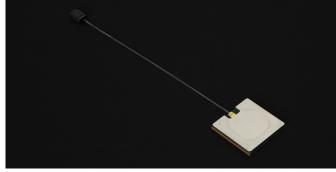

## Optical Fiber Attach

An industry-wide challenge

2.6 cm

3.3 cm

### Optical Fiber Beachfront Density

Max Fiber Count

64

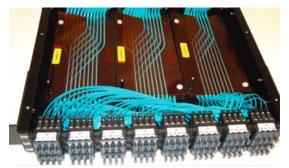

#### Optical Fiber Management

Serviceability, manufacturability, yield

**JIGHTMATTER**

#### Lasers

- Performance

- Max 8 colors

- ~50 mW per laser

- Max 8 lasers per laser chip

- Packaging and Form Factor

- Too many laser modules to power just one chip's I/O.

- Primitive packaging (wirebond)

- Limited thermal budgets

- Small mode field diameters for fiber coupling

- Supporting components require board real estate

- Functionality

- Color Multiplexing in laser die not generally available

# They have wings but do not fly.

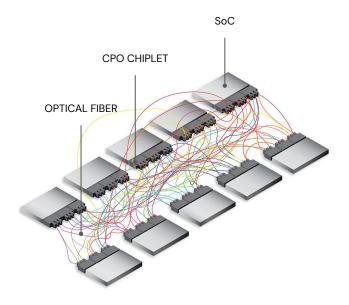

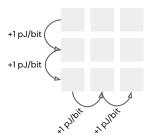

### Chiplets and Co-packaged Optics Needed

Challenges

MORE HOPS, MORE ENERGY

Each chiplet hop adds to communications energy consumption. Building large chiplet arrays this way will incur significant energy costs. CHIPLET XPU & CPO

- Fibers have low beachfront densityMore wavelengths, more BW

- Static interconnect

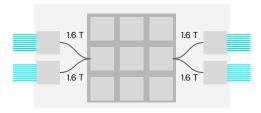

FEW CHIPS PER SWITCH

Only 8x CPO enabled chips saturate an entire 51.2 Tbps switch. Compute to switch ratio is poor.

# Supply Chain

- Is the photonics supply chain ready to support the growth it is about to see?

- Boutique players often have the tech needed for scale.

## New ideas are needed.

#### Recap

- Per-chip performance must scale. Chiplet packages can only get so big (latency, power)

- 10,000 GPU clusters are common place. I/O BW and latency must scale

- Shoreline limitation on BW

- CPO is growing the package footprint. Limited by beachfront.

- Fiber management is a major issue.

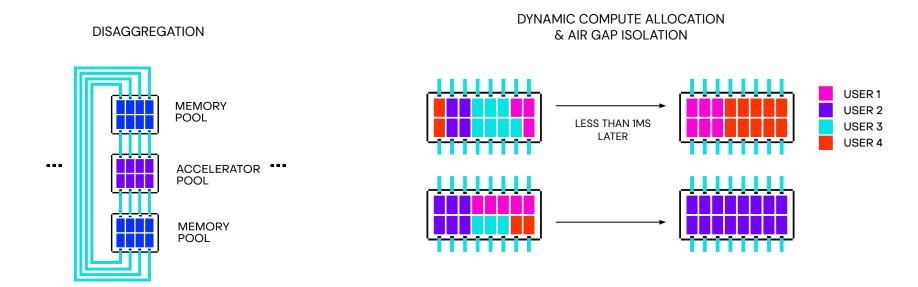

- Optical circuit switching is increasingly viewed as a path towards ultra-high performance, configurable interconnect.

# How can you address all of these challenges in one pass?

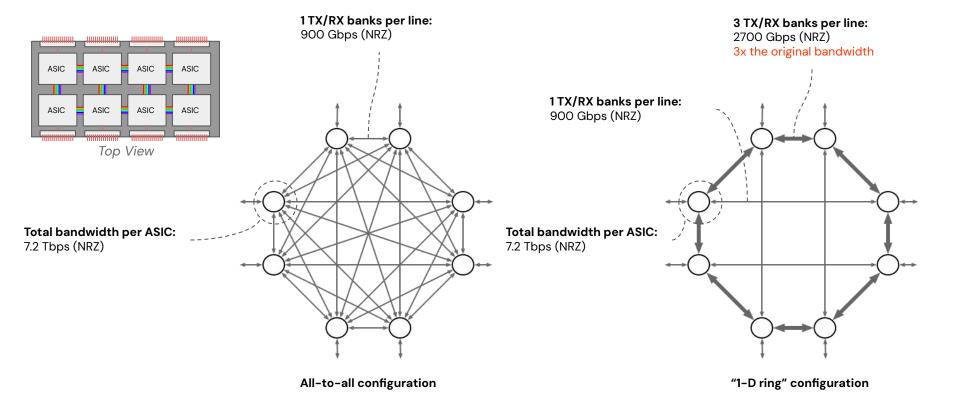

Uniform architecture allows flexible dicing based upon end application.

TOP VIEW

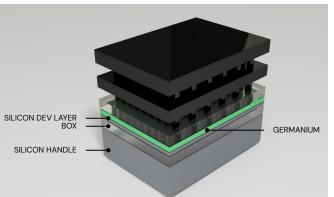

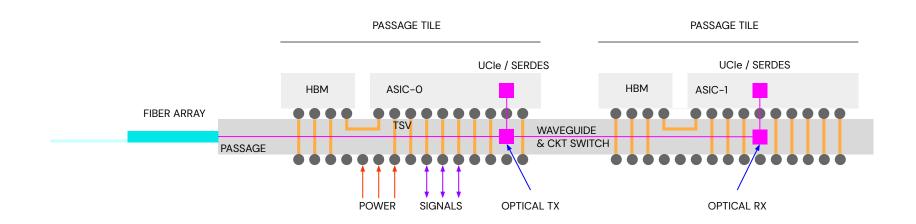

#### **Cross Section**

Chip-on-wafer Packaging

- Up to 700W of power delivery per ~800mm<sup>2</sup> area via TSVs.

- Cooling solution depends on tile ASIC TDP.

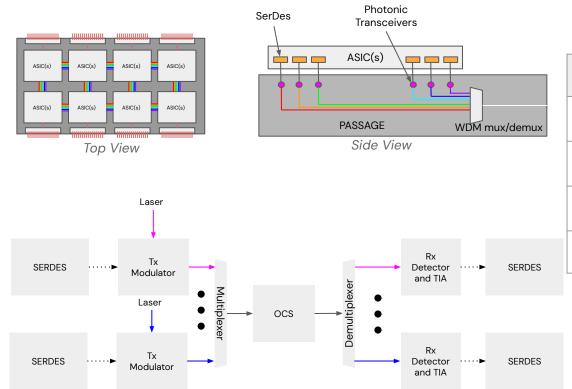

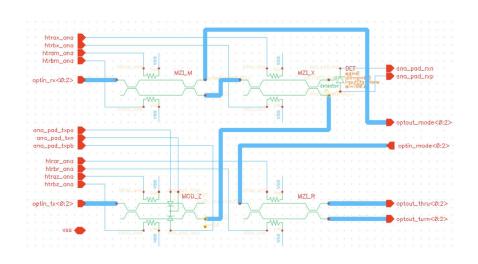

#### Photonic Datapath

#### **Supported Speeds**

| Modulation format                            | NRZ                        | PAM-4                   |

|----------------------------------------------|----------------------------|-------------------------|

| Bandwidth per TX/RX<br>(transceiver) pair    | 56 Gbps                    | 112 Gbps                |

| Wavelengths                                  | 8λ @ 200 GHz<br>spacing    | 8λ @ 200 GHz<br>spacing |

| Bandwidth per bank<br>(of 8λ or 1 waveguide) | 900 Gbps BiDi              | 1.8 Tbps BiDi           |

| BER                                          | 10 <sup>-15</sup> (no FEC) | 10 <sup>-6</sup>        |

#### How it works

Waveguide and metal stitching

RETICLE BOUNDARY

#### How it works

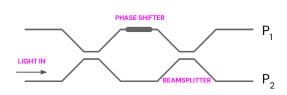

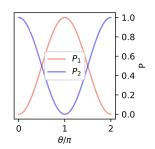

**Optical Circuit Switching**

MACH-ZEHNDER INTERFEROMETER

A spatial-mode router

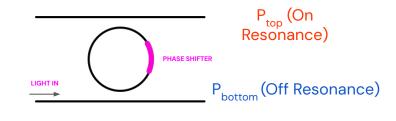

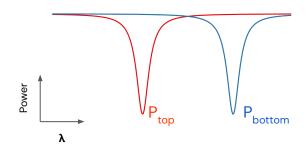

### RING RESONATOR A spectral-mode router

#### Reconfigurable Topologies

**Optical Circuit Switching**

### Reconfigurable Topologies

Optical Circuit Switching — Passage™ Native

INTRA- AND INTER-PASSAGE OCS

**OPTICAL FIBER OCS**

| Input/Output Fiber<br>Permutations |  |

|------------------------------------|--|

| (non-blocking switch network)      |  |

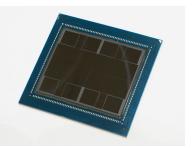

#### First-Generation Passage

The world's first photonic wafer-scale interconnect

#### Passage™ Alpha Silicon

- <50 Watts

- 32 channels per site, 1.024 Tbps

- 32 Gbps per channel NRZ

- 48 x 800mm<sup>2</sup> tiles

- 288x 50 mW Lasers

- 6.144 DACs

- 6,144 MZIs

- 150,000 photonic components

- JTAG interface

- Integrated Lasers, transistors, photonics

- Programmable interconnect topologies

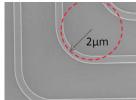

Photonic waveguides with ~4 µm pitch.

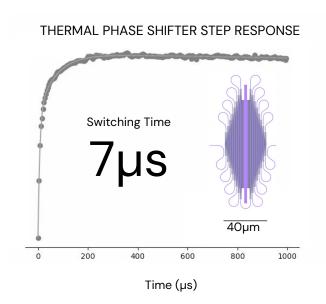

#### Circuit Switching

Controller and device performance

...AND THERE'S A PATH TO NANOSECONDS.

#### Solutions LM is Driving

A variety of applications

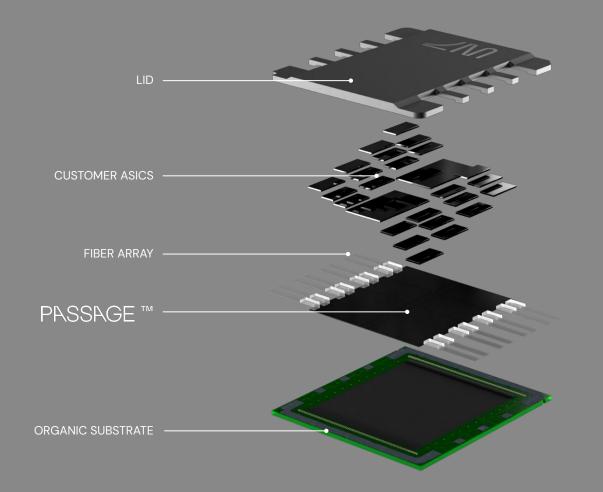

#### What is Passage?

Passage is a 3D co-packaged optics technology that combines a **self-contained** active optical interposer, advanced packaging technology and state of the art light sources to profoundly increase the capability of your ASICs.

- Multiplying bandwidth density

- Increasing serviceability

- Enabling volume manufacturing

- Reducing pJ/bit

- Reducing package size

# **ZHANK YOU**