Pipelined and Partitionable Forward Error Correction and Cyclic Redundancy Check Circuitry Implementation for PCI Express® 6.0

Dr. Debendra Das Sharma and Swadesh Choudhary

Intel Corporation

# Agenda

- PCIe 6.0 FEC and CRC recap

- FEC implementation

- CRC implementation

- Results

#### PCIe FEC and CRC Recap

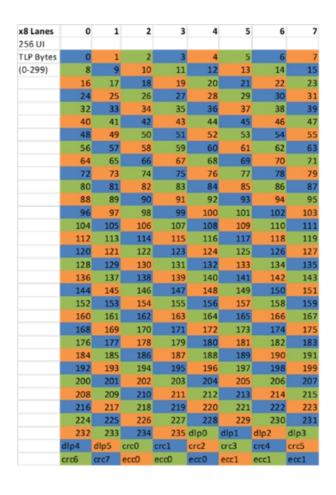

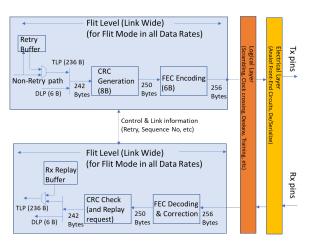

- 256B Flit, with 3 groups of FEC (interleaved bytes)

- 8B of CRC, 6B of FEC

- FEC covers the CRC bytes as well

- Each FEC is a (86, 84) code

- Syndrome and Parity bytes added by the encoder

- CRC is a Reed Solomon (250, 242) code

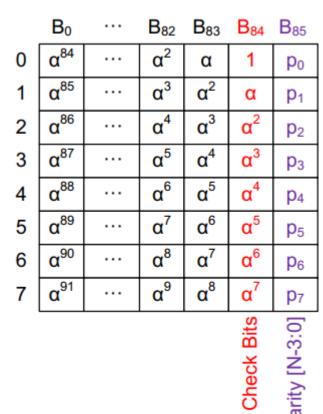

#### FEC encoder (Flat)

- Parity byte is a simple XOR of all the bytes

- $\alpha$  is the root of the primitive polynomial ( $x^8+x^4+x^3+x^2+1$ ) that is used to generate this code

- The check bits are computed using the following equation:

$$C = \sum_{i=0}^{83} B_i \times \alpha^{(84-i)}$$

## FEC encoder parity byte (pipelined)

| Width | Cycle | FEC Group |              |              |  |

|-------|-------|-----------|--------------|--------------|--|

|       |       | 0         | 1            | 2            |  |

| X16   | 0     | B [42:0]  | B [42:0]     | B [41:0]     |  |

|       | 1     | B[83:43]  | 00h,B[82:43] | 00h,B[82:42] |  |

| X8    | 0     | B[21:0]   | B[20:0]      | B[20:0]      |  |

|       | 1     | B[42:22]  | B[42:21]     | B[41:21]     |  |

|       | 2     | B[63:43]  | B[63:43]     | B[63:42]     |  |

|       | 3     | B[83:64]  | 00h,B[82:64] | 00h,B[82:64] |  |

| X4    | 0     | B[10:0]   | B[10:0]      | B[9:0]       |  |

|       | 1     | B[21:11]  | B[20:11]     | B[20:10]     |  |

|       | 2     | B[31:22]  | B[31:21]     | B[31:21]     |  |

|       | 3     | B[42:32]  | B[42:32]     | B[41:32]     |  |

|       | 4     | B[53:43]  | B[52:43]     | B[52:42]     |  |

|       | 5     | B[63:54]  | B[63:53]     | B[63:53]     |  |

|       | 6     | B[74:64]  | B[74:64]     | B[73:64]     |  |

|       | 7     | B[83:75]  | 00h,B[82:75] | 00h,B[82:74] |  |

- Depending on the link subdivision and FEC group, different bytes are available at different clock cycles (shown in the table)

- Parity computation is accumulated every cycle and is ready for consumption after the last chunk of the data is available

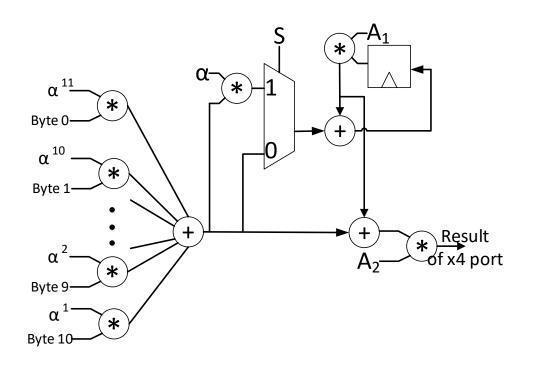

### FEC encoder check byte (pipelined for x4)

Key property utilized is that powers of α can be accumulated over a partial result to give an equivalent check value:

$$B_i * \alpha^{x+y} + B_j * \alpha^{z+y} = \left(B_i * \alpha^x + B_j * \alpha^z\right) * \alpha^y$$

A<sub>1</sub> and A<sub>2</sub> are parameters that map to specific powers of α and are selected to perform adjustments to account for the slight differences between the data byte ordering for the different FEC groups

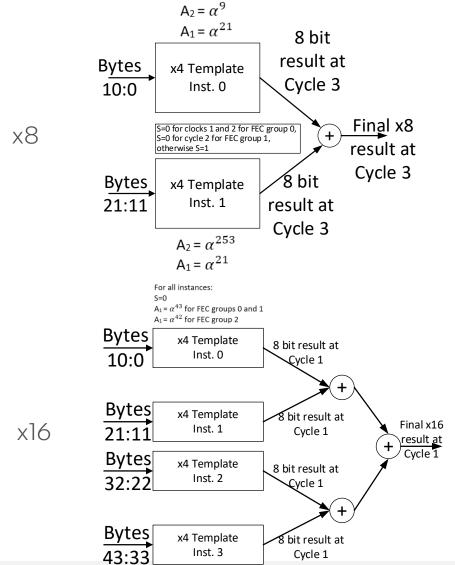

## FEC encoder check byte (pipelined for x8 and x16)

- Use x4 as a building block

- Multiple instances of them follow as it follows the data path split configuration

- S, A<sub>1</sub> and A<sub>2</sub> are selected to ensure the check computation is consistent and they account for slight differences in the byte order between different FEC groups

#### FEC Decoder

- Syndromes of Parity and Check are computed

- XOR of computed Parity, Check with the received Parity, Check respectively

- If Data[k] is the true message byte in kth position, and E[k] is the error byte that corrupted the kth position and A[k] is the corresponding power of  $\alpha$

- Syndrome of Parity = E[k]

- Syndrome of Check = E[k] \* A[k]

- Kth byte is in error if syndrome of Parity \*A[k] = Syndrome of Check

- The corresponding Data byte is corrected by an XOR with syndrome of parity

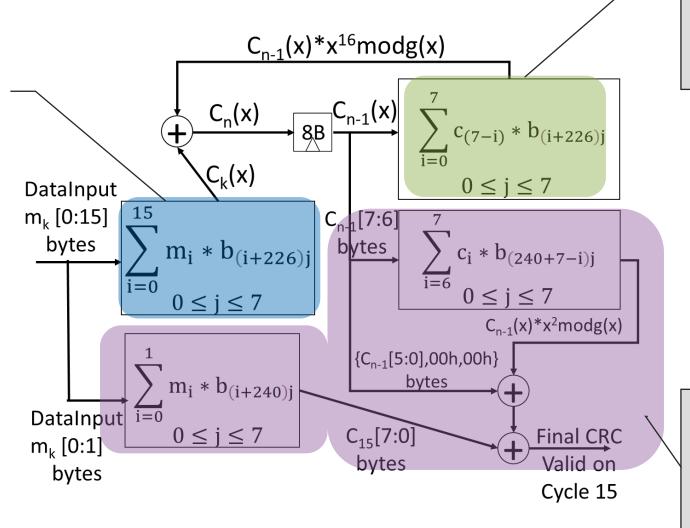

#### CRC Pipelining

- PCIe uses 8B CRC derived from a Reed Solomon code (250, 242)

- Given its generator matrix, each message symbol's contribution to the CRC is the XOR of the message with the corresponding byte in a specific row from the generator matrix

- Mathematical properties of polynomial division permit us to operate a message symbol on Row "x" of the generator matrix, followed by a translation operation on the result to get a value that is equivalent to operating the message symbol on Row "y"

- As data bytes stream in over multiple clock cycles

- Compute intermediate results using a subset of CRC computation and accumulate in eight bytes of flip-flops

- Final translation operation is performed to get a result equivalent to the Flat implementation (this translation also maps to a subset of CRC computation)

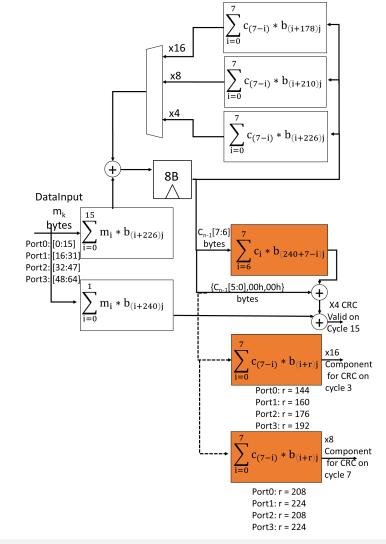

### CRC pipelining for a x4 port

Incoming Bytes for cycles 0 to 14 operate on rows 226:241 of the generator matrix

Intermediate results continue translation and accumulation every clock cycle

Final computation and adjustment to get CRC value on cycle 15

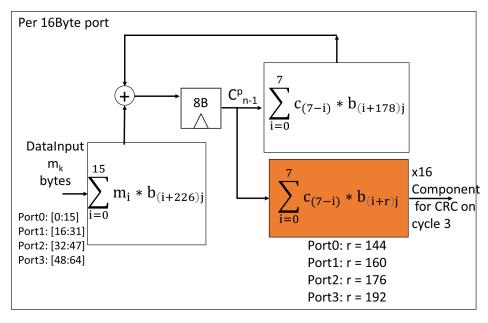

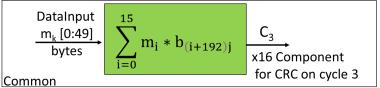

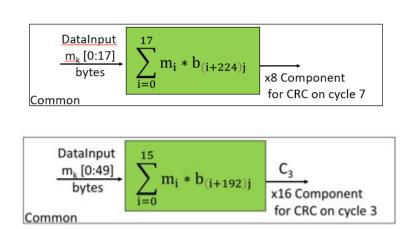

# CRC pipelining example of building x16 using x4 component

- x16 built using x4 components, but each port gets a different translation computation for the intermediate results

- There is common logic for computing the result of bytes coming in on the last cycle (cycle 3)

CRC pipelined implementation for x4, x8 and x16 together

#### Results

#### Logic Levels

|         | FEC (vs flat) | CRC (vs flat) |

|---------|---------------|---------------|

| Encoder | 12 (vs 9)     | 9 (vs 10)     |

| Decoder | 25 (vs 25)    | 9 (vs 10)     |

#### Area Improvement

|                            | Flat logic<br>(single port) | Flat logic<br>(4 ports)<br>~(4* 1 port) | Pipelined<br>logic<br>(4 ports) | Area<br>improvement |

|----------------------------|-----------------------------|-----------------------------------------|---------------------------------|---------------------|

| FEC<br>encoder             | 6,185                       | 24,740                                  | 9,619                           | >2.6x               |

| FEC<br>decoder             | 25,969                      | 103,876                                 | 88,755                          | >1.17x              |

| CRC<br>Encoder/<br>decoder | 17,887                      | 71,548                                  | 28,082                          | >2.5x               |

## Thank You!