# Highly Scalable Vertical Bypass RRAM (VB-RRAM) for 3D V-NAND Memory

<u>Geonhui Han</u><sup>1</sup>, Youngdong Kim<sup>1</sup>, Jaeseon Kim<sup>1</sup>, Dongmin Kim<sup>1</sup>, Yoori Seo<sup>1</sup>, Chuljun Lee<sup>1</sup>, Jinmyung Choi<sup>2</sup>, Jinwoo Lee<sup>2</sup>, Dongho Ahn<sup>2</sup>, Sechung Oh<sup>2</sup>, Donghwa Lee<sup>2</sup>, and Hyunsang Hwang<sup>1</sup>

- Department of Material Science and Engineering, Pohang University of Science and Technology (POSTECH), Republic of Korea

- <sup>2</sup> Advanced Process Development Team 2, Samsung Electronics, Republic of Korea

- Introduction

- Feasibility of bypass reading in planar structure

- Vertical integration for V-NAND operation

- Memory characteristics of the VB-RRAM

- Interface resistance (R<sub>int</sub>) issue in the VB-RRAM

- Conclusion

## High scalability of the RRAM for V-NAND

✓ Charge based Flash memory

Charge spreading

✓ Non-charge based RRAM

10<sup>5</sup>

> 10 years

endurance

Retention

$10^6 \sim 10^{12}$

> 10 years

scaling > same nanofilament > better performance scaling > less electrons > performance degrade Retention <10nm Cycling Reliability [Crossbar] V-RRAM **RRAM** Flash VNAND Cell area <4F<sup>2</sup> if 3D <4F<sup>2</sup> if 3D Bit Line Half Pitch (F<sub>VC</sub>) Bit Line Half Pitch (F<sub>p</sub>) = Gate + 3-layers CTF + 1-Poly Ch./Space = 2-Electrodes + Single ReRAM stack Multi-bit Channel Switching material < 20 nm < 10 nm Scalability Electrode (~ 60 nm) (direct tunneling (~ 30 nm) CTF stack limited > 5 nm) Voltage > 10 V < 3 V(~ 20 nm) 70% thinner WL ~ 10us < 10 ns speed Short channel effect WL leakage Vertical coupling Energy/bit ~ 100pJ ~ 0.1 pJ WL

[LETI memory workshop 2012]

✓ RRAM is gaining interest as a potential alternative to flash memory

30% lower

✓ RRAM: High scalability, low voltage, stable endurance, and low power consumption

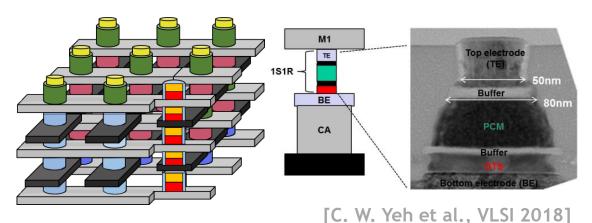

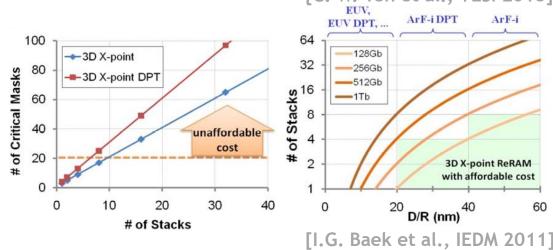

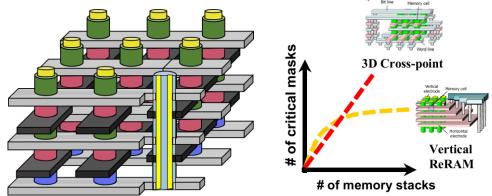

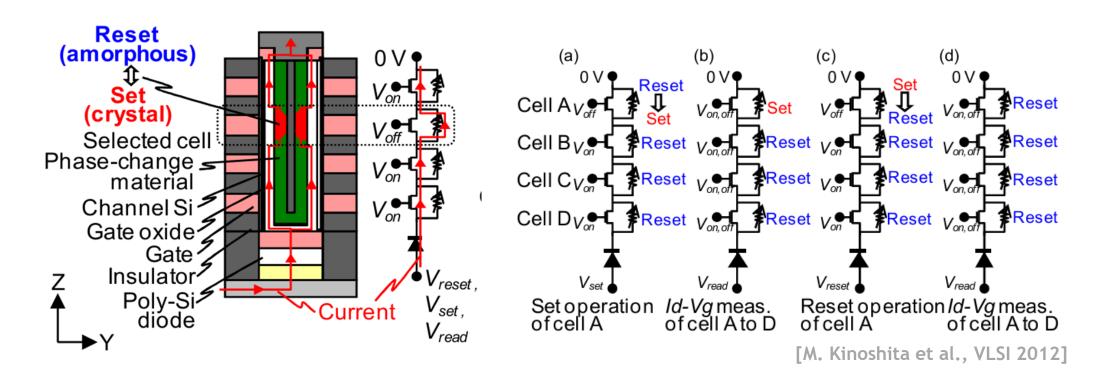

#### Limitation of conventional 3D vertical RRAM

✓ Cross-point array (3D X-RRAM)

Good performance but high costs

(Complex fabrication / process)

✓ Vertical RRAM (V-RRAM)

[I.G. Baek et al., IEDM 2012]

[Q. Luo et al., IEDM 2015]

Low costs but poor performance (Requirements of selector integration)

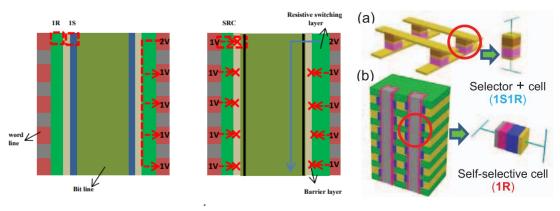

## V-NAND compatible structure (bypass memory)

- ✓ Bypass memory can be a promising candidate for the V-NAND memory

- ✓ Bypass memory utilizes the switching layer as memory and transistor as selector.

- ✓ Excellent memory characteristics & low costs can be achieved in bypass memory.

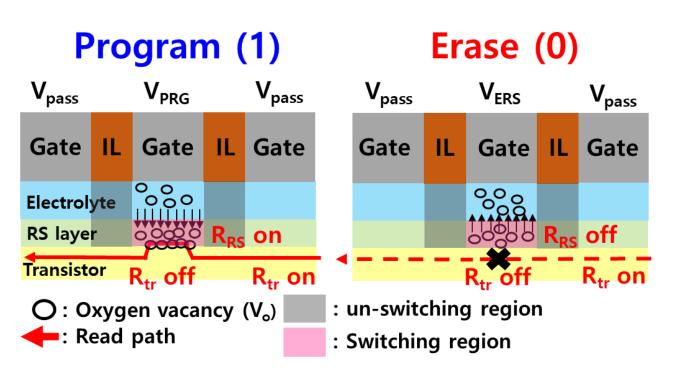

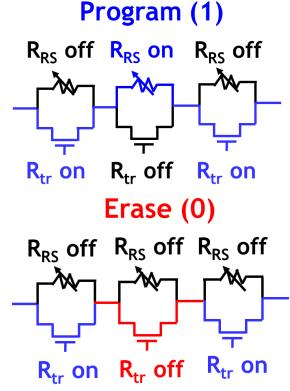

## Concept of V-NAND compatible bypass RRAM

\* RS layer: Resistive switching layer

- ✓ For the first time, we proposed bypass RRAM using interface switching RRAM

- ✓ Bypass RRAM operates through bypass reading between the RS and Tr layer

- $\checkmark$  RS states can be varied depending on the  $V_o$  concentration by PRG / ERS voltage

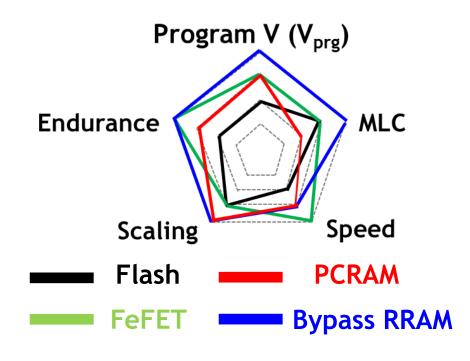

## Advantages of the bypass RRAM for V-NAND

|                | V <sub>prg</sub> Endurance |   | Speed | MLC Scalability |   |

|----------------|----------------------------|---|-------|-----------------|---|

| Flash          | X                          | X | X     | 0               | Δ |

| FeFET          | Δ                          | 0 | 0     | X               | X |

| PCRAM          | X                          | Δ | 0     | X               | 0 |

| Bypass<br>RRAM | 0                          | 0 | Δ     | 0               | 0 |

$O: Good \Delta: Medium X: Bad$

- ✓ Bypass RRAM holds potential as a promising candidate for NVM applications.

- ✓ Compared to other memory, bypass RRAM has high scalability and MLC operation.

- Introduction

- Feasibility of bypass reading in planar structure

- Vertical integration for V-NAND operation

- Memory characteristics of the VB-RRAM

- Interface resistance (R<sub>int</sub>) issue in the VB-RRAM

- Conclusion

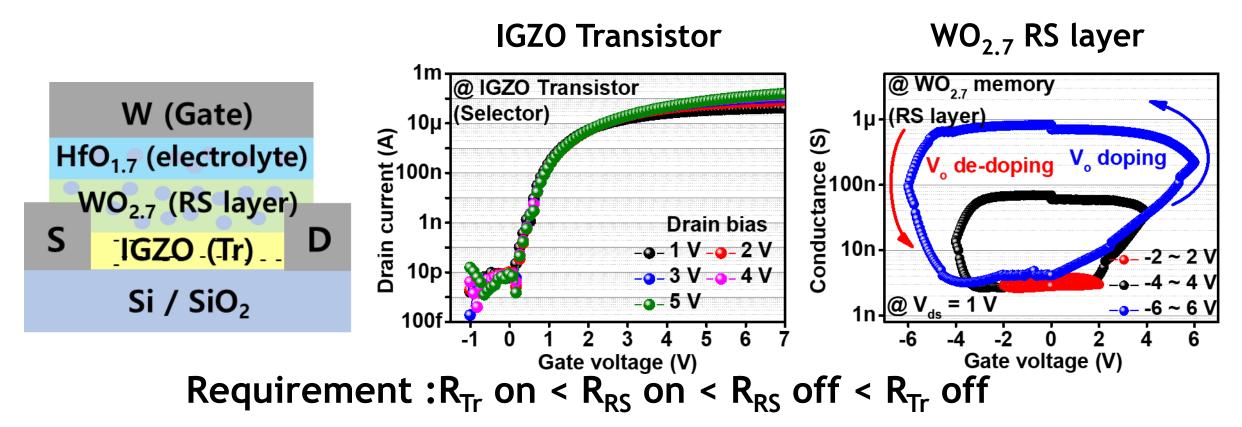

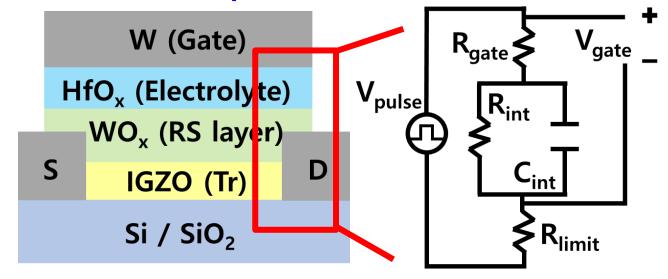

## Fabrication of bypass RRAM in planar structure

- ✓ Selector : IGZO based Tr layer for high on/off ratio  $(10^4 \sim 10^{11} \,\Omega)$

- ✓ Memory: WO<sub>2,7</sub> based RS layer for multi-bit operation (> 4 bit)

- ✓ We integrated the  $WO_{2.7}$  RS layer (memory) to the IGZO Tr (selector) for bypass RRAM

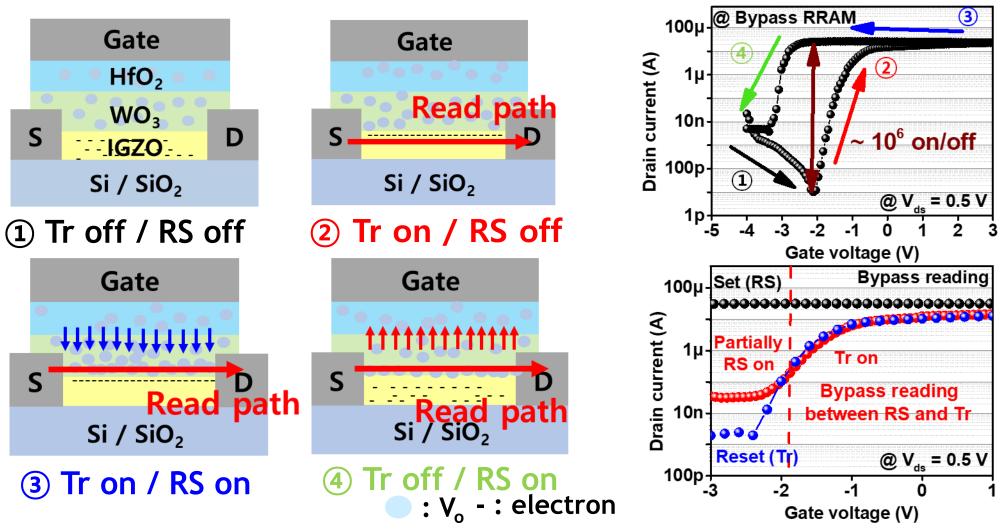

## Feasibility of bypass reading in planar structure

✓ We confirmed the bypass reading depending on RS states in the bypass RRAM

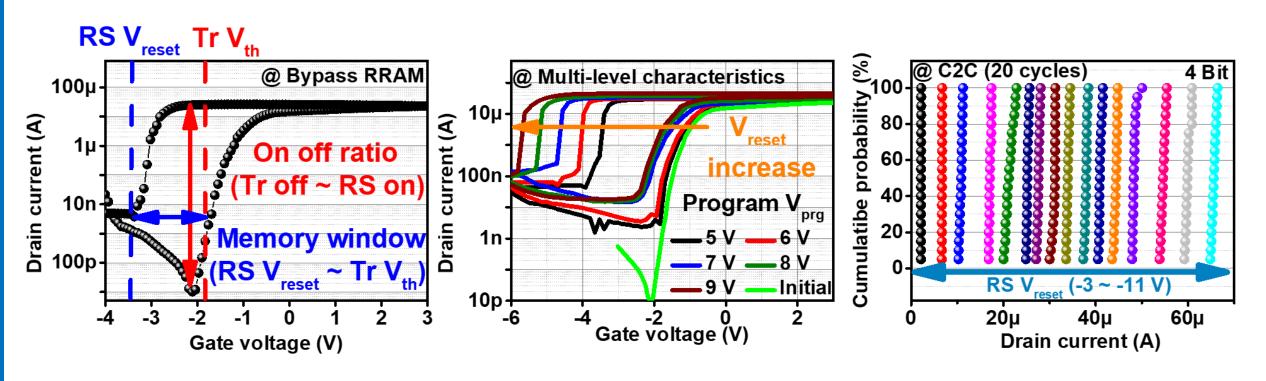

## MLC in bypass RRAM for high-density memory

- ✓ Memory window (MW) : RS V<sub>reset</sub> ~ Tr V<sub>th</sub>

- ✓ Analog switching of RS layer induce the MLC operation

- ✓ We achieved the 8 V MW and 4-bit operation for high-density memory.

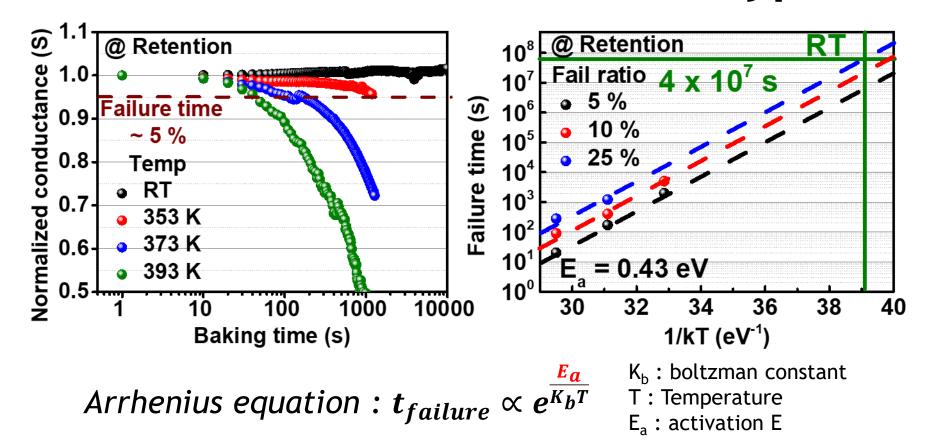

## Retention characteristics of the bypass RRAM

- ✓ We evaluated the failure time (retention) at various temperature

- ✓ We obtained the 1-year retention at 25 % fail ratio by extracted  $E_a$  (0.43 eV)

- ✓ Retention can be improved by increasing E<sub>a</sub> through the diffusion barrier

- Introduction

- Feasibility of bypass reading in planar structure

- Vertical integration for V-NAND operation

- Memory characteristics of the VB-RRAM

- Interface resistance (R<sub>int</sub>) issue in the VB-RRAM

- Conclusion

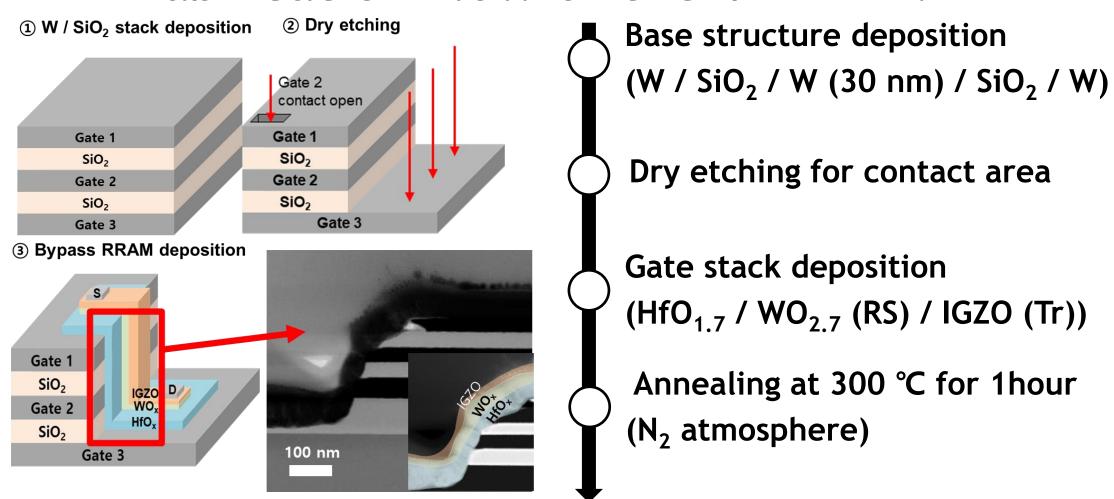

#### Fabrication flow of the VB-RRAM

- ✓ We integrated the bypass RRAM to the vertical structure for V-NAND operation

- ✓ We utilized the 30 nm W (switching area) and 50 nm SiO<sub>2</sub> (IL layer) for the VB-RRAM

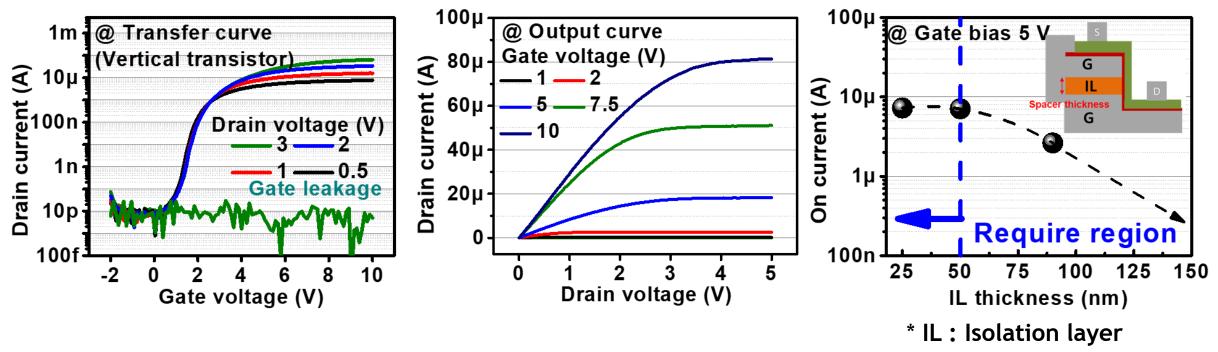

## Optimization of IL thickness for VB-RRAM

- ✓ Without IL, we obtained high I<sub>on</sub> (> 10 uA) in vertical IGZO transistor

- ✓ If the IL is too thick (> 50 nm),  $I_{on}$  of transistor decreases abruptly

- ✓ IL thickness should be below the 50 nm for the high I<sub>on</sub> of the transistor

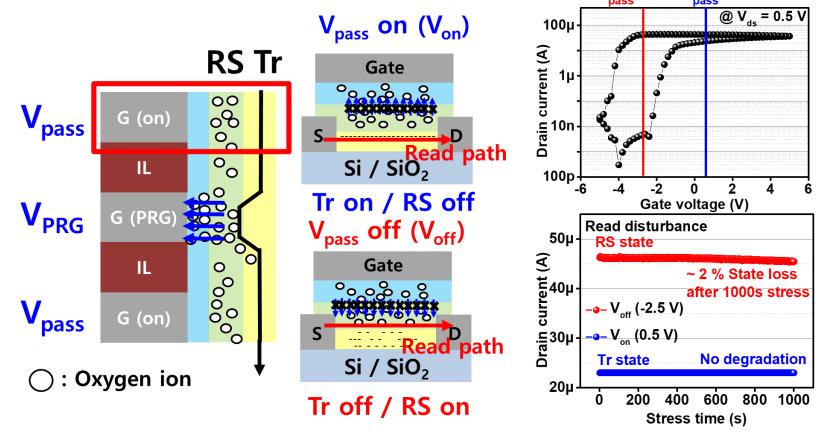

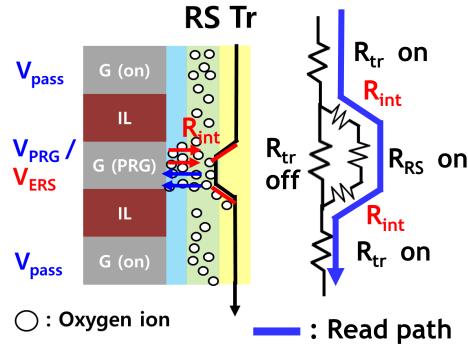

## Read disturbance issues in VB-RRAM

- ✓ In VB-RRAM, read disturbance should be considered (unselected cell)

- $\checkmark$  We applied  $V_{pass}$  on (0.5 V) and  $V_{pass}$  off (-2.5 V) during 1000s stress

- ✓ Only 2 % state loss of RS states occurs while the Tr is tuned off

- Introduction

- Feasibility of bypass reading in planar structure

- Vertical integration for V-NAND operation

- Memory characteristics of the VB-RRAM

- Interface resistance (R<sub>int</sub>) issue in the VB-RRAM

- Conclusion

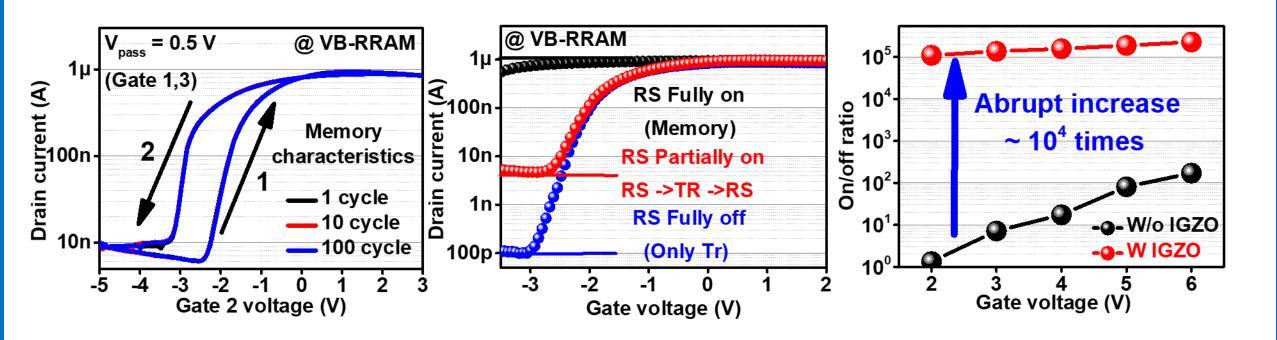

## Memory characteristics of the VB-RRAM (1)

- ✓ VB-RRAM also shows the counter-clockwise hysteresis (memory characteristics)

- ✓ We demonstrated the bypass reading in VB-RRAM depending on the RS states

- √ On/off ratio (> 10<sup>5</sup>) increase abruptly owing to the low off current of IGZO Tr

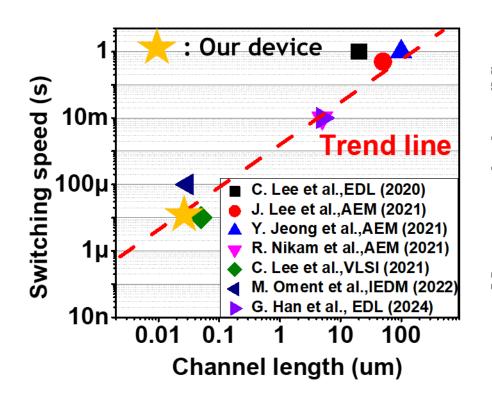

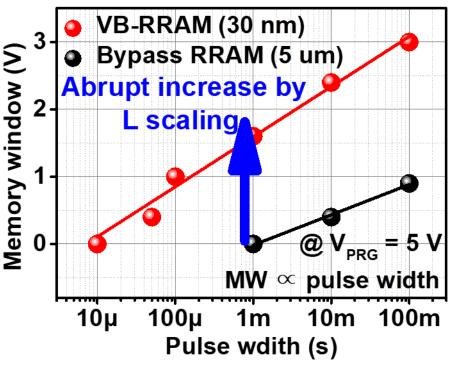

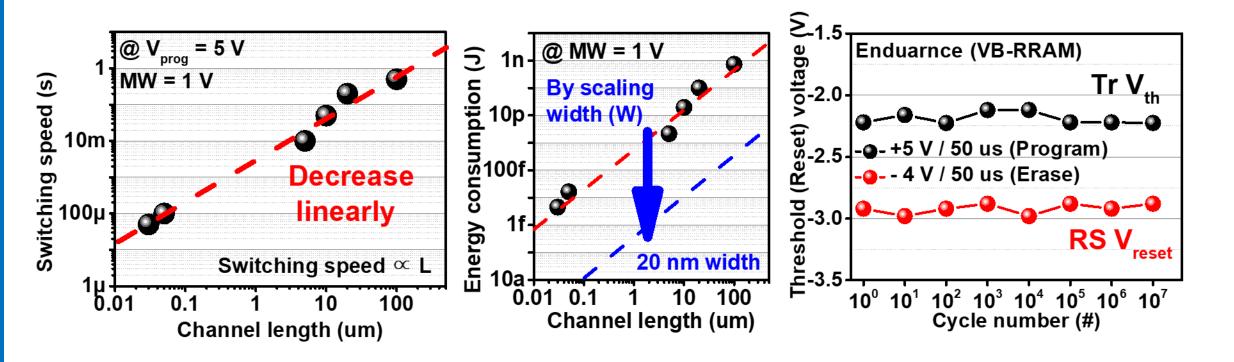

## Improved switching speed by area scaling

\* ECRAM: Electrochemical RAM

- ✓ In conventional, Ion based ECRAM has area dependence of switching speed

- ✓ As channel length decreases, MW and switching speed are improved in VB-RRA.

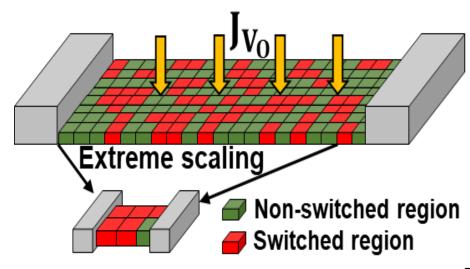

## Origin of area dependence in VB-RRAM

✓ Non-uniform ion injection

$$j_{ion} = 2cizieavoe^{-Ea/kbT} \sinh(\frac{z_i eaE}{k_b T})$$

a = Jump distance

C<sub>i</sub> = Concentration

$v_0$  = Jump frequency

$E_a$  = Activation E

**K**<sub>b</sub> = Boltzman constant

T = Temperature

✓ Interface cap issues in VB-RRAM

$$t_{switch} \propto R_{limit} * C_{int} (C_{int} \propto A)$$

$R_{\text{gate}}$ : Resistance of gate stack

$R_{int}$ : Resistance of interface in gate stack  $C_{int}$ : Interface capacitance in gate stack

R<sub>limit</sub>: External resistance

- ✓ As the channel length decreases, probability of uniform ion injection increases

- ✓ Also, C<sub>int</sub> can be reason of the slow switching speed in the um channel length

## Memory characteristics of the VB-RRAM (2)

- ✓ VB-RRAM achieved 1 V MW with 50 us pulse width (30 nm channel length)

- ✓ Low power consumption (~5 fJ) was also obtained in VB-RRAM

- ✓ With 50 us pulse width, VB-RRAM has excellent endurance (> 10<sup>7</sup> cycles) for V-NAND

- Introduction

- Feasibility of bypass reading in planar structure

- Vertical integration for V-NAND operation

- Memory characteristics of the VB-RRAM

- Interface resistance (R<sub>int</sub>) issue in the VB-RRAM

- Conclusion

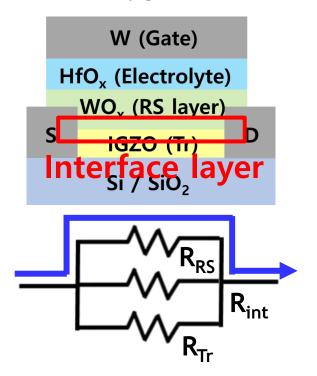

## Interface resistance issues (R<sub>int</sub>) in the VB-RRAM

<TEM image>

W (Gate)

W (Gate)

HfO<sub>x</sub> (Electrolyte)

WO<sub>x</sub> (RS)

iGZO (Tr)

20 nm Interface layer

Planar Bypass RRAM

**Vertical Bypass RRAM**

Requirements:  $2 R_{tr}$  on  $+2 R_{int} < R_{RS}$  on \*  $R_{int}$  = Resistance of the interface layer

- ✓ Compared to the planar structure, interface layer (IL) issues occurred in VB-RRAM

- ✓ During the bypass reading, resistance of IL (R<sub>int</sub>) can disturb the RS reading

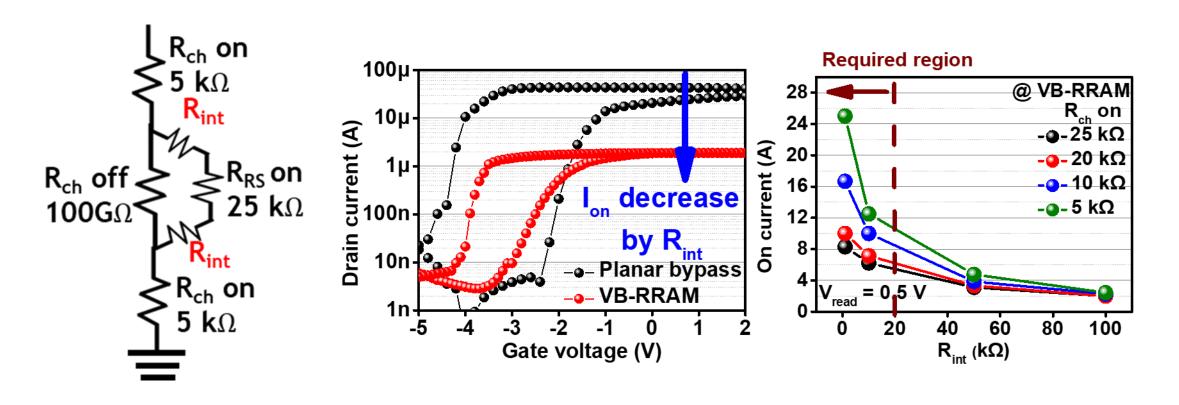

## Interface resistance issues (R<sub>int</sub>) in the VB-RRAM

- $\checkmark$  I<sub>on</sub> is decreased at VB-RRAM compared to planar bypass RRAM due to R<sub>int</sub>

- $\checkmark$  We extracted the R<sub>int</sub> as 100 k $\Omega$  by I<sub>on</sub> of the VB-RRAM

- $\checkmark$  R<sub>int</sub> should be reduced below the 20 k $\Omega$  (R<sub>RS</sub> on) for accurate reading of RS states

## Origin of the interface layer in VB-RRAM

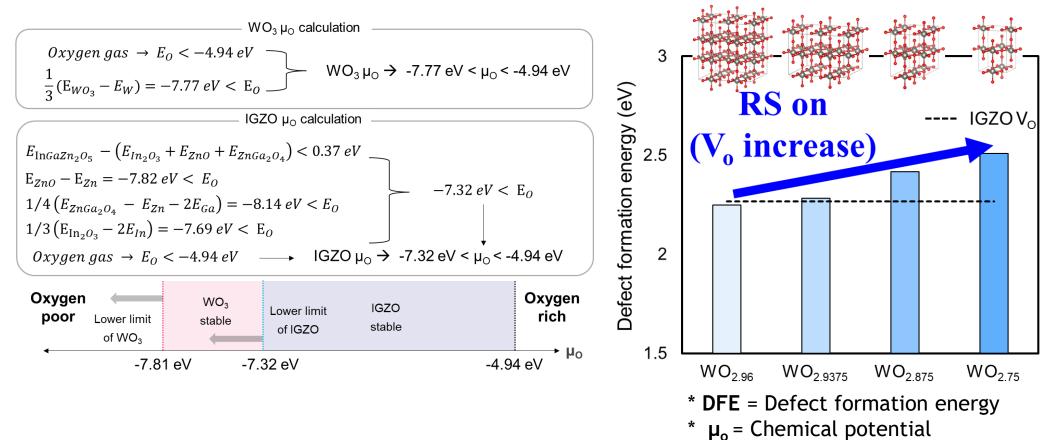

- $\checkmark$  Difference of  $\mu_0$  and DFE can induce the interface layer (IL) between tr and RS layer

- ✓ WO<sub>3</sub> layer is more stable than IGZO transistor based on  $\mu_o$  and DFE

- ✓ After integration, WO<sub>y</sub> IL can be formed between RS and Tr layer

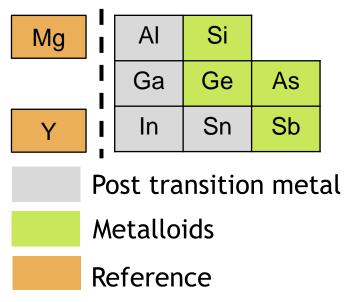

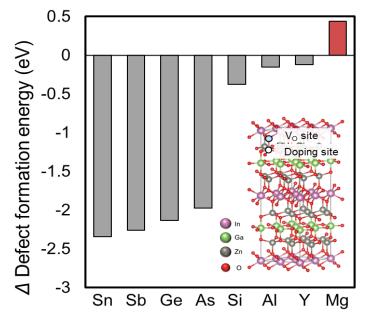

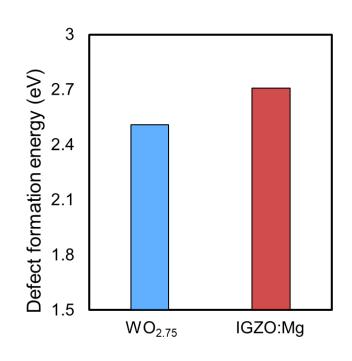

## Mg:IGZO based transistor for low Rint

Various dopants for IGZO

- ✓ Among various dopants, Mg can be a promising candidate for reducing the IL

- ✓ Difference of DFE between WO<sub>2,7</sub> and Mg doped IGZO is only 0.2 eV

- ✓ R<sub>int</sub> can be decreased by Mg doping to the IGZO transistor by reduced IL issue

- Introduction

- Feasibility of bypass reading in planar structure

- Vertical integration for V-NAND operation

- Memory characteristics of the VB-RRAM

- Interface resistance (R<sub>int</sub>) issue in the VB-RRAM

- Conclusion

## Comparison table of V-NAND type memory

|                | Flash [1]   | PCRAM [2]              | PCRAM [3]              | FeFET [4]               | Our work                 |

|----------------|-------------|------------------------|------------------------|-------------------------|--------------------------|

| Mechanism      | Charge trap | Phase change           | Phase change           | Polarization            | Electrochemical reaction |

| $V_{prog}$     | 20 V        | 10 V                   | 20 V                   | 3 V                     | < 5 V                    |

| Speed          | 100 us      | -                      | 0.6 us                 | 1 us                    | 50 us                    |

| On/off<br>(MW) | 10⁵ (5.6 V) | 10                     | 100                    | 10 <sup>4</sup> (2.5 V) | 10 <sup>6</sup> (> 5 V)  |

| Endurance      | 104         | <b>10</b> <sup>6</sup> | <b>10</b> <sup>5</sup> | <b>10</b> <sup>8</sup>  | 10 <sup>7</sup>          |

| MLC            | > 4 bit     | 1 bit                  | 1 bit                  | 2 bit                   | > 4 bit                  |

- √ High scalability (~ 30 nm)

- ✓ Low voltage operation (< 5 V)

</p>

- ✓ Reasonable speed (~ 50 us)

- √ High on/off ratio (> 10<sup>6</sup>)

- ✓ Stable endurance (> 10<sup>7</sup>)

- ✓ MLC operation (> 4 bit)

```

[1] J. Jang, et al., VLSI (2009) [2] S. Morita et al., VLSI (2011) [3] W. Choi et al., ACS Appl. Mater (2023) [4] M. Kim et al., Sci. Adv (2021)

```

- ✓ We demonstrated the feasibility of interface switching RRAM-based V-NAND

- ✓ VB-RRAM shows the excellent memory characteristics compared to other memories

## Summary

- Excellent memory characteristics of the bypass RRAM

- Bypass reading between the RS and Tr depending on the resistance  $(R_{tr} \text{ on } < R_{RS} \text{ on } < R_{RS} \text{ off } < R_{tr} \text{ off})$

- Low voltage (< 5 V), Stable endurance (> 10<sup>7</sup> cycles), reasonable speed (~ 50 us)

- High scalability (~ 30 nm) and 4-bit operation for high-density memory

- V-NAND integration issues

- Isolation layer should be below the 50 nm for high I<sub>on</sub> (> 10 uA)

- Almost no read disturbance issues (~ 2 % state loss)

- Remain issues in VB-RRAM

- $R_{int}$  between RS and Tr should be reduced for accurate reading of RS states (2  $R_{tr}$  + 2  $R_{int}$  <  $R_{RS}$  on)

- Mg: IGZO can be a promising candidate for the low R<sub>int</sub> with WO<sub>3</sub> based RS layer

## Thank you for your attention

Acknowledgement: This work was supported by the Samsung Electronics Co., LTD (IO211115-09118-01)