# Low Latency Wide IO DRAM Specification

Date: 2022/05/03

# **Revision History**

| Revision | Date       | Description                            |

|----------|------------|----------------------------------------|

| 0.0      | 05/03/2022 | First version for target specification |

# **Contents**

| 1. General Description                                                             | 5   |

|------------------------------------------------------------------------------------|-----|

| 1.1. Key Feature List                                                              | 5   |

| 1.2. Comparison between LPDDR4X and LPDDR5                                         | 6   |

| 1.3. Command Set                                                                   |     |

|                                                                                    |     |

| 2. Die Outline                                                                     | 8   |

| 2.1. Block Diagram                                                                 | 8   |

| 2.2. Die Floor Plan                                                                | 8   |

| 2.3. Bump Map                                                                      | g   |

| 2.4. Pad Layout Requirements                                                       |     |

| 2.5. Alignment Mark, Scribe Lane and Seal Ring Requirements                        |     |

|                                                                                    |     |

| 3. Pad Definition and Description                                                  | 12  |

| 3.1. Pin Definition                                                                | 12  |

| 4 Functional Description                                                           | 4.4 |

| 4. Functional Description                                                          |     |

| 4.1. State Diagram                                                                 |     |

| 4.2. Multi-Channel and Slice Operation                                             | 14  |

| 4.3. Power-up, Initialization, Power-off Procedures                                | 15  |

| 4.4. Half DQ Mode                                                                  | 15  |

| 4.5. Mode Register Assignment Table                                                | 15  |

| 4.6. Detailed Mode Register Settings                                               |     |

| 4.6.1. MR0 Register information – TBD                                              |     |

| 4.6.2. MR1 Register information – Read Preamble                                    |     |

| 4.6.3. MR2 Register information – RL/WL Offset, Early CS                           |     |

| 4.6.4. MR3 Register information – STU, Operating Speed, tRCW offset                |     |

| 4.6.5. MR4 Register information – Refresh rate, TUF                                |     |

| 4.6.6. MR5 Register information – Manufacturer ID                                  |     |

| 4.6.7. MR6 Register information – Revision ID 1                                    |     |

| 4.6.8. MR7 Register information – Revision ID 2                                    |     |

| 4.6.9. MR8 Register information – Type, Density, IO width                          |     |

| 4.6.11. MR10 Register information – Veridor Specific rest wode                     |     |

| 4.6.12. MR11 Register information – DS, PPR-Ch, PPRE, CBT, RPT, Write leveling     |     |

| 4.6.13. MR12 Register information – Vref CA setting                                |     |

| 4.6.14. MR14 Register information – Vref DQ setting                                |     |

| 4.6.15. MR15 Register information – DQS Oscillator count start                     |     |

| 4.6.16. MR16 Register information – DQS Oscillator count stop                      |     |

| 4.6.17. MR17 Register information – DQS interval timer setting                     |     |

| 4.6.18. MR18 Register information – DQS Oscillator count LSBLSB                    |     |

| 4.6.19. MR19 Register information – DQS Oscillator count MSB (Same as LPDDR4)      |     |

| 4.6.20. MR24 Register information – MAC Value (# of Active Counter for Row hammer) |     |

| 4.6.21. MR47 Register information – PPR Resource                                   |     |

| 5. Command Definition and AC Timing                                                | 24  |

| <u> </u>                                                                           |     |

| 5.1. Command Truth Table                                                           |     |

| 5.2. Read                                                                          | 25  |

| 5.2.1.                   | . Read Post-amble to Pre-amble Merge Behavior        | 26 |

|--------------------------|------------------------------------------------------|----|

| 5.3.<br>5.3.1.<br>5.3.2. | 3                                                    | 27 |

| 5.4.                     | Mode Register Read                                   | 28 |

| 5.5.                     | Mode Register Write                                  |    |

| 5.6.                     | Refresh                                              |    |

| 5.6.1.                   |                                                      |    |

| 5.6.1.                   | 1. Sub-bank Based Special Row Hammer Refresh Command | 30 |

| 5.6.1.                   | Bank Based Special Row Hammer Refresh Command        | 30 |

| 5.7.                     | Power Down Entry and Exit                            | 30 |

| 5.8.                     | Self Refresh Entry and Exit                          | 31 |

| 5.9.                     | Early CS Mode Option                                 | 31 |

| 5.10.                    | Input Clock Frequency Change                         | 32 |

| 5.11.                    | Training and Calibration Requirements                | 32 |

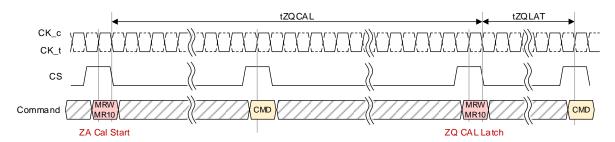

| 5.11.1                   | 1. ZQ Calibration                                    | 32 |

| 5.11.2                   | 3/                                                   |    |

| 5.11.3                   | 3                                                    |    |

| 5.11.4<br>5.11.5         | 3                                                    |    |

|                          | Timing Parameters                                    |    |

|                          | •                                                    |    |

| 5.13.                    | Command to Command Timing Rules                      | 38 |

| 6. A                     | Absolute Maximum DC Rating                           | 39 |

| 7. A                     | AC and DC Operating Condition                        | 40 |

| 7.1.                     | Supply Voltage Requirements                          | 40 |

| 7.2.                     | Temperature Requirements                             | 40 |

| 7.3.                     | Signaling Requirements                               | 40 |

| 7.4.                     | ESD and Latch-up Requirements                        | 41 |

| 8. IE                    | DD Specification Parameters                          | 43 |

| 8.1.                     | Low Latency Wide IO IDD Definitions                  | 43 |

| 8.2.                     | IDD spec table                                       | 43 |

| 9. To                    | estability and Repair Requirements                   | 46 |

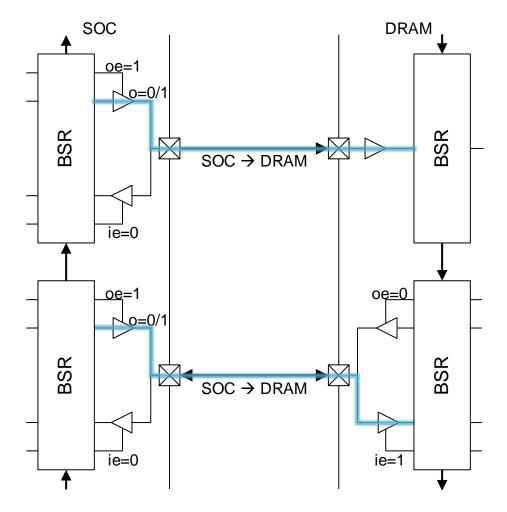

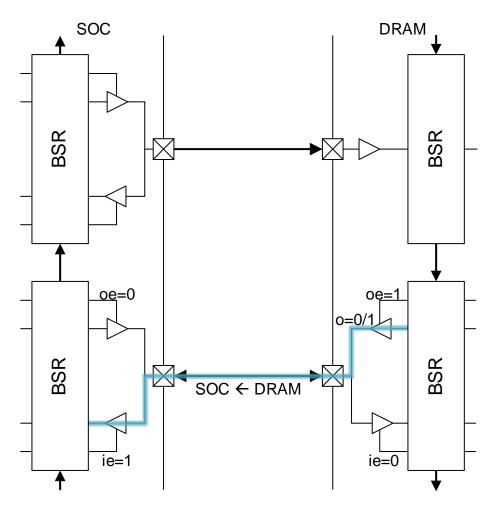

| 9.1.                     | Boundary Scan                                        | 46 |

| 9.2.                     | Direct Access                                        | 47 |

| 9.3.                     | Lane Repair                                          | 48 |

| 9.3.1.                   |                                                      |    |

| 9.4.                     | Post Package Repair (PPR)                            | 49 |

| 9.4.1.                   |                                                      |    |

| 9.5                      | Production Test                                      | 50 |

# 1. General Description

# 1.1. Key Feature List

- Total capacity: 256MB

- Total peak bandwidth: 128GB/sec (x512)

- Four independent channels per die

- Two data slices per channel

- Dedicated DQ pins per data slice

- Shared command pins among data slices in same channel

- Both command and data running at DDR data rate of 2Gbps

- Different data slices may execute overlapping Read or Write commands

- Eight banks per data slice:

- Page size: 1KB

- Prefetch size: 64B every 4tCK

- Supports 64B, 128B, and 256B data bursts on the fly

- · Refresh:

- Auto refresh is per data slice only. All banks in a given data slice are refreshed with one refresh command

- Self-refresh is per channel

- Optimized refresh scheme supported

- Closed-page operation without any explicit activate/precharge commands

- On-die ECC support w/ 16B data sectors and one-bit correct scheme

- Masked-Write support with 16B minimum granularity (no internal RMW for ECC)

- Small memory tiles compared to commodity DRAM

- Early CS mode option to improve idle power

# 1.2. Comparison between LPDDR4X and LPDDR5

Table 1.1. Comparison between LPDDR4X and LPDDR5

|                  | Items                                               | LPDDR4X                                   | LPDDR5                                                     | Low Latency Wide IO<br>DRAM               |

|------------------|-----------------------------------------------------|-------------------------------------------|------------------------------------------------------------|-------------------------------------------|

|                  | CLK scheme                                          | Differential (CLK/CLKB)                   | Differential (CLK/CLKB)                                    | Differential (CLK/CLKB)                   |

|                  | Data scheme                                         | DDR Single ended,<br>Bi-Directional       | DDR Single ended,<br>Bi-Directional                        | DDR Single ended,<br>Bi-Directional       |

|                  | DQS scheme                                          | Differential (DQS/DQSB)<br>Bi-Directional | Support RDQS<br>Differential(RDQS/RDQSB)<br>Bi-Directional | Differential (DQS/DQSB)<br>Bi-Directional |

|                  | ADD / CMD scheme                                    | SDR                                       | DDR                                                        | DDR                                       |

|                  | Operation Policy<br>(Opened page /<br>Clopsed page) | Support both                              | Support both                                               | Support closed page only                  |

|                  | I/O Interface                                       | LVSTL_0.6V                                | LVSTL_0.5V                                                 | LVSTL_0.6V                                |

|                  | Burst Length                                        | 16, 32 (OTF)                              | 16, 32 (OTF)                                               | 8, 16, 32 (OTF)                           |

| Feature          | Burst Type                                          | Sequential                                | Sequential                                                 | Sequential                                |

|                  | # of Bank per Ch.                                   | 8                                         | 8 or 16B or 4B/4BG                                         | 16<br>(8bank per data slice)              |

|                  | Organization per Ch.                                | x8, x16                                   | x8, x16                                                    | x64, x128<br>(x32, x64 per data slice)    |

|                  | Data Mask                                           | Support (Masked Write)                    | Support (Masked Write)                                     | Support (Masked Write)                    |

|                  | Refresh mode                                        | Auto / Self Refresh                       | Auto / Self Refresh                                        | Auto / Self Refresh                       |

|                  | DBI                                                 | Support                                   | Support                                                    | N/A                                       |

|                  | Speed bin [Mbps]                                    | 3200/3733/4266                            | 5500/6400                                                  | 2000                                      |

|                  | tRC                                                 | 63ns<br>(tRC, Act to Act delay)           | 63ns<br>(tRC, Act to Act delay)                            | 32ns<br>(tRCW,<br>ACT-WR-PRE-ACT)         |

| Cassial Function | ZQ Calibration                                      | Support                                   | Support                                                    | Support                                   |

| Special Function | Write Leveling                                      | Support                                   | Support                                                    | Support                                   |

|                  | VDD1 [V]                                            | 1.70 ~ 1.95                               | 1.70 ~ 1.95                                                | 1.70 ~ 1.95                               |

| Dower Supply     | VDD2/2H [V]                                         | 1.06 ~ 1.17                               | 1.01 ~ 1.12                                                | 0.97 ~ 1.07                               |

| Power Supply     | VDD2L [V]                                           | N/A                                       | 0.87 ~ 0.97                                                | N/A                                       |

|                  | VDDQ [V]                                            | 0.57 ~ 0.65                               | 0.47 ~ 0.55                                                | 0.57 ~ 0.65                               |

# 1.3. Command Set

Command set resembles LPDDR style command definition. A key exception is that no activation or precharge commands are used. They will be implicit within Read and Write commands (closed page memory operation only). All configuration and test mode settings are handled via MRW (Mode Register Write) and MRR (Mode Register Read). Table 1.2 shows a list of all valid Low Latency Wide IO commands.

**Table 1.2. Command List**

| Command    | Description                                                                                            |

|------------|--------------------------------------------------------------------------------------------------------|

| Read       | Active page; Reads 64B/128B/256B on the fly; Precharges page                                           |

| Write      | Active page; Writes 64B/128B/256B on the fly; Precharges page Same command supports both masked writes |

| Refresh    | Refreshes all banks in a given data slice (no per bank refresh supported)                              |

| MRW        | Writes a given Mode Register                                                                           |

| MRR        | Reads a given Mode Register                                                                            |

| SREF Entry | Enters channel into self-refresh state                                                                 |

| PD Entry   | Enters channel into power-down state                                                                   |

| PD or SREF Exit | Exits channel from either SREF or PD state |

|-----------------|--------------------------------------------|

| NOP             | Explicit NOP command                       |

# 2. Die Outline

# 2.1. Block Diagram

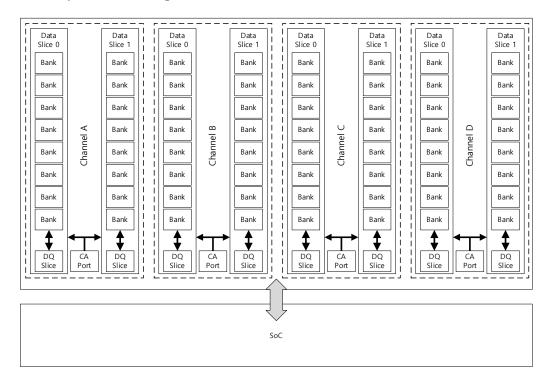

Figure 2.1. Conceptual Block Diagram

## 2.2. Die Floor Plan

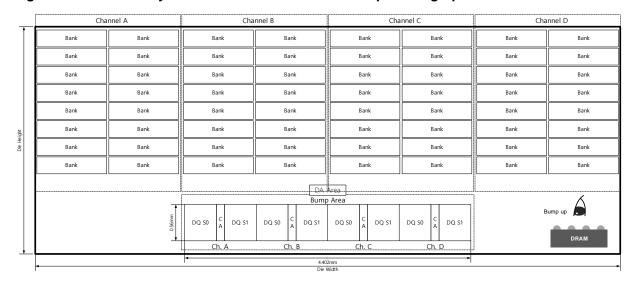

Figure 2.2 shows the outline of Low Latency Wide IO die and arrangement of channels, slices, and banks. Overall physical dimensions of Low Latency Wide IO die shall comply with width and height as specified in this figure. Die width and height are defined by seal ring stepping distance. Bump area for Low Latency Wide IO to SoC connections has a shoreline of 4.402mm and is located at the bottom center of the die.

Figure 2.2. Low Latency Wide IO Die Floor Plan with Bumps Facing Up

SAMSUNG

Figure 2.3. Low Latency Wide IO Power Bump Regions with Bumps Facing Up

TBD

# 2.3. Bump Map

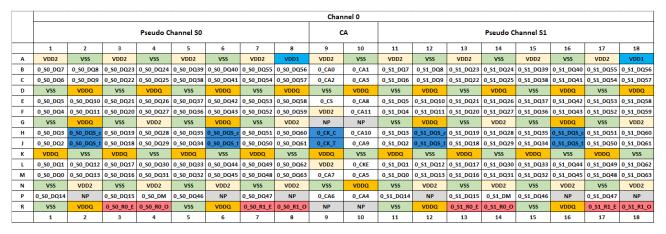

Figure 2.4 shows the physical requirement for the bump area. Bumps shall have vertical pitch of 40um and a horizontal pitch of 62um and follow the bump to signal assignments as specified in this figure. Additional testing pins that contain boundary scan and direct access are shown in Figure 2.5. Bump coordinates for all Low Latency Wide IO bumps are listed in Appendix A. No additional bumps permitted unless listed. Bump coordinates are hard requirements with the exception of power and ground groups as defined in Figure 2.3.

Figure 2.4. Bump map for Low Latency Wide IO Channel0 with bumps facing up

Figure 2.5. Bump map for Low Latency Wide IO Direct Access (DA) Port

TBD (Around 50pcs pin will be placed)

# 2.4. Pad Layout Requirements

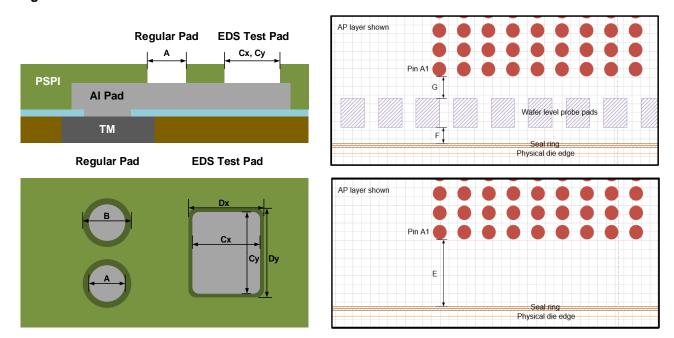

All pad designs shall follow the same basic cell structure, an example of which is shown in Figure 2.6. PIQ layer shall always cover AP sidewall. AP CD for regular pads is a recommended value only. Proper sizing of AP CD inline with the hard requirement for PIQ CD shall be ensured.

For wafer level probing, dedicated probe pads are required with its own separate pad design. The sizing of these pads is decided by vendor requirements and the CD in table xx is provided for reference. Minimum spacing between AP, seal ring, probe pad are illustrated in Figure 2.6 and listed in Table 2.1.

Figure 2.6. Pad Rules

**Table 2.1. AP Pad Requirements**

| No | Description                                                      | Label   | Rule          | Comments           |

|----|------------------------------------------------------------------|---------|---------------|--------------------|

| 1  | Circular shape of PIQ (polymer) opening is required              |         |               |                    |

| 2  | PIQ CD (Regular pad)                                             | А       | = 17um        | Hard requirement   |

| 3  | AP CD (Regular pad)                                              | В       | = 28um        | Recommendation     |

| 4  | PIQ CD (Dedicated probe pad)                                     | Cx / Cy | = 50um x 60um | Vendor requirement |

| 5  | AP CD (Dedicated probe pad)                                      | Dx / Dy | =56um x 66um  | Vendor requirement |

| 6  | All PIQ openings on die must be included in mcm design file      |         |               |                    |

| 7  | Pads dedicated for probing must be identified in mcm design file |         |               |                    |

| 8  | AP spacing to seal ring                                          | E       | >= 55um       |                    |

| 9  | Probe pad spacing to seal ring (AP layer)                        | F       | >= 20um       |                    |

| 10 | Bump PIQ edge spacing to probe pad PIQ edge                      | G       | >= 36um       |                    |

# 2.5. Alignment Mark, Scribe Lane and Seal Ring Requirements

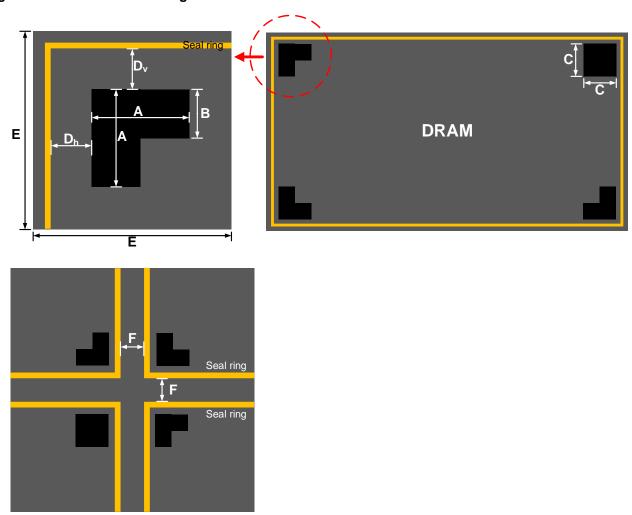

Recommended alignment mark reference design is provided in Figure 2.7.

Table 2.2. Scribe and Alignment Mark Rules

| No | Description                                                                  | Label | Rule    |

|----|------------------------------------------------------------------------------|-------|---------|

| 1  | L-Shaped alignment marks on 3 die corners and square mark on the last corner |       |         |

| 2  | L-Shaped alignment mark dimension A                                          | А     | = 62 um |

| 3  | L-Shaped alignment mark dimension B                                          | В     | = 30um  |

| 4  | Rectangle alignment mark dimension                                           | С     | = 62um  |

**SAMSUNG**

| 5 | Alignment mark to seal ring distance                            |   | = 43um vertical,<br>= 49um horizontal |

|---|-----------------------------------------------------------------|---|---------------------------------------|

| 6 | Routing forbidden zone for L-shaped alignment mark (all layers) | E | = 80um                                |

| 7 | Scribe lane width (from seal ring to seal ring)                 | F | >= 70um (TBD)                         |

Figure 2.7. Scribe Lane and Alignment Mark Rules

# 3. Pad Definition and Description

# 3.1. Pin Definition

Low Latency Wide IO die has a total of 684 signal pins. There are four groups of 162 pins per each channel as detailed in Table 3.1.

Table 3.1. Signal pins per each channel

| Port           | Pin Name                         | Туре  | Description                                                                                             | Count | Nominal<br>Signaling Levels |

|----------------|----------------------------------|-------|---------------------------------------------------------------------------------------------------------|-------|-----------------------------|

|                | CK_t, CK_c                       | Input | Differential Clock                                                                                      | 2     | VSS - VDDQ                  |

| Command        | CKE                              | Input | Clock Enable, SDR signal                                                                                | 1     | VSS - VDD2                  |

| Command        | CS                               | Input | Chip Select, SDR signal                                                                                 | 1     | VSS - VDDQ                  |

|                | CA [11:0]                        | Input | Command/Address inputs, DDR signal                                                                      | 12    | VSS - VDDQ                  |

|                | DQ_S0 [63:0]                     | Ю     | Bidirectional DDR data input/output pins.<br>BL=8, 16, 32 for 64B, 128B, 256B accesses<br>respectively. | 64    | VSS - VDDQ                  |

| Data Slice 0   | DQS_S0_t [1:0]<br>DQS_S0_c [1:0] | Ю     | Bidirectional differential DQ Strobes. One pair of differential strobes per every 32 DQ's.              | 4     | VSS - VDDQ                  |

|                | DM_S0                            | Ю     | Data Mask Input. DDR. No DBI supported. DM pin shall be in DQS_S0_t/c[0] domain.                        | 1     | VSS - VDDQ                  |

|                | RDQE_S0 [1:0]<br>RDQO_S0 [1:0]   | Ю     | Redundant DQ's. One pair of even/odd redundant DQ's per each DQS domain.                                | 4     | VSS - VDDQ                  |

|                | DQ_S1 [63:0]                     | Ю     | Bidirectional DDR data input/output pins.<br>BL=8, 16, 32 for 64B, 128B, 256B accesses<br>respectively. | 64    | VSS - VDDQ                  |

| Data Slice 1   | DQS_S1_t [1:0]<br>DQS_S1_c [1:0] | Ю     | Bidirectional differential DQ Strobes.  One pair of differential strobes per every 32 DQ's.             | 4     | VSS - VDDQ                  |

|                | DM_S1                            | Ю     | Data Mask Input. DDR. No DBI supported. DM pin shall be in DQS_S1_t/c[0] domain.                        | 1     | VSS - VDDQ                  |

|                | RDQE_S1 [1:0]<br>RDQO_S1 [1:0]   | Ю     | Redundant DQ's. One pair of even/odd redundant DQ's per each DQS domain.                                | 4     | VSS - VDDQ                  |

| Total signal c | ount per channel :               | 162   |                                                                                                         |       |                             |

There are 36 signal pins shared among all four channels as detailed in Table 3.2.

Table 3.2. Signal pins shared among channels

| Pin Name  | Туре      | Description                                                                                                                                                                                                              | Count | Nominal<br>Signaling Levels |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------|

| Reset_n   | Input     | RESET: When asserted LOW, the RESET_n signal resets all channels of the die                                                                                                                                              | 1     | VSS - VDD2                  |

| ZQ        | Reference | Calibration Reference: Used to calibrate the output drive strength. There is one ZQ pin per die. The ZQ pin shall be connected to VDDQ through a $240\Omega \pm 1\%$ resistor.                                           | 1     | Analog                      |

| SEN [1:0] | Input     | Boundary Scan Enable: When SEN[0] is enabled, only boundary scan operations is available through all channels. SEN[0] must be routed directly to external package I/O pads to allow un-buffered access to these signals. | 2     | VSS - VDD2                  |

| SSH       | Input     | Boundary Scan Shift: There is one SSH provided to channels. SSH must be routed directly to external package I/O pads to allow unbuffered access to these signals.                                                        | 1     | VSS - VDD2                  |

| SDI                                                                         | Input                                        | Boundary Scan Serial Data In:<br>There is one SDI provided to input the boundary scan data.<br>SDI must be routed directly to external package I/O pads to<br>allow un-buffered access to these signals.                                                                                                                                            | 1   | VSS - VDDQ |  |  |

|-----------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|--|--|

| SCK                                                                         | Input                                        | Boundary Scan Clock: There is one SCK provided to all channels. SCK must be routed directly to external package I/O pads to allow unbuffered access to these signals.                                                                                                                                                                               | 1   | VSS - VDDQ |  |  |

| SDO                                                                         | Output                                       | Boundary Scan output: There is one SDO to check serialized output data. SDO must be routed directly to external package I/O pads to allow un-buffered access to these signals.                                                                                                                                                                      | 1   | VSS - VDDQ |  |  |

| DAEN_DA<br>Reset_n_DA<br>CKE_DA                                             | Input                                        | Direct Access: These I/O pins provide digital direct access to internal                                                                                                                                                                                                                                                                             | 3   | VSS - VDD2 |  |  |

| CA_DA[11:0]<br>CK_t/c_DA<br>CS_DA[3:0]<br>DQS_t/c_DA<br>DQ_DA[3:0]<br>DM_DA | Ю                                            | DRAM core signals for test/debug purposes. DA pins must be routed directly to external package I/O pads to allow unbuffered access to these signals. When DAEN input is High and DA port is enabled, all non-DA signal pins are in high-Z and must be ignored including Reset_n. When DAEN is Low, All other DA pins must be in high-Z and ignored. | TBD | VSS - VDDQ |  |  |

| Total signal cou                                                            | Total signal count (excluding power/GND): 36 |                                                                                                                                                                                                                                                                                                                                                     |     |            |  |  |

# Table 3.3. Power and ground pins shared among channels (Target)

| Pin Name       | Туре                            | Description          | Count |  |  |  |  |

|----------------|---------------------------------|----------------------|-------|--|--|--|--|

| VDD1           | Power                           |                      | 18    |  |  |  |  |

| VDD2           | Power                           | Power supplies       | 119   |  |  |  |  |

| VDDQ           | Power                           |                      | 128   |  |  |  |  |

| VSS            | GND                             | Ground and IO Ground | 225   |  |  |  |  |

| Total power/GN | Total power/GND pin count : 490 |                      |       |  |  |  |  |

# 4. Functional Description

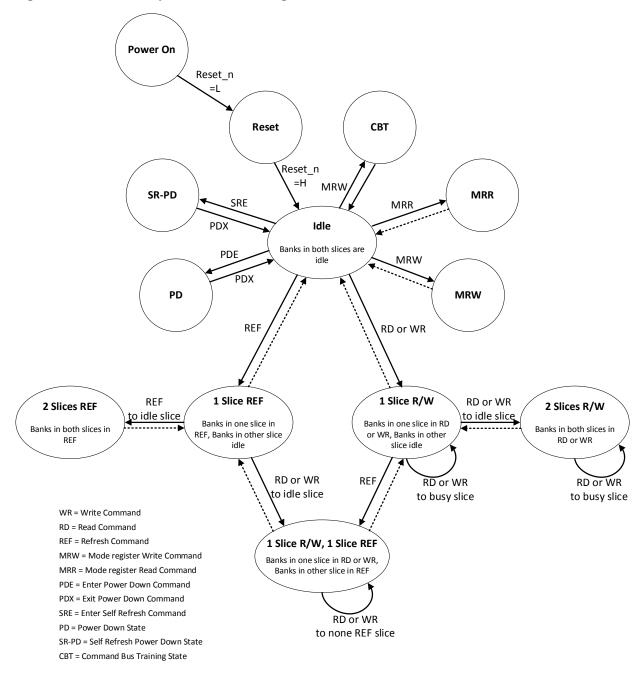

# 4.1. State Diagram

Figure 4.1. Low Latency Wide IO State Diagram for Each Channel

# 4.2. Multi-Channel and Slice Operation

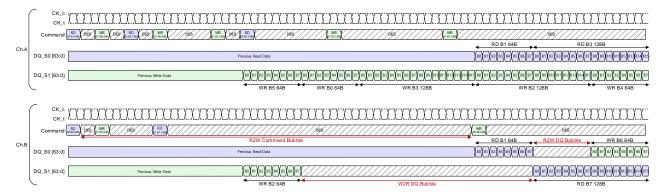

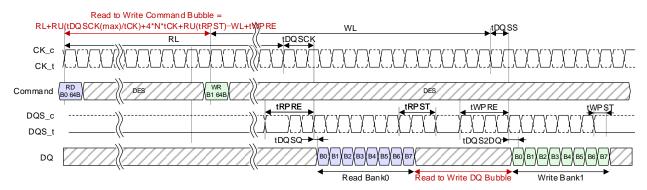

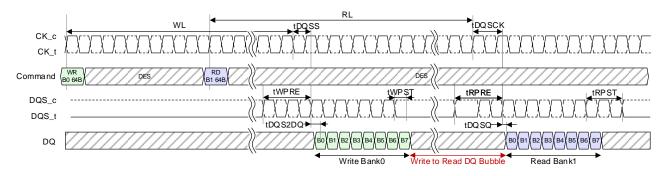

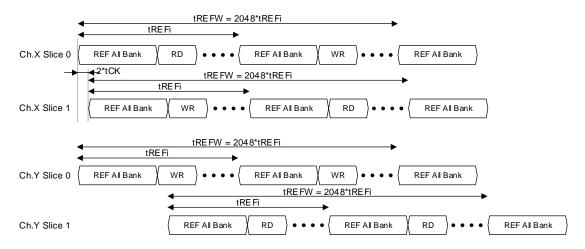

Figure 4.2 shows an example timing diagram for how two data slices in two channels can operate. Each command requires one cycle and commands to different slices in the same channel can be issued every other cycle. Although not strictly required, a round robin approach can be used to issue a new transaction to the same data slice every four clock cycles as shown. In this example, Channel A data slice 0 performs a sequence of gapless read transactions of varying burst lengths (64B and 128B). Concurrently, channel A data slice 1 performs a sequence of gapless write transactions of varying burst lengths. Channel B slice

SAMSUNG

0 in this example switches from performing read transactions to performing write transactions. Such a read to write turn results in a "R2W command bubble" in command sequence and a "R2W DQ bubble" as shown. Channel B data slice 1 in this example performs a write to read turn switching from write transactions to read transactions. Such a write to read turn results in a "W2R DQ bubble" on channel B slice 1 DQ bus as shown. More detailed timing diagrams and timing specifications are described in Section Chapter 5, Command Definition and AC Timing.

Figure 4.2. Example of multi-channel and multi-slice operation

# 4.3. Power-up, Initialization, Power-off Procedures

Low Latency Wide IO power-up, initialization, and power-off procedures shall follow the same exact requirements as LPDDR4, which are specified in Section 3.3 of JEDEC document JESD209-4A.

## 4.4. Half DQ Mode

**TBD**

# 4.5. Mode Register Assignment Table

**Table 4.1. Mode Register Assignments**

| MR #<br>MA[5:0] | Access | OP7   | OP6                       | OP5            | OP4         | OP3             | OP2        | OP1          | OP0         |  |

|-----------------|--------|-------|---------------------------|----------------|-------------|-----------------|------------|--------------|-------------|--|

| 00, 0x00        | R      |       |                           |                | RF          | -U              |            |              |             |  |

| 01, 0x01        | W      |       |                           |                | RFU         |                 |            |              | RD-PRE      |  |

| 02, 0x02        | W      | Early | Early CS                  |                |             | WL offset       |            | RL offset    |             |  |

| 03, 0x03        | W      |       | RFU                       |                |             | Operating Speed |            |              | tRCW offset |  |

| 04, 0x04        | R      | TUF   | TUF RFU                   |                |             |                 |            | Refresh rate |             |  |

| 05, 0x05        | R      |       |                           |                | Manufa      | cture ID        |            |              |             |  |

| 06, 0x06        | R      |       |                           |                | Revision    | on ID 1         |            |              |             |  |

| 07, 0x07        | R      |       |                           |                | Revision    | on ID 2         |            |              |             |  |

| 08, 0x08        | R      | IO v  | IO width                  |                |             | Density         |            | Ту           | /pe         |  |

| 09, 0x09        | W      |       | Vendor Specific Test Mode |                |             |                 |            |              |             |  |

| 10, 0x0A        | W      |       | ZQ Ca                     | ıl start : 0xF | F, ZQ Cal L | atch : 0xBB     | , ZQ Reset | : 0xC3       |             |  |

| 11, 0x0B | W   | WR<br>Leveling | RPT                                     | СВТ | PPRE      | LRE         | RFU  | Driver Strength |

|----------|-----|----------------|-----------------------------------------|-----|-----------|-------------|------|-----------------|

| 12, 0x0C | R/W | RF             | -U                                      |     |           | Vref        | (CA) |                 |

| 13, 0x0D | N/A |                |                                         |     | RF        | -U          |      |                 |

| 14, 0x0E | R/W | RF             | -U                                      |     |           | Vref        | (DQ) |                 |

| 15, 0x0F | W   |                | DQS OSC Count Start                     |     |           |             |      |                 |

| 16, 0x10 | W   |                | DQS OSC Count Stop                      |     |           |             |      |                 |

| 17, 0x11 | W   |                | DQS OSC Interval Timer Run Time Setting |     |           |             |      |                 |

| 18, 0x12 | R   |                | DQS OSC Count - LSB                     |     |           |             |      |                 |

| 19, 0x13 | R   |                |                                         |     | DQS OSC ( | Count - MSE | 3    |                 |

| 20:23    | N/A |                |                                         |     | RF        | -U          |      |                 |

| 24, 0x18 | R   |                | RFU                                     |     | ARH       | IM - MAC V  | alue | RFU             |

| 25:37    | N/A |                | RFU                                     |     |           |             |      |                 |

| 38:46    | N/A | Do Not Use     |                                         |     |           |             |      |                 |

| 47, 0x2F | R   |                |                                         |     | PPR Re    | esource     |      |                 |

# 4.6. Detailed Mode Register Settings

# 4.6.1. MR0 Register information - TBD

**TBD**

# 4.6.2. MR1 Register information – Read Preamble

Table 4.2. MR1 Register information - Read Preamble

| Function                       | Register<br>Type | Operand | Data                                                                                         | Notes |

|--------------------------------|------------------|---------|----------------------------------------------------------------------------------------------|-------|

| RD-PRE<br>(Read Preamble Type) | W                | OP[0]   | 0b0: Read Preamble = 1 tCK static + 1 tCK toggle (Default) 0b1: Read Preamble = 2 tCK toggle | 1     |

Notes:

# 4.6.3. MR2 Register information - RL/WL Offset, Early CS

Table 4.3. MR2 Register information - RL/WL Offset, Early CS Mode

| Function                      | Register<br>Type | Operand | Data                                                                                                                         | Notes |

|-------------------------------|------------------|---------|------------------------------------------------------------------------------------------------------------------------------|-------|

| RL and MRR_RL offset at 2Gbps | - W              | OP[2:0] | 0b000: Reserved<br>0b001: RL offset = 0 (Default)<br>0b010: RL offset = +1<br>0b011: RL offset = +2<br>0b100: RL offset = +4 | 1,2   |

| WL offset<br>at 2Gbps         |                  | OP[5:3] | 0b000: Reserved<br>0b001: WL offset = 0 (Default)<br>0b010: WL offset = +1<br>0b011: WL offset = +2<br>0b100: WL offset = +3 | 1,2   |

<sup>1.</sup> For Read operations this bit must be set to select between a "static" pre-amble and a mixed Preamble.

| Early CS | OP[7:6] | 0b00: Disable Early CS (Default) 0b01: Enable Early CS – 4tCK ahead 0b10: Enable Early CS – TBD tCK ahead 0b11: Reserved |  |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------|--|

|----------|---------|--------------------------------------------------------------------------------------------------------------------------|--|

#### Notes:

- 1. MRR\_RL, RL and WL offset specified in MR2 OP[2:0] and OP[5:3] are only available to apply at the full speed (2Gbps). For other operating speeds (1Gbps, 100Mbps), only the default value applies regardless of offset setting.

- 2. RL and WL can be modified with the setting of MR2 OP[2:0] and OP[5:3]. For example, if MR2 OP[2:0] = 0b100 and MR2 OP[5:3] = 0b010, RL and WL will be set to 28 and 9, respectively. (RL is 28 = 26 + 2, WL is 9 = 9 + 0)

# 4.6.4. MR3 Register information – STU, Operating Speed, tRCW offset

Table 4.4. MR3 Register information - STU, Operating Speed, tRCW offset

| Function           | Register<br>Type | Operand | Data                                                                                                                                | Notes |

|--------------------|------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------|-------|

| tRCW offset enable |                  | OP[1:0] | 0b00: tRCW = 28ns + BL/2 (Default)<br>0b01: tRCW = 28ns + BL/2 + 8ns<br>All Others : Reserved                                       | 2     |

| Operating Speed    | W                | OP[4:2] | 0b000: <100Mbps, WL = 2, RL = 8 (Default)<br>0b001: 1Gbps, WL = 4, RL = 14<br>0b010: 2Gbps, WL = 9, RL = 26<br>All Others: Reserved | 1     |

#### Notes:

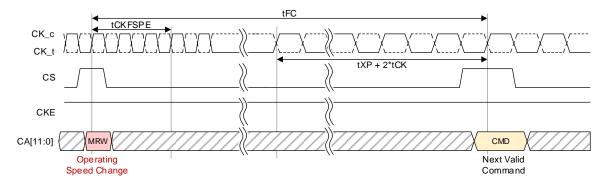

- 1. When OP[4:2] = 0b000, Low Latency Wide IO only allows to operate below 100Mbps. It is required to modify MR3 setting to proper state prior to operate the other speeds. For example, set MR3 OP[4:2]=0b010 prior to operate Low Latency Wide IO with 2Gbps.

- 2. MR for tRCW offset is an optional feature to make sure the core write operation at the cold temperature. Offset value must be <=8ns and the temperature range for which OP[1:0]=0b01 is required must be < 0C.

## 4.6.5. MR4 Register information – Refresh rate, TUF

Table 4.5. MR4 Register information - Refresh rate, TUF

| Function                            | Register<br>Type | Operand | Data                                                                                                                                                                                                                                           | Notes           |

|-------------------------------------|------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Refresh Rate                        | R                | OP[2:0] | 0b000: DRAM Low temperature operating limit exceeded 0b001: 4x refresh, Below 0'C 0b010: 4x refresh, Above 0'C 0b011: 2x refresh 0b100: 1x refresh 0b100: 1x refresh 0b101: 0.5x refresh 0b111: DRAM High temperature operating limit exceeded | 1,2,3,4,<br>7,8 |

| TUF<br>(Temperature Update<br>Flag) |                  | OP[7]   | 0b0: No change in OP[2:0] since last MR4 read (default) 0b1: Change in OP[2:0] since last MR4 read                                                                                                                                             | 5,6,7           |

#### Notes:

- 1. The refresh rate for each MR4 OP[2:0] setting applies to tREFI and tREFW. OP[2:0]=0b100 corresponds to a device temperature of 85 °C. Other values require either a longer (2x, 4x) refresh interval at lower temperatures, or a shorter (0.5x, 0.25x) refresh interval at higher temperatures. If OP[2:0]=0b101 or higher, the device temperature is greater than 85 °C.

- 2. At higher temperatures (>85 °C), no AC timing de-rating shall be required.

- 3. DRAM vendor may or may not report all of the possible settings over the operating temperature range

of the device. The vendor guarantees that their device will work at any temperature within the range using the refresh interval requested by their device.

- 4. The device may not operate properly when OP[2:0]=0b000 or 0b111.

- 5. When OP[7]=1, the refresh rate reported in OP[2:0] has changed since the last MR4 read. Once MR4 OP[2:0] is read, OP[7] will be reset to '0'.

- 6. OP[7] = 0 at power-up. OP[2:0] bits are valid after initialization sequence(Te).

- 7. See the section on "temperature Sensor" for information on the recommended frequency of reading MR4.

- 8. When MR4 OP[2:0]=0b001, Low Latency Wide IO controller can enable tRCW offset feature when necessary by setting MR3 OP[1:0]=0b01.

## 4.6.6. MR5 Register information – Manufacturer ID

# Table 4.6. MR5 Register information - Manufacturer ID

| Function        | Register<br>Type | Operand | Data                 | Notes |

|-----------------|------------------|---------|----------------------|-------|

| Manufacturer ID | R                | OP[7:0} | 0b00000001 : Samsung |       |

# 4.6.7. MR6 Register information – Revision ID 1

Table 4.7. MR6 Register information – Revision ID 1

| Function      | Register<br>Type | Operand | Data                   | Notes |

|---------------|------------------|---------|------------------------|-------|

| Revision ID 1 | R                | OP[7:0] | 0b00001000 : I-version | 1     |

#### Notes:

1. MR6 is vendor specific.

## 4.6.8. MR7 Register information – Revision ID 2

Table 4.8. MR7 Register information – Revision ID 2

| Function      | Register<br>Type | Operand | Data                   | Notes |

|---------------|------------------|---------|------------------------|-------|

| Revision ID 2 | R                | OP[7:0] | 0b00000000 : A-version | 1     |

#### Notes:

1. MR7 is vendor specific.

# 4.6.9. MR8 Register information – Type, Density, IO width.

Table 4.9. MR8 Register information - Type, Density, IO width

| Function | Register<br>Type | Operand | Data                                                                           | Notes |

|----------|------------------|---------|--------------------------------------------------------------------------------|-------|

| Туре     |                  | OP[1:0] | 0b00: Low Latency Wide IO 4ch, SDRAM<br>All Others: Reserved                   |       |

| Density  | R                | OP[5:2] | 0b000: 2Gb (per die)<br>All Others : Reserved                                  |       |

| IO width |                  | OP[7:6] | 0b000: x128 (per channel)<br>0b001: x64 (per channel)<br>All Others : Reserved |       |

## 4.6.10. MR9 Register information – Vendor Specific Test Mode

TBD

## 4.6.11. MR10 Register information – ZQ Calibration code

Table 4.10. MR10 Register information - ZQ Calibration code

| Function            | Register<br>Type | Operand | Data                                                                                   | Notes   |

|---------------------|------------------|---------|----------------------------------------------------------------------------------------|---------|

| ZQ Calibration Code | W                | OP[7:0] | 0xFF: ZQ Calibration Start<br>0xBB: ZQ Latch<br>0xC3: ZQ Reset<br>All Others: Reserved | 1,2,3,4 |

#### Notes:

- 1. Host processor shall not write MR10 with "Reserved" values.

- 2. Low Latency Wide IO devices shall ignore calibration command when a "Reserved" value is written into MR10.

- 3. If ZQ is connected to VDDQ through RZQ, the ZQ calibration Start MRW Command is supported. If ZQ is connected to VSSQ, the device may operate with the calibration command, but ZQ calibration commands are ignored. In both cases, the ZQ connection shall not change after power is applied to the device.

# 4.6.12. MR11 Register information – DS, PPR-Ch, PPRE, CBT, RPT, Write leveling

Table 4.11. MR11 Register information - DS, PPR-Ch, PPRE, CBT, RPT, Write leveling

| Function                         | Register<br>Type | Operand | Data                                                                                       | Notes |

|----------------------------------|------------------|---------|--------------------------------------------------------------------------------------------|-------|

| DS (Driver Strength)             |                  | OP[1:0] | 0b00: RFU<br>0b01: RZQ / 2 : 1200hm<br>0b10: RZQ / 3 : 800hm – (Default)<br>0b11: Reserved | 1     |

| LRE<br>(Lane Repair Entry)       |                  | OP[3]   | 0b0: Normal Operation (Default) 0b1: Lane Repair Mode                                      |       |

| PPRE (PPR Entry)                 | w                | OP[4]   | 0b0: Normal Operation (Default)<br>0b1: PPR Mode                                           |       |

| CBT<br>Command Bus Training      | VV               | OP[5]   | 0b0: Disabled (Default) 0b1: Enabled                                                       |       |

| RPT<br>Read Preamble<br>Training |                  | OP[6]   | 0b0: Disabled (Default) 0b1: Enabled                                                       |       |

| WR Leveling                      |                  | OP[7]   | 0b0: Disabled (Default)<br>0b1: Enabled                                                    | 2     |

#### Notes:

- 1. All values are "typical". The actual value after calibration will be within the specified tolerance for a given voltage and temperature.

- 2. After a MRW to set the Write Leveling Enable bit (OP[7]=0b1), Low Latency Wide IO device remains in the MRW state until another MRW command clears the bit (OP[7]=0b0). No other commands are allowed until the Write Leveling Enable bit is cleared.

# 4.6.13. MR12 Register information - Vref CA setting

Low Latency Wide IO shall support independent Vref CA generator for each channel so that channels can be independently trained. The Vref settling time to +/- 1% accuracy shall be less than 1us for >5-step

change and less than 200ns for 1-step change.

Table 4.12. MR12 Register information - Vref CA setting

| Operand | Vref Values (%         | % of VD | DDQ)     |     |           |     |            |     |

|---------|------------------------|---------|----------|-----|-----------|-----|------------|-----|

|         | 0b 000000              | 16%     | 0b 10000 | 32% | 0b 100000 | 48% | 0b 110000  | 64% |

|         | 0b 000001              | 17%     | 0b 10001 | 33% | 0b 100001 | 49% | 0b 110001  | 65% |

|         | 0b 000010              | 18%     | 0b 10010 | 34% | 0b 100010 | 50% | 0b 110010  | 66% |

|         | 0b 000011              | 19%     | 0b 10011 | 35% | 0b 100011 | 51% | 0b 110011  | 67% |

|         | 0b 000100              | 20%     | 0b 10100 | 36% | 0b 100100 | 52% | 0b 110100  | 68% |

|         | 0b 000101              | 21%     | 0b 10101 | 37% | 0b 100101 | 53% | 0b 110101  | 69% |

|         | 0b 000110<br>0b 000111 | 22%     | 0b 10110 | 38% | 0b 100110 | 54% | 0b 110110  | 70% |

| ODIE:01 |                        | 23%     | 0b 10111 | 39% | 0b 100111 | 55% | 0b 110111  | 71% |

| OP[5:0] | 0b 001000              | 24%     | 0b 11000 | 40% | 0b 101000 | 56% | 0b 111000  | 72% |

|         | 0b 001001              | 25%     | 0b 11001 | 41% | 0b 101001 | 57% | 0b 111001  | 73% |

|         | 0b 001010              | 26%     | 0b 11010 | 42% | 0b 101010 | 58% |            |     |

|         | 0b 001011              | 27%     | 0b 11011 | 43% | 0b 101011 | 59% |            |     |

|         | 0b 001100              | 28%     | 0b 11100 | 44% | 0b 101100 | 60% | All Others |     |

|         | 0b 001101              | 29%     | 0b 11101 | 45% | 0b 101101 | 61% | Reserved   |     |

|         | 0b 001110              | 30%     | 0b 11110 | 46% | 0b 101110 | 62% |            |     |

|         | 0b 001111              | 31%     | 0b 11111 | 47% | 0b 101111 | 63% |            |     |

# 4.6.14. MR14 Register information - Vref DQ setting

Low Latency Wide IO shall support independent Vref DQ generator for each channel so that channels can be independently trained. The Vref settling time to +/- 1% accuracy shall be less than 1us for >5-step change and less than 200ns for 1-step change.

| Operand | Vref Values (% | 6 of VD | DDQ)     |     |           |     |                        |     |

|---------|----------------|---------|----------|-----|-----------|-----|------------------------|-----|

|         | 0b 000000      | 16%     | 0b 10000 | 32% | 0b 100000 | 48% | 0b 110000              | 64% |

|         | 0b 000001      | 17%     | 0b 10001 | 33% | 0b 100001 | 49% | 0b 110001              | 65% |

|         | 0b 000010      | 18%     | 0b 10010 | 34% | 0b 100010 | 50% | 0b 110010              | 66% |

|         | 0b 000011      | 19%     | 0b 10011 | 35% | 0b 100011 | 51% | 0b 110011              | 67% |

|         | 0b 000100      | 20%     | 0b 10100 | 36% | 0b 100100 | 52% | 0b 110100              | 68% |

|         | 0b 000101      | 21%     | 0b 10101 | 37% | 0b 100101 | 53% | 0b 110101              | 69% |

|         | 0b 000110      | 22%     | 0b 10110 | 38% | 0b 100110 | 54% | 0b 110110              | 70% |

| OP[5:0] | 0b 000111      | 23%     | 0b 10111 | 39% | 0b 100111 | 55% | 0b 110111              | 71% |

|         | 0b 001000      | 24%     | 0b 11000 | 40% | 0b 101000 | 56% | 0b 111000              | 72% |

|         | 0b 001001      | 25%     | 0b 11001 | 41% | 0b 101001 | 57% | 0b 111001              | 73% |

|         | 0b 001010      | 26%     | 0b 11010 | 42% | 0b 101010 | 58% |                        |     |

|         | 0b 001011      | 27%     | 0b 11011 | 43% | 0b 101011 | 59% |                        |     |

|         | 0b 001100      | 28%     | 0b 11100 | 44% | 0b 101100 | 60% | All Others<br>Reserved |     |

|         | 0b 001101      | 29%     | 0b 11101 | 45% | 0b 101101 | 61% |                        |     |

|         | 0b 001110      | 30%     | 0b 11110 | 46% | 0b 101110 | 62% |                        |     |

|  | 0b 001111     | 31%  | 0b 11111 | 47%   | 0b 101111 | 63%    |

|--|---------------|------|----------|-------|-----------|--------|

|  | 00 00 1 1 1 1 | 0.70 | 00       | 11 /0 | 00 101111 | 00 / 0 |

## 4.6.15. MR15 Register information - DQS Oscillator count start

#### Table 4.13. MR15 Register information – DQS Oscillator count start

| Function                      | Register<br>Type | Operand | Data                            | Notes |

|-------------------------------|------------------|---------|---------------------------------|-------|

| DQS Oscillator Count<br>Start | W                | OP[7:0] | 0x01 DQS Oscillator Count Start | 1     |

#### Notes:

## 4.6.16. MR16 Register information – DQS Oscillator count stop

Table 4.14. MR16 Register information - DQS Oscillator count stop

| Function                     | Register<br>Type | Operand | Data                           | Notes |

|------------------------------|------------------|---------|--------------------------------|-------|

| DQS Oscillator Count<br>Stop | W                | OP[7:0] | 0x01 DQS Oscillator Count Stop | 1,2   |

#### Notes

- 1. DQS Oscillator Count Start MRW command (MR15) shall be issued prior to issue DQS Oscillator Count Stop MRW command (MR16).

- 2. Once MR16 is accessed by host, DQS oscillator counter stops to operate. Other than issuing DQS Oscillator Count Stop command or reaching automatic counter stop by MR17, DQS oscillator keeps running to count the DQS clocks.

## 4.6.17. MR17 Register information – DQS interval timer setting

Table 4.15. MR17 Register information – DQS interval timer setting

| Function                   | Register<br>Type | Operand | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Notes |

|----------------------------|------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| DQS interval time run time | W                | OP[7:0] | 0b00000000: DQS interval timer stop via MR16 (default) 0b00000001: DQS interval timer stop automatically at 16th clocks after timer start 0b00000010: DQS interval timer stop automatically at 32th clocks after timer start 0b00000011: DQS interval timer stop automatically at 48h clocks after timer start 0b00000100: DQS interval timer stop automatically at 64th clocks after timer startThru 0b00111111: DQS interval timer stop automatically at (63*16)th clocks after timer start 0b01XXXXXX: DQS interval timer stop automatically at 2048th clocks after timer start 0b10XXXXXX: DQS interval timer stop automatically at 4096th clocks after timer start 0b11XXXXXXX: DQS interval timer stop automatically at 8192th clocks after timer start | 1,2   |

#### Notes:

1. MRW DQS OSC Count Stop command with MR16 stops DQS interval timer in case of MR17 OP[7:0]

<sup>1.</sup> Once MR15 is accessed by host, DQS oscillator counter starts to operate. Other than issuing DQS Oscillator Count Stop command or reaching automatic counter stop by MR17, DQS oscillator keeps running to count the DQS clocks.

- = 00000000B.

- 2. MRW DQS OSC Count Stop command with MR16 is illegal with non-zero values in MR17 OP[7:0].

# 4.6.18. MR18 Register information – DQS Oscillator count LSB

#### Table 4.16. MR18 Register information - DQS Oscillator count LSB

| Function                                          | Register<br>Type | Operand | Data                                | Notes |

|---------------------------------------------------|------------------|---------|-------------------------------------|-------|

| DQS Oscillator<br>(WR Training DQS<br>Oscillator) | R                | OP[7:0] | 0-255 LSB DRAM DQS Oscillator Count | 1,2,3 |

#### Notes:

- 1. MR18 reports the LSB bits of the DRAM DQS oscillator count. The DRAM DQS Oscillator count value is used to train DQS to the DQ data valid window. The value reported by the DRAM in this mode register can be used by the memory controller to periodically adjust the phase of DQS relative to DQ.

- 2. Both MR18 and MR19 must be read (MRR) and combined to get the value of the DQS Oscillator count.

- 3. A MRW DQS OSC Count Stop command (MR16) could be issued to reset the contents of MR18/MR19.

# 4.6.19. MR19 Register information – DQS Oscillator count MSB (Same as LPDDR4)

#### Table 4.17. MR19 Register information - DQS Oscillator count MSB

| Function                                          | Register<br>Type | Operand | Data                                | Notes |

|---------------------------------------------------|------------------|---------|-------------------------------------|-------|

| DQS Oscillator<br>(WR Training DQS<br>Oscillator) | R                | OP[7:0] | 0-255 MSB DRAM DQS Oscillator Count | 1,2,3 |

#### Notes:

- 1. MR19 reports the MSB bits of the DRAM DQS oscillator count. The DRAM DQS Oscillator count value is used to train DQS to the DQ data valid window. The value reported by the DRAM in this mode register can be used by the memory controller to periodically adjust the phase of DQS relative to DQ.

- 2. Both MR18 and MR19 must be read (MRR) and combined to get the value of the DQS Oscillator count.

- 3. A MRW DQS OSC Count Stop command (MR16) could be issued to reset the contents of MR18/MR19.

# 4.6.20. MR24 Register information - MAC Value (# of Active Counter for Row hammer)

# Table 4.18. MR24 Register information – MAC Value (# of Active Counter for Row hammer)

| Function  | Register<br>Type | Operand | Data | Notes |

|-----------|------------------|---------|------|-------|

| MAC Value | R                | OP[4:2] | TBD  |       |

## 4.6.21. MR47 Register information – PPR Resource

MR 47 is a read-only register. Each OP code indicates availability of one of eight PPR resources for the channel of Low Latency Wide IO. Each channel has its own separate MR 47. 0b0 indicates that corresponding PPR resource is not available and 0b1 indicates that PPR resource is available. Mapping the eight PPR resources to banks/slices within channel are as follows:

#### Table 4.19. MR47 Register information - PPR Resource

| MR | Register Type OP[0] | OP[1] | OP[2] | OP[3] | OP[4] | OP[5] | OP[6] | OP[7] | l |

|----|---------------------|-------|-------|-------|-------|-------|-------|-------|---|

|----|---------------------|-------|-------|-------|-------|-------|-------|-------|---|

| MR47 | D | Slice 0   | Slice 0   | Slice 0   | Slice 0   | Slice 1   | Slice 1   | Slice 1   | Slice 1   |  |

|------|---|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|

| WK47 | ĸ | Banks 0,1 | Banks 2,3 | Banks 4,5 | Banks 6,7 | Banks 0,1 | Banks 2,3 | Banks 4,5 | Banks 6,7 |  |

# 5. Command Definition and AC Timing

## 5.1. Command Truth Table

Table 5.1 defines the command truth table for each Low Latency Wide IO channel. Each command takes one clock cycle. CA pins are DDR and are specified at both rising and falling edge of each CK\_t transition. The following notes apply to this table:

- Cells with X represent don't care values. Cells with V indicate valid logic high or low level is OK

- DS specifies the data slice address within channel

- BA0, BA1, and BA2 specify the bank address in a given data slice

- R0 to R10 specify the page (row) address in a given bank

- C0 to C3 specify the column address for a 64B data segment

- BL0 and BL1 specify on the fly burst length as defined in Table 5.2

**Table 5.1. Command Truth Table**

|            |      | SDR Co       | ommand         | Pins | DDR Command Pins |       |       |       |       |       |       |       |       |       |        |        |

|------------|------|--------------|----------------|------|------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|

| Command    | CK t | Ck           | CKE            |      |                  |       |       |       |       |       |       |       |       |       |        |        |

| Command    | CK_t | @CK<br>(N-1) | @<br>CK<br>(N) | cs   | CA[0]            | CA[1] | CA[2] | CA[3] | CA[4] | CA[5] | CA[6] | CA[7] | CA[8] | CA[9] | CA[10] | CA[11] |

| Read       | R    | Н            | Н              | Н    | Н                | Н     | BL0   | BL1   | C0    | C1    | C2    | C3    | DS    | BA0   | BA1    | BA2    |

| Reau       | F    | П            | П              | Х    | R0               | R1    | R2    | R3    | R4    | R5    | R6    | R7    | R8    | R9    | R10    |        |

| Write      | R    | Н            | Н              | Н    | L                | I     | BL0   | BL1   | C0    | C1    | C2    | C3    | DS    | BA0   | BA1    | BA2    |

| vviite     | F    |              | 11             | Х    | R0               | R1    | R2    | R3    | R4    | R5    | R6    | R7    | R8    | R9    | R10    |        |

| Refresh    | R    | Н            | Н              | Н    | Н                | L     | Н     | L     | L     | ٧     |       |       | DS    | ٧     |        |        |

| Kellesii   | F    | 11           | 11             | Х    | V                |       |       |       |       |       |       |       |       |       |        |        |

| Refresh_S  | R R  |              | н н            | Н    | Н                | L     | Н     | Н     | V     |       |       |       | DS    | V     |        |        |

| Kellesii_S | F    | 11           |                | Х    | V                |       |       |       |       |       |       |       |       |       |        |        |

| MRW        | R    | Н            | н              | Н    | Н                | L     | L     | Н     | MA0   | MA1   | MA2   | MA3   | MA4   | MA5   | MA6    | MA7    |

| IVIIXVV    | F    |              |                | Х    | OP0              | OP1   | OP2   | OP3   | OP4   | OP5   | OP6   | OP7   | V     |       |        |        |

| MRR        | R    | Н            | Н              | Н    | Н                | L     | L     | L     | MA0   | MA1   | MA2   | MA3   | MA4   | MA5   | MA6    | MA7    |

| IVIIXIX    | F    |              |                | Х    | V                |       |       |       |       |       |       |       |       |       |        |        |

| NOP        | R    | н            | н              | Н    | L                | L     | L     | L     | V     |       |       |       |       |       |        |        |

| NOI        | F    |              | Н              | Х    | V                |       |       |       |       |       |       |       |       |       |        |        |

| SREF       | R    | Н            | Н              | Н    | Н                | L     | Н     | L     | Н     | V     |       |       |       |       |        |        |

| Entry      | F    | Χ            |                | Х    | V                |       |       |       |       |       |       |       |       |       |        |        |

| PD Entry   | R    | Н            | L              | L    | Х                |       |       |       |       |       |       |       |       |       |        |        |

| 1 D Linuy  | F    | Χ            | _              | Х    | Х                |       |       |       |       |       |       |       |       |       |        |        |

| SREF/PD    | R    | L            | Н              | L    | Х                |       |       |       |       |       |       |       |       |       |        |        |

| Exit       | F    | Χ            |                | Χ    | Х                |       |       |       |       |       |       |       |       |       |        |        |

| DeSelet    | R    | Н            | Н              | L    | V                |       |       |       |       |       |       |       |       |       |        |        |

| (DES)      | F    | 11           | 11             | Х    | V                |       |       |       |       |       |       |       |       |       |        |        |

Table 5.2 shows the truth table for how burst length bits (BL0, BL1) and column address bits (C0, C1, C2, C3) shall define the burst length and burst order. C0 shall be used to determine which 64B data segment is burst in or our first for 128B and 256B Read and Write commands. C1 is don't care for 256B Read and Write commands.

Table 5.2. Burst Length and Burst Order Options Truth Table

|               | Burst Le | ngth Bits |                   | Column A           | ddress Bits |               | Resulting Burst Order |            |         |         |  |

|---------------|----------|-----------|-------------------|--------------------|-------------|---------------|-----------------------|------------|---------|---------|--|

|               | BL1      | BL0       | C0                | C1                 | C2          | C3            | 1st BL8               | 2nd BL8    | 3rd BL8 | 4th BL8 |  |

| 64B (BL=8)    | ı        | Х         |                   | Select 1 of 16     |             |               |                       | 1st 64B NA |         |         |  |

| 04B (BL=0)    | L        | ^         | 64B data segments |                    |             |               | 130 040               | 1 1/7      |         |         |  |

| 130D (DI -16) |          |           | L                 | L Select 1 of 8    |             |               |                       | 2nd 64B    | NA NA   |         |  |

| 128B (BL=16)  | Н        | L         | Н                 | 128B data segments |             |               | 2nd 64B               | 1st 64B    | I NA    |         |  |

|               |          |           | L                 |                    |             | Select 1 of 4 |                       | 2nd 64B    | 3rd 64B | 4th 64B |  |

| 256B (BL=32)  | Н        | Н         |                   | Х                  | ( 256B data |               | 2m d C4D              | 4 + 645    | 411 640 | 2   CAD |  |

|               |          |           | Н                 |                    | segm        | ents          | 2nd 64B               | 1st 64B    | 4th 64B | 3rd 64B |  |

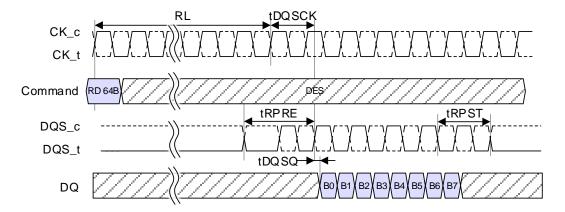

# 5.2. Read

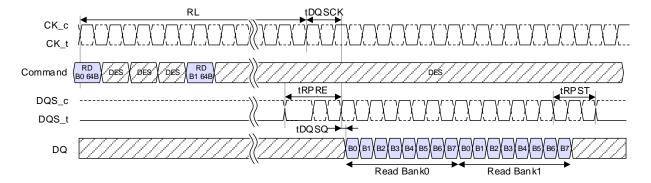

Read command replaces the common sequence of activate, read, precharge commands of LPDDR memory. Three different burst lengths of 8, 16, and 32 corresponding to 64B, 128B, and 256B data accesses can be specified on the fly with the Read command. Figure 5.1 and Figure 5.2 show timing diagrams for a single Read and gapless back to back Read operations in the same data slice. Figure 5.3 shows minimum time from a Read command to a Write command in the same slice. Read timing parameters RL, tDQSCK, tRPRE, tDQSQ, and tRPST are defined in Table 5.7.

Figure 5.1. 64B Read command timing diagram

Figure 5.2. Gapless back to bank 64B Reads to different banks in same slice

Figure 5.3. 64B Read followed by a 64B Write to different banks in same slice

# 5.2.1. Read Post-amble to Pre-amble Merge Behavior

When subsequent Read commands to a data slice are more than 4\*N\*tCK (burst-length of first Read command) apart and post-amble of first Read overlaps pre-amble of second Read, DQS signals shall follow the post-amble waveform for the duration of the post-amble to pre-amble overlap and then switch to the remaining waveform of pre-amble for the remainder of the tRPRE. This situation happens when second Read command is (4N+1)\*tCK or (4N+2)\*tCK or (4N+3)\*tCK after the first Read command.

Both DQ and DQS signals during read shall transition from high-Z to low-Z state only at the onset of DQS Read pre-amble until the end of DQS Read post-amble.

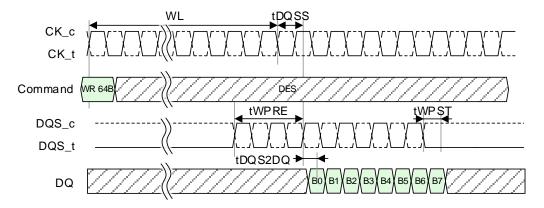

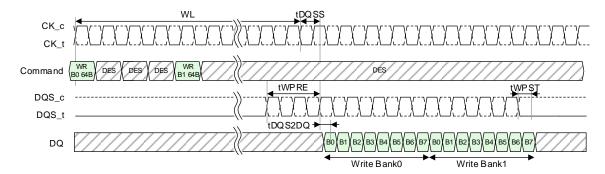

## 5.3. Write

Write command replaces the common sequence of activate, write, precharge commands of LPDDR memory. Three different burst lengths of 8, 16, and 32 corresponding to 64B, 128B, and 256B data accesses can be specified on the fly with the Write command. Figure 5.4 and Figure 5.5 show timing diagrams for a single Write and gapless back to back Write operations in the same data slice. Figure 5.6 shows minimum time from a Write command to a Read command in the same slice. Write timing parameters WL, tDQSS, tWPRE, tDQS2DQ, and tWPST are defined in Table 5.7.

Figure 5.4. 64B Write timing diagram

Figure 5.5. Gapless back to bank 64B Writes to different banks in same slice

Figure 5.6. 64B Write followed by a 64B Read to different banks in same slice

## 5.3.1. Write Post-amble to Pre-amble Merge Behavior

When subsequent Write commands to a data slice are more than 4\*N\*tCK (burst-length of first Write command) apart and post-amble of first Write overlaps pre-amble of second Write, DQS signals shall follow the post-amble waveform for the duration of the post-amble to pre-amble overlap and then switch to the remaining waveform of pre-amble for the remainder of the tWPRE. This situation happens when second Write command is (4N+2)\*tCK after the first Write command. Please note that Write to write command distance of (4N+1)\*tCK is illegal.

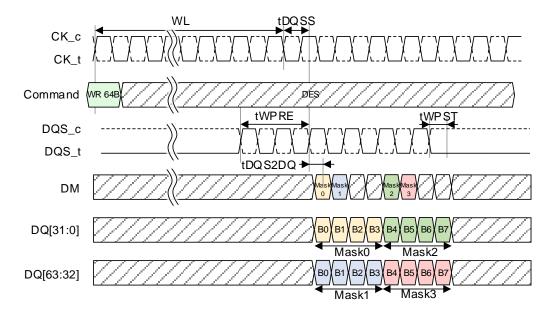

#### 5.3.2. Masked Writes and ECC

Masked writes shall have the same command and same timing requirements as normal writes except for use of DM pin to specify write data to be masked. In Low Latency Wide IO, due to small banks, ECC codec logic is placed once per each data slice and shared among all eight banks. Data mask segments shall have 16B granularity and match the granularity of the Low Latency Wide IO internal ECC data segments so that no internal read-modify-write operation is needed to support masked writes. Figure 5.7 shows the mapping of data mask bits sent on DM pin and the 16B data segment that will be masked as a result. In every burst length of 8, there are only four valid mask bits as shown with other four bits being ignored.

Figure 5.7. Mapping of DM mask bits to 16B data segments in a masked write operation

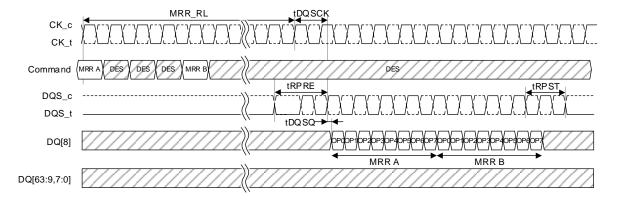

# 5.4. Mode Register Read

The Mode Register Read (MRR) command is used to read configuration and status data from Low Latency Wide IO channel. The mode register address operands (MA[5:0]) allow the user to select one of 64 registers. The 8-bit mode register content OP[7:0] is burst out of DQ\_S0[8] of data slice 0 according to the timing shown in Figure 5.8. DQS in slice 0 is toggled for the duration of the Mode Register READ burst. The MRR has a command burst length of 8. MRR operation shall not be interrupted. tMRR timing parameter is defined in Table 5.7. Other timing parameters shown for MRR shall match normal Read timings.

Figure 5.8. Mode Register Read (MRR) timing diagram

Table 5.3. Mapping of MRR read data to DQ

| Pin Name                       | BL0             | BL1 | BL2 | BL3 | BL4 | BL5 | BL6 | BL7 |

|--------------------------------|-----------------|-----|-----|-----|-----|-----|-----|-----|

| DQ_S0[8]                       | OP0             | OP1 | OP2 | OP3 | OP4 | OP5 | OP6 | OP7 |

| DQ_S0[63:9,7:0]<br>DQ_S1[63:0] | DQ_S0[63:9,7:0] |     |     |     |     |     |     |     |

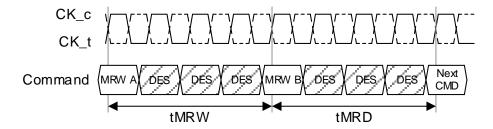

# 5.5. Mode Register Write

The Mode Register Write (MRW) command is used to write configuration data to the mode registers. The mode register address and the data written to the mode registers are contained in MRW command as specified in Table 5.1. The MRW command period is defined by tMRW. After an MRW command, a time period of tMRD must pass before any other command can be issued. Mode register Writes to read-only registers have no impact on the functionality of the device. MRW timing parameters tMRW and tMRD are defined in Table 5.7.

Figure 5.9. Mode Register Write (MRW) timing diagram

## 5.6. Refresh

Refresh command in Low Latency Wide IO only supports all-bank refresh for the banks in the same slice. Each data slice shall receive a refresh command every tREFI. Refresh command intervals cannot be pulled-in or pushed out by more than one tREFI period. A total of 2048 Refresh commands must be issued to every Low Latency Wide IO data slice every tREFW period. Figure 5.10 shows an example of how refresh operations may be mixed and overlapped among multiple data slices and channels. Refresh timing parameters tRFC, tREFI, tREFW are defined in Table 5.7.

Figure 5.10. Example Refresh operation timing diagram in two slices and two different channels

Low Latency Wide IO shall support JEDEC "Optimized Refresh" feature. Optimized Refresh requires that Low Latency Wide IO controller shall record the amount of time that has passed since the last refresh command for each data slice prior to entering self-refresh state. After exiting self-refresh state, Low Latency Wide IO controller shall wait for the remaining amount of time to complete refresh interval (tREFI) before issuing another refresh command to a data slice. Similarly, Low Latency Wide IO shall retain the amount of time that has expired in the current self-refresh interval prior to exiting self-refresh state, so that a remaining amount of time may expire after re-entering self-refresh state prior to performing a first self-refresh operation. Low Latency Wide IO controller shall keep track of Optimized refresh requirements for each channel separately (one timer per channel). Low Latency Wide IO device only needs to track

Optimized refresh requirements on a per channel basis.

# 5.6.1. Row Hammer Mitigation

There shall be no limitation on the number of read/write accesses to an Low Latency Wide IO page due to "row hammer" limitations in Low Latency Wide IO. To ensure "row hammer free" operation, Low Latency Wide IO controller will support the following two features. One of the two features can be enabled by Low Latency Wide IO controller:

## 5.6.1.1. Sub-bank Based Special Row Hammer Refresh Command

When enabled, Low Latency Wide IO controller will keep count of number of Read and Write accesses (one activate per access) issued to each of four sub-banks in a given bank in a given data slice (32 counters per data slice). If the number of accesses in any given sub-bank reaches a threshold as specified by MR24 OP[4:2], a special row hammer refresh command, Refresh\_S, is issued to the corresponding data slice. The four sub-banks within each Low Latency Wide IO bank are separated by the two most-significant page address bits (R10 and R9) in Read and Write command. No other command can be issued to the same data slice for tRFC\_SR duration after a Refresh\_S command. Once Refresh\_S command is issued to a given data slice, all 32 counters for that data slice are reset by Low Latency Wide IO controller.

## 5.6.1.2. Bank Based Special Row Hammer Refresh Command

When enabled, Low Latency Wide IO controller will keep count of number of Read and Write accesses (one activate per access) issued to each bank in a given data slice (8 counters per data slice). If the number of accesses in any given bank reaches a threshold as specified by MR24 OP[4:2], a special row hammer refresh command, Refresh\_S, is issued to the corresponding data slice. No other command can be issued to the same data slice for tRFC\_SR duration after a Refresh\_S command. Once Refresh\_S command is issued to a given data slice, all 8 counters for that data slice are reset by Low Latency Wide IO controller.

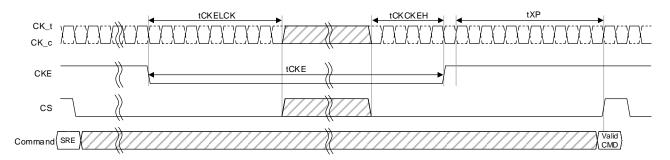

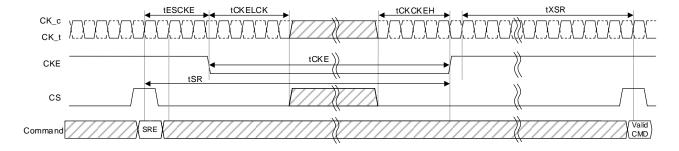

# 5.7. Power Down Entry and Exit

Power-down is asynchronously entered when CKE is driven LOW. CKE can only go low after both data slices in the channel have completed any on-going operation and are in idle state. Table 2.6 shows the earliest time power down entry can happen following any given command.