# International Memory Workshop

# **Tutorial**

14<sup>th</sup> International Memory Workshop (IMW) May 15<sup>th</sup> 2022 Dresden, Germany

**Platinum Sponsors**

**Gold Sponsors**

Western Digital.

Silver Sponsors

#### **Agenda**

#### **Tutorials**

09:00AM - 04:00PM

Organizers: Dirk Wouters (RWTH Aachen) and Thomas Mikolajick (NaMLab/TU Dresden)

Part 1 – Ferroelectric Memories 09:00AM – 12:00PM

Chairs: Dirk Wouters (RWTH Aachen)

*Katherine Chiang (TSMC)*

Laurent Grenouillet CEA-Leti 09:00AM – 10:00AM

"Ferroelectric Random Access Memory (FeRAM)"

Halid Mulaosmanovic, GlobalFoundries 10:00AM – 11:00AM

"Ferroelectric Field Effect Transistors (FeFET)"

Shosuke Fujii Kioxia 11:00AM – 12:00PM

### Part 2 – 3D Memories – Security Aspects of Memories

02:00PM - 04:00PM

Chairs: Antonio Arreghini (imec)

Thomas Mikolajick (Namlab/TU Dresden)

**Onur Mutlu ETH Zurich** 02:00PM – 03:00PM

"Security aspects of DRAM"

Swaroop Ghosh Penn State University 03:00PM - 04:00PM

"Security Aspects in Nonvolatile Memories"

<sup>&</sup>quot;Ferroelectric Tunnel Junction (FTJ)"

Laurent Grenouillet CEA-Leti

Laurent Grenouillet received the Engineer degree in physics in 1998 from the National Institute of Applied Sciences (INSA) in Lyon, France, and the PhD degree in electronic devices in 2001 for his work on the optical spectroscopy of diluted nitrides grown on GaAs substrates. After a post-doctoral position in the field of Molecular Beam Epitaxy, he joined CEA-Leti in 2002 and worked on GaAs-based VCSELs emitting in the 1.1-1.3µm range and single photon sources with quantum dots. In 2006, he joined the Silicon Photonics group where he developed CMOS compatible hybrid III-V on silicon lasers. In 2009, he joined IBM Alliance in Albany as a Leti assignee to contribute to the development of FDSOI technology. Within Albany state-of-the-art facilities, he extensively worked on device integration to improve performance of FDSOI devices (28nm and 14nm node). Back in France at CEA-LETI in 2013, he focused on the performance boosters for the 10nm node FDSOI technology, and took part to the FDSOI technology transfer to Global Foundries (22FDX) in 2015. During that period he joined the Advanced Memory Device Laboratory at CEA-Leti. His current research interests include resistive switching memory devices and selectors, and ferroelectric HfO2-based memories. Laurent Grenouillet authored or coauthored over 80 papers (conferences and journals) and has filed over 40 patents. He serves as committee member of Solid-State Devices and Materials (SSDM) conference.

# 1T-1C FERROELECTRIC RAM

Dr. L. Grenouillet, CEA-Leti | 14th International Memory Workshop, 2022 | Tutorial | 2022-05-15

laurent.grenouillet@cea.fr

**Ferroelectricity basics**

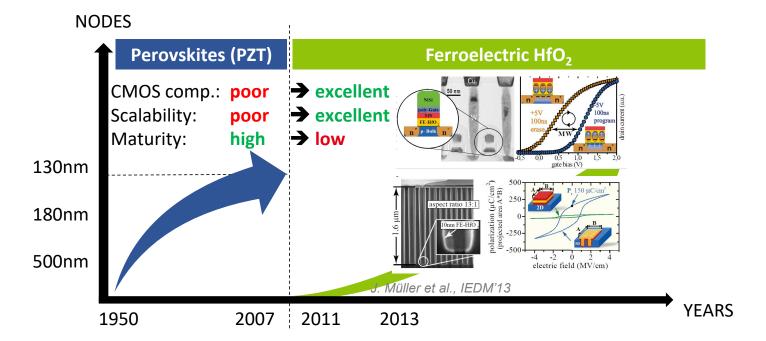

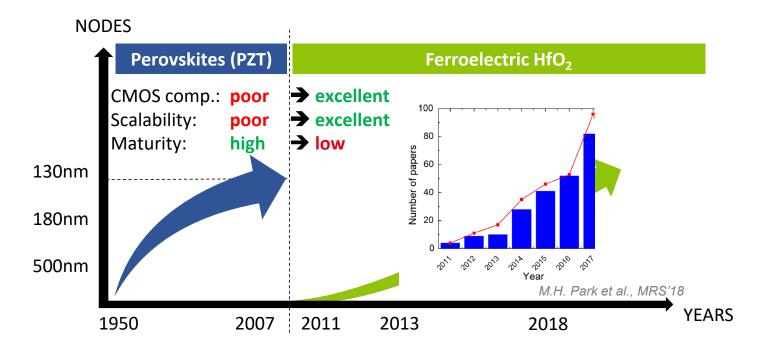

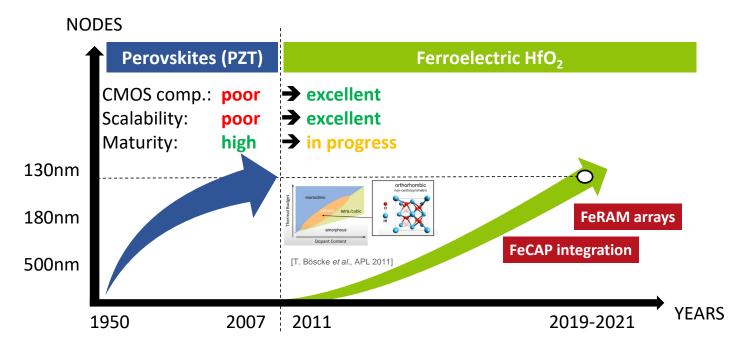

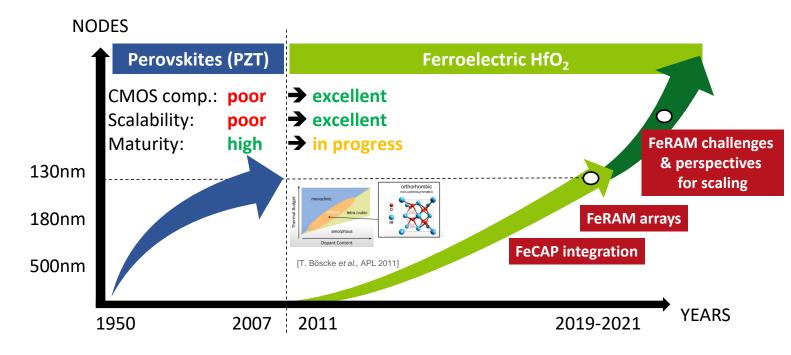

Ferroelectric HfO<sub>2</sub>: a change of paradigm for NVM

1T-1C FeRAM arrays: basics

HfO<sub>2</sub>-based MFM capacitors integrated above CMOS

HfO<sub>2</sub>-based 1T-1C FeRAM arrays: performance overview

Scalability: challenges and perspectives

## **Ferroelectricity basics**

Ferroelectric HfO<sub>2</sub>: a change of paradigm for NVM

1T-1C FeRAM arrays: basics

HfO<sub>2</sub>-based MFM capacitors integrated above CMOS

HfO<sub>2</sub>-based 1T-1C FeRAM arrays: performance overview

Scalability: challenges and perspectives

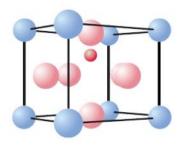

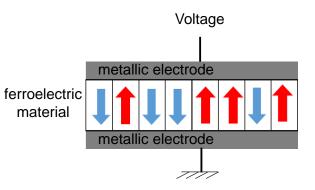

#### FERROELECTRIC MATERIAL: SOME BASICS

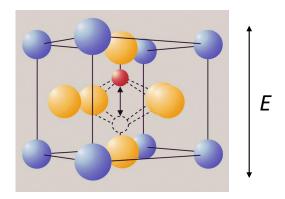

#### CRYSTALLOGRAPHY

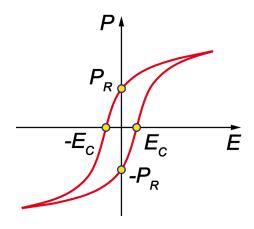

# **FERROELECTRICS:**

Crystallize in a non-centrosymmetric phase → ELECTRIC DIPOLE

#### FERROELECTRIC MATERIAL: SOME BASICS

#### CRYSTALLOGRAPHY

#### **ELECTRIC DIPOLE**

# **FERROELECTRICS:**

Crystallize in a non-centrosymmetric phase → ELECTRIC DIPOLE

1.5

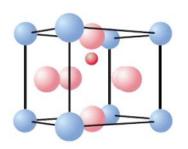

#### FERROELECTRIC MATERIAL: SOME BASICS

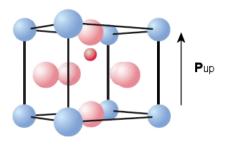

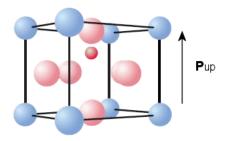

# Pup : A : 0 : B

**CRYSTALLOGRAPHY**

# ELECTRIC DIPOLE

# **FERROELECTRICS:**

- Crystallize in a non-centrosymmetric phase → ELECTRIC DIPOLE

- Show a SPONTANEOUS & SWITCHABLE ELECTRIC POLARIZATION

|6

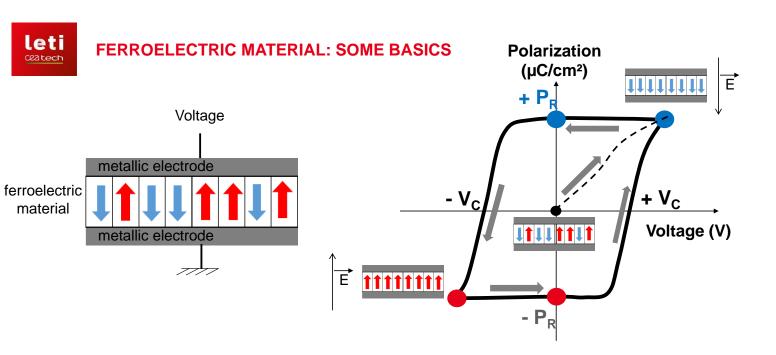

#### FERROELECTRIC MATERIAL: SOME BASICS

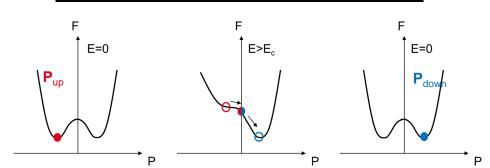

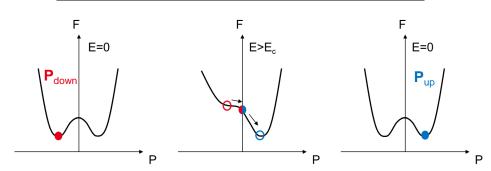

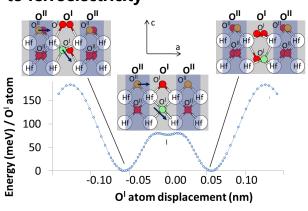

#### CRYSTALLOGRAPHY

#### THERMODYNAMICS (Landau-Ginzburg-Devonshire)

# **FERROELECTRICS:**

2 STABLE POLARIZATION STATES that can be switched by an ELECTRIC FIELD

. \_

#### FERROELECTRIC MATERIAL: SOME BASICS

#### **CRYSTALLOGRAPHY**

#### THERMODYNAMICS (Landau-Ginzburg-Devonshire)

# non-volatile memory

ultra low power

# **FERROELECTRICS:**

FCTRIC FIFLD

2 STABLE POLARIZATION STATES that can be switched by an ELECTRIC FIELD

#### **FERROELECTRIC MATERIAL: SOME BASICS**

# **FERROELECTRICS:**

2 STABLE POLARIZATION STATES that can be switched by an ELECTRIC FIELD

# **FERROELECTRICS:**

2 STABLE POLARIZATION STATES that can be switched by an ELECTRIC FIELD

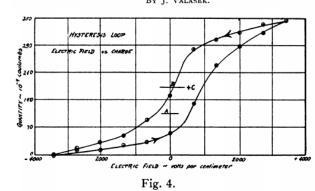

#### **FERROELECTRICS: KEY DATES**

1921: discovery of the elegant, fundamental physics of ferroelectricity by J. Valasek

# PIEZO-ELECTRIC AND ALLIED PHENOMENA IN ROCHELLE SALT.¹

By J. Valasek.

J. Valasek, Phys. Rev. 17, 475 (1921)

leti ceatech

#### **FERROELECTRICS: KEY DATES**

- 1921: discovery of the elegant, fundamental physics of ferroelectricity by J. Valasek

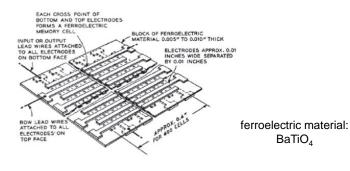

- 1952: ferroelectric memory invented by Dudley Allen Buck (crosspoint arrays)

1.

#### **FERROELECTRICS: KEY DATES**

- 1921: discovery of the elegant, fundamental physics of ferroelectricity by J. Valasek

- 1952: ferroelectric memory invented by Dudley Allen Buck (crosspoint arrays)

- 1990's: disturb issue solved by adding a select transistor (1T-1C bitcell)

ferroelectric material:  $Pb(Zr_xTi_{1-x})O_3$  (PZT)  $Sr_{1-x}Bi_{2+y}Ta_2O_9$  (SBT)

4096-Bit FRAM® Memory

D. Bondurant, Ferroelectrics, (1990)

"The FeRAM is the world's first integrated 'nonvolatile static RAM'."

| 13

## leti ceatech

#### **FERROELECTRICS: KEY DATES**

- 1921: discovery of the elegant, fundamental physics of ferroelectricity by J. Valasek

- 1952: ferroelectric memory invented by Dudley Allen Buck (crosspoint arrays)

- 1990's: disturb issue solved by adding a select transistor (1T-1C cell)

- Today: main Ferroelectric Random Access Memory (FeRAM) players

INFINEON

**TEXAS INSTRUMENT**

LAPIS (ROHM)

SKhynix

**FUJITSU**

Fujitsu has sold more PZT FRAM chips than any emerging memory in history – over 4 billion units since 1999!

#### FERROELECTRIC MEMORY (FERAM) MAIN INTERESTS

#### ATTRACTIVE FEATURES:

Ultra low power: < 10fJ/bit</li>

• **Fast**: < 100ns

Low voltage: < 3V</li>

High endurance: Up to 10<sup>15</sup> cycles

#### Reliability of Ferroelectric Random Access Memory Embedded within 130nm CMOS

J. Rodriguez, K. Remack, J. Gertas, L. Wang, C. Zhou, K. Boku, J. Rodriguez-Lato K. R. Udayakumar, S. Summerfelt, T. Moise Texas instruments Inc. Dallas, Texas USA jez@to.com

> D. Kim, J. Groat, J. Eliason, M. Depner, F. C RAMTRON International Corporation Colorado Springs, Colorado USA

#### **BUT**

#### **DOWNSIDES:**

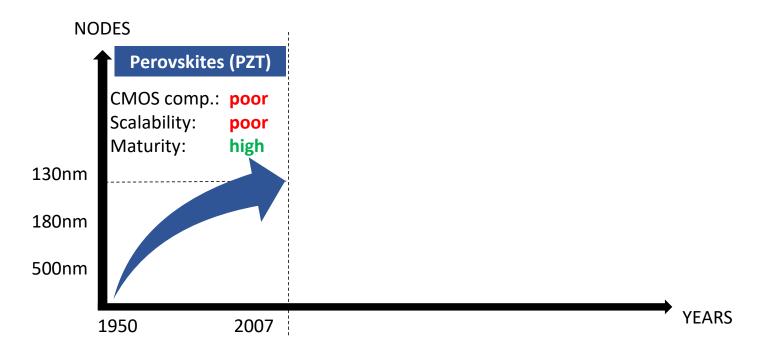

- PZT is not CMOS friendly (lead)

- PZT is not scalable

- → PZT-based FeRAM limited to niche applications & relaxed nodes (130nm)

#### **OUTLINE**

#### **Ferroelectricity basics**

Ferroelectric HfO<sub>2</sub>: a change of paradigm for NVM

1T-1C FeRAM arrays: basics

HfO<sub>2</sub>-based MFM capacitors integrated above CMOS

HfO<sub>2</sub>-based 1T-1C FeRAM arrays: performance overview

Scalability: challenges and perspectives

#### FERROELECTRIC HfO<sub>2</sub>

> a change of paradigm for NVM

#### FERROELECTRIC HfO<sub>2</sub>

> a change of paradigm for NVM

#### FERROELECTRIC HfO,

> a change of paradigm for NVM

110

#### FERROELECTRIC HfO,

> a change of paradigm for NVM

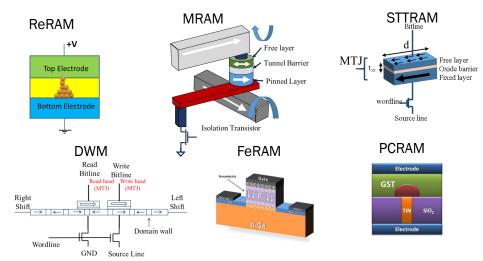

#### **VARIOUS FERROELECTRIC MEMORIES**

**Embedded memory arrays**

Artificial synapse (neuromorphics) Vector Matrix Multiplications

| 21

#### leti ceatech

#### **VARIOUS FERROELECTRIC MEMORIES**

**Embedded memory arrays**

APPLICATION SPACE

Artificial synapse (neuromorphics) Vector Matrix Multiplications

**Ferroelectricity basics**

Ferroelectric HfO<sub>2</sub>: a change of paradigm for NVM

1T-1C FeRAM arrays: basics

HfO<sub>2</sub>-based MFM capacitors integrated above CMOS

HfO<sub>2</sub>-based 1T-1C FeRAM arrays: performance overview

Scalability: challenges and perspectives

Loo

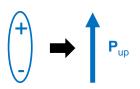

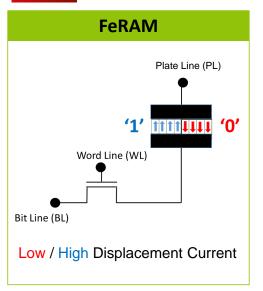

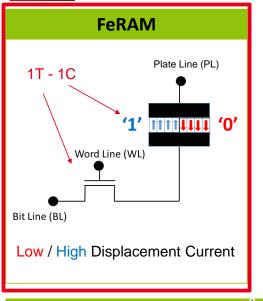

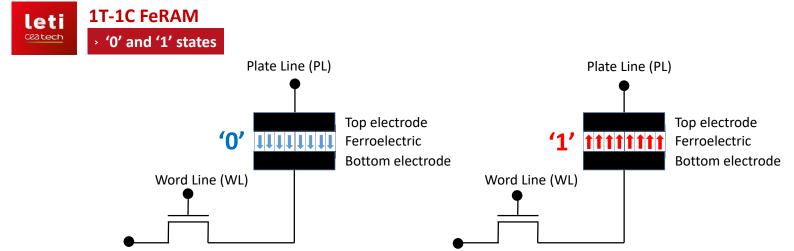

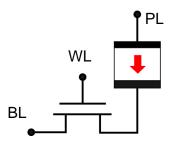

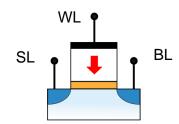

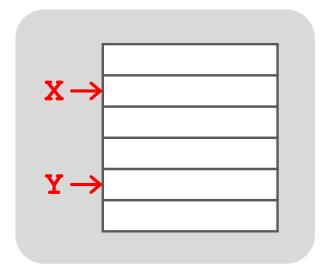

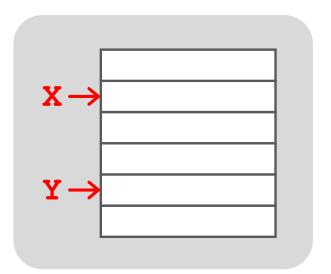

Bit Line (BL)

State '0' → Pdown

Bit Line (BL)

State '1' → Pup

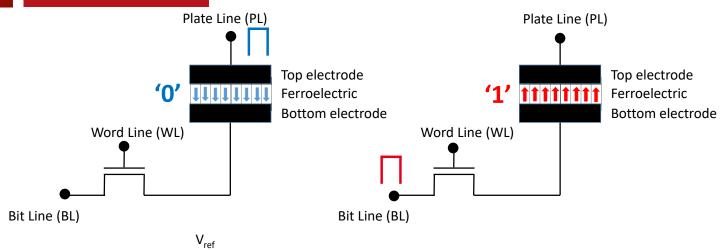

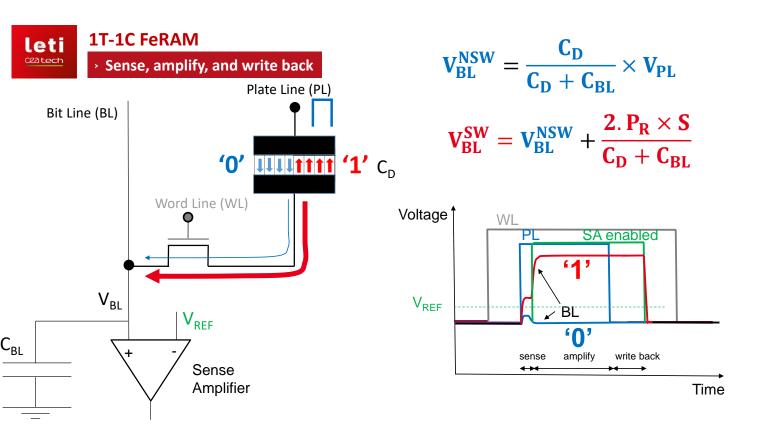

#### > WRITE '0' and '1' states

- WRITE '0' :

- precharge BL to GND

- pulse WL > Vth

- pulse PL > Vc

- WRITE '1':

- PL to GND

- pulse WL > Vth

- pulse BL > Vc

| 25

#### leti ceatech

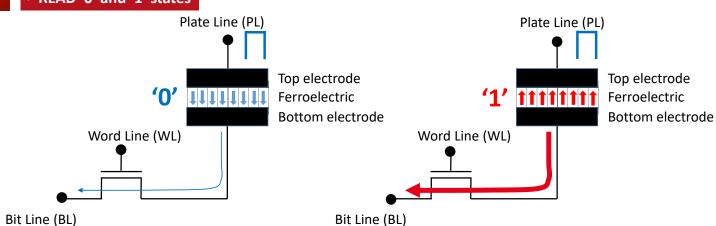

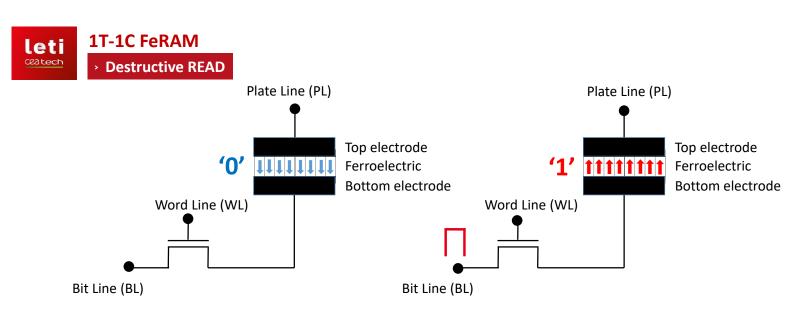

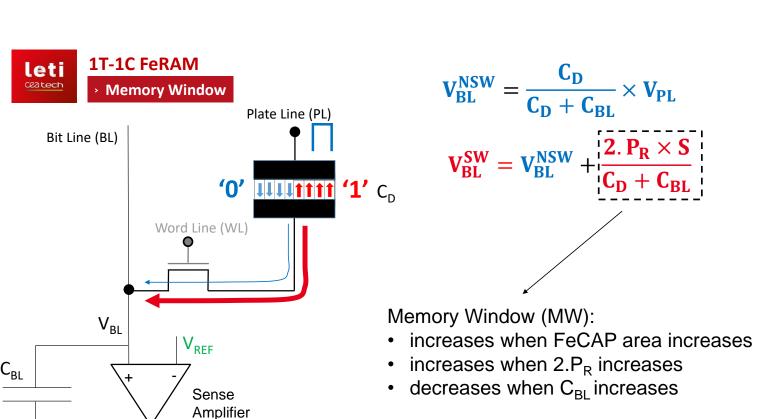

#### 1T-1C FeRAM

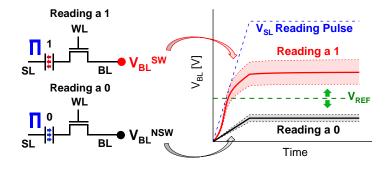

#### > READ '0' and '1' states

- READ '0':

- BL floating

- pulse WL > Vth

- pulse PL > Vc → small V<sub>BL</sub> elevation (displacement current)

- READ '1':

- BL floating

- pulse WL > Vth

- pulse PL > Vc → high V<sub>BL</sub> elevation (displacement current + switching current)

14

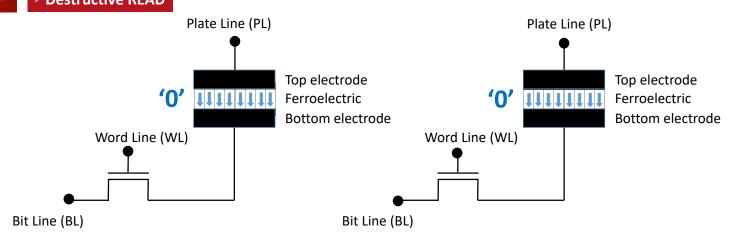

READ operation is destructive!

| 27

READ operation is destructive! → WRITE BACK necessary

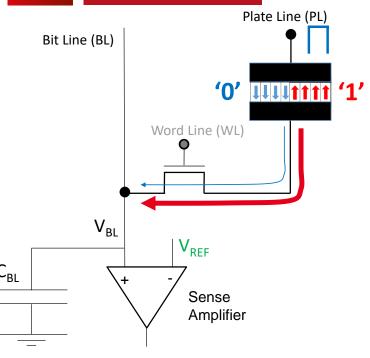

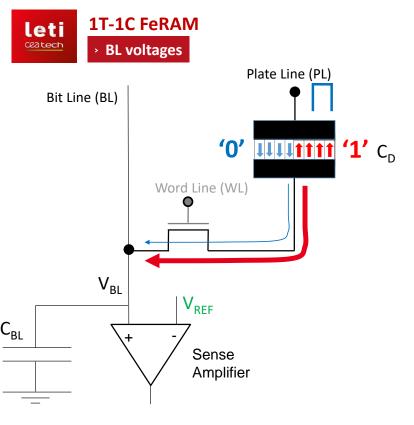

#### → READ '0' and '1' states

$$\begin{split} V_{BL}^{NSW} &= \frac{C_D}{C_D + C_{BL}} \times V_{PL} \\ V_{BL}^{SW} &= V_{BL}^{NSW} + \frac{2.\,P_R \times S}{C_D + C_{BL}} \end{split}$$

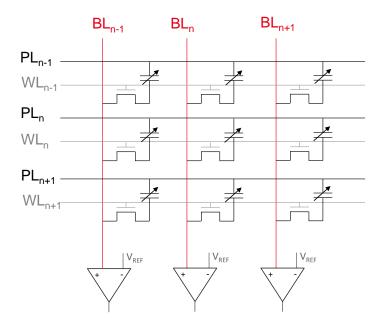

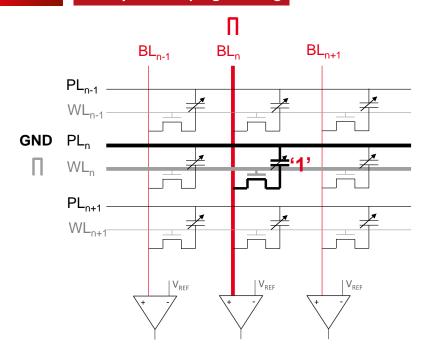

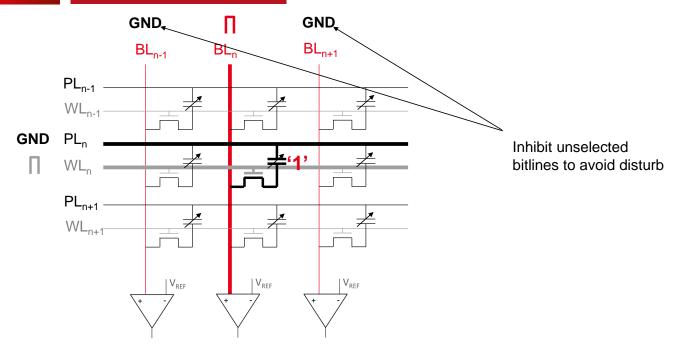

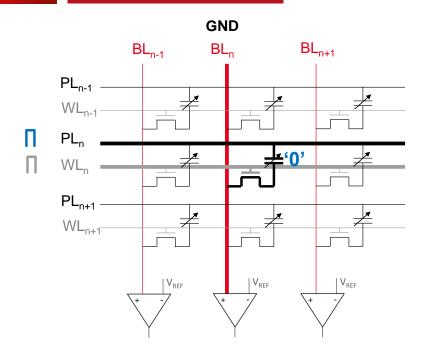

## > Arrays: bitcell programming

#### > Arrays: bitcell programming

#### **1T-1C FeRAM**

## > Arrays: bitcell programming

| 35

#### Arrays: bitcell programming

#### 1T-1C FeRAM

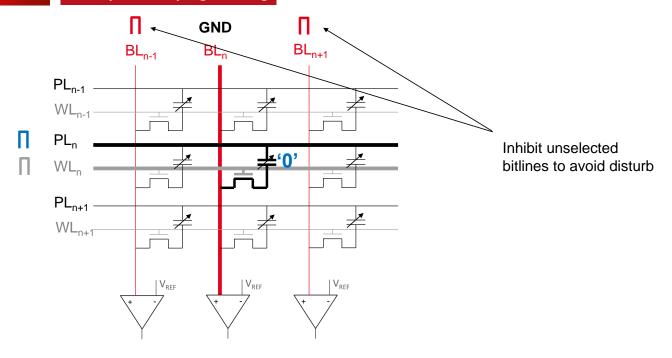

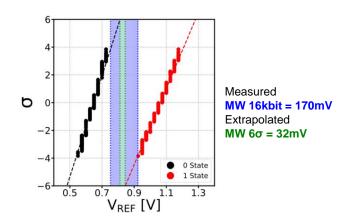

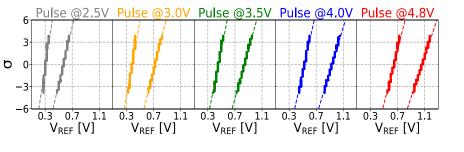

> Arrays: analog-like characterization with destructive READ operation

## Specific methodology to achieve analog-like characterization

Iterative READ and WRITE operations with scanning  $V_{REF}$  allows to reconstruct '0' and '1' distributions in 1T-1C FeRAM arrays

**Ferroelectricity basics**

Ferroelectric HfO<sub>2</sub>: a change of paradigm for NVM

1T-1C FeRAM arrays: basics

HfO<sub>2</sub>-based MFM capacitors integrated above CMOS

HfO<sub>2</sub>-based 1T-1C FeRAM arrays: performance overview

Scalability: challenges and perspectives

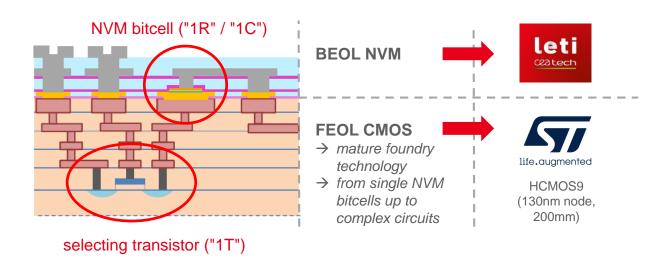

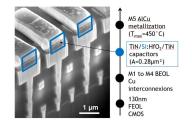

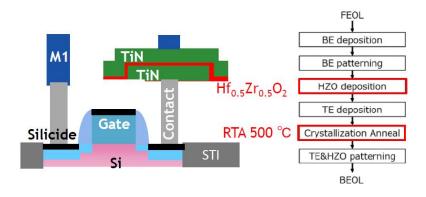

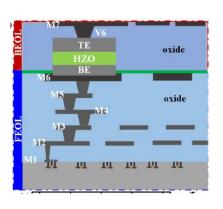

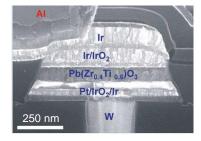

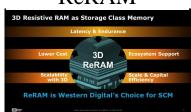

#### HfO<sub>2</sub>-BASED MFM CAPACITORS INTEGRATION

> BEOL integration in MAD200 test vehicle (130nm node)

MAD200: a versatile platform for assessing BEOL-NVMs (OxRAM, PCRAM... and FeRAM)

| 3

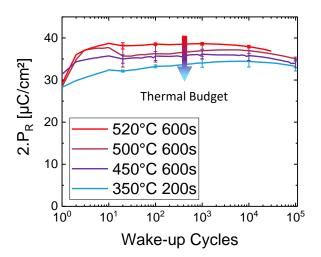

> Thermal budget for crystallization: prerequisite for BEOL integration

[T. Francois et al., IEDM 2019]

$2.P_R > 30\mu C/cm^2$  demonstrated down to a thermal budget of 350°C

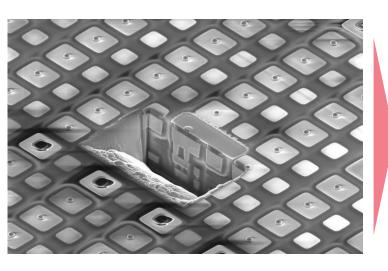

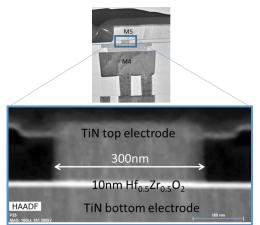

#### HfO<sub>2</sub>-BASED MFM CAPACITORS INTEGRATION

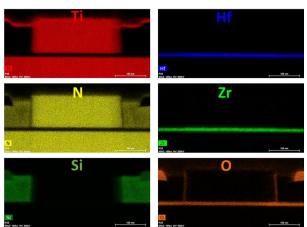

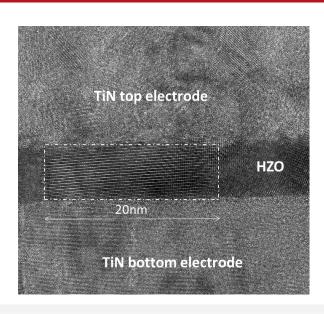

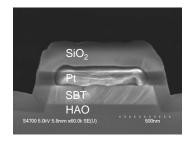

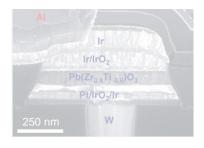

> BEOL integration at 130nm node - Morphological results

[T. Francois et al., IEDM 2019]

> BEOL integration at 130nm node - Morphological results

[T. Francois et al., IEDM 2019]

#### HfO<sub>2</sub>-BASED MFM CAPACITORS INTEGRATION

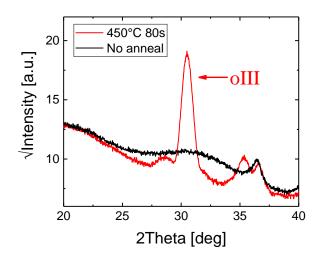

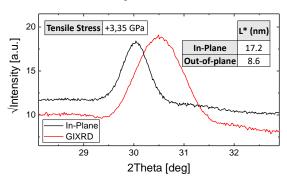

> BEOL integration at 130nm node - Morphological results

GIXRD characterization demonstrating oIII ferroelectric phase, with ~10nm-thick / 20nm-large cristallites

[T. Francois et al., IEDM 2019]

2019: demonstration of ferroelectric  $Hf_{0.5}Zr_{0.5}O_2$  in BEOL-integrated sub- $\mu m^2$  FeCap (NaMLab/Leti)

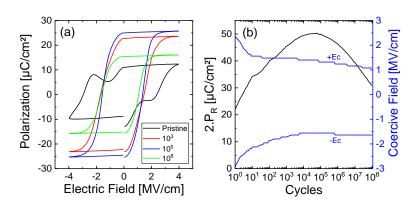

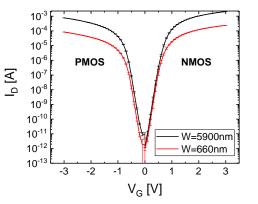

> BEOL integration at 130nm node - Electrical results

#### Integration of \$550nm HZO FeCap in BEOL...

#### ... while preserving FEOL CMOS

[T. Francois et al., IEDM 2019]

electrical demonstration of scaled FeRAM capacitors integrated in BEOL without impacting FEOL

1.45

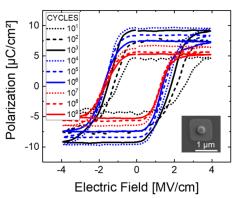

#### HfO<sub>2</sub>-BASED MFM CAPACITORS INTEGRATION

> BEOL integration at 130nm node - Electrical results

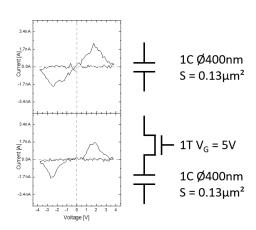

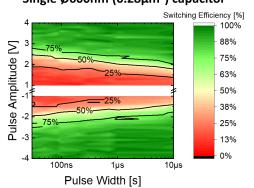

#### Switching kinetics on single scaled capacitors (10nm HZO)

Same behavior on 1C and 1T-1C

# After 10<sup>3</sup> wake-up cycles Single Ø600nm (0.28µm²) capacitor

[T. Francois et al., IEDM 2019]

down to 30ns switching capability >50% even at low voltages (2V) Suitable for memory application

146

> BEOL integration at 130nm node - Electrical results

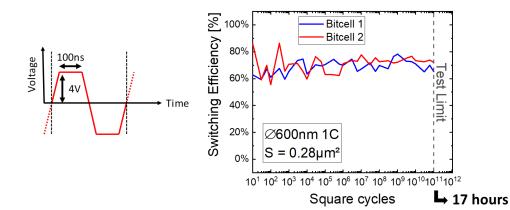

#### **Endurance measurement on single scaled capacitors (10nm HZO)**

[T. Francois et al., IEDM 2019]

Endurance >10<sup>11</sup> cycles (4V) for a BEOL-integrated HZO FeCap

#### HfO<sub>2</sub>-BASED MFM CAPACITORS INTEGRATION

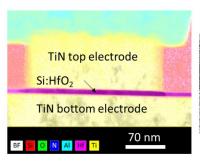

> BEOL integration at 130nm node-Si-implanted HfO<sub>2</sub>

#### Si:HfO<sub>2</sub> (HSO) FeCap in BEOL (thermal budget 450°C)

[L. Grenouillet et al., VLSI 2020]

${\rm Si:HfO_2}$  as a BEOL compatible ferroelectric material. Si doping by ion implantation

| 4

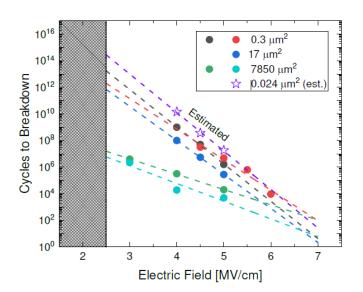

BEOL integrated FeCap: area scaling

[R. Alcala et al., EDTM 2022]

Scaling down FeRAM to sub-μm² sizes has a positive impact on reliability: promising for NVM application

| 49

#### HfO<sub>2</sub>-BASED MFM CAPACITORS INTEGRATION

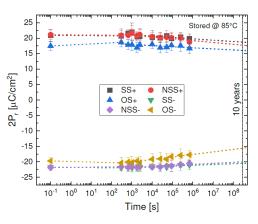

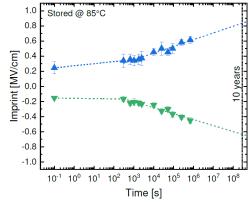

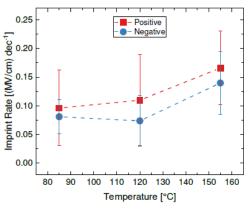

Data retention & Imprint

[R. Alcala et al., EDTM 2022]

Good data retention at 85°C even for Opposite State. Imprint rate increases above 125°C

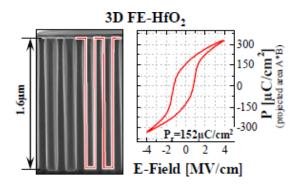

#### BEOL integration of 3D FeCap

# 3D Scalable, Wake-up Free, and Highly Reliable FRAM Technology with Stress-Engineered HfZrO<sub>x</sub>

Y.D. Lin<sup>1,3</sup>, H.Y. Lee<sup>1,\*</sup>, Y.T. Tang<sup>2</sup>, P.C. Yeh<sup>1</sup>, H.Y. Yang<sup>1</sup>, P.S. Yeh<sup>1</sup>, C.Y. Wang<sup>1</sup>, J.W. Su<sup>1,3</sup>, S.H. Li<sup>1</sup>, S.S. Sheu<sup>1</sup>, T.H. Hou<sup>1</sup>, W.C. Lo<sup>1</sup>, M. H. Lee<sup>4</sup>, M.F. Chang<sup>2</sup>, Y.C. King<sup>3</sup> and C.J. Lin<sup>3</sup>

<sup>1</sup>EOSL, Industrial Technology Research Institute, Hsinchu, Taiwan, \*email: hengyuan@itri.org.tw

<sup>2</sup> Taiwan Semiconductor Research Institute, Hsinchu, Taiwan,

<sup>3</sup>Institute of Electronics Engineering, National Tsing Hua University, Hsinchu, Taiwan

<sup>4</sup>Institute of Electro-Optical Science and Technology, National Taiwan Normal University, Taipei, Taiwan

| Ref.<br>Device          | This work                      |                               |  |

|-------------------------|--------------------------------|-------------------------------|--|

| 1C stacks               | (2D)<br>IL/HfZrO<br>10nm/IL    | (3D)<br>IL*/HfZrO<br>10nm/IL* |  |

| Cycling speed (kHz)     | 625                            | 625                           |  |

| Applied field (MV/cm)   | 2.5                            | 2.2                           |  |

| P <sub>r</sub> (uC/cm²) | 20~32                          | 18~20                         |  |

| Endurance               | 10 <sup>10</sup>               | 10 <sup>9</sup>               |  |

| Retention               | 5x10 <sup>4</sup> .<br>(105°C) | 5x10 <sup>4</sup> .<br>(85°C) |  |

\* 170 uC/cm2: N

[Y.D. Lin et al., IEDM 2019]

2D & 3D 10nm HZO-based FeCap integrated between M6 & M7. Endurance > 109 cycles

151

#### HfO<sub>2</sub>-BASED MFM CAPACITORS INTEGRATION

> Middle Of Line integration

[J. Okuno et al., VLSI 2020]

Advantage of MOL integration: higher thermal budget allowed for crystallization

## **Ferroelectricity basics**

Ferroelectric HfO<sub>2</sub>: a change of paradigm for NVM

1T-1C FeRAM arrays: basics

HfO<sub>2</sub>-based MFM capacitors integrated above CMOS

$\rightarrow$

HfO<sub>2</sub>-based 1T-1C FeRAM arrays: performance overview

Scalability: challenges and perspectives

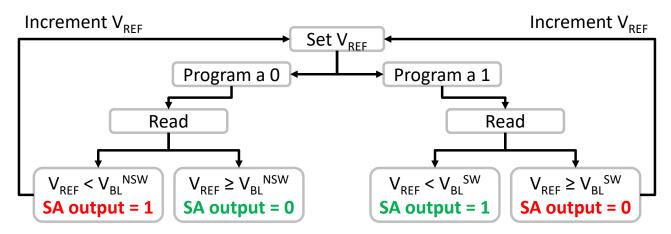

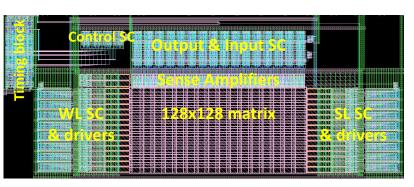

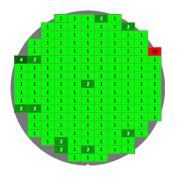

#### HfO<sub>2</sub>-BASED FERAM ARRAYS

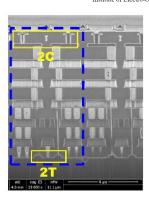

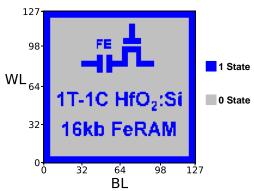

> 16 kbit FeRAM test vehicle (Leti - MAD200v3)

#### 16 kbit 1T-1C FeRAM layout

#### 16 kbit 1T-1C FeRAM chip view

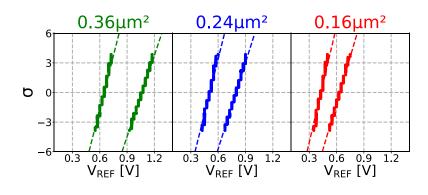

- 3x circuit versions, with FeCap areas = 0.36 / 0.24 / 0.16μm<sup>2</sup>

- Scan chains for bitcell addressing, circuit control and buffering out data

- Sense Amplifiers for (destructive) reading operations

- Internal Pulse Generators for sub-ns programming

#### HfO<sub>2</sub>-BASED FERAM ARRAYS

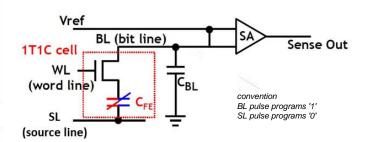

> 16 kbit FeRAM test vehicle (Leti - MAD200v3)

#### FeRAM bitcell & read operation

- bitcell = 1T FEOL + 1C BEOL Array = 128 Word Lines x 128 Bit Lines

- Polarization state of a bitcell is not directly measurable

- Read operation = attempt to program a '0'

- if bitcell = '1' → ferro switch detected

- if bitcell = '0' → no ferro switch detected

- program back data

155

# leti

#### HfO<sub>2</sub>-BASED FERAM ARRAYS

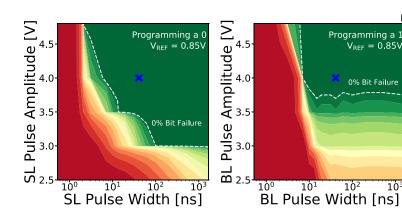

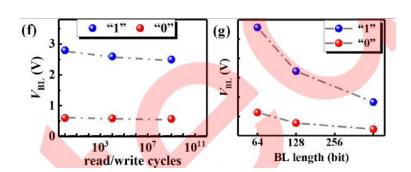

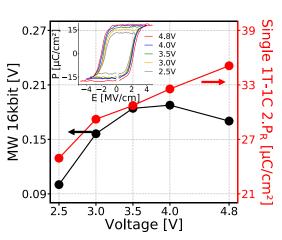

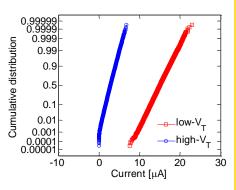

> 16 kbit FeRAM electrical results (Leti - MAD200v3)

Distributions on Si:HfO<sub>2</sub>-based 16 kbit FeRAM (0.36 μm<sup>2</sup> FeCap, 4.8V/2μs pulses, after wake-up)

Nominal memory operation at V<sub>REF</sub>=0.85V

[T. Francois et al., IEDM 2021]

0 bitfail, large Memory Window

#### HfO2-BASED FERAM ARRAYS

> 16 kbit FeRAM electrical results (Leti - MAD200v3)

Bit Failure [%]

100.00

26.83

7.20

1.93

0.52 0.14 0.05

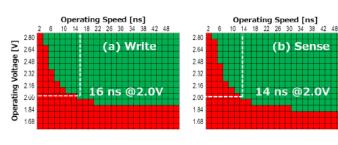

#### **Memory speed**

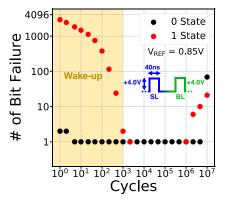

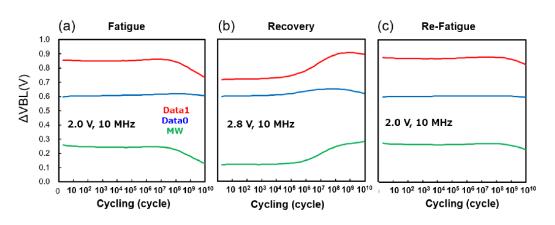

#### Endurance Si:HfO<sub>2</sub>-based 16 kbit FeRAM

[T. Francois et al., IEDM 2021]

Excellent switching speed down to 10ns

Endurance > 10<sup>7</sup> cycles using high cycling field

# leti

#### HfO<sub>2</sub>-BASED FERAM ARRAYS

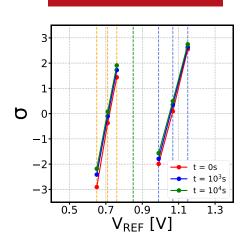

→ 16 kbit FeRAM electrical results (Leti - MAD200v3)

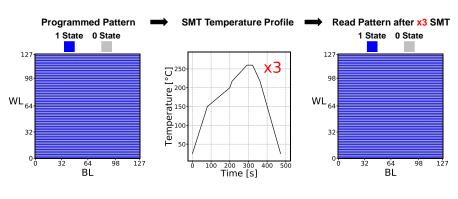

#### Data retention at 125°C

#### 0 bitfail after 3x solder reflow test (T<sub>max</sub>=260°C)

[T. Francois et al., IEDM 2021]

MW open after 10<sup>4</sup>s @125°C with V<sub>REF</sub> = 0.85V Solder reflow compatibility demonstrated for the first time

. . .

#### HfO<sub>2</sub>-BASED FERAM ARRAYS

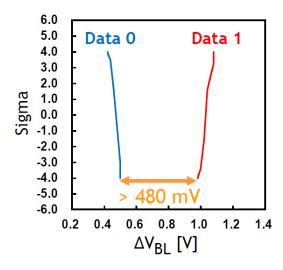

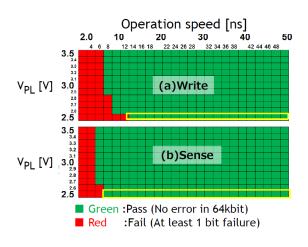

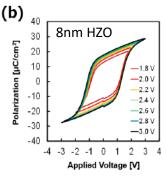

#### > 64 kbit FeRAM electrical results (SONY)

[J. Okuno et al., VLSI 2020]

100 % bit functionality and 480 mV read margin (1μm² FeCap) Sub 10 ns operation speed and < 2.5 V operating voltage

1.50

#### HfO<sub>2</sub>-BASED FERAM ARRAYS

#### > 16 kbit FeRAM electrical results (Xidian University, Xi'an UniIC Semiconductor)

[W. Xiao et al., Science China 2022]

Integration between M6 & M7 of TaN/HZO/TaN 64µm² FeCap and larger 30 ns switching speed, >10<sup>4</sup> s data retention, and >10<sup>11</sup> cycling capability. > 10<sup>9</sup> write/read cycling for the 1T–1C cell is achieved for the first time at array level.

|                             | Sony<br>(VLSI 2020)         | Sony<br>(IMW 2021,<br>EDTM2022)                                          | Leti<br>(IEDM 2021)                   | Xidian University,<br>Xi'an UniIC<br>Semiconductor |

|-----------------------------|-----------------------------|--------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------|

| Node                        | 130nm                       | 130nm                                                                    | 130nm                                 | 130nm                                              |

| Circuit size                | 64 kbit                     | 64 kbit                                                                  | 16 kbit                               | 16 kbit                                            |

| Ferro material-<br>stack    | TiN / HZO 10nm / TiN        | TiN / HZO 8nm / TiN                                                      | TiN / HSO 10nm / TiN                  | TaN / HZO 20nm /<br>TaN                            |

| Integration, thermal budget | MOL (M1) > 500°C            | MOL (M1) > 500°C                                                         | BEOL (M4-M5) <<br>500°C               | BEOL (M6-M7) <<br>500°C                            |

| Min. write voltage          | 2.5V                        | 2V                                                                       | 2.5V                                  | 3.5V                                               |

| Write speed                 | 14ns at 2.5V (one<br>state) | 16ns at 2V (one state)                                                   | 4ns at 4.8V (both state)              | 30ns                                               |

| Endurance                   | -                           | $>10^{15}$ at 2V<br>(extrapolated)<br>$>10^{10}$ at<br>2V/2.8V(measured) | > 10 <sup>7</sup> at 4V<br>(measured) | > <b>10<sup>9</sup> at 3.5V</b><br>(measured)      |

| Retention                   | -                           | -                                                                        | 125°C 10 <sup>4</sup> s               | 10 <sup>4</sup> s (RT)                             |

| Solder reflow               | -                           | -                                                                        | Yes                                   | -                                                  |

| 6

|                   | NOR FLASH                         | MRAM                              | PCRAM         | OxRAM                                        | FeRAM (PZT)        | FeRAM (HfO <sub>2</sub> )                                      |

|-------------------|-----------------------------------|-----------------------------------|---------------|----------------------------------------------|--------------------|----------------------------------------------------------------|

| Programming power | ~200pJ/bit                        | ~20pJ/bit                         | ~300pJ/bit    | ~100pJ/bit                                   | ~100fJ/bit         | ~100fJ/bit                                                     |

| Write speed       | 20 μs                             | 20 ns                             | 10-100 ns     | 10-100 ns                                    | <100ns             | 14ns @ 2.5V (Sony)<br>4ns @ 4.8V (Leti)                        |

| Endurance         | 10 <sup>5</sup> - 10 <sup>6</sup> | 10 <sup>6-</sup> 10 <sup>15</sup> | 108           | 10 <sup>5</sup> – 10 <sup>6</sup> on 16 kbit | > 10 <sup>15</sup> | > 10 <sup>11</sup> single device<br>10 <sup>9</sup> on 16 kbit |

| Retention         | > 125°C                           | 85°C - 165 °C                     | 165°C         | > 150°C                                      | 125°C              | 125°C – SMT<br>compliant                                       |

| Extra masks       | Very high (>10)                   | Limited (3-5)                     | Limited (3-5) | Low (2)                                      | Low (2)            | Low (2)                                                        |

| Process flow      | Complex                           | Medium                            | Medium        | Simple                                       | Simple             | Simple                                                         |

| Multi-Level Cell  | Yes                               | No                                | Yes           | Yes                                          | No                 | No                                                             |

| Scalability       | Bad                               | Medium                            | High          | High                                         | Poor (130nm)       | Poor (2D)<br>High (3D)                                         |

| 63

#### HfO<sub>2</sub>-BASED FERAM ARRAYS

Scalability towards more advanced nodes?

**Ferroelectricity basics**

Ferroelectric HfO<sub>2</sub>: a change of paradigm for NVM

1T-1C FeRAM arrays: basics

HfO<sub>2</sub>-based MFM capacitors integrated aboveCMOS

HfO<sub>2</sub>-based 1T-1C FeRAM arrays: performance overview

Scalability: challenges and perspectives

164

#### **CHALLENGES AND PERSPECTIVES FOR FERAM SCALING**

Voltage scaling

Si:HfO<sub>2</sub> 16 kbit FeRAM

4.8V → 2.5V programming voltage

[T. Francois et al., IEDM 2021]

Low voltage operation reduces MW

Voltage scaling

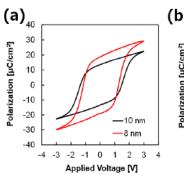

#### 10nm HZO → 8nm HZO

[J. Okuno et al., IMW 2021]

Thickness scaling of ferroelectric layer from 10nm down to 8nm enables operation down to 2V

167

# leti

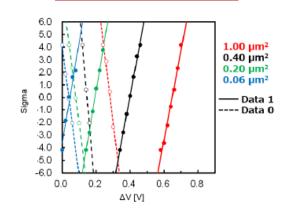

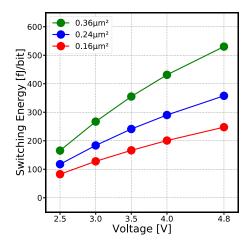

#### CHALLENGES AND PERSPECTIVES FOR FERAM SCALING

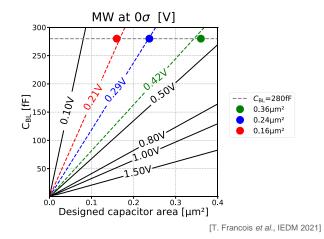

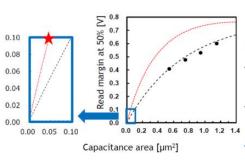

Area scaling

10nm Si:HfO<sub>2</sub> 16 kbit FeRAM 0.36μm<sup>2</sup> → 0.16μm<sup>2</sup> FeCap

8nm HZO 64 kbit FeRAM

1μm² → 0.06μm² FeCap

[T. Francois et al., IEDM 2021]

[J. Okuno et al., IMW 2021]

Scaling FeCap area reduces MW

Area scaling

3D Al:HfO<sub>2</sub> FeCap, aspect ratio = 13:1

#### 3D HZO anti-ferroelectric capacitor above FinFET

[P. Polakowski et al., IMW 2014]

[S. -C. Chang et al., IEDM 2021]

Maintaining large FeCap area while reducing footprint is possible using 3D capacitors

16

# leti

#### **CHALLENGES AND PERSPECTIVES FOR FERAM SCALING**

Voltage & Area scaling

[T. Francois et al., IEDM 2021]

Voltage scaling & FeCap area scaling results in switching energy lower than 100 fJ/bit

→ Area scaling – 1T-1C bitcell

→ 1T footprint can be small

Main diffentiator w.r.t. resistive memories (OxRAM, PCM, ...) for which selector needs to drive  $> 100~\mu\text{A}$

leti

#### CHALLENGES AND PERSPECTIVES FOR FERAM SCALING

> Bitline Capacitance scaling

- Experiment

Simulation at CBL 250 fF

Simulation at CBL 120 fF

- Experimental result meet the estimation

- ✓ Potential to work < 0.05 µm² in leading edge technology

- → 3D structure

[J. Okuno et al., VLSI 2020]

C<sub>BL</sub> expected to decrease for nodes beyond 130nm

- → allows to improve MW at fixed capacitor area

- → allows to decrease capacitor area at fixed MW

Endurance

#### **HZO-based FeRAM arrays (4 kbit)**

[J. Okuno et al., EDTM 2022]

Encouraging endurance results reported at array level (> 10<sup>10</sup> cycles) with recovery phase Better understanding of role of defects needed at the fundamental level, to reduce wake-up and fatigue.

130

| 73

#### **OUTLINE**

Scalability: challenges and perspectives

#### FERROELECTRIC HfO2: TAKE-AWAY MESSAGES FOR FeRAM

- Ferroelectricity in HfO<sub>2</sub> was unveiled 10 years ago

- Ferroelectric HfO<sub>2</sub> currently attracts a lot of attention for non-volatile memory applications:

- CMOS compatibility

- Scalability

- Ultra low power

- Easy integration

- HfO<sub>2</sub>-based ferroelectric ramdom access memories (FeRAM) are already demonstrating excellent performances at the array level (16kbit – 64 kbit) at 130nm

- High speed operation < 20ns

- Low voltage operation < 2.5V

- Ultra low energy < 100 fJ/bit

- Endurance > 109 cycles

- Data retention at 125°C

- Solder Reflow Compatilibity

- Material and stack improvement and better understanding needed (wake-up, fatigue, imprint ...)

- Destructive reading requires very high endurance and prevents multi-level capability

- HfO<sub>2</sub>-based FeRAM scaling to node < 130 nm is envisioned

leti

#### SPECIAL THANKS TO CEA TEAM ...

Terry François

Justine Barbot

Julie Laguerre Jennifer Izaguirre

Adam Makosiej Bastien Giraud

Simon Martin Niccolo Castellani

Catherine Carabasse Mélanie Louro

Nick Barrett

Philippe Blaise

François Triozon Olivier Billoint Vaxelaire

Elisa Vianello Jean Coignus

Thomas Magis, Catherine Pellissier, Massoud Bedjaoui, Virginie Beugin, Philippe Rodriguez, Guillaume Rodriguez, Sébastien Kerdilès, Hélène Grampeix, Virginie Loup, Pierre-Marie Deleuze, Tifenn Hirtzlin, Filippo Moro, Wassim Hamouda, François Aussenac, Chiara Sabbione, Magali Tessaire, Fred Mazen, Marianne Coig, Olivier Renault, Etienne Nowak, Caroline Coutier, François Andrieu, Thierry Poiroux, Julien Arcamone

... AND TO YOU FOR YOUR ATTENTION!

**QUESTIONS?**

Halid Mulaosmanovic GlobalFoundries

Halid Mulaosmanovic received the Ph.D. in Information Technology at Politecnico di Milano, Italy, in 2016. He worked as a research fellow at NaMLab, Dresden, Germany, from 2016 to 2021, where his research interests included ferroelectric materials and devices, with a particular focus on ferroelectric field-effect transistors for memory and unconventional applications. Now, he is with GlobalFoundries Inc., Germany, and is involved in ferroelectric memory projects among others.

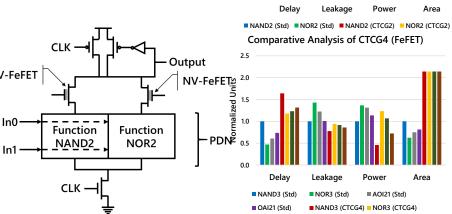

## **Ferroelectric FETs**

Halid Mulaosmanovic

- > Introduction to Ferroelectric FETs

- > Ferroelectric HfO<sub>2</sub>

- Device characteristics

- Memory window

- Switching kinetics

- · Size dependence

- · Reliability

- · (Co)-Integration

- > Ferroelectric FETs beyond memory

- > Conclusions

- Ferroelectric HfO<sub>2</sub>

- Device characteristics

- Memory window

- Switching kinetics

- · Size dependence

- · Reliability

- · (Co)-Integration

- > Ferroelectric FETs beyond memory

- Conclusions

### **Ferroelectricity**

perovskite oxide (ABO<sub>3</sub>): PZT, SBT, BTO ...

Courtesy of Fujitsu Semiconductor

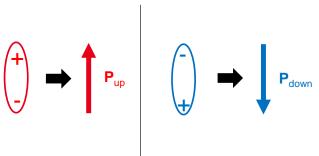

- > Polarization is switched between two equivalent states by an external electric field

- Reversibly switchable permanent dipoles appealing for information storage

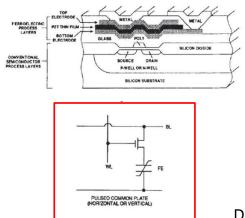

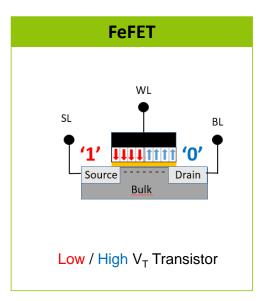

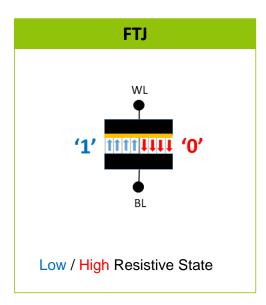

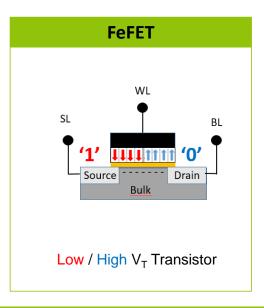

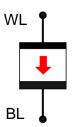

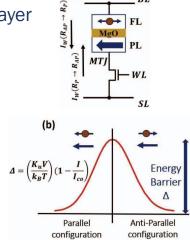

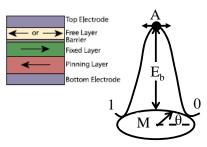

### **Ferroelectric memory**

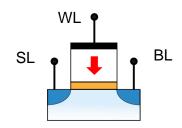

#### 1T1C FeRAM

J. F. Scott, Science, 2007

#### 1T FeFET

L. V. Hai, Semi. Sci. Tech., 2010

#### 1C FTJ

H. J. Mao, RCS PCCP, 2015

GlobalFoundries © 2021 All Rights Reserved 5

### **Ferroelectric memory**

#### 1T1C FeRAM

J. F. Scott, Science, 2007

#### 1T FeFET

L. V. Hai, Semi. Sci. Tech., 2010

#### 1C FTJ

H. J. Mao, RCS PCCP, 2015

GlobalFoundries © 2021 All Rights Reserved 6

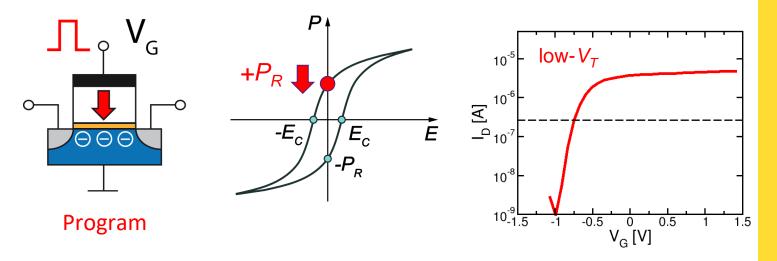

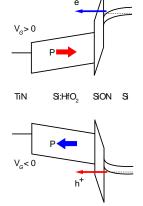

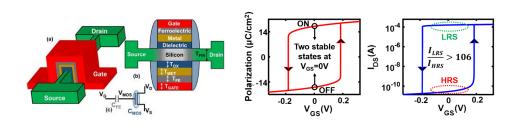

### **Ferroelectric FET**

- ➤ Write: permanent reversal of polarization under  $V_G = V_G (|E_F| > |E_C|)$   $\rightarrow$  e.g. n-type FeFET:  $P \downarrow$  results in low- $V_T$

- > Read is nondestructive

GlobalFoundries © 2021 All Rights Reserved

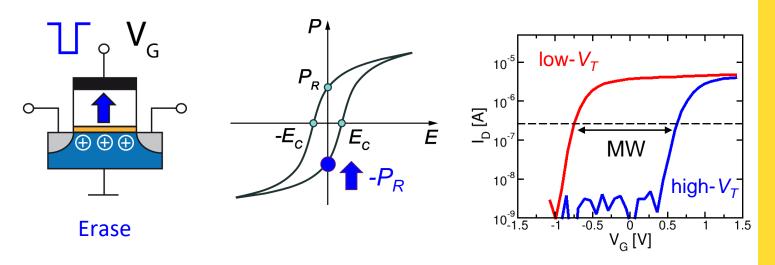

### **Ferroelectric FET**

- ➤ Write: permanent reversal of polarization under  $V_G = V_G (|E_F| > |E_C|)$ → e.g. n-type FeFET:  $P \uparrow$  results in **high-V**<sub>T</sub>

- > Read is nondestructive

GlobalFoundries © 2021 All Rights Reserved

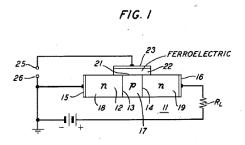

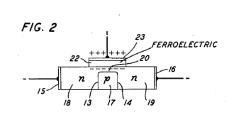

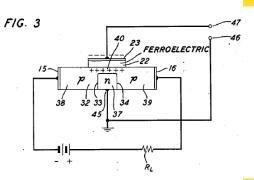

### An old idea

#### United States Patent Office

2,791,760

SEMICONDUCTIVE TRANSLATING DEVICE

Ian M. Ross, New Providence, N. J., assignor to Bell Telephone Laboratories, Incorporated, New York, N. Y., a corporation of New York

Application February 18, 1955, Serial No. 489,223 9 Claims. (Cl. 340—173)

"...one feature of this invention comprises altering the conductivity of a path through a semiconductive body by polarizing a ferroelectric maintained in proximity to the body to alter the surface charge on a portion of that body."

GlobalFoundries © 2021 All Rights Reserved

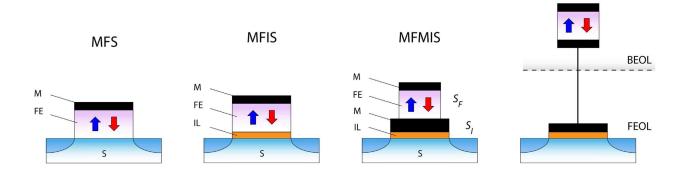

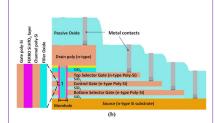

### **FeFET structures**

- ➤ Each of the structures has its particular advantages:

- MFS: direct contact between FE and S → optimal voltage control of the device

- MFIS: buffer layer between FE and S → interface quality tailoring; no interdiffusion phenomena

- MFMIS: S<sub>E</sub>/S<sub>I</sub> tailoring to improve the operation voltage and memory window

- ➤ Also full-BEoL FeFETs have been demonstrated

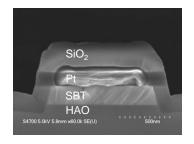

### **Perovskite FeFETs**

- Excellent endurance and retention

- 64kbit NAND functionality

- However, scaling and integration concerns!

Sakai et al., JJAP, 2004 Sakai et al., IEEE EDL, 2004 Zhang et al., JJAP, 2011

GlobalFoundries © 2021 All Rights Reserved

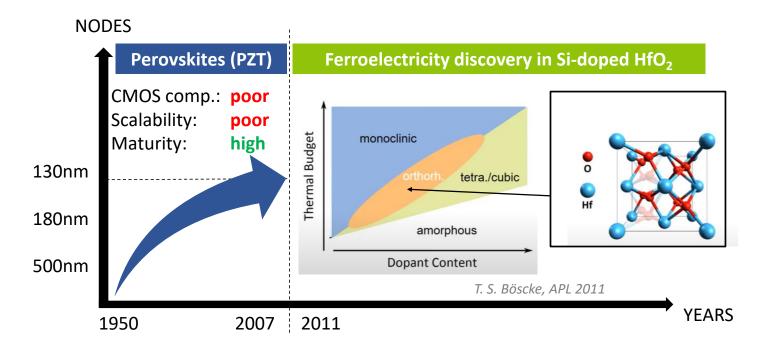

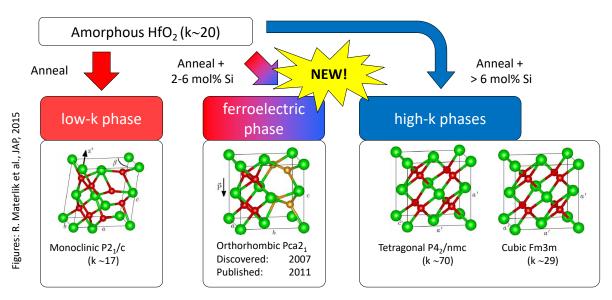

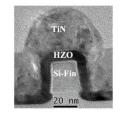

### Ferroelectricity in HfO<sub>2</sub>

#### Courtesy of FMC

Many stabilization knobs for the ferroelectric phase: doping, stress, annealing, film thickness ...

### Ferroelectric HfO<sub>2</sub>

- → HfO₂ is a simple binary oxide → various mature deposition techniques available

- ➤ Large bandgap (5.3-5.7 eV) → reduced leakage

- ➤ Well known high-k material in semiconductor industry → CMOS compatible

- Robust ferroelectricity even upon aggressive vertical and lateral scaling

T. S. Böscke et al., APL, 2011

GlobalFoundries © 2021 All Rights Reserved

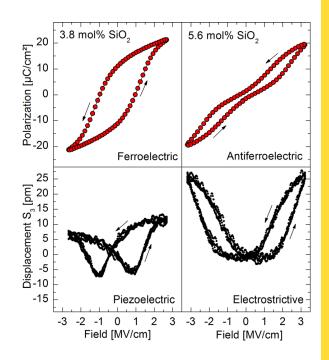

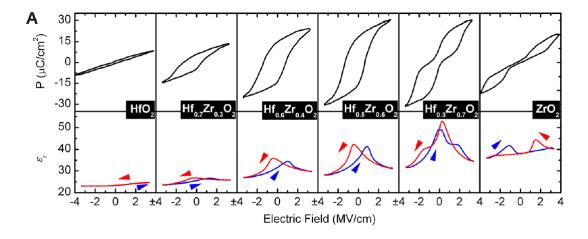

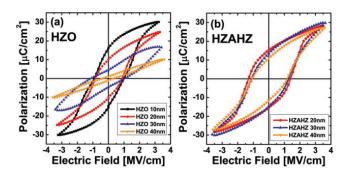

### Ferroelectric Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub>

J. Müller, Nano Lett., 2012

- HfO<sub>2</sub> and ZrO<sub>2</sub> have very similar physical and chemical properties

- FE and AFE behavior has been confirmed in HfO<sub>2</sub> ZrO<sub>2</sub> solid solution and in pure ZrO<sub>2</sub> as well

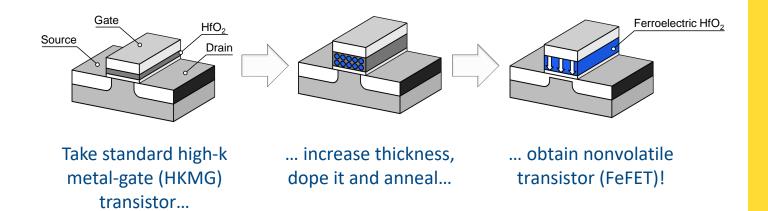

### From MOSFET to HfO<sub>2</sub> FeFET

Courtesy of FMC

- Only a few additional masks needed for FeFET fabrication

- > Full front-end CMOS compatibility make HfO<sub>2</sub> FeFETs attractive

GlobalFoundries © 2021 All Rights Reserved

2008

### Ferroelectric HfSiO in a transistor

Courtesy of U. Schröder, NaMLab

First HfO<sub>2</sub> based FeFET realized in 65 nm technology

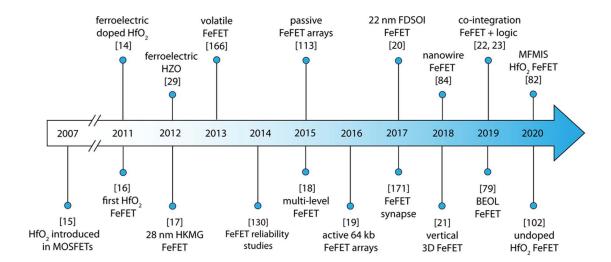

### **FeFET evolution**

#### > Rapid progress in material and device development

Mulaosmanovic et al., Nanotechnology, 2021

GlobalFoundries © 2021 All Rights Reserved

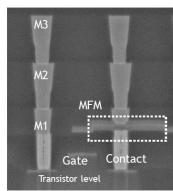

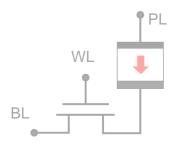

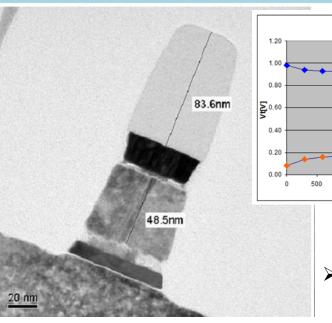

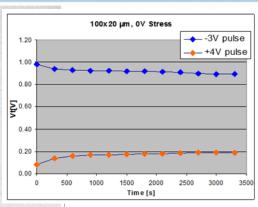

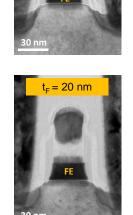

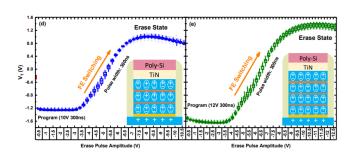

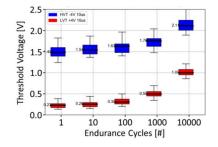

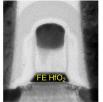

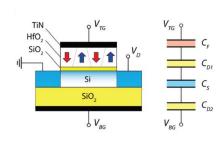

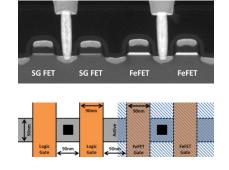

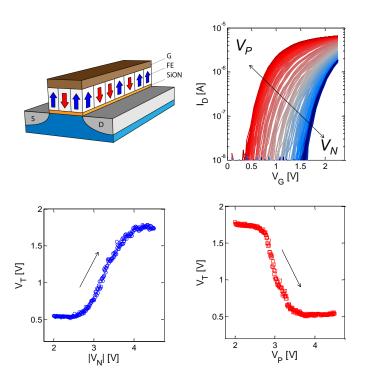

### **HKMG FeFET at GF**

###

22FDX° eFeFET

FEFET NISI

MG

FE

SOI

BOX

mini array devices full wafer map W/L=450nm/450nm

64 kbit AND array W/L=450nm/450nm

- H. Mulaosmanovic, IEDM, 2015

- M. Trentzsch, IEDM, 2016

- S. Dünkel, IEDM, 2017

- S. Beyer, IMW, 2020

- Memory window > 1.5V

- · Retention > 10 years

- Endurance: 10<sup>4</sup> –10<sup>5</sup>

- Low operation voltages (< 4V)</li>

- · Fast access time (ns-regime)

- · Full FEoL CMOS compatibility

- Fine-grained co-integration with CMOS transistors

- · Only 2 structural DUV mask adder

- High scalability ( $L_G = 20 \text{ nm}$ )

- Ferroelectric HfO<sub>2</sub>

- Device characteristics

- Memory window

- Switching kinetics

- · Size dependence

- Reliability

- · (Co)-Integration

- Ferroelectric FETs beyond memory

- > Conclusions

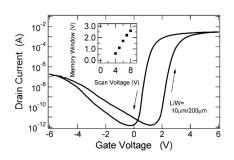

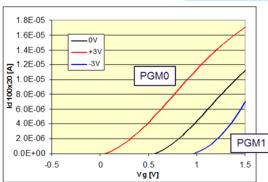

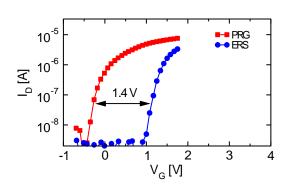

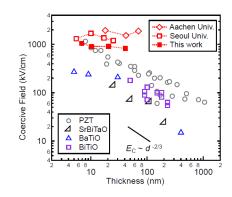

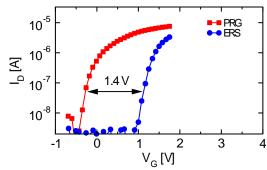

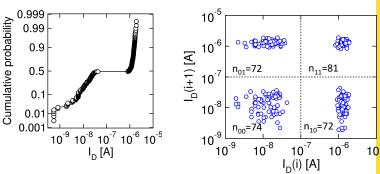

### **Memory window**

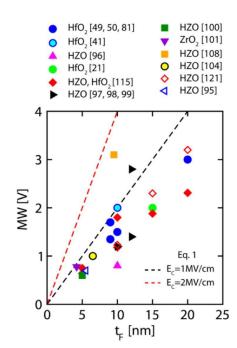

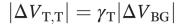

$$\mathsf{MW} = 2 \cdot \alpha \cdot E_C \cdot t_F$$

- $\triangleright$  Coercive field  $E_C$  relatively invariant

- Thickness of FE  $t_F$  can be increased

S. Migita et al., JJAP, 2018

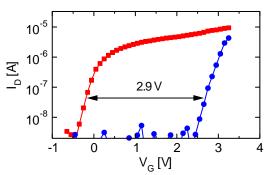

$t_{\rm E} = 20 \, \rm nm$

- 10<sup>-5</sup>

10<sup>-6</sup>

2.9 V

10<sup>-8</sup>

-1 0 1 2 3 4

V<sub>G</sub> [V]

- $MW = 2 \cdot \alpha \cdot E_C \cdot t_F$

- $\triangleright$  Coercive field  $E_C$  relatively invariant

- $\triangleright$  Thickness of FE  $t_F$  can be increased

- MW up to 3 V is achieved

- Stable retention and endurance

- > Possibility of multi-level storage

H. Mulaosmanovic, IEEE T-ED, 2019

GlobalFoundries © 2021 All Rights Reserved

### **Memory window**

= 10 nm

Mulaosmanovic et al., Nanotechnology, 2021

#### $MW = 2 \cdot \alpha \cdot E_C \cdot t_F$

GlobalFoundries © 2021 All Rights Reserved

### **Memory window**

Kim et al., APL, 2014

Ali et al., IEDM, 2019

- Ferroelectric properties tend to rapidly degrade at higher film thicknesses

- Insertion of interlayers (e.g. AIO<sub>v</sub>) may contrast this degradation

- Penalty: integration complexity and larger operation voltage (e.g. 12 V)

GlobalFoundries © 2021 All Rights Reserved

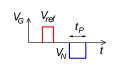

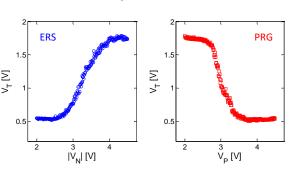

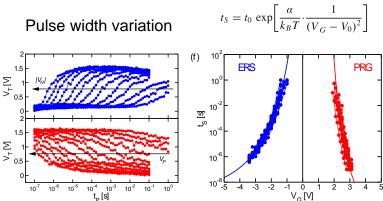

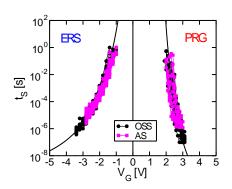

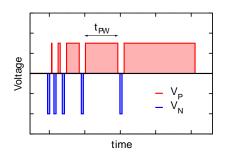

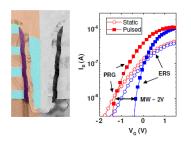

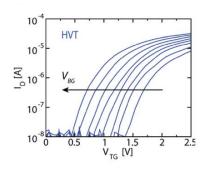

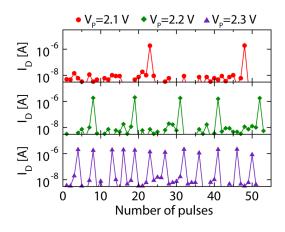

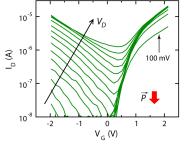

### **Switching kinetics**

Mulaosmanovic et al, IEEE T-ED 67, 5804 (2020)

#### Amplitude variation

#### Pulse width variation

- Significant time-voltage switching dependency

- Trade-off: fast switching → larger amplitudes

- Sub-nanesecond switching demonstrated

GlobalFoundries © 2021 All Rights Reserved

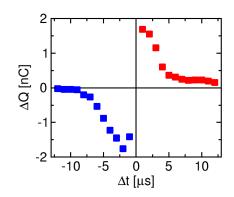

Mulaosmanovic et al, ACS AMI 10, 23997 (2018) Mulaosmanovic et al, IEEE T-ED 67, 5804 (2020)

- > FeFETs undergo switching even upon sub-critical voltage pulses

- > Accumulative effect demonstrated over a broad range of electrical conditions

- Same physical laws governing both one-shot and accumulative switching

GlobalFoundries © 2021 All Rights Reserved

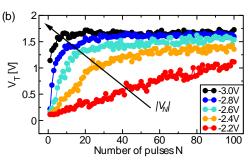

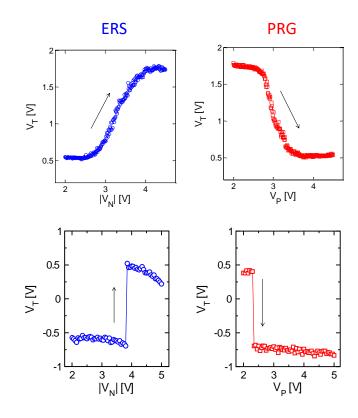

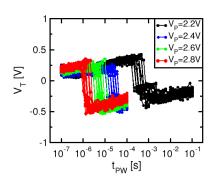

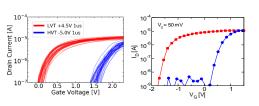

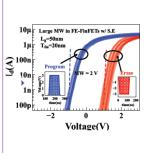

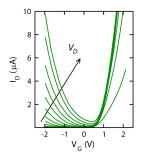

### **Size Dependency**

#### ➤ Large FeFETs:

- $W = 1 \mu m, L = 1 \mu m$

- Gradual switching between 2 states

- > 64 intermediate  $V_T$  states

#### ➤ Ultra-scaled FeFETs:

- W = 80 nm, L = 30 nm

- · Abrupt switching between 2 states

- · Apparently, no intermediate states

H. Mulaosmanovic et al., IEDM, 2015 H. Mulaosmanovic et al., EDTM, 2020

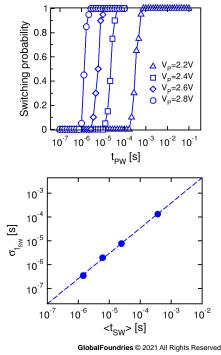

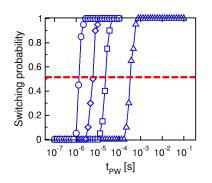

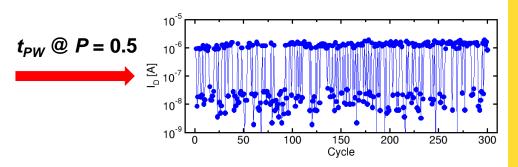

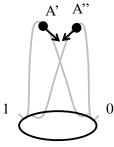

### **Stochastic switching**

- Time-voltage trade-off for ferroelectric switching

- Switching is a stochastic process!

- Unity slope over several decades in the mean  $t_{\text{SW}}$  vs. standard deviation ( $\sigma_{tSW}$ ) plot  $\rightarrow$  Poisson process

H. Mulaosmanovic et al., ACS AMI, 2017

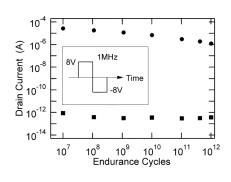

### Reliability

#### **Charge trapping**

- > Screening of MW

- Long read latency

- Degradation of IL

- ➤ Endurance walk-out

#### **Cycling Endurance**

➤ Usually < 10<sup>6</sup> cycles

A. Tan, IEEE EDL, 2021

➤ But, some reports with > 10<sup>10</sup> cycles avalable

#### **Data Retention**

- Proper stack design → robust retention, even at T > 250°C

- ➤ Improper stack → depolarization

GlobalFoundries © 2021 All Rights Reserved

### **Integration**

**Planar**

28 nm bulk

22 nm FDSOI

Trentzsch, IEDM, 2016

Dünkel, IEDM, 2017

**Vertical 3D**

K. Florent, IEDM, 2018

#### Fin-FeFET

Omega-FeF<mark>ET</mark>

10<sup>4</sup> V<sub>0s</sub>=0.2V 2 10<sup>3</sup> 10<sup>3</sup> 10<sup>3</sup> 10<sup>-1</sup> 10<sup>-1</sup> 10<sup>-1</sup> 10<sup>-1</sup> 1.5 -1.0 -0.5 0.0 0.5 1.0 1.5

S. De, VLSI, 2021

Chen, IRPS, 2<mark>020</mark>

GlobalFoundries © 2021 All Rights Reserved

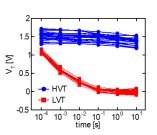

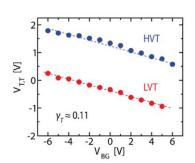

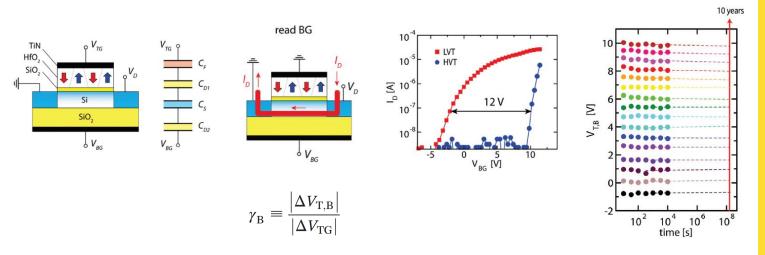

### 22 FDSOI FeFET: add-on functionality

- $\succ$  Back bias enables independent tuning of  $V_T$  (HVT and LVT)

- ➤ No polarization disturb

- > Targeting option for read out

H. Mulaosmanovic, Nanoscale, 2021

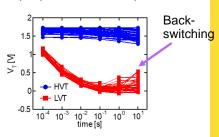

### 22 FDSOI FeFET: add-on functionality

- Back-gate can act as an independent read-out terminal

- Artificial increase of MW up to 12 V

- ➤ Enables easy V<sub>T</sub> distinction → 4 bit/cell storage

- ➤ Write and read paths are separated → no read disturb

4 bits/cell

H. Mulaosmanovic, Nanoscale, 2021

GlobalFoundries © 2021 All Rights Reserved

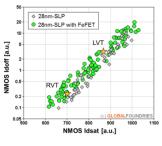

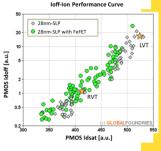

### **Co-Integration FeFET + CMOS**

24Mb 0.120μm2 SRAM yield >90% & CMOS within 10% on 28SLPe with FeFET technology

- FeFETs and logic FETs sharing the same active area

- 90 nm gate-to-gate distance

24 Mb D120 QRAM yield

- SRAM yield comparable to the high-volume production CMOS base platform

- Device matching is within 10% of the base platform

- · Can be further improved by target implants

S. Beyer et al., IMW, 2020

- Ferroelectric HfO<sub>2</sub>

- Device characteristics

- Memory window

- Switching kinetics

- · Size dependence

- · Reliability

- · (Co)-Integration

#### > Ferroelectric FETs beyond memory

> Conclusions

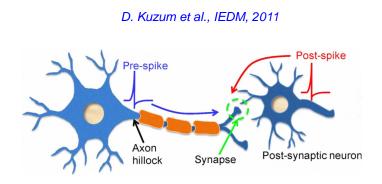

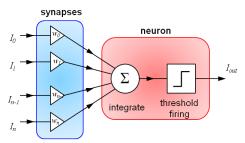

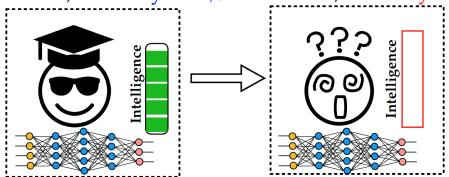

### **Neuromorphic Computing**

- > Directly or remotely inspired by the computing in biological brains

- Main building blocks: synapses and neurons

### **Ferroelectric synapses**

- ➤ Polycrystalline HfO<sub>2</sub> → multi-domain ferroelectric

- ➤ Gradual switching → analog conductivity tuning

- Spike-timing dependent plasticity (STDP) demonstrated

- Suitable for analog weights in DNNs as well

H. Mulaosmanovic et al., VLSI, 2017

GlobalFoundries © 2021 All Rights Reserved

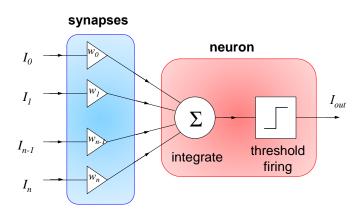

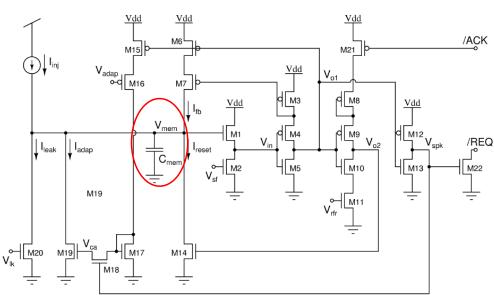

### **Artificial neurons with CMOS**

G. Indiveri et al., IEEE Trans. Neur. Net., 2006

- ightharpoonup Large capacitor  $C_{mem}$  for the integration of spikes occupies a significant area

- Mimicking of additional neuronal dynamics → dramatic increase of n. of transistors

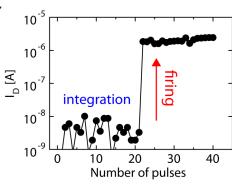

W = 80 nm; L = 30 nm

- ➤ Integration of gate pulses → integration of spikes coming from other neurons

- ➤ Abrupt switching → firing

H. Mulaosmanovic et al., Nanoscale, 2018

GlobalFoundries © 2021 All Rights Reserved

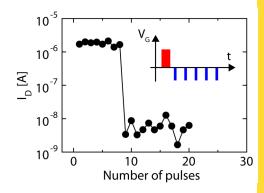

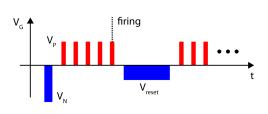

### **Ferroelectric neurons**

W = 80 nm; L = 30 nm

- Stronger neuronal input signals induce higher firing frequency → firing rate tuning

- Refractory period can be arbitrarily tuned over several orders of magnitude to satisfy circuital requirements (e.g. real-time as well as accelerated-time neuronal dynamics)

H. Mulaosmanovic et al., Nanoscale, 2018

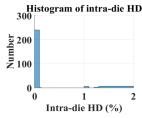

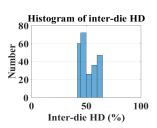

### **Random number generation**

- > Stream of equally probable "1" and "0"

- > Populations of "00", "01", "10" and "11" is nearly matched

H. Mulaosmanovic et al., IEEE EDL, 2018

GlobalFoundries © 2021 All Rights Reserved

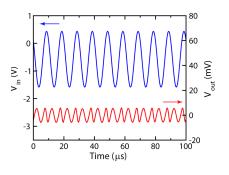

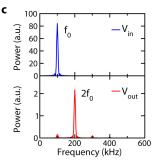

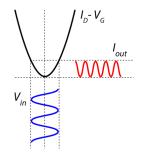

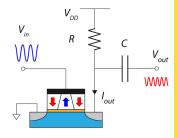

### **Frequency multiplication**

- Tune the symmetry of FeFET's I<sub>D</sub>-V<sub>G</sub> by polarization switching and GIDL

- > Frequency multiplication is achieved

Mulaosmanovic et al., Nature Electron. 3, 2020

- > Introduction to Ferroelectric FETs

- Ferroelectric HfO<sub>2</sub>

- > Device characteristics

- · Memory window

- Switching kinetics

- Size dependence

- Reliability

- · (Co)-Integration

- > Ferroelectric FETs beyond memory

- Conclusions

### **Conclusions**

- Ferroelectricity intrinsic memory functionality

- > FeFETs very attractive 1T memory solutions for embedded applications

- > Ferroelectric HfO<sub>2</sub> opens new opportunities for FeFETs

- Significant progress in device physics, integration, reliability, and scaling over the years

- Main switching mechanisms revealed

- → important learning for retention, disturbs, endurance, array operation schemes

- Unconventional applications due to variety of switching patterns

- → Neuromorphic; Reconfigurable logic-in-memory; Frequency manipulation; Security

#### **GF FeFET Team**

Dr. Sven Beyer

Dr. Stefan Dünkel

Dr. Johannes Müller

Dr. Martin Trentzsch

#### **Partners**

#### **Funding**

This work is funded by the Federal Ministry for Economics and Energy (BMWi) and by the State of Saxony in the framework "Important Project of Common European Interest (IPCEI)."

GlobalFoundries © 2021 All Rights Reserved

Shosuke Fujii Kioxia Corporation

Shosuke Fujii is a Chief Specialist at Kioxia Corporation, currently leading an emerging device technology team. He received the B.S. (2005) and M.S. (2007) degrees in materials science and engineering from Kyoto University, Japan. He joined Toshiba Corporation in 2007, where he was engaged in the research on reliability physics of MONOS memories. From 2009 to 2016, he was engaged in the research of emerging memory cell technology including resistive switching memory and ferroelectric memory. From 2016 to 2018, he was a visiting scholar in Stanford University, where he studied scaling effects of resistive switching memories. He is currently with Kioxia Corporation (renamed from Toshiba Memory Corporation), where he is engaged in research and development of emerging memory devices. He served as a technical committee member for memory reliability in IEEE IRPS in 2014 and 2015, and a tutorial lecturer in IEEE IRPS in 2016. He has been serving as a technical program committee member in VLSI Symposium since 2020.

### **Ferroelectric Tunnel Junction**

Shosuke Fujii KIOXIA

**KIOXIA**

#### **Outline**

- 1. Ferroelectric tunnel junction

- 2. Ferroelectric HfO<sub>2</sub>-based tunnel junction

- 3. FTJ for emerging application

- 4. Summary

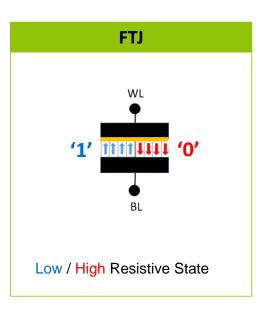

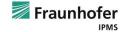

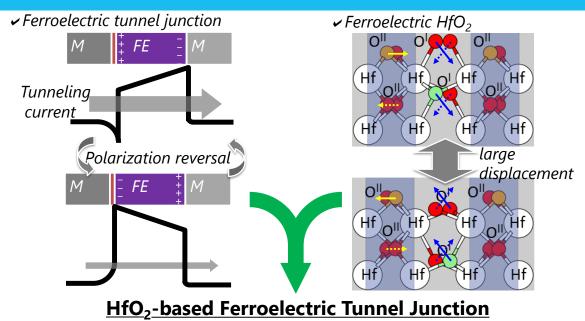

#### **Ferroelectric Tunnel Junction (FTJ)**

✓ Emerging memory that utilizes polarization reversal

→ Demonstration of BaTiO<sub>3</sub> FTJ

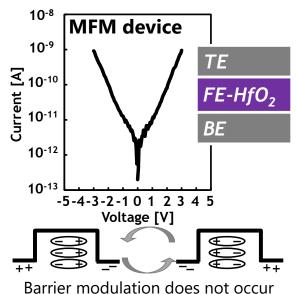

#### Mechanism of barrier modulation

- -Single barrier: Screening length of electrodes

- -Composite barrier: Paraelectric layer

L. Wang et al., Nano Letters, 16 (2016) p.3911 © 2016 American Chemical Society [1]

KIOXIA

**Switching Mechanism**

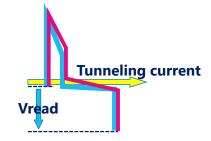

### Depolarization field, E<sub>dep</sub>, modulates potential profile, inducing TER

####

#### Effect of E<sub>dep</sub> on FTJ TER

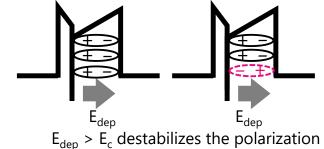

### **E**<sub>dep</sub> is the TER mechanism, but deceasing memory window

#### Ec > Edep required for stable polarization

$$E_c > E_{dep} = \frac{P}{\varepsilon_{FE}\varepsilon_0} \left(1 + \frac{\varepsilon_{PE}t_{FE}}{\varepsilon_{FE}t_{PE}}\right)^{-1}$$

#### Data reading further destabilizes the polarization

$$E_c > E_{dep} = \frac{P}{\varepsilon_{FE}\varepsilon_0} \left( 1 + \frac{\varepsilon_{PE}t_{FE}}{\varepsilon_{FE}t_{PE}} \right)^{-1} + \frac{\varepsilon_{PE}}{\varepsilon_{FE}t_{PE} + \varepsilon_{PE}t_{FE}} V_{read}$$

Voltage application is inevitable to obtain a sufficient amount of tunneling current, but it decreases the TER.

KIOXIA

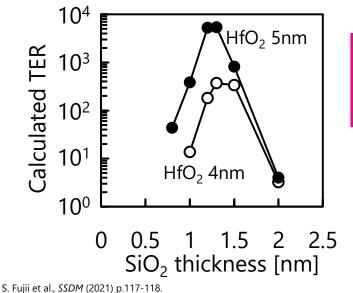

#### TER considering data reading

### Precise stack design is needed to obtain a reasonable amount of TER

✓ FTJ with <u>THIN</u> PE

Weak modulation due to small  $E_{dep}$ .

→ Small TER

✓ FTJ with THICK PE

Larger voltage is needed for detectable read current, leading larger E<sub>dep</sub>.

→ Small TER

S. Fujii et al., *SSDM* (2021) p.117-118. © 2021 The Japan Society of Applied Physics [2]

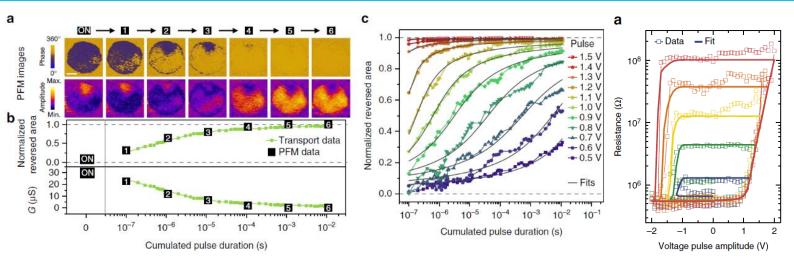

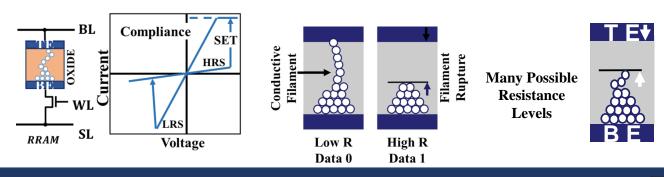

#### **Memristive switching**

# Continuous resistance change due to nucleation and expansion of domains → Opportunity for emerging in-memory computing application

Boyn, S., Grollier, J., Lecerf, G. et al. Learning through ferroelectric domain dynamics in solid-state synapses. Nature Communications 8, 14736 (2017). [3] https://doi.org/10.1038/ncomms14736 https://creativecommons.org/licenses/by/4.0/

KIOXIA

#### **Outline**

- 1. Ferroelectric tunnel junction

- 2. Ferroelectric HfO<sub>2</sub>-based tunnel junction

- 3. FTJ for emerging application

- 4. Summary

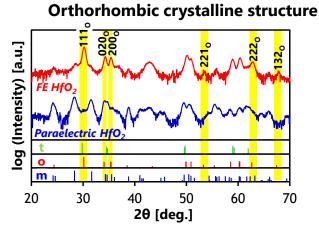

#### Ferroelectric HfO<sub>2</sub>

- → First reported in 2011

- ✓ Most common high-k material in CMOS technology

- → HfO₂ with various dopant (Si, Y, etc), Hf₀,5Zr₀,5O₂

- 10nm or less (much thinner than conventional ferroelectric material such as PZT)

#### XRD of ferroelectric HfO<sub>2</sub>:

#### Displacement of O atoms contributes to ferroelectricity

S. Fujii et al., VLSI Tech. (2016) p.148. © 2016 IEEE [4]

KIOXIA

#### Combination of FTJ with HfO<sub>2</sub>

### HfO<sub>2</sub>-based FTJ: A CMOS compatible emerging non-volatile memory

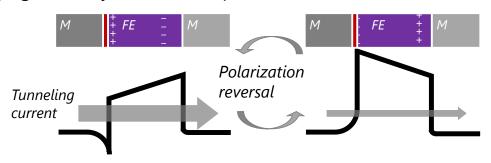

#### **Recent Hafnia-FTJ research**

### Most of HfO<sub>2</sub>-FTJ research is on composite barrier structure

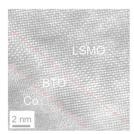

|                         | Fraunhofer                                                     | Namlab/Leti                           | UCB                                     | KAIST                          | SNU/SKH                                                      | IBM                  | U Tokyo                      | WD/UCB                                   |

|-------------------------|----------------------------------------------------------------|---------------------------------------|-----------------------------------------|--------------------------------|--------------------------------------------------------------|----------------------|------------------------------|------------------------------------------|

| Top<br>Electrode        | TiN                                                            | TiN                                   | W                                       | TiN                            | TiN                                                          | TiN                  | Al                           | Pt                                       |

| Ferro                   | HfZrO<br>4~8nm                                                 | HfZrO<br>10nm                         | HfZrO<br>1nm                            | HfZrO<br>~5nm                  | HfOx<br>6nm                                                  | HfZrO                | HfZrO<br>4nm                 | HfZrO<br>~2nm                            |

| Interface<br>layer (PE) | SiO <sub>2</sub><br>or Al <sub>2</sub> O <sub>3</sub><br>1~2nm | Al <sub>2</sub> O <sub>3</sub><br>2nm | SiO <sub>2</sub><br>1nm                 | Ta <sub>2</sub> O <sub>5</sub> | SiO <sub>2</sub><br>or Al <sub>2</sub> O <sub>3</sub><br>1nm | WOx                  | SiO <sub>2</sub><br>1nm      | Semicon<br>ductor                        |

| Bottom electrode        | Si-sub                                                         | TiN                                   | Si-sub                                  | TaN                            | Si-sub                                                       | TiN                  | Si-sub                       | LSMO                                     |

| Reference               | IEEE T-ED<br>2022 [5]                                          | IEEE<br>ISCAS<br>2021 [6]             | Adv.<br>Electron.<br>Mater.<br>2021 [7] | IEDM<br>2021<br>[8]            | Nanotech.<br>2021 [9]                                        | EDTM<br>2021<br>[10] | IEEE<br>JEDS<br>2018<br>[11] | Adv.<br>Electron.<br>Mater.<br>2021 [12] |

KIOXIA 11

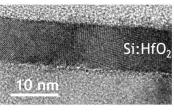

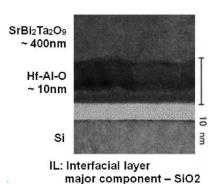

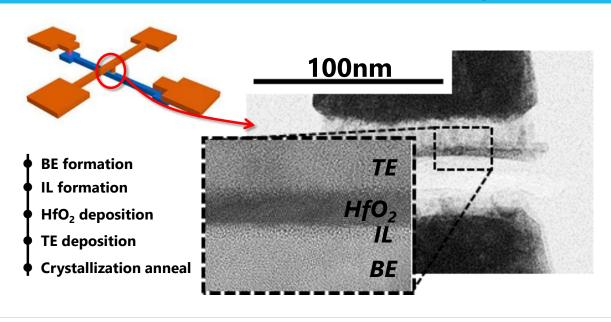

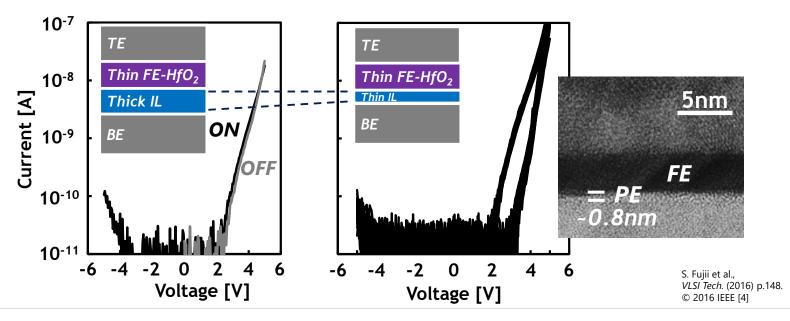

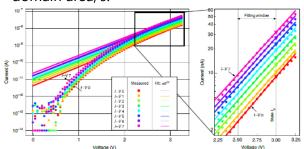

#### Demonstration of HfO<sub>2</sub>-based FTJ: Device structure

#### Simple cross point structure

No current limiter, such as series resistor or transistor, is required

S. Fujii et al., *VLSI Tech*. (2016) p.148. © 2016 IEEE [4]

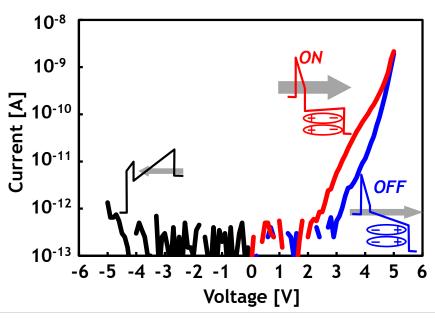

#### Demonstration of HfO<sub>2</sub>-based FTJ: Device performance

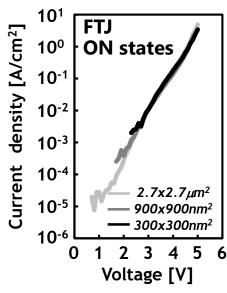

## FTJ performance is suitable for cross-point architecture

#### **Advantages**

- ✓ Low current operation

- ✓ Self compliance

- ✓ Large non-linearity

- ✓ Intrinsic diode

- → Suitable for cross-point architecture

S. Fujii et al., *VLSI Tech.* (2016) p.148. © 2016 IEEE [4]

KIOXIA

13

#### Distinguish from Resistive RAM and Trap Asist Tunneling

# Clear area scaling → Non-filamentary switching No switching without IL → Consistent with FTJ mechanism

S. Fujii et al., *VLSI Tech*. (2016) p.148. © 2016 IEEE [4]

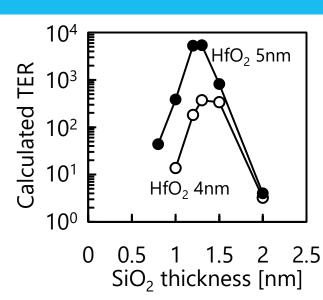

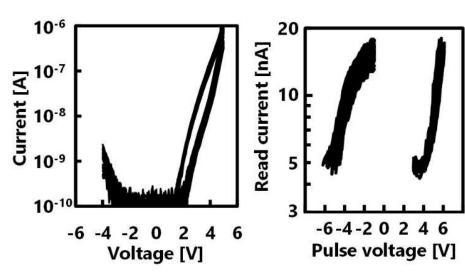

#### **Device design for FTJ with composite barrier**

### Precise stack design is necessary for performance improvement

$E_{dep} = \frac{P}{\varepsilon_{FE}} \left( 1 + \frac{\varepsilon_{IL} t_{FE}}{\varepsilon_{FE} t_{IL}} \right)^{-1} < E_{c}$  $t_{\it FE}$ : FE thickness,  $t_{\it IL}$ : IL thickness

© 2021 The Japan Society of Applied Physics [2]

KIOXIA

#### **Device design for FTJ with composite barrier**

### Thickness design is key for performance improvement

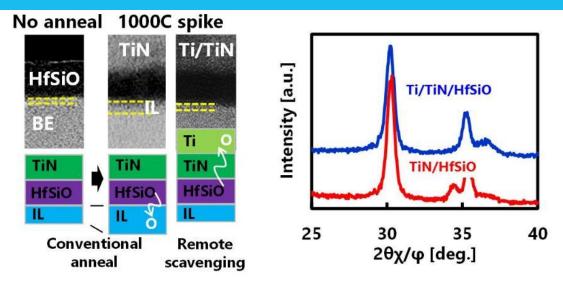

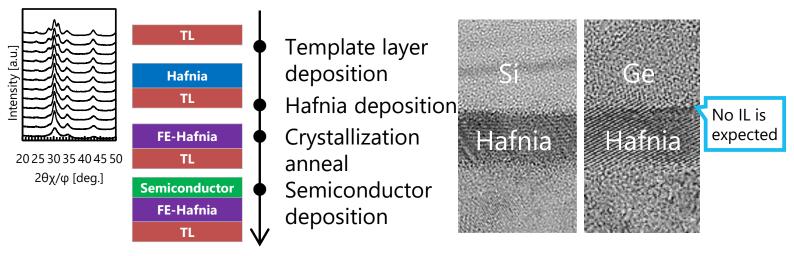

#### Thickness control technique: Remote scavenging

#### Remote scavenging process keeps IL thickness as designed

- -Scavenger Ti traps O during crystallization

- -IL thickness is kept as designed while suppressing monoclinic phase

S. Fujii et al., VLSI Technology 2020, p.1 © 2020 IEEE [13]

KIOXIA

17

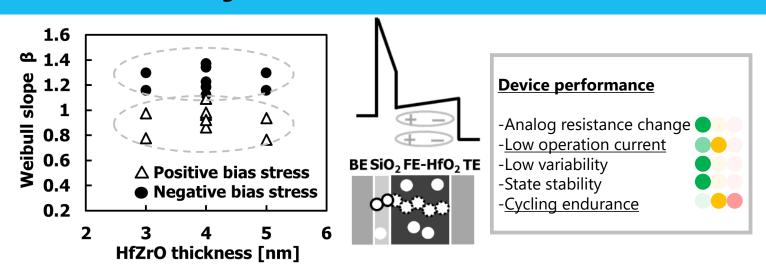

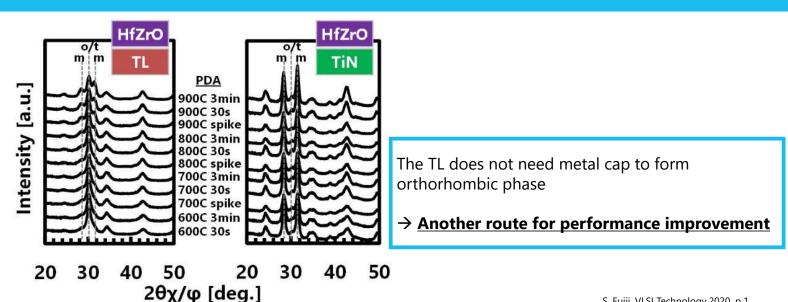

#### Thickness control technique: Template-induced crystallization(TIC)

## TIC reduces crystallization temperature, keeping IL as designed

- -Crystallization temperature is lowered owing to the assist of template layer.

- -Low temperature PMA keeps PE thickness as designed.

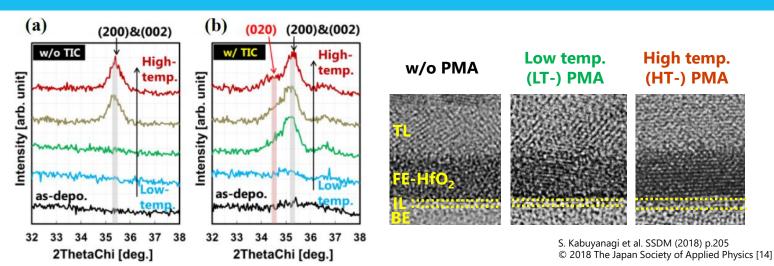

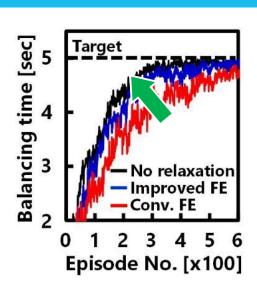

### The improved FTJ shows large TER with low operation current

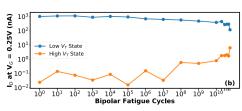

**Device performance**

- -Analog resistance change

- -Low operation current

- -Low variability

- -State stability

- -Cycling endurance

n current is

S. Fujii et al., VLSI Technology 2020, p.1 © 2020 IEEE [13] Although low operation current is mandatory for future low power application, too small read current could degrade operation speed

KIOXIA

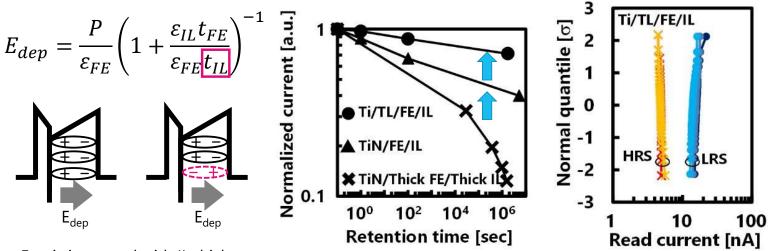

State stability: Long term data retention

## Stable polarization is achieved by decreasing E<sub>dep</sub>

-E<sub>dep</sub> is increased with IL thickness

-Thin IL with the assist of TL and remote scavenging achieves stable polarization

S. Fujii et al., VLSI Technology 2020, p.1 © 2020 IEEE [13]

KIOXIA

2

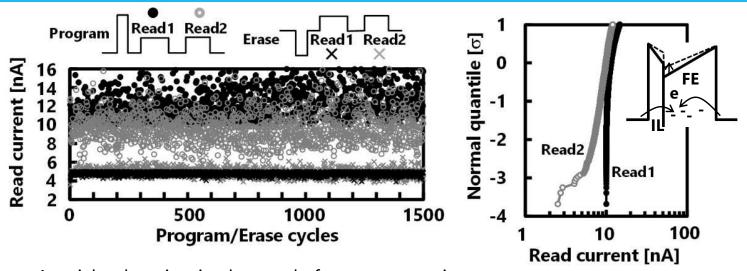

#### State stability: Short term relaxation

### Quick electron trapping in LRS immediately after programming

- A quick relaxation is observed after programming

- Electron trapping increases the effective barrier height

S. Fujii et al., VLSI Technology 2020, p.1 © 2020 IEEE [13]

KIOXIA

FE engineering for suppressing quick relaxation

### Quick relaxation is suppressed by FE process optimization

© 2021 The Japan Society of Applied Physics [2]

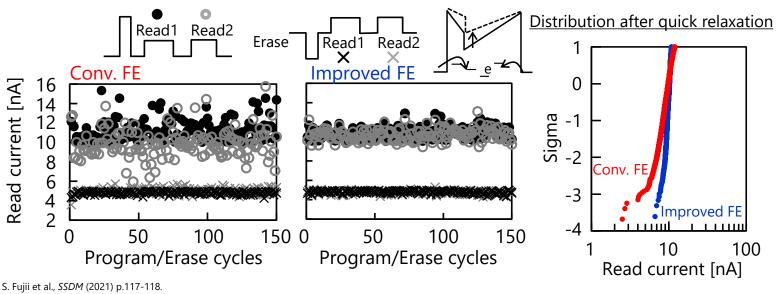

#### Endurance failure can be described as conventional breakdown model

- Endurance failure is caused by breakdown

- M. Yamaguchi et al., IRPS 2018, 6D.2 © 2018 IEEE [15]

- FTJ breakdown is well normalized by Weibull distribution

- Conventional percolation model is applicable

KIOXIA 23

#### Breakdown mechanism of the HfO<sub>2</sub> FTJ

### **Defects generation in IL determines breakdown**

- Weibull slope is independent of the FE thickness → IL determines the breakdown

M. Yamaguchi et al., IRPS 2020 © 2020 IEEE [16]

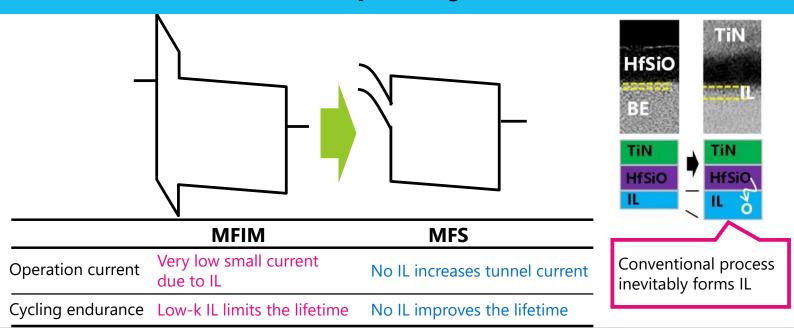

#### To improve the endurance

### MFS structure with no IL is promising, but difficult to realize it

KIOXIA 25

#### **Utilizing TIC for fabricating MFS structure**

## The TL improves controllability of stack structure

S. Fujii, VLSI Technology 2020, p.1 © 2020 IEEE [13]

#### MFS FTJ structure

### Novel process technologies could realize the MFS structure

The MFS FTJ using our novel process technologies could further improve operation current and endurance

S. Fujii et al., SSDM (2021) p.117-118. © 2021 The Japan Society of Applied Physics [2]

KIOXIA

27

#### **Outline**

- 1. Ferroelectric tunnel junction

- 2. Ferroelectric HfO<sub>2</sub>-based tunnel junction

- 3. FTJ for emerging applications

- 4. Summary

#### Memristive switching for emerging applications

### Analog resistance change can be utilized for emerging applications

KIOXIA

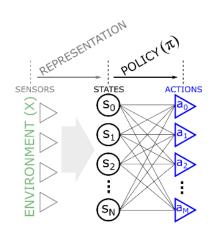

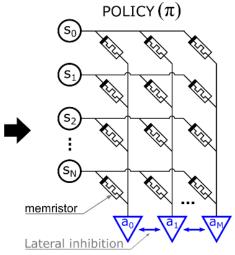

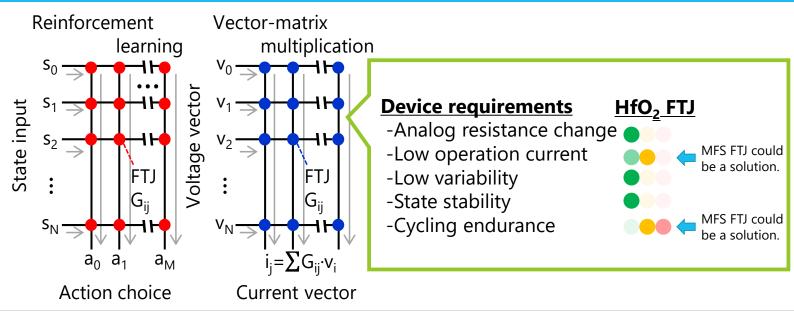

#### **Memristor-based reinforcement learning**

#### Reinforcement learning (RL)

# State **S**t Action ENVIRONMENT **AGENT**

## In-memory RL with memristive FTJ

$s_i : a_{t+1} = \max(G_{ij})$

- Evaluate state  $\rightarrow$  execute action  $\rightarrow$  get reward Maximize the reward by learning

- Requires massive computation

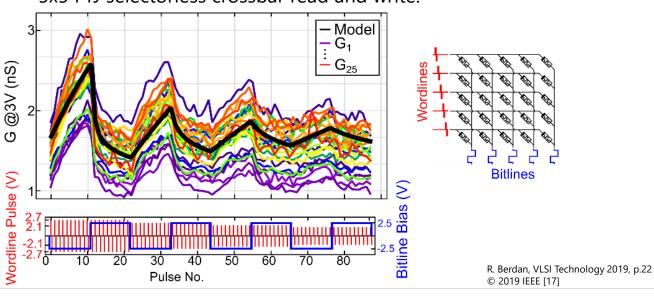

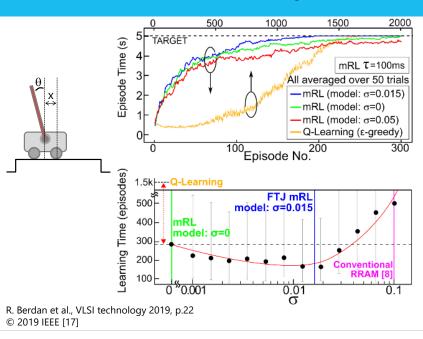

R. Berdan et al., VLSI Tech. 2019, p.22 © 2019 IEEE [17]

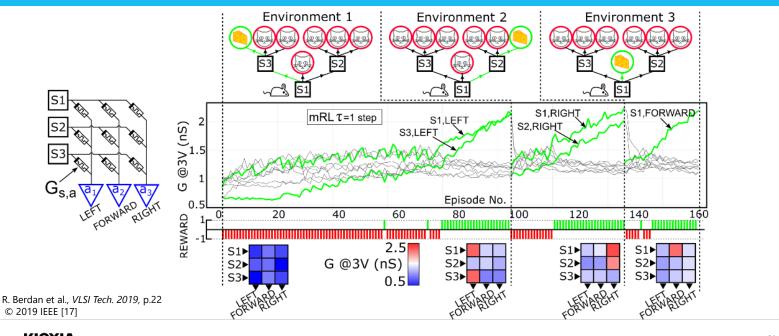

#### In-memory reinforcement learning

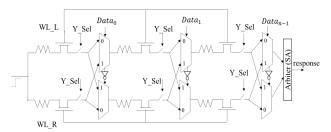

## Path-finding demonstration using FTJ memristor crossbar

KIOXIA

#### Impact of variability and relaxation on learning performance

#### FTJ with moderate variability and reduced relaxation shows better performance

S. Fujii et al., VLSI Technology 2020, p.1 © 2020 IEEE [13]

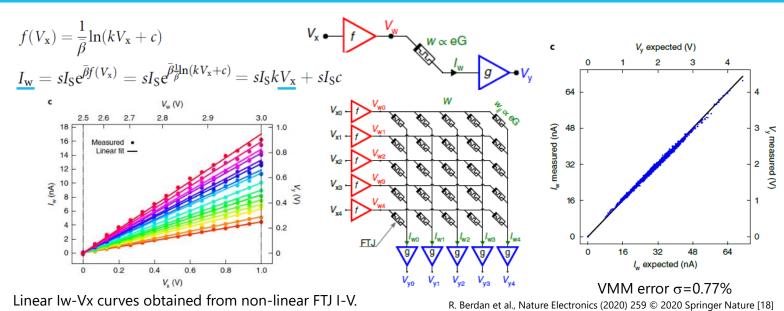

#### **Vector Matrix Multiplication (VMM)**

### Linear computation using FTJ tunneling current

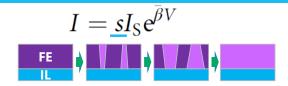

#### Low-power linear computation using nonlinear ferroelectric tunnel junction memristors

Radu Berdan <sup>1,2</sup> ✓, Takao Marukame <sup>1</sup>, Kensuke Ota³, Marina Yamaguchi³, Masumi Saitoh³, Shosuke Fujii3, Jun Deguchi2 and Yoshifumi Nishi1

Analogue in-memory computing using memristors could alleviate the performance constraints imposed by digital von Neumann systems in data-intensive tasks. Conventional linear memristors typically operate at high currents, potentially limiting power efficiency and scalability in practical applications. Here, we show that nonlinear ferroelectric tunnel junction memristors can perform linear computation at ultralow currents. Using logarithmic line drivers, we demonstrate that analogue-voltage-amplitude vector-matrix multiplication (VMM) can be performed in selectorless ferroelectric tunnel junction crossbars by exploiting a device nonlinearity factor that remains constant for multiple conductive states. We also show that our ferroelectric tunnel junction crossbars by exploiting and the conductive states. tion crossbars have the attributes required to scale analogue VMM-intensive applications, such as neural inference en towards energy efficiencies above 100 tera-operations per second per watt.

R. Berdan et al., Nature Electronics (2020) 259 © 2020 Springer Nature [18]

Tunneling current is proportional to conductive domain area, s.

Each state has the same  $\beta$  with different  $\alpha$ (effective conductive area).

**KIOXIA**

#### **Conversion to linear I-V**

**KIOXIA**

## VMM operation owing to low variability of FTJ

#### FTJ for emerging applications

Device performance required for various emerging applications are almost the same HfO<sub>2</sub> FTJ is suitable for those applications

KIOXIA 35

#### **Outline**

- 1. Ferroelectric tunnel junction

- 2. Ferroelectric HfO<sub>2</sub>-based tunnel junction

- 3. FTJ for emerging applications

- 4. Summary

#### Summary

#### **Ferroelectric tunnel junction**

- -Depolarization E<sub>dep</sub> is the TER mechanism.

- -Precise stack design is necessary for reasonable TER.

- -Continuous resistance change owing to nucleation and expansion of the domain.

#### HfO<sub>2</sub> FTJ

- -A CMOS compatible emerging memory, having low operation current, low variability, stable memory state, and analog resistance change.

- -Precise stack design can be realized by sophisticated process technologies

- -Cycling endurance and small read current could be improved using MFS structure

#### FTJ for emerging application

- -Analog resistance change with low variability opened an opportunity for emerging computing application, reinforcement learning and vector-matrix-multiplication.

- -Device performance required for various emerging applications are almost the same, and the HfO<sub>2</sub> FTJ is suitable for those applications.

Company names, product names, and service names may be trademarks of their respective companies.

KIOXIA

#### References

- [1] L. Wang, M. R. Cho, Y. J. Shin, J. R. Kim, S. Das, J-G. Yoon, J-S. Chung, and T. W. Noh, "Overcoming the Fundamental Barrier Thickness Limits of Ferroelectric Tunnel Junctions through BaTiO3/SrTiO3 Composite Barriers", Nano Letters, vol 6 (2016) p.3911-3918.

- [2] S. Fujii, M. Yamaguchi, S. Kabuyanagi, K. Ota, and M. Saitoh, "Hafnia-based Ferroelectric Tunnel Junction for Emerging Applications", SSDM 2021, p117-118.

- [3] S. Boyn, J. Grollier, G. Lecerf, et al. "Learning through ferroelectric domain dynamics in solid-state synapses", Nature Communications 8, 14736 (2017).

- [4] S. Fujii, Y. Kamimuta, T. Ino, Y. Nakasaki, R. Takaishi, and M. Saitoh, "First demonstration and performance improvement of ferroelectric HfO2-based resistive switch with low operation current and intrinsic diode property," 2016 IEEE Symposium on VLSI Technology, 2016, p.148-149.

- [5] A. Sünbül et al., "Optimizing Ferroelectric and Interface Layers in HZO-Based FTJs for Neuromorphic Applications," in IEEE Transactions on Electron Devices, vol. 69, no. 2, pp. 808-815 [6] E. Covi et al., "Ferroelectric Tunneling Junctions for Edge Computing," 2021 IEEE International Symposium on Circuits and Systems (ISCAS), 2021, pp. 1-5 [7] Cheema, S. S., Shanker, N., Hsu, C.-H., Datar, A., Bae, J., Kwon, D., Salahuddin, S., One Nanometer HfO2-Based Ferroelectric Tunnel Junctions on Silicon. Adv. Electron. Mater. 2021,

- [8] Y. Goh, et al., "High Performance and Self-rectifying Hafnia-based Ferroelectric Tunnel Junction for Neuromorphic Computing and TCAM Applications", 2021 IEEE International Electron Devices Meeting (IEDM), 2021 p.378-381

- [9] Kyung Kyu Min et al, "Interlayer engineering for enhanced ferroelectric tunnel junction operations in HfO,-based metal-ferroelectric-insulator-semiconductor stack", 2021 Nanotechnology 32 495203

- [10] L. Bégon-Lours et al., "A BEOL Compatible, 2-Terminals, Ferroelectric Analog Non-Volatile Memory," 2021 5th IEEE Electron Devices Technology & Manufacturing Conference (EDTM),

- [11] M. Kobayashi, Y. Tagawa, F. Mo, T. Saraya and T. Hiramoto, "Ferroelectric HfO2 Tunnel Junction Memory With High TER and Multi-Level Operation Featuring Metal Replacement Process," in IEEE Journal of the Electron Devices Society, vol. 7, pp. 134-139

- [12] Prasad, B., Thakare, V., Kalitsov, A., Zhang, Z., Terris, B., Ramesh, R., Large Tunnel Electroresistance with Ultrathin Hf0.5Zr0.5O2 Ferroelectric Tunnel Barriers. Adv. Electron. Mater. 2021, 7 2001074 [13] S. Fujii, M. Yamaguchi, S. Kabuyanagi, K. Ota, and M. Saitoh, "Improved state stability of HfO2 ferroelectric tunnel junction by template-induced crystallization and remote scavenging

- for efficient in-memory reinforcement learning", 2020 IEEE Symposium on VLSI Technology, 2020, p.1-2 [14] S. Kabuyanagi, S. Fujii, K. Usuda, M. Yamaguchi, T. Ino, Y. Nakasaki, R. Takaishi, Y. Kamimuta, M. Saitoh, "Performance improvement by template-induced crystallization in ferroelectric

- HfO2 tunnel junction memory for cross-point high-density application", SSDM (2018) p.205. [15] M. Yamaguchi, S. Fujii, Y. Kamimuta, S. Kabuyanagi, T. Ino, Y. Nakasaki, R. Takaishi, R. Ichihara, M. Saitoh, "Impact of specific failure mechanisms on endurance improvement for HfO2-

- based ferroelectric tunnel junction memory", IEEE International Reliability Physics Symposium (IRPS), 2018, p. 6D2.1-6D2.6.

- [16] M. Yamaguchi, S. Fujii, K. Ota and M. Śaitoh, "Breakdown Lifetime Analysis of HfO2-based Ferroelectric Tunnel Junction (FTJ) Memory for In-Memory Reinforcement Learning," 2020 IEEE International Reliability Physics Symposium (IRPS), 2020, pp. 1-6

- [17] R. Berdan, T. Marukame, S. Kabuyanagi, K. Ota, M. Saitoh, S. Fujii, J. Deguchi, and Y. Nishi, "In-memory reinforcement learning with moderately-stochastic conductance switching of ferroelectric tunnel junction", 2019 Symposium on VLSI Technology, 2019, p.22-23

- [18] R. Berdan, T. Marukame, K. Ota, M. Yamaguchi, M. Saitoh, S. Fújii, J. Deguchi, and Y. Nishi, "Low-power linear computation using nonlinear ferroelectric tunnel junction memristors", Nature Electronics, vol 3 (2020) p. 259-266.

Onur Mutlu ETH Zurich

Onur Mutlu is a Professor of Computer Science at ETH Zurich. He is also a faculty member at Carnegie Mellon University, where he previously held the Strecker Early Career Professorship. His current broader research interests are in computer architecture, systems, hardware security, and bioinformatics. A variety of techniques he, along with his group and collaborators, has invented over the years have influenced industry and have been employed in commercial microprocessors and memory/storage systems. He obtained his PhD and MS in ECE from the University of Texas at Austin and BS degrees in Computer Engineering and Psychology from the University of Michigan, Ann Arbor. He started the Computer Architecture Group at Microsoft Research (2006-2009) and held various product and research positions at Intel Corporation, Advanced Micro Devices, VMware, and Google. He received the Intel Outstanding Researcher Award, IEEE High Performance Computer Architecture Test of Time Award, the IEEE Computer Society Edward J. McCluskey Technical Achievement Award, ACM SIGARCH Maurice Wilkes Award, the inaugural IEEE Computer Society Young Computer Architect Award, the inaugural Intel Early Career Faculty Award, US National Science Foundation CAREER Award, Carnegie Mellon University Ladd Research Award, faculty partnership awards from various companies, and a healthy number of best paper or "Top Pick" paper recognitions at various computer systems, architecture, and security venues. He is an ACM Fellow "for contributions to computer architecture research, especially in memory systems", IEEE Fellow for "contributions to computer architecture research and practice", and an elected member of the Academy of Europe (Academia Europaea). His computer architecture and digital logic design course lectures and materials are freely available on YouTube (https://www.youtube.com/OnurMutluLectures), and his research group makes a wide variety of software and hardware artifacts freely available online (<a href="https://safari.ethz.ch/">https://safari.ethz.ch/</a>). For more information, please see his webpage at <a href="https://people.inf.ethz.ch/omutlu/">https://people.inf.ethz.ch/omutlu/</a>.

# Security Aspects of DRAM The Story of RowHammer

Onur Mutlu

omutlu@gmail.com

https://people.inf.ethz.ch/omutlu

15 May 2022 IMW Tutorial

SAFARI

Carnegie Mellon

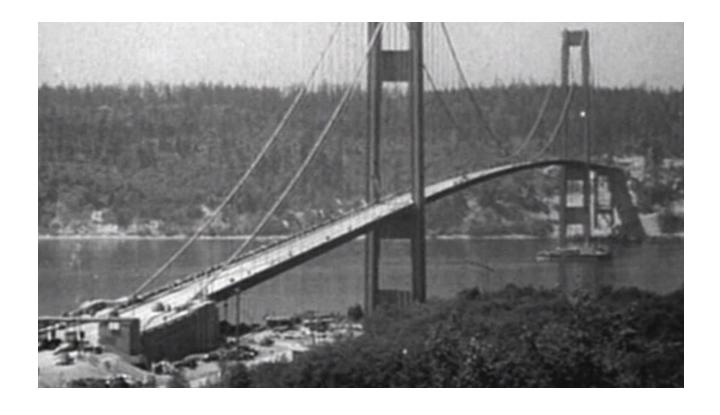

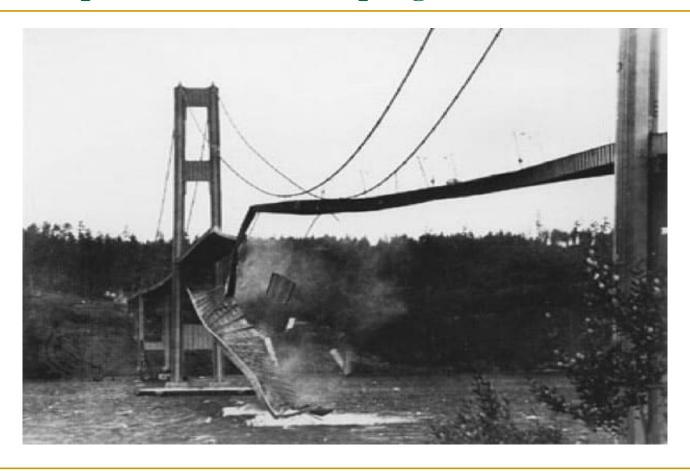

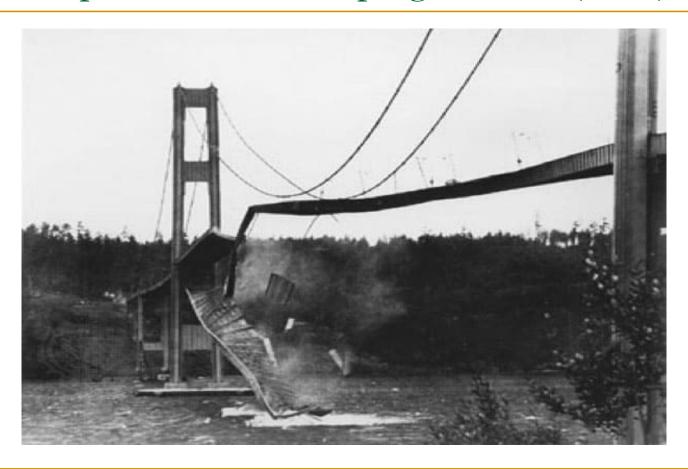

How Reliable/Secure/Safe is This Bridge?

# Collapse of the "Galloping Gertie"

SAFARI

Source: AP http://www.wsdot.wa.gov/tnbhistory/connections/connections3.htm 3

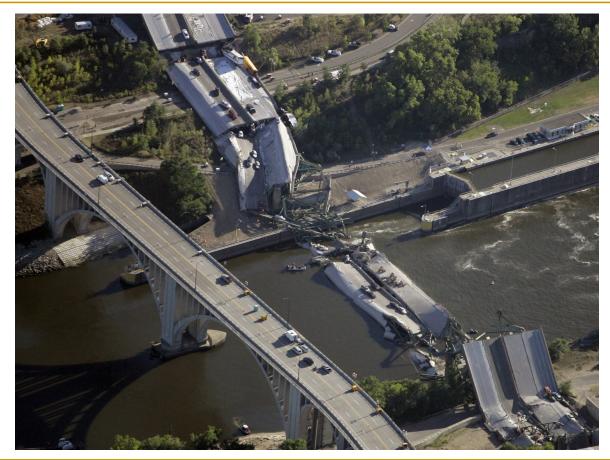

# How Secure Are These People?

## Security is about preventing unforeseen consequences

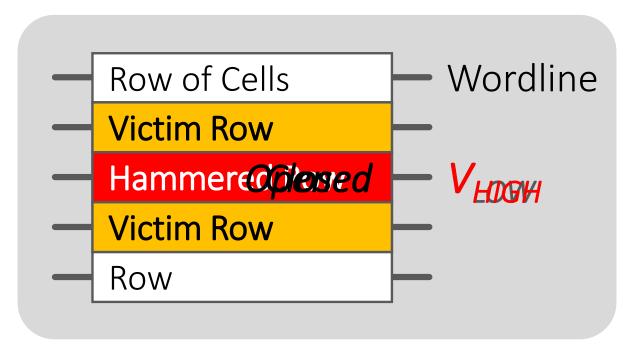

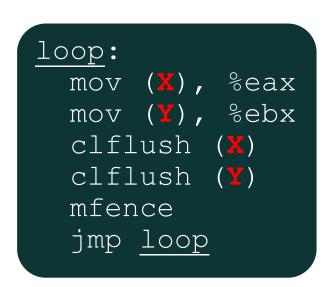

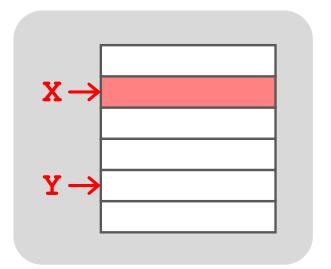

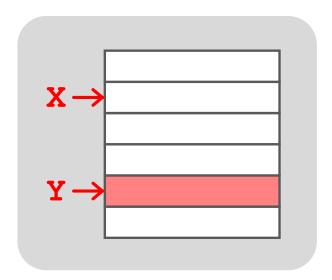

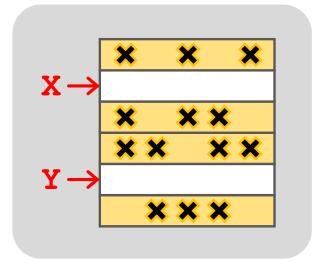

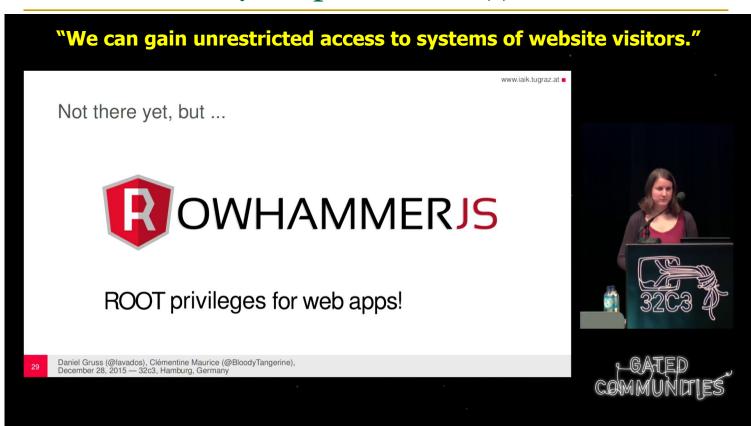

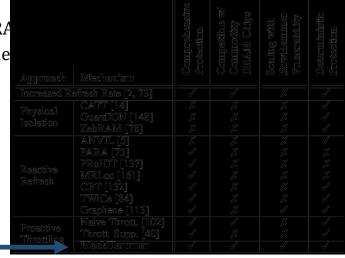

## What Is RowHammer?

- One can predictably induce bit flips in commodity DRAM chips

- □ >80% of the tested DRAM chips are vulnerable

- First example of how a simple hardware failure mechanism can create a widespread system security vulnerability

WIRED

TWEET

Forget Software-Now Hackers Are Exploiting Physics

SHARE

FORGET SOFTWARE—NOW

HACKERS ARE EXPLOITING

PHYSICS

# An "Early" Position Paper [IMW'13]

Onur Mutlu,

"Memory Scaling: A Systems Architecture Perspective"

Proceedings of the 5th International Memory

Workshop (IMW), Monterey, CA, May 2013. Slides

(pptx) (pdf)

EETimes Reprint

## Memory Scaling: A Systems Architecture Perspective

Onur Mutlu

Carnegie Mellon University

onur@cmu.edu

http://users.ece.cmu.edu/~omutlu/

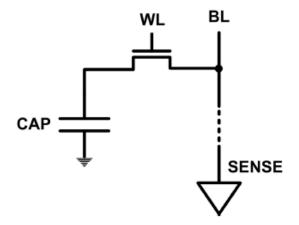

# The DRAM Scaling Problem

- DRAM stores charge in a capacitor (charge-based memory)

- Capacitor must be large enough for reliable sensing

- Access transistor should be large enough for low leakage and high retention time

- Scaling beyond 40-35nm (2013) is challenging [ITRS, 2009]

DRAM capacity, cost, and energy/power hard to scale

SAFARI 7

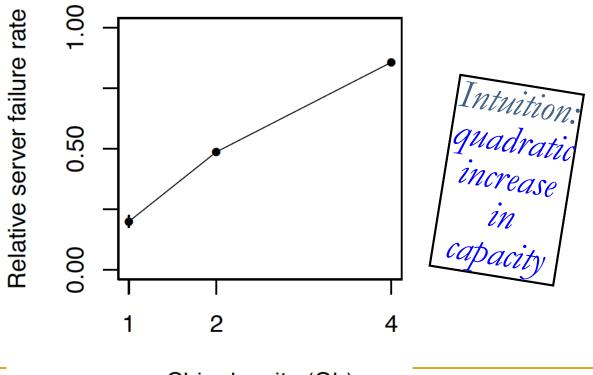

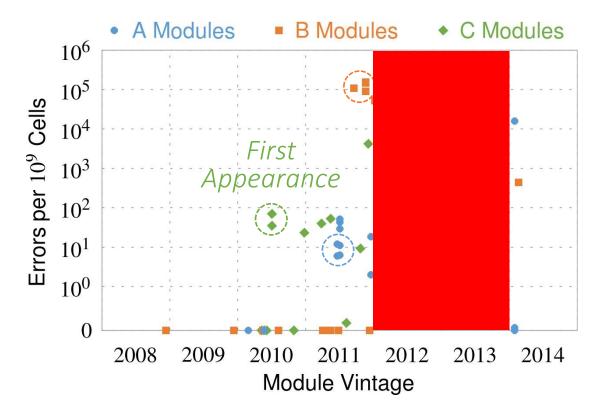

# As Memory Scales, It Becomes Unreliable

- Data from all of Facebook's servers worldwide

- Meza+, "Revisiting Memory Errors in Large-Scale Production Data Centers," DSN'15.

# Large-Scale Failure Analysis of DRAM Chips

- Analysis and modeling of memory errors found in all of Facebook's server fleet

- Justin Meza, Qiang Wu, Sanjeev Kumar, and Onur Mutlu, "Revisiting Memory Errors in Large-Scale Production Data Centers: Analysis and Modeling of New Trends from the Field" Proceedings of the 45th Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN), Rio de Janeiro, Brazil, June 2015.

[Slides (pptx) (pdf)] [DRAM Error Model]

## Revisiting Memory Errors in Large-Scale Production Data Centers: Analysis and Modeling of New Trends from the Field

Justin Meza Qiang Wu\* Sanjeev Kumar\* Onur Mutlu Carnegie Mellon University \* Facebook, Inc.

SAFARI

9

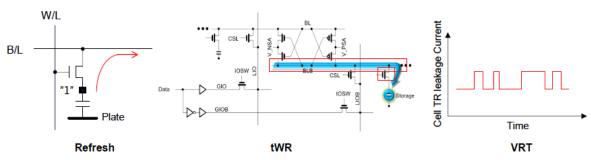

## Infrastructures to Understand Such Issues

Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors (Kim et al., ISCA 2014)

Adaptive-Latency DRAM: Optimizing DRAM Timing for the Common-Case (Lee et al., HPCA 2015)

AVATAR: A Variable-Retention-Time (VRT)

Aware Refresh for DRAM Systems (Qureshi et al., DSN 2015)

An Experimental Study of Data Retention Behavior in Modern DRAM Devices: Implications for Retention Time Profiling Mechanisms (Liu et al., ISCA 2013)

The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A

Comparative Experimental Study

(Khan et al., SIGMETRICS 2014)

## Infrastructures to Understand Such Issues

SAFARI

Kim+, "Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors," ISCA 2014.

11

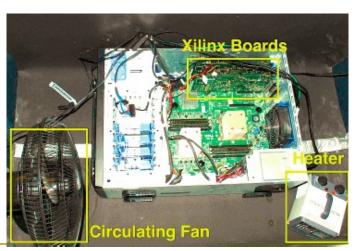

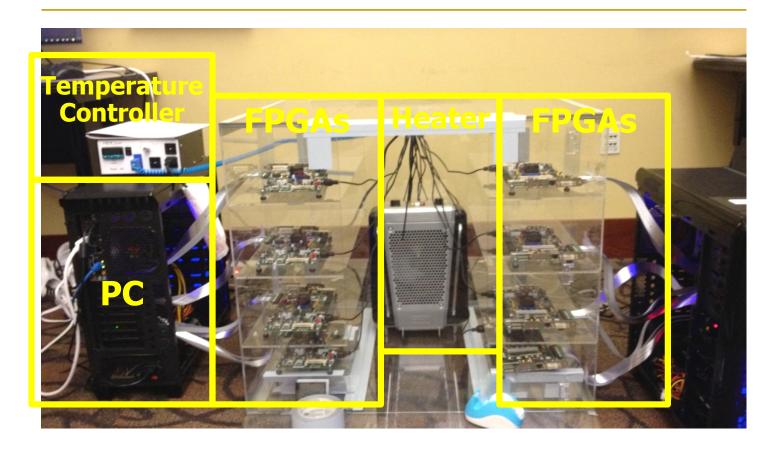

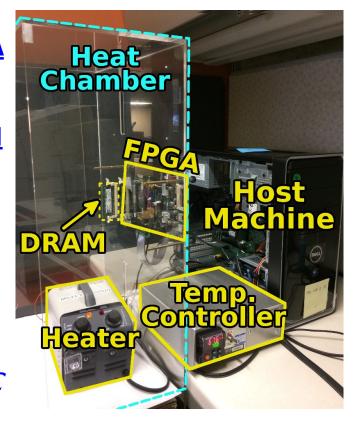

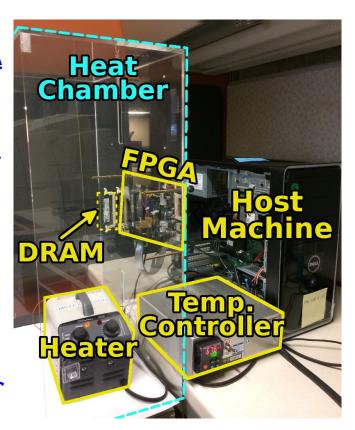

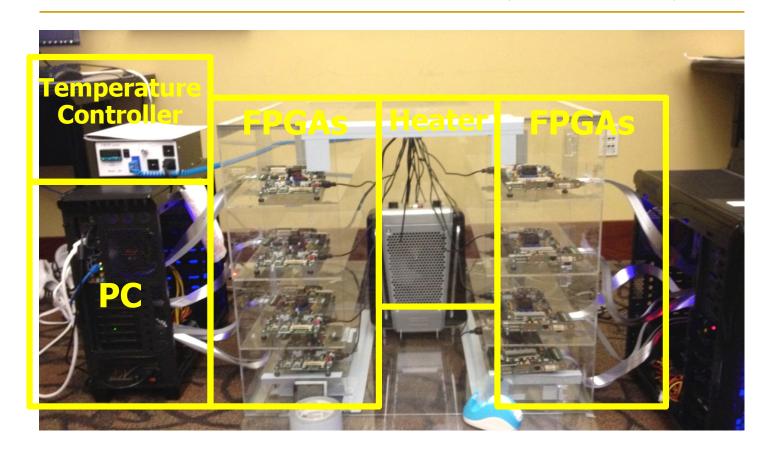

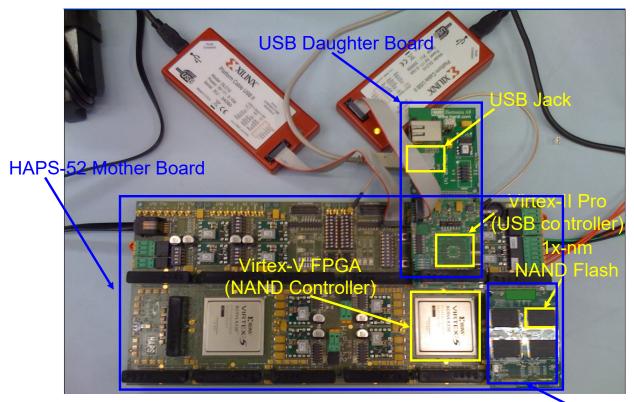

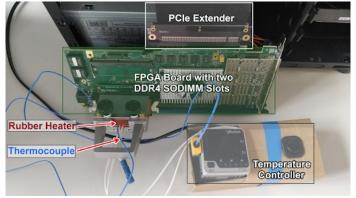

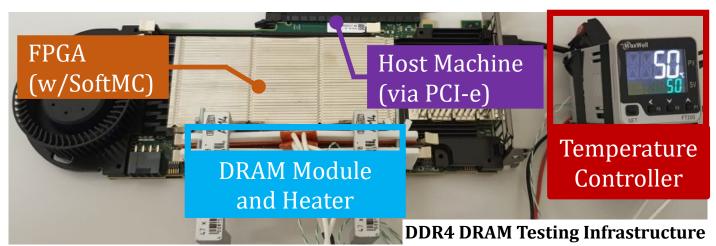

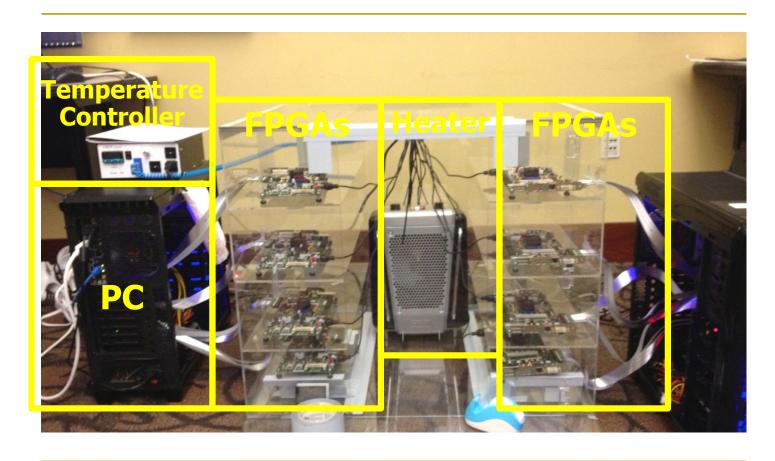

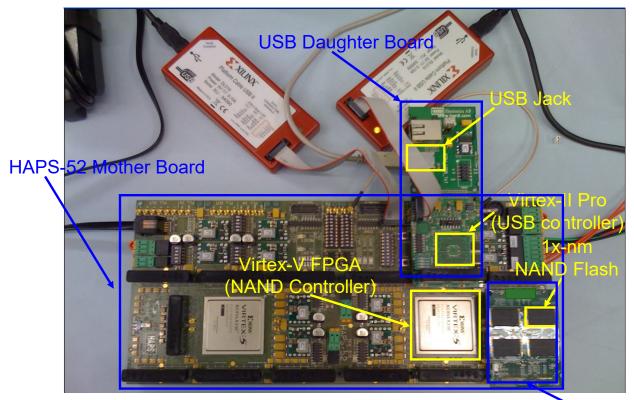

# SoftMC: Open Source DRAM Infrastructure

- Hasan Hassan et al., "SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies," HPCA 2017.

- Flexible

- Easy to Use (C++ API)

- Open-source github.com/CMU-SAFARI/SoftMC

SAFARI 12

## SoftMC: Open Source DRAM Infrastructure

https://github.com/CMU-SAFARI/SoftMC

# SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies

Hasan Hassan $^{1,2,3}$  Nandita Vijaykumar $^3$  Samira Khan $^{4,3}$  Saugata Ghose $^3$  Kevin Chang $^3$  Gennady Pekhimenko $^{5,3}$  Donghyuk Lee $^{6,3}$  Oguz Ergin $^2$  Onur Mutlu $^{1,3}$

$^1ETH$  Zürich  $^2TOBB$  University of Economics & Technology  $^3C$  arnegie Mellon University  $^4U$ niversity of Virginia  $^5M$ icrosoft Research  $^6NVIDIA$  Research

SAFARI 13

# SoftMC: Open Source DRAM Infrastructure

https://github.com/CMU-SAFARI/SoftMC

# SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies

Hasan Hassan  $^{1,2,3}$  Nandita Vijaykumar  $^3$  Samira Khan  $^{4,3}$  Saugata Ghose  $^3$  Kevin Chang  $^3$  Gennady Pekhimenko  $^{5,3}$  Donghyuk Lee $^{6,3}$  Oguz Ergin  $^2$  Onur Mutlu  $^{1,3}$

<sup>1</sup>ETH Zürich <sup>2</sup>TOBB University of Economics & Technology <sup>3</sup>Carnegie Mellon University <sup>4</sup>University of Virginia <sup>5</sup>Microsoft Research <sup>6</sup>NVIDIA Research

SAFARI 1-

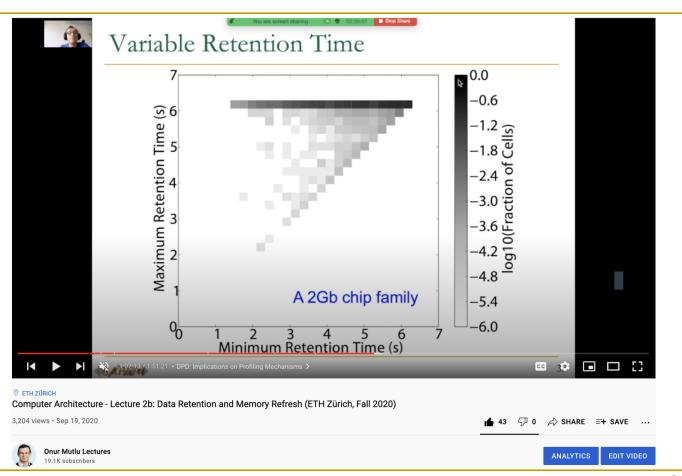

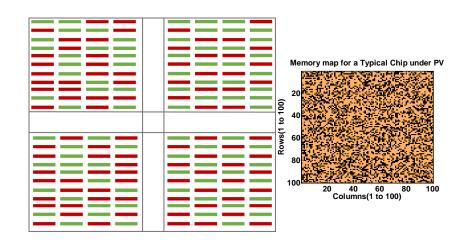

# Data Retention in Memory [Liu et al., ISCA 2013]

Retention Time Profile of DRAM looks like this:

64-128ms

>256ms

128-256ms

**Stored value pattern** dependent **Time** dependent

SAFARI

Liu+, "RAIDR: Retention-Aware Intelligent DRAM Refresh," ISCA 2012.

15

## RAIDR: Heterogeneous Refresh [ISCA'12]

Jamie Liu, Ben Jaiyen, Richard Veras, and Onur Mutlu, "RAIDR: Retention-Aware Intelligent DRAM Refresh" Proceedings of the <u>39th International Symposium on</u> <u>Computer Architecture</u> (ISCA), Portland, OR, June 2012. <u>Slides (pdf)</u>

## RAIDR: Retention-Aware Intelligent DRAM Refresh

Jamie Liu Ben Jaiyen Richard Veras Onur Mutlu Carnegie Mellon University

# Analysis of Data Retention Failures [ISCA'13]

Jamie Liu, Ben Jaiyen, Yoongu Kim, Chris Wilkerson, and Onur Mutlu, "An Experimental Study of Data Retention Behavior in Modern DRAM **Devices: Implications for Retention Time Profiling Mechanisms**" Proceedings of the 40th International Symposium on Computer Architecture (ISCA), Tel-Aviv, Israel, June 2013. Slides (ppt) Slides (pdf)

## An Experimental Study of Data Retention Behavior in **Modern DRAM Devices:** Implications for Retention Time Profiling Mechanisms

Jamie Liu Carnegie Mellon University 5000 Forbes Ave. Pittsburgh, PA 15213 jamiel@alumni.cmu.edu

Ben Jaiyen Carnegie Mellon University 5000 Forbes Ave. Pittsburgh, PA 15213 bjaiyen@alumni.cmu.edu

Yoongu Kim Carnegie Mellon University 5000 Forbes Ave. Pittsburgh, PA 15213 yoonguk@ece.cmu.edu

Chris Wilkerson **Intel Corporation** 2200 Mission College Blvd. Santa Clara, CA 95054 chris.wilkerson@intel.com

Onur Mutlu Carnegie Mellon University 5000 Forbes Ave. Pittsburgh, PA 15213 onur@cmu.edu

## Mitigation of Retention Issues [SIGMETRICS'14]

Samira Khan, Donghyuk Lee, Yoongu Kim, Alaa Alameldeen, Chris Wilkerson, and Onur Mutlu,

"The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study"

Proceedings of the ACM International Conference on Measurement and Modeling of Computer Systems (SIGMETRICS), Austin, TX, June 2014. [Slides (pptx) (pdf)] [Poster (pptx) (pdf)] [Full data sets]

## The Efficacy of Error Mitigation Techniques for DRAM Retention Failures: A Comparative Experimental Study

Samira Khan<sup>†</sup>∗ samirakhan@cmu.edu

Donghyuk Lee<sup>†</sup> donghyuk1@cmu.edu

Yoongu Kim<sup>†</sup> yoongukim@cmu.edu

Alaa R. Alameldeen\* alaa.r.alameldeen@intel.com chris.wilkerson@intel.com

Chris Wilkerson\*

Onur Mutlu† onur@cmu.edu

<sup>†</sup>Carnegie Mellon University

\*Intel Labs

## Mitigation of Retention Issues [DSN'15]

Moinuddin Qureshi, Dae Hyun Kim, Samira Khan, Prashant Nair, and Onur Mutlu,

"AVATAR: A Variable-Retention-Time (VRT) Aware Refresh for DRAM Systems"

Proceedings of the <u>45th Annual IEEE/IFIP International Conference on</u> <u>Dependable Systems and Networks</u> (**DSN**), Rio de Janeiro, Brazil, June 2015.

[Slides (pptx) (pdf)]

# AVATAR: A Variable-Retention-Time (VRT) Aware Refresh for DRAM Systems

Moinuddin K. Qureshi<sup>†</sup> Dae-Hyun Kim<sup>†</sup>

Georgia Institute of Technology

{moin, dhkim, pnair6}@ece.gatech.edu

Samira Khan‡

Prashant J. Nair<sup>†</sup> Onur Mutlu<sup>‡</sup>

<sup>‡</sup>Carnegie Mellon University

{samirakhan, onur}@cmu.edu

19

SAFARI SAFARI

# Mitigation of Retention Issues [DSN'16]

Samira Khan, Donghyuk Lee, and Onur Mutlu,

"PARBOR: An Efficient System-Level Technique to Detect Data-Dependent Failures in DRAM"

Proceedings of the <u>45th Annual IEEE/IFIP International Conference on</u>

<u>Dependable Systems and Networks</u> (**DSN**), Toulouse, France, June 2016.

[Slides (pptx) (pdf)]

# PARBOR: An Efficient System-Level Technique to Detect Data-Dependent Failures in DRAM

Samira Khan\* Donghyuk Lee<sup>†‡</sup>

\*University of Virginia <sup>†</sup>Carnegie Mellon University

Onur Mutlu\*†

\*Nvidia \*ETH Zürich

SAFARI

# Mitigation of Retention Issues [MICRO'17]

Samira Khan, Chris Wilkerson, Zhe Wang, Alaa R. Alameldeen, Donghyuk Lee, and Onur Mutlu,

"Detecting and Mitigating Data-Dependent DRAM Failures by Exploiting Current Memory Content"

Proceedings of the <u>50th International Symposium on Microarchitecture</u> (**MICRO**), Boston, MA, USA, October 2017.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Poster (pptx) (pdf)]

# Detecting and Mitigating Data-Dependent DRAM Failures by Exploiting Current Memory Content

Samira Khan\* Chris Wilkerson<sup>†</sup> Zhe Wang<sup>†</sup> Alaa R. Alameldeen<sup>†</sup> Donghyuk Lee<sup>‡</sup> Onur Mutlu\*

\*University of Virginia <sup>†</sup>Intel Labs <sup>‡</sup>Nvidia Research \*ETH Zürich

#### SAFARI

# Mitigation of Retention Issues [ISCA'17]

- Minesh Patel, Jeremie S. Kim, and Onur Mutlu,

"The Reach Profiler (REAPER): Enabling the Mitigation of DRAM

Retention Failures via Profiling at Aggressive Conditions"

Proceedings of the 44th International Symposium on Computer

Architecture (ISCA), Toronto, Canada, June 2017.

[Slides (pptx) (pdf)]

[Lightning Session Slides (pptx) (pdf)]

- First experimental analysis of (mobile) LPDDR4 chips

- Analyzes the complex tradeoff space of retention time profiling

- Idea: enable fast and robust profiling at higher refresh intervals & temperatures

## The Reach Profiler (REAPER): Enabling the Mitigation of DRAM Retention Failures via Profiling at Aggressive Conditions

Minesh Patel<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> Onur Mutlu<sup>§‡</sup> ETH Zürich <sup>‡</sup>Carnegie Mellon University

# Mitigation of Retention Issues [DSN'19]

Minesh Patel, Jeremie S. Kim, Hasan Hassan, and Onur Mutlu, "Understanding and Modeling On-Die Error Correction in Modern DRAM: An Experimental Study Using Real Devices" Proceedings of the 49th Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN), Portland, OR, USA, June 2019.

[Source Code for EINSim, the Error Inference Simulator] **Best paper award.**

# Understanding and Modeling On-Die Error Correction in Modern DRAM: An Experimental Study Using Real Devices

Minesh Patel $^{\dagger}$  Jeremie S. Kim $^{\ddagger\dagger}$  Hasan Hassan $^{\dagger}$  Onur Mutlu $^{\dagger\ddagger}$   $^{\dagger}ETH$  Zürich  $^{\ddagger}Carnegie$  Mellon University

#### SAFARI

# Mitigation of Retention Issues [MICRO'20]

Minesh Patel, Jeremie S. Kim, Taha Shahroodi, Hasan Hassan, and Onur Mutlu,

"Bit-Exact ECC Recovery (BEER): Determining DRAM On-Die ECC

Functions by Exploiting DRAM Data Retention Characteristics"

Proceedings of the 53rd International Symposium on

Microarchitecture (MICRO), Virtual, October 2020.

[Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[Talk Video (15 minutes)]

[Lightning Talk Video (1.5 minutes)]

Best paper award.

# Bit-Exact ECC Recovery (BEER): Determining DRAM On-Die ECC Functions by Exploiting DRAM Data Retention Characteristics

Minesh Patel $^{\dagger}$  Jeremie S. Kim $^{\ddagger\dagger}$  Taha Shahroodi $^{\dagger}$  Hasan Hassan $^{\dagger}$  Onur Mutlu $^{\dagger\ddagger}$   $^{\dagger}$ ETH Zürich  $^{\ddagger}$ Carnegie Mellon University

## Mitigation of Retention Issues [MICRO'21]

Minesh Patel, Geraldo F. de Oliveira Jr., and Onur Mutlu,

"HARP: Practically and Effectively Identifying Uncorrectable Errors in Memory Chips That Use On-Die Error-Correcting Codes"

Proceedings of the <u>54th International Symposium on Microarchitecture</u> (**MICRO**), Virtual, October 2021.

[Slides (pptx) (pdf)]

[Short Talk Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[Talk Video (20 minutes)]

[Lightning Talk Video (1.5 minutes)]

[HARP Source Code (Officially Artifact Evaluated with All Badges)]

# HARP: Practically and Effectively Identifying Uncorrectable Errors in Memory Chips That Use On-Die Error-Correcting Codes

Minesh Patel ETH Zürich Geraldo F. Oliveira ETH Zürich Onur Mutlu ETH Zürich

25

## More on DRAM Refresh & Data Retention

## SoftMC: Enabling DRAM Infrastructure

Hasan Hassan et al., "SoftMC: A Flexible and Practical Open-Source Infrastructure for Enabling Experimental DRAM Studies," HPCA 2017.

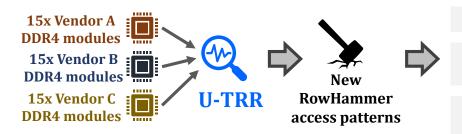

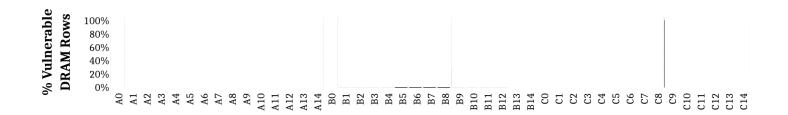

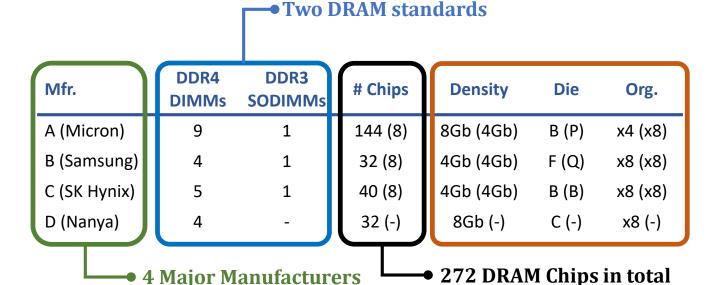

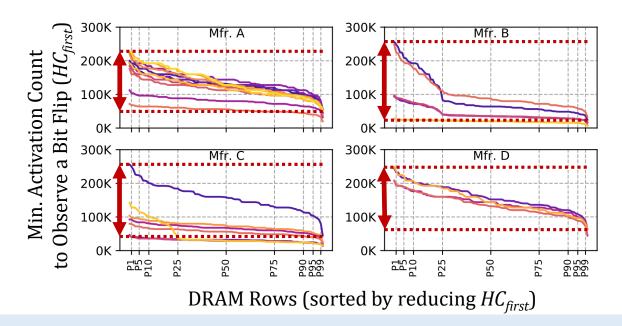

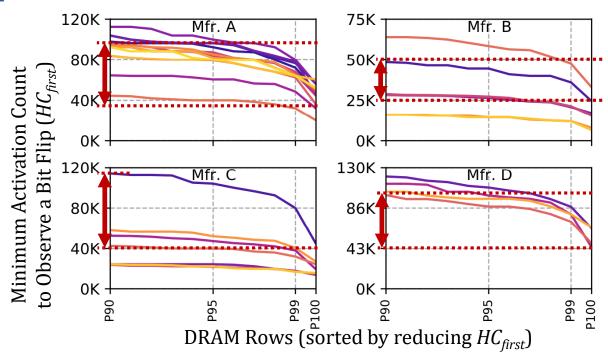

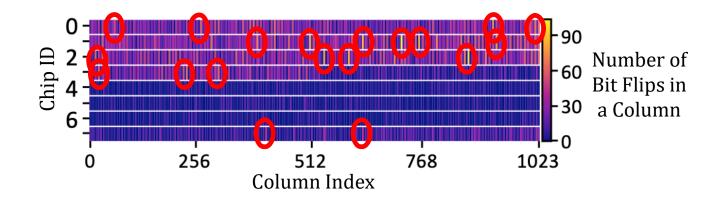

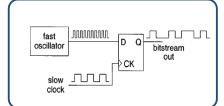

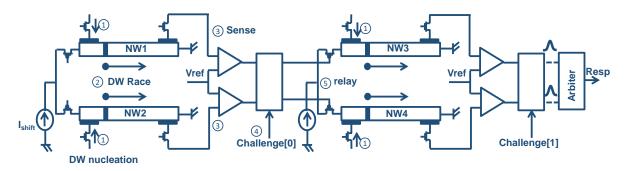

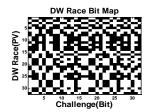

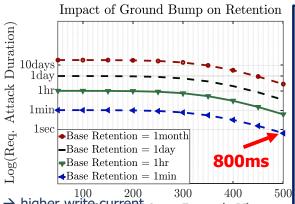

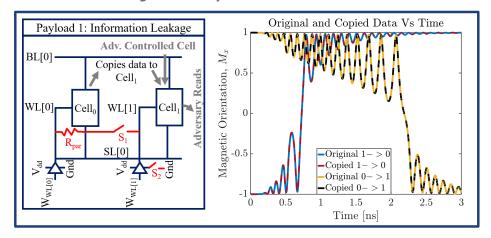

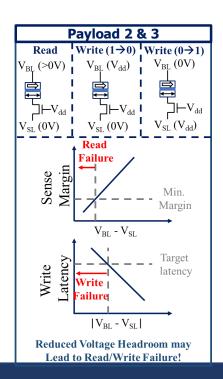

- Flexible