# Ultrafast Charge Trap-based Volatile Memory Cell with Schottky Barrier S/D and Thin Tunnel Oxide

Hyeongyu Kim<sup>1\*</sup>, Dabok Lee<sup>2\*</sup>, Hyun-Sik Choi<sup>3</sup>, Yoojin Seol<sup>1</sup>, Jonghyeon Ha<sup>2</sup>, Sung-Il Chang<sup>4</sup>, Kihyun Kim<sup>1</sup>, Jungsik Kim<sup>2</sup>, Won-Ju Cho<sup>3</sup>, Zvi Or-Bach<sup>4</sup>

<sup>1</sup>Division of Electronic Engineering, Jeonbuk National University, Jeonju, Jeonbuk, 54896, Rep. of Korea <sup>2</sup>Department of Electrical Engineering, Gyeongsang National University, Jinju, Gyeongnam, 52828, Republic of Korea <sup>3</sup>Electronic Materials Engineering, Kwangwoon University, Seoul, 01897, Rep. of Korea <sup>4</sup>MonolithIC3D, Klamath Falls, OR 97601, United States

\*: Equal contribution; Corresponding E-mail: <a href="mailto:sung.il@monolithic3d.com">sung.il@monolithic3d.com</a>

Abstract—In this paper, we propose a novel 3D Charge Trap-based DRAM (CT DRAM) having great advantages on power consumption and heat dissipation. Schottky barrier-induced hot carrier injection and ultrathin tunnel oxide were used for fast write operation. Microwave anneal (MWA) shows better silicide formation (low resistance and high diode on/off ratio) than conventional rapid-thermal annealing (RTA) and its volume heating is quite effective for 3D integrated devices. We designed key parameters (Schottky barrier height, ONO thickness, and trap characteristics) with 3D TCAD simulation and fabricated the planar device having poly-Si channel to explore 3D integration. The device is expected to have a program/erase window larger than 2 V below 10 ns write pulse, and retention time longer than 10s@85°C, and >0.22V window after 10<sup>15</sup> cycles.

## I. INTRODUCTION

The current technology of 10-nm saddle-fin-based DRAM has reached the limit of miniaturization due to various reasons, such as the limitation of meeting the minimum line resistance and capacitance values and the reliability problem of bit flip due to row hammer [1-2]. Although various attempts are also being made to develop next-generation 3D DRAMs, 1T1C 3D DRAM is extremely hard to integrate, and 2T IGZO 3D DRAM is not cost-effective for over several hundreds of layers [1, 3]. Therefore, developing a DRAM structure with a straightforward 3D integration scheme like 3D NAND is essential to achieve higher bit density [4].

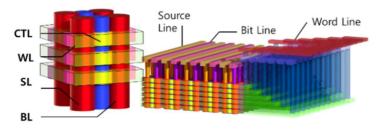

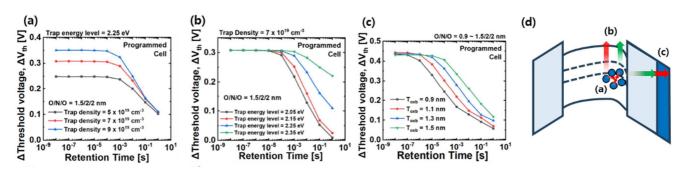

In this paper, we present a novel 3D charge trap-based memory cell structure as a next-generation DRAM, as shown in Fig. 1. It uses an ONO structure instead of a capacitor and a metal silicide source/drain (S/D) for hot carrier injection (HCI) [5]. Based on parameters optimized by TCAD simulation, 2D device was fabricated and their operating speed and reliability were measured to verify the feasibility of 3D memory cells.

# II. DEVICE DESIGN OF 3D DRAM

### A. Structure design

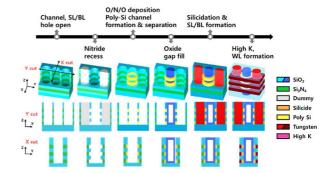

Fig. 2. summarizes the main process flow of the 3D CT DRAM devices. The key processes are a thin tunnel oxide, donut-type poly-Si channel and metal silicidation. We deposit O/N/O and poly-Si sequentially on the nitride-indented mold with holes. Following poly-Si etch results in the formation of

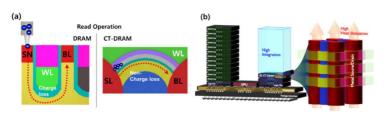

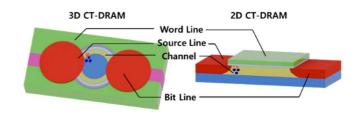

the separated donut-type poly-Si channels in the recessed region. The process sequence used to form the poly-Si islands is already verified through the mass production of the floating-gate type 3D NAND devices from Intel and it is a highly reliable process [6-7]. Metal silicide is formed at the both ends of the poly-Si channel in the SL and BL sides. The proposed structure has strong advantages in power consumption and heat dissipation, which are the most important aspects for high-performance DRAM like HBM. Fig. 3. (a) shows its power advantage. It consumes less power than the conventional 1T1C DRAM cell because it does not lose charges during the read operation and does not need to be restored. The CT DRAM without capacitors can achieve extremely high integration density and metal S/Ds is very effective to dissipate heat from the underlying logic die as shown in Fig. 3 (b).

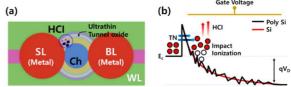

Fig. 4. (a) shows the cross-sectional device structure of the 3D CT DRAM and Fig 4. (b) shows its program operation. It is very hard for the poly-Si channel transistors to make hot electrons at the drain side because of many grain boundaries and trap sites. But if we utilize the SB at the source side, we can make hot carriers easily even with the poly-Si channel. The electrons injected through the SB gain additional energy and result in impact ionization by the steep E-field on the source side to form electron-hole pairs (EHPs).

# B. Optimization of device parameters

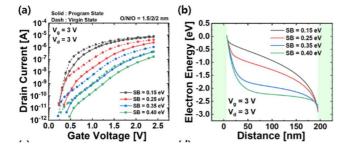

We optimized the process/device parameters of the 3D CT DRAM with 3D TCAD simulation. Fig. 5. (a) and (b) show the simulated  $I_d\text{-}V_g$  curves and the energy band diagrams along with various SB heights, respectively. The larger SB height is, the steeper band bending occurs on the source side but on-state current is decreased because of decreased carrier tunneling. Considering the program characteristics and the on-current, SB of around 0.25 eV is good for the device. For  $T_{\text{oxb}}$  between 0.9 nm and 1.5 nm, the variation in threshold voltage ( $V_{\text{th}}$ ) and electrostatic potential is small as shown in Fig. 5. (c), which means that the difference in vertical and lateral E-fields required for HCI is also negligible as shown in Fig. 5. (d).

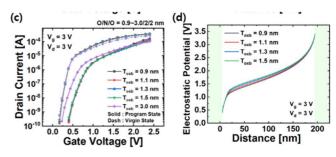

Fig. 6. (a) shows the retention time as a function of the trap density of charge trap layer (CTL). A high trap density increases the number of electrons trapped in the CTL, resulting in a higher initial  $V_{th}$ . Fig. 6. (b) shows the retention time as a function of trap energy level. High trap energy level improves

retention time because a deep trap is formed, requiring high energy for electrons to escape from the trap. In Fig. 6. (c), we can see that the thicker  $T_{oxb}$  leads to an increase in the energy to escape to the channel beyond the tunnel oxide, which improves the retention time.  $T_{oxb}$  around 1 nm is good enough considering the proper retention characteristics for DRAM. Fig. 6. (d) summarizes the mechanism of electron leakage.

The process target values were set based on the simulation result, and the detailed parameters are shown in Table 1.

#### III. DEVICE FABRICATION

The feasibility of the 3D CT DRAM was verified by fabricating and measuring CT DRAM devices with planar structures as shown in Fig. 7.

#### A. Schottky barrier silicide formation

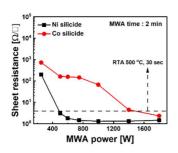

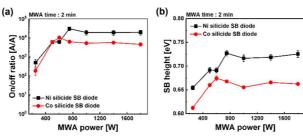

In this study we formed silicides by using Microwave annealing (MWA). MWA utilizes electromagnetic radiation to heat the materials, offering the advantage of achieving uniform volume heating [8]. The sheet resistance ( $R_s$ ) and junction characteristics of the silicide were examined as a function of microwave power. Fig. 8 depicts the sheet resistance of Ni and Co-silicide according to MWA conditions. Overall, Ni-silicide exhibits lower  $R_s$  compared to Co-silicide. Fig. 9. (a) and (b) show the on/off current ratio and SB heights ( $\phi_b$ ) of the SB diodes, respectively. On/off currents were extracted from 5 V and averaging reverse current, respectively.  $\phi_b$  was extracted using the following equation (1).

$$\phi_b = \frac{kT}{q} \ln(\frac{A^{**}T^2}{J_0}) \tag{1}$$

Where q, k, T,  $A^{**}$ , and  $J_0$  are the unit electron charge, Boltzmann's constant, absolute temperature, equivalent Richardson's constant, and reverse saturation current density, respectively. In this study, we applied Ni, which exhibits a relatively higher on/off current ratio, SB heights, and lower  $R_s$ . SB height can be further adjusted by optimizing the stoichiometry of Ni silicide [9-10].

# B. Device integration

Fig. 10 illustrates the fabrication of the 2D CT DRAM device. Buried oxide and active poly-Si layers were formed on the substrate. After the active region was formed, N/O layers and n+ poly-Si gate were formed. Then, ON spacer was formed to isolate gate and S/D regions during following self-aligned silicidation process. Finally, nickel was deposited using an Electron Beam Evaporator, and MWA was performed to form a silicide with low contact resistance. The unreacted Ni was removed.

## IV. RESULTS AND DISCUSSIONS

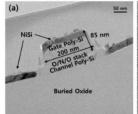

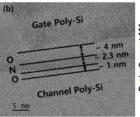

Fig. 11. (a) shows the cross-sectional TEM image of the fabricated device. NiSi was formed successfully at the gate, source, and drain. The S/D regions were fully silicided and its thickness is 20 nm. The gate spacer of 15 nm can be further reduced to decrease the non-overlap length between the gate and the NiSi S/D. Fig. 11. (b) illustrates the thickness of the

ONO layer, with the tunnel oxide, trap layer, and blocking oxide layers of 1, 2.3, and 4 nm, respectively.

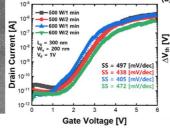

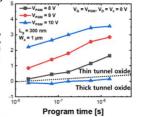

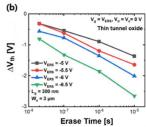

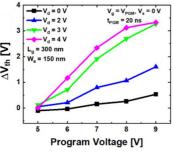

Fig. 12 illustrates the I<sub>d</sub>-V<sub>g</sub> curves of the 2D CT DRAM devices utilizing MWA at different time and power levels. As mentioned earlier, we used 600 W/1 min of MWA condition considering the lateral growth of NiSi as well as on-current of the devices. Fig. 13. (a) compares the program characteristics of the device with a tunnel oxide thickness of 1 nm to that with a thickness of 2.9 nm. The device with T<sub>oxb</sub> of 1 nm showed as fast program speed as V<sub>th</sub> shift of 2 V even at the program time of 20  $ns@V_{GS} = 10$  V. Fig. 13. (b) shows the erase characteristics of the device as a function of erase time and voltage. The device with a Toxb of 1 nm demonstrated a fast erase speed with a V<sub>th</sub> change of approximately -0.8 V at an erase time of 20 ns@ $V_{GS} = -6.5$  V. Fig. 14. shows the program characteristics utilizing hot carrier injection at a short program time of 20 ns and lower gate biases. When programming using FN tunneling without applying drain voltage, the threshold voltage shift was very small, approximately 0.5 V at a program voltage of 9 V. As the drain voltage increases, a larger E-field is generated at the source end, resulting in significantly faster program characteristics.

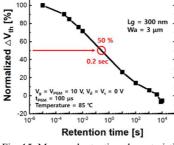

Fig. 15 shows the retention characteristics at 85°C of the 2D CT DRAM device with a thin tunnel oxide. Even with the tunnel oxide as thin as 1 nm, more than 50% of the initial Vth window was retained after 0.2 seconds, which is sufficient for DRAM applications.

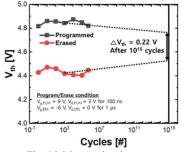

Fig. 16 shows the endurance (> $5x10^5$  Cycles) of the fabricated device as a function of pulse cycles. The fabricated 2D CT DRAM cell shows a  $V_{th}$  window of 0.22 V, ensuring sufficient reliability after  $10^{15}$  P/E cycles.

#### V. CONCLUSIONS

This study investigated the CT device, its potential as a next-generation 3D memory solution. We showed that CT DRAM was promising when it was combined with ultrathin tunnel oxide and HCI from metal silicide S/D. Moreover, the 1T CT DRAM is one of the most promising candidates for 3D DRAM due to its simple process integration and easy heat dissipation through the metal S/D.

#### ACKNOWLEDGMENT

The authors would like thank H.-C. Hwang/B.-R. Yoon at NNFC for helping the device fabrication.

## REFERENCES

- [1] J. W. Han, et. al., IEEE VLSI Tech., 2023

- [2] M. Suh, et. al., IEEE TED, 2024

- [3] A. Belmonte, et. al., IEEE IEDM, 2021

- [4] J. Kim, et. al., IEEE IEDM, 2023

- [5] S. -J. Choi, et al., IEEE VLSI Tech., 2009

- [6] A. Khakifirooz, et. al., IEEE ISSCC, 2023

- [7] K. Parat, et. al., IEEE IEDM, 2015

- [8] Min, J.G., et. al., Nanomaterials, 2022

- [9] K. Takahashi, et al., IEEE IEDM, 2004

- [10] A. Lauwers, et. al., IEEE IEDM, 2005

Fig. 1. Schematic illustration of the 3D CT DRAM

Fig. 2. Process integration of the 3D CT DRAM with SB S/D.

Fig. 3. Advantages of the CT DRAM compared to the conventional DRAM in view of (a) power and (b) 3D integration/heat dissipation.

Fig. 4. (a) Cross-sectional view of the 3D CT DRAM with Schottky barrier (SB) S/D and ultrathin tunnel oxide (b) HCI at the source-side was used for the program operation at the device having a poly-Si channel.

Fig. 5.  $I_d$ – $V_g$  characteristics at different (a) SB (0.15 eV  $\sim$  0.40 eV). The SB characteristics that vary with (b) programmed energy band.  $I_d$ – $V_g$  characteristics at the different tunnel oxide thickness (0.9 nm  $\sim$  1.5 nm) shown in (c). (d) The electrostatic potential hardly changes with tunnel oxide thickness.

Fig. 6. The retention characteristics at (a) different trap density, (b) trap energy level, and (c) tunnel oxide thickness. (d) Mechanism of electron leakage.

Table 1. Optimized Device parameters for the 3D CT DRAM

| Description (parameter)                                            | Values -                            |

|--------------------------------------------------------------------|-------------------------------------|

| Blocking oxide thickness (Toxt)                                    | 2 nm .                              |

| CTL(Si <sub>3</sub> N <sub>4</sub> ) thickness (T <sub>CTL</sub> ) | 2 nm -                              |

| Tunnel oxide thickness (Toxb)                                      | 1 nm -                              |

| Channel length (Lg)                                                | 150~300 nm                          |

| Channel thickness (Tch)                                            | 7 nm -                              |

| Schottky barrier height (SB)                                       | 0.25 eV                             |

| Nitride Trap density (N <sub>trap</sub> )                          | 7×10 <sup>19</sup> cm <sup>-3</sup> |

| Substrate doping concentration                                     | Undoped -                           |

| Gate work function                                                 | 4.65 eV .                           |

| Trap energy level                                                  | 2.25 eV -                           |

Fig. 7. Schematic of a planar CT DRAM to verify the feasibility of the 3D CT DRAM.

Buried oxide oxidation (2000 Å)

Undoped poly deposition (300 Å)

Poly-Si channel formation

O/N/O deposition (10/30/30 Å)

N+ gate formation (1000 Å)

Oxide/Nitride deposition (150/150 Å)

Spacer formation

Nickel deposition (300 Å)

Microwave annealing (600/700 W, 1/2 min)

Fig. 8. Sheet resistance of Ni and Co silicide according to MWA power.

Fig. 9. (a) On/off current ratio, and (b) SB heights of Ni and Co-silicide SB diodes.

Fig. 10. Process integration of the 2D CT DRAM with SB S/D

Fig. 11. TEM photographs of the fabricated 2D CT DRAM with SB S/D (a) Cross-sectional TEM (b) Magnified TEM of ONO layers.

Fig. 13. Measured (a) program and (b) erase characteristics of the devices with thick and thin tunnel oxide.

Fig. 14. Measured program operation characteristics using hot carrier injection with varying drain voltages.

Fig. 15. Measured retention characteristics of the device with thin tunnel oxide at 85 °C.

Fig. 16. Measured endurance characteristics of the device with thin tunnel oxide