## Cost Effective and Technically Competitive Nova Lake 8nm PCH

Negotiated \$235M in value, enabled platform compatibility

#### Cost

NRE, IP cost coverage Switching cost payment 30% lower die cost

#### Capacity

Supply assurance Flexible supply/ purchase commitment terms

### \$235M

NRE/price reduction value through '24-'28

#### Capability

Supplier Design service Intel/3<sup>rd</sup> party IP porting IP customization

#### Cooperation

Engineering collaboration excellence

Roadmap based engagement

#### Enabling multiple generations of desktop CPU to market

| YEAR                       | 2024           | 2025         | 2026          | 2027       |  |

|----------------------------|----------------|--------------|---------------|------------|--|

| Leading Client<br>Platform | Arrow Lake     | Panther Lake | Nova Lake     | Razor Lake |  |

| PCH                        | MTL-PCH (14nm) |              | NVL-PCH (8nm) |            |  |

#### Supporting CCG's architectural evolution

Platform compatibility and PCle5 upgrade across 3 CPU generations at the total lowest cost.

Reuse of external 14nm process to enable NVL product with minimal platform cost.

Team Acknowledgement: EMS, TEG, DEG, FTE, CCG

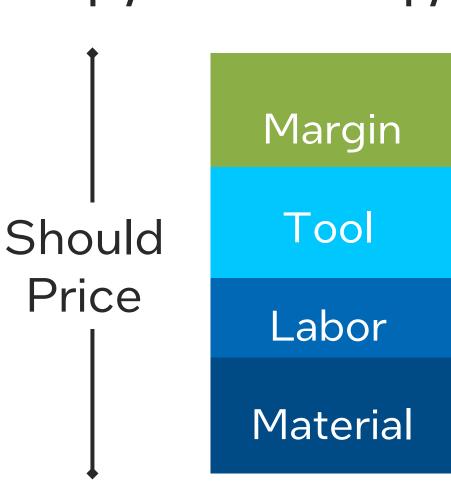

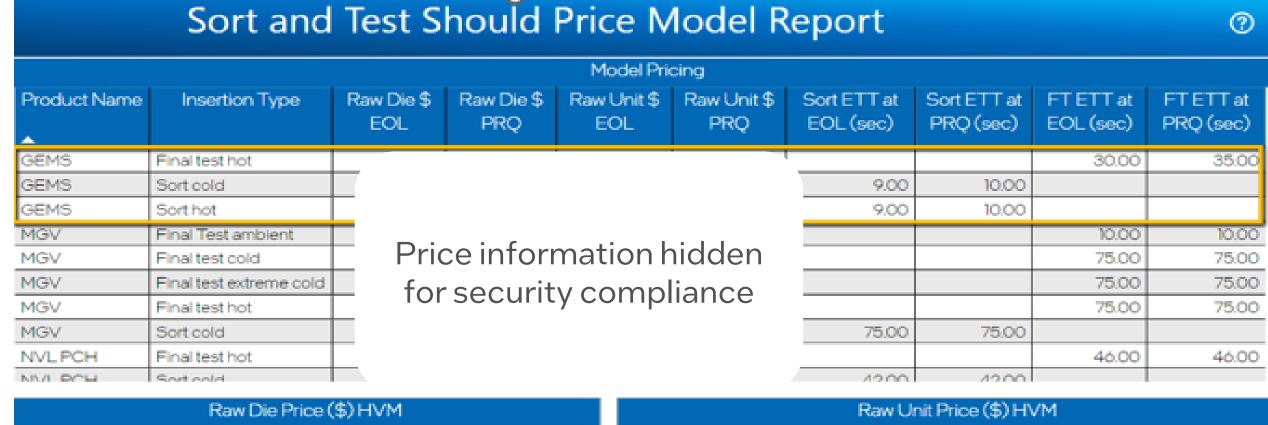

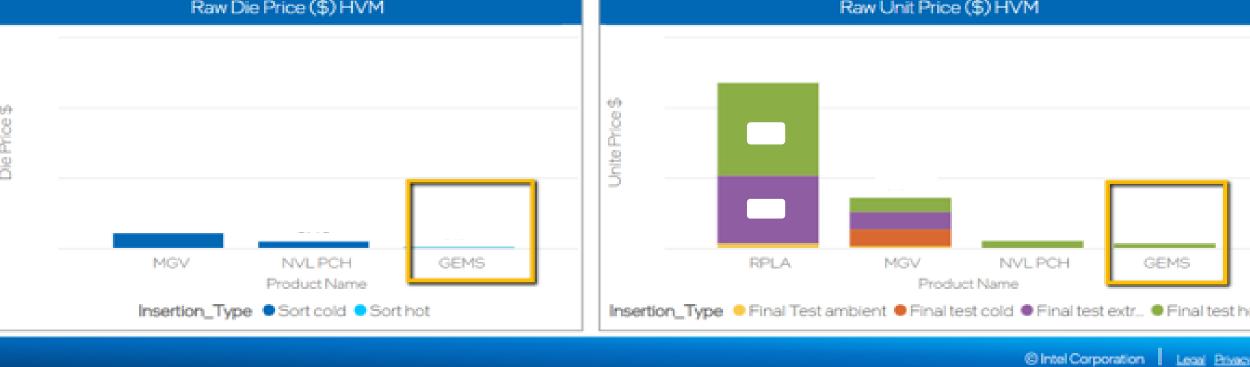

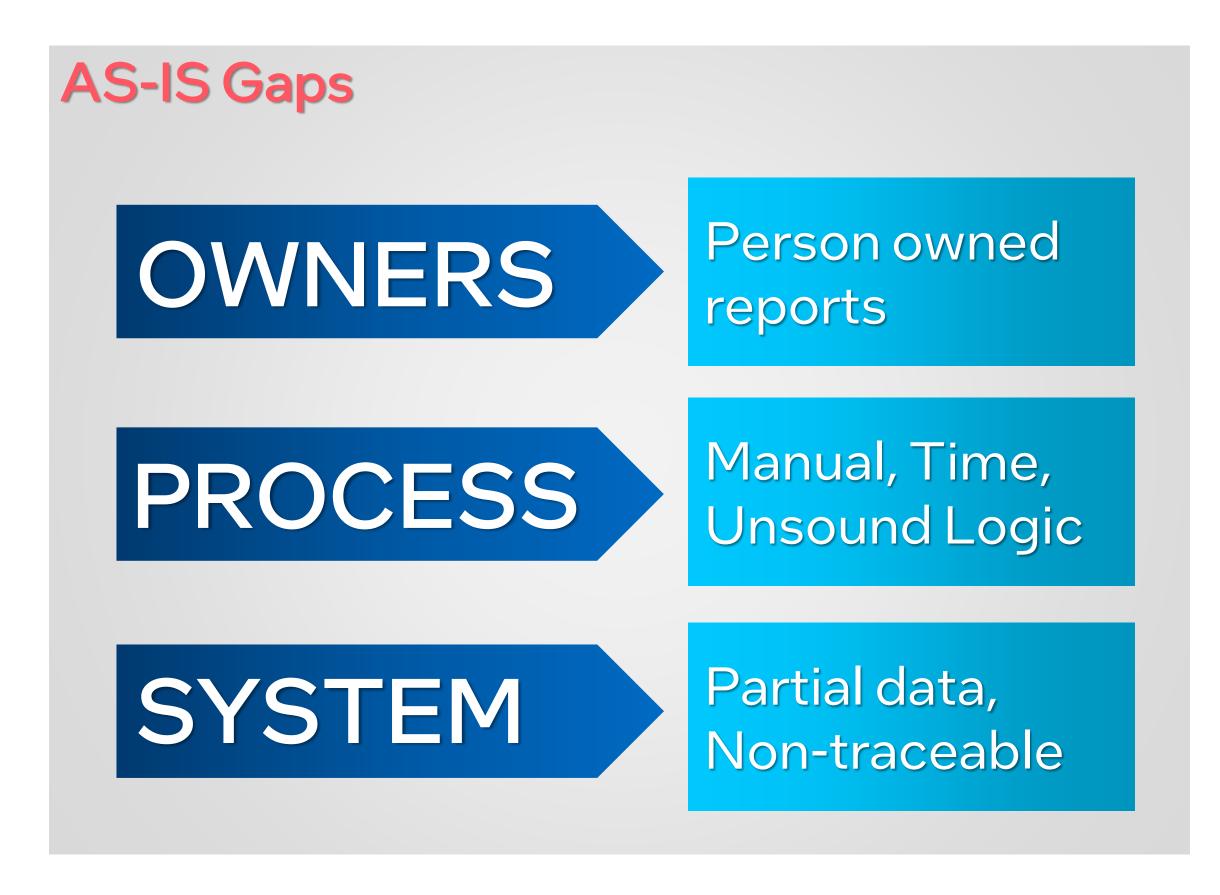

#### GEMS SHOULD PRICE MODELS

Authors: Jelena Culic-Viskota, Sandeep Kumar, Beilei Zhu Kousik Ganesan, Ana Phillips, Daniela Stickel, Max Wu, Srini Moola

#### Fab-to-Finish Cost-Efficiency Unleashed: Counters Competition and Bolsters Intel's Market Position

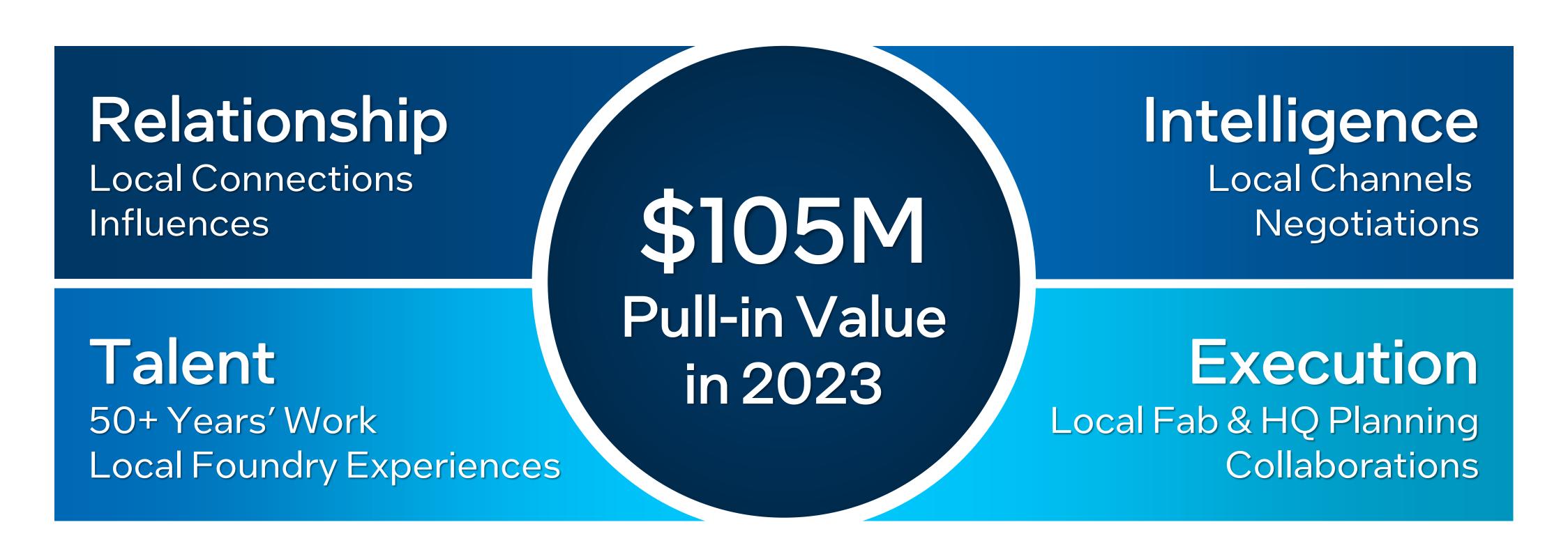

#### Relationship

Trust and collaboration with Intel Products

& Intel Foundry

#### Model

Cover Packaging, Sort and Test insertions

>\$1B CCGPnL Impact

#### Intelligence

Validated bottoms up analysis

#### Influence

Drive pricing negotiation & Benchmarking

#### Methodology:

Iteration of inflation, Utilization, yield, Overhead, Margin etc.

#### \$/hour or \$/ unit

Should Cost

#### Bump and Assembly Should Price Model Report

GOTO/GEMS-SPM

GOTO/STSPM

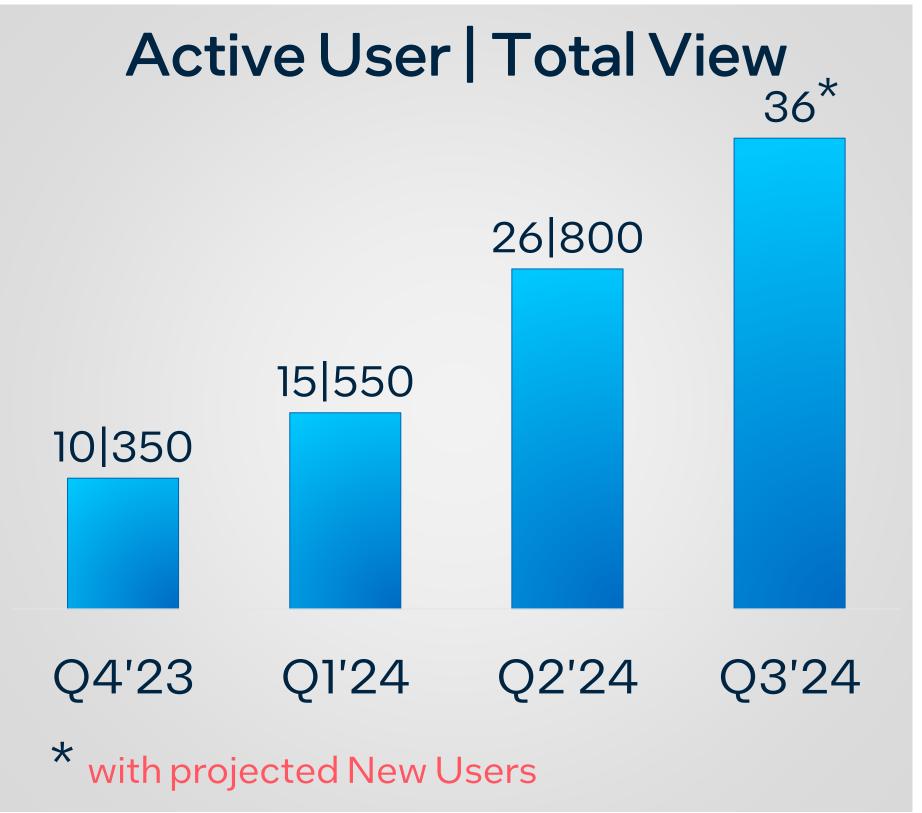

Azure Cloud Centralized and Ondemand Analytics with Self-service Power Bl

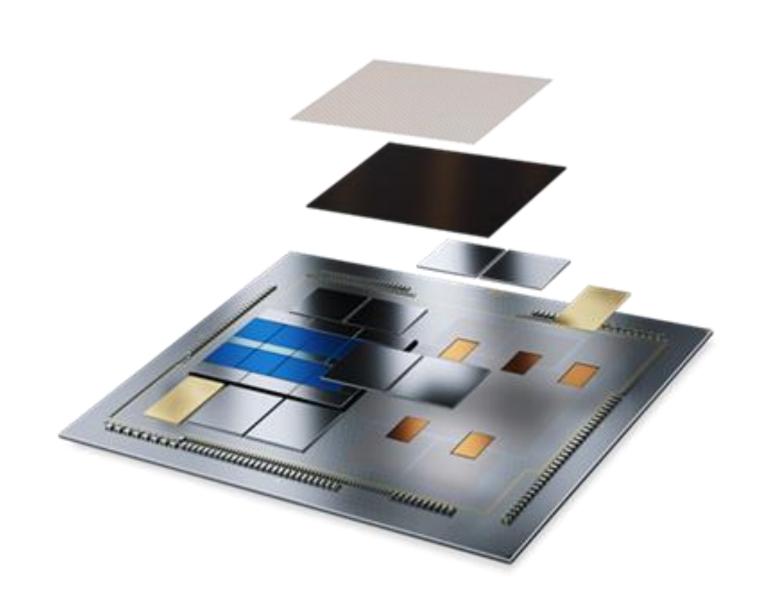

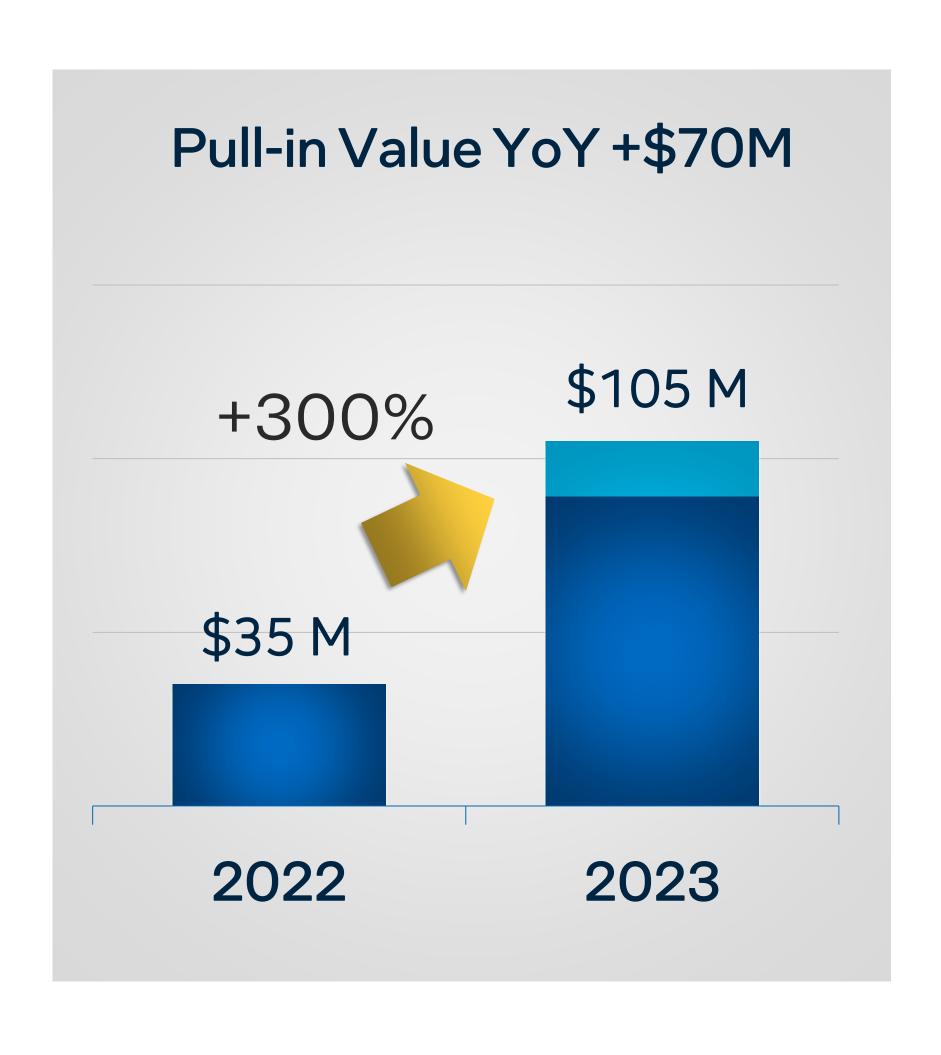

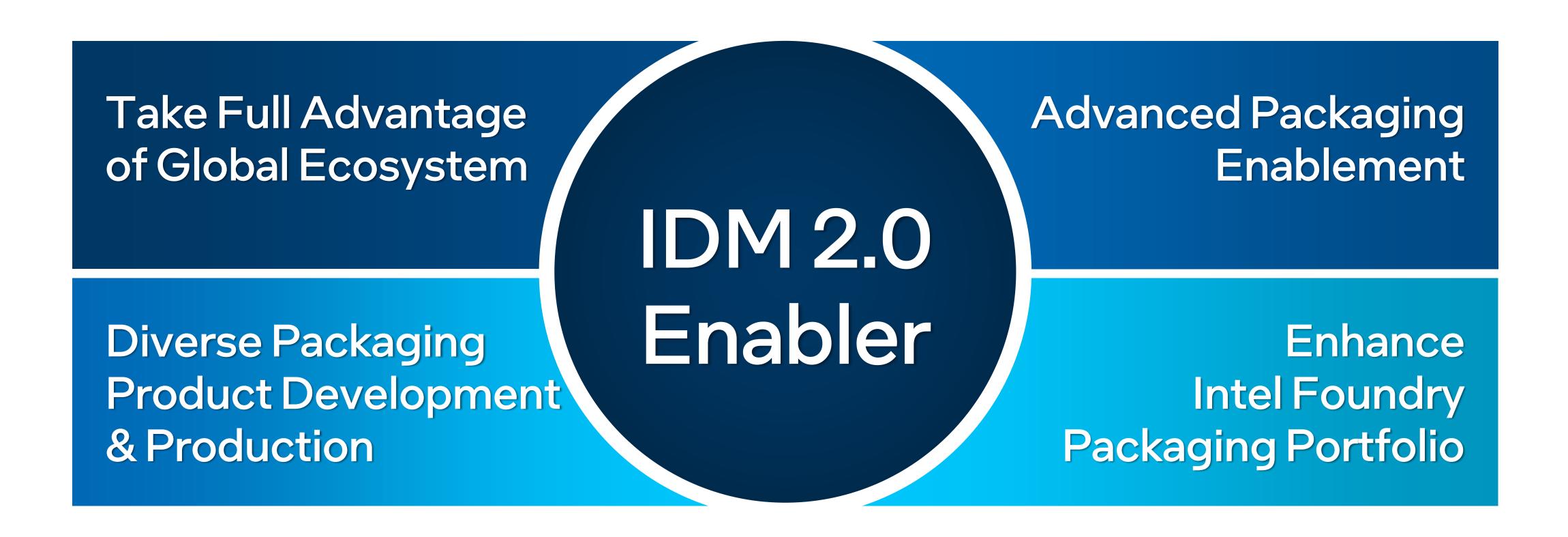

## Product Package Development for IDM 2.0

Enable Intel Products with Worldwide Assembly Capability and Capacity

Comprehensive product applications

Cost effectiveness

Full Portfolio of packaging solutions for IDM 2.0

Complex supply chain management

Extensive Si foundry integration

#### Packaging Product NPI Portfolio and Summary

CCD

CCG

WCS

NCNG

MBE

Altera

SPPD

VTG

5 Product Architectures

5 Si Foundry 10 Si nodes

8 OSAT Factories

5 Substrate Suppliers

5 Component & Memory Suppliers

22 Products

#### Packaging Product Development Highlights

### Resilient supply chain for:

- Increase the IF

flexibility: qualified first

PCH (MTL/ARL PCH)

w/ two OSATs.

- Enable Intel Product

w/OSAT: Huddle Bay to

meet cost/time req as

the first Intel 16 product.

### Competitive product cost:

**\$6M lifetime saving** and ahead of time for FmP2 & WhP2 by increasing strip density.

### Effective Strategy & Methodology:

- Streamline key deliverables & roadmap

- Create automatic NPI dashboards for GEMS/BUs with email/message time reduction of 15%.

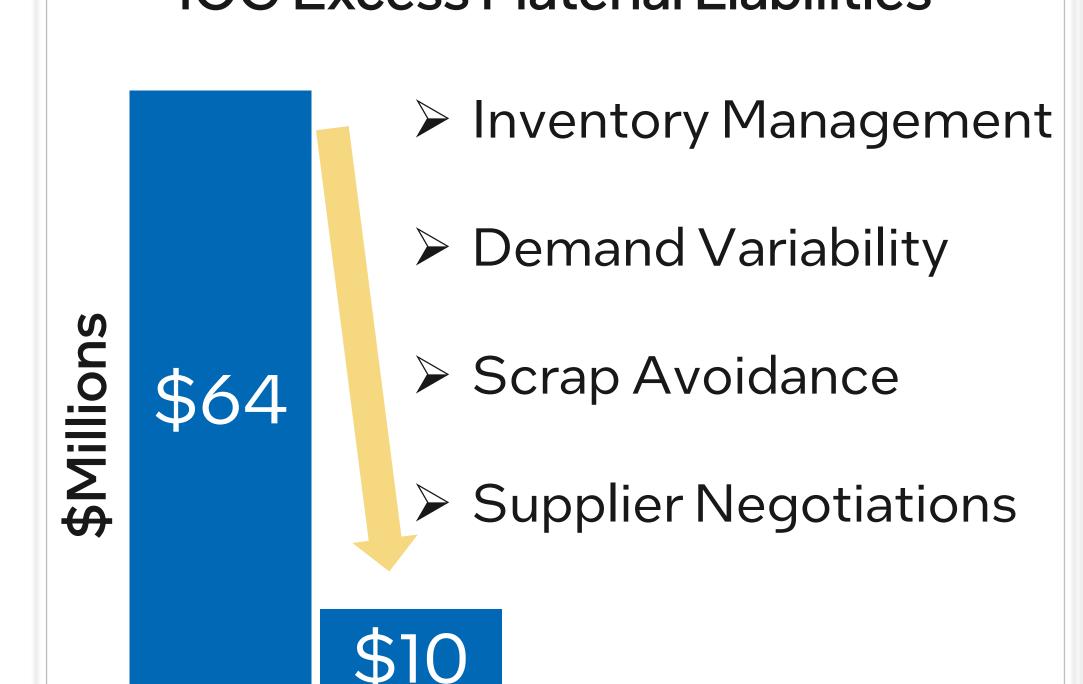

## Optane's Stylish Exit

Maximize profitability through excess liability management and innovative revenue sources

Enhanced

Profitability

**Contact Authors**

#### **Excess Liabilities**

Demand Generation Scrap, Cleanup

#### Cost Mgt.

April'23

Spending Discipline

Capital Reuse & Resale

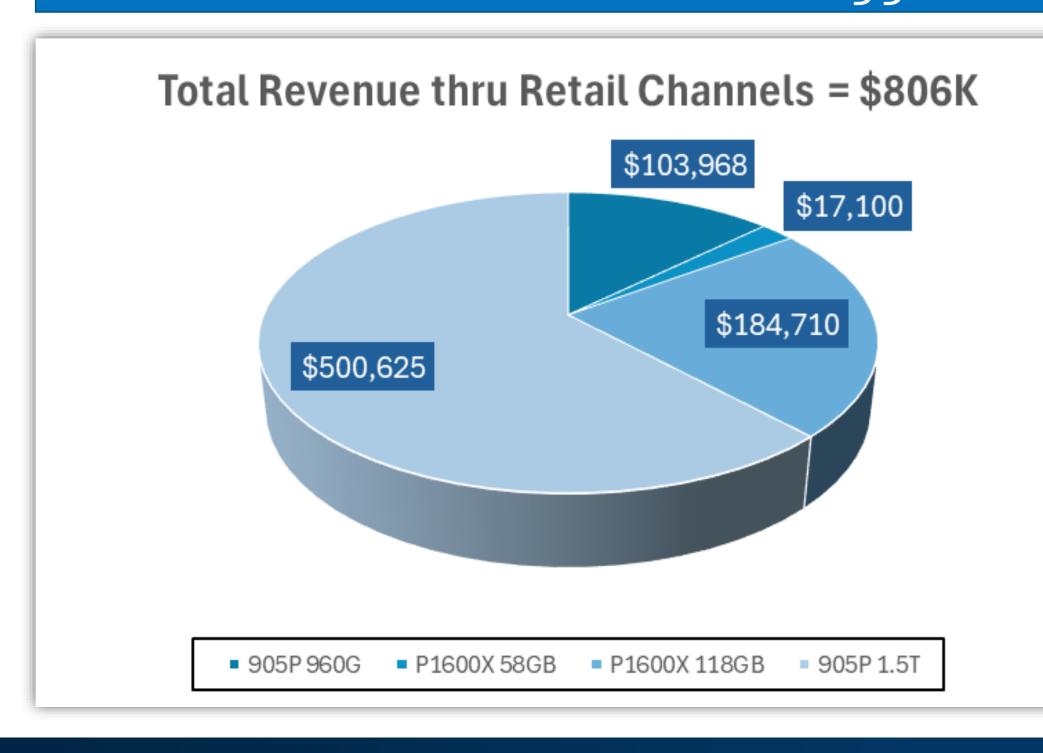

### Retail Channels

Amazon Newegg

#### Intel Benefit

Re-purpose Excess Drives to Intel Network

#### IOG Excess Material Liabilities

#### Cost Management Benefits to Intel

- Operating Margin Task Force

- > Supplier tier pricing & negotiations

- Asset reuse and resale >\$25M cash impact to Intel

#### Revenue & Cost Avoidance

**\$806K** revenue thru sales of excess client drives to Amazon and Newegg

April'24

Saved Intel \$444K by using Intel Network to re-purpose excess drives

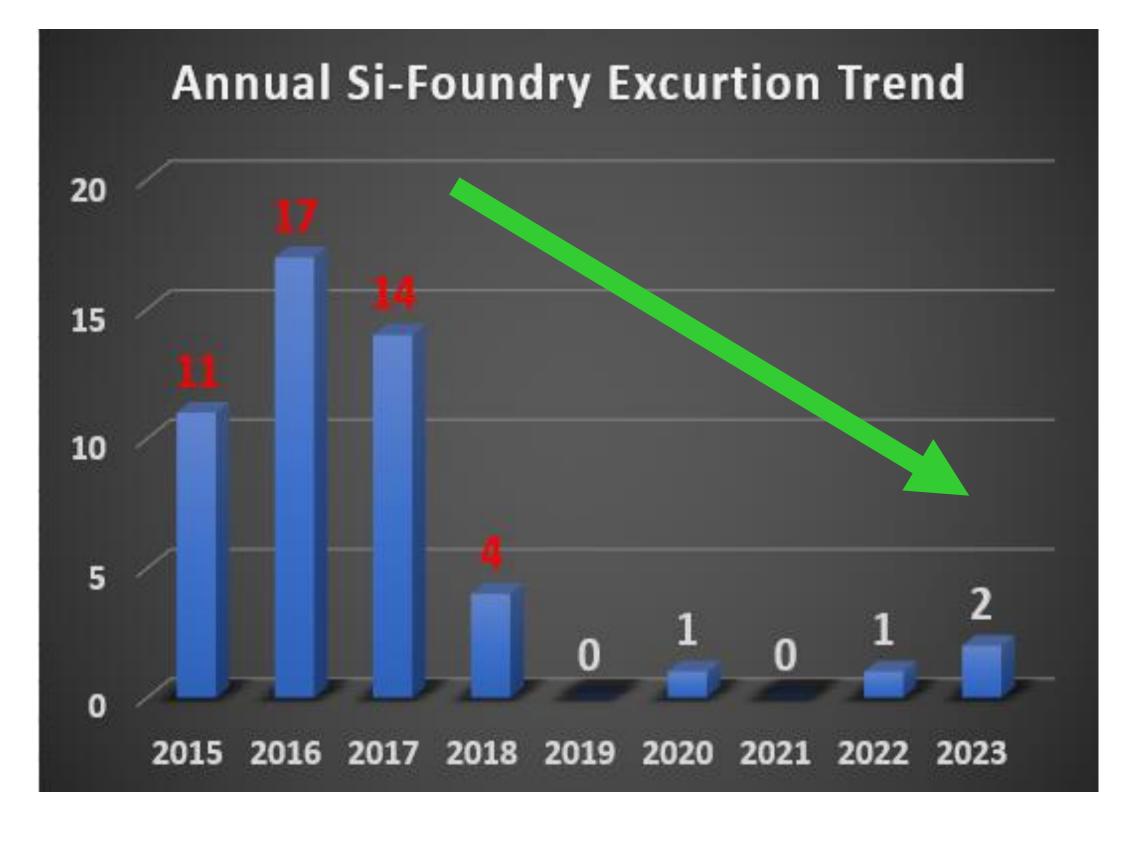

## Quality First, Success Always

Impactful outcomes through a dedicated quality mindset:

- Faster response time to bug sightings & quicker implementation of new features via high coding practices in SCIPIO Supply/Demand solver overhaul.

- Reduce excursions by 75% in 2022 & 2023; 2024 YTD has 0 MRB/DRB.

- Cut down excursion closure time by 40% in 2023.

- Boost 2023 EES quality score by 15% (2024 EES results on Circuit in July).

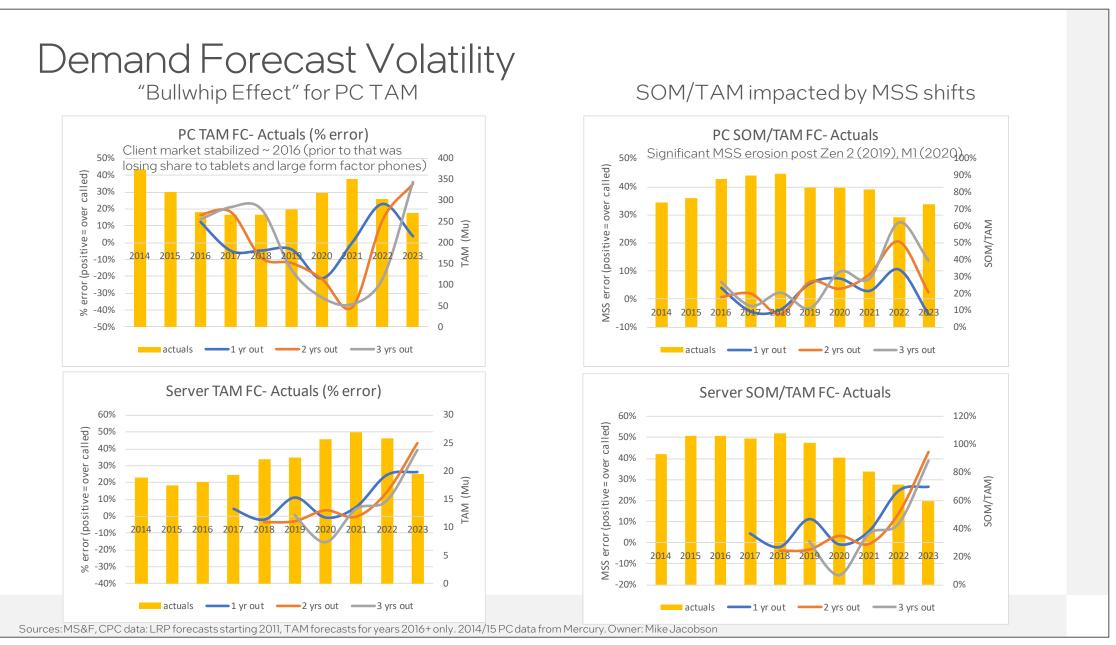

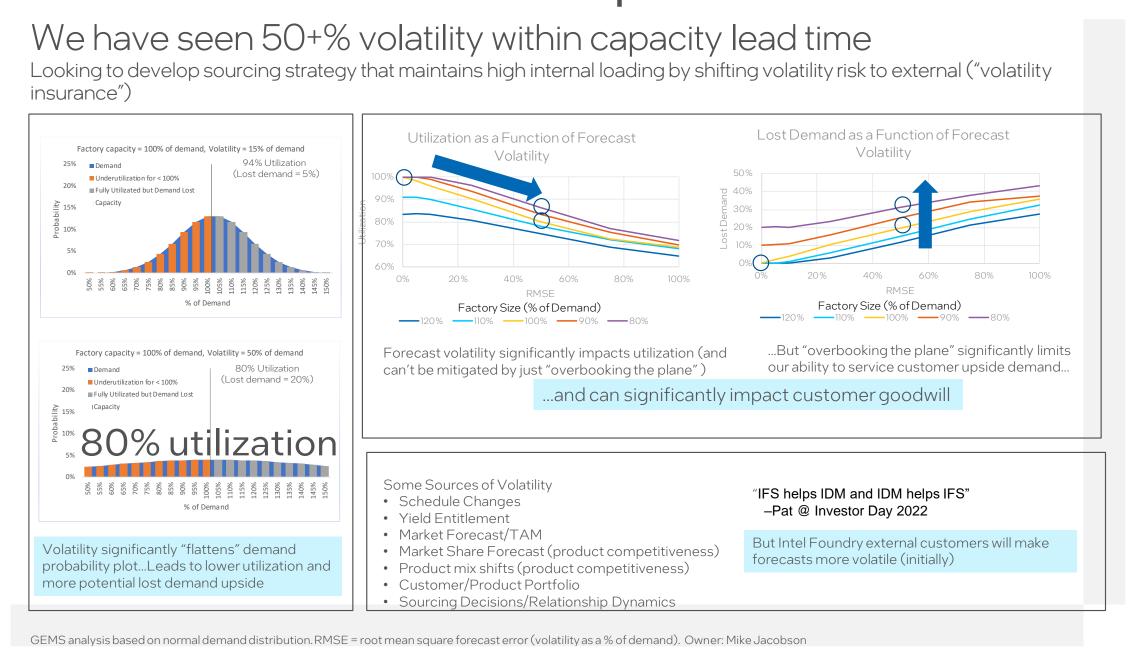

## Volatility and The Outsourcing Paradox

External Manufacturing Can Actually Help Intel Foundry's Bottom Line

GEMS thought leadership directly helps Intel Foundry

- ~\$700M of capital decisions in Q1'24 were informed by GEMS analysis

- Volatility-based guardrails for capital pull-in/push-out are being implemented in Q2'24 LRP

- Additional projects underway to explore dual-drive opportunities to flex demand in/out to help optimize Intel Foundry internal loading while minimizing capex

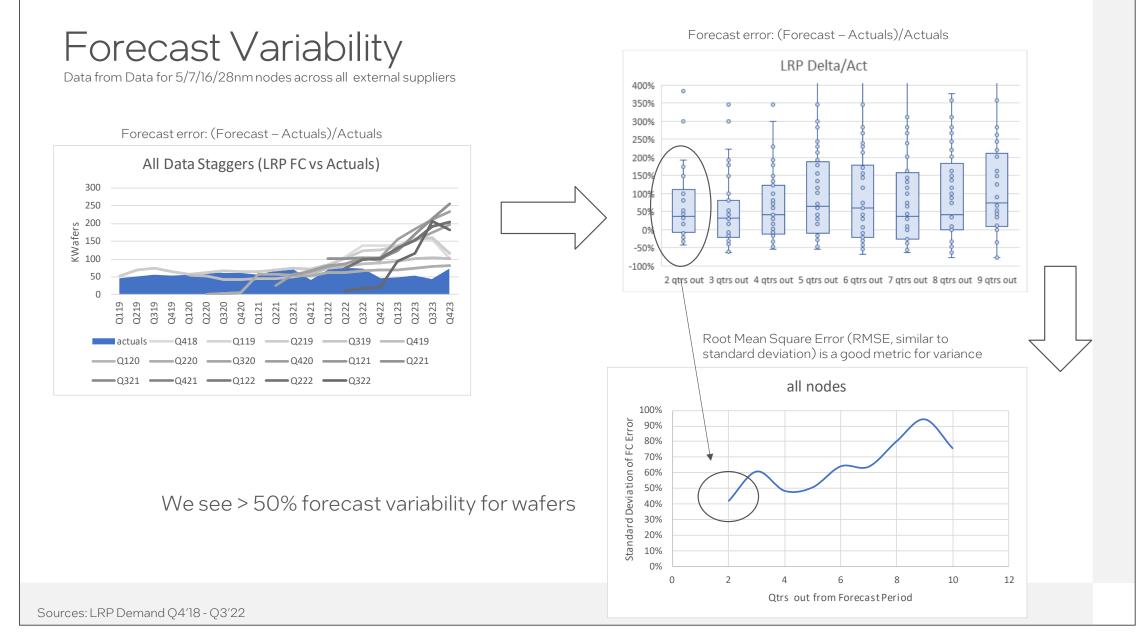

Predicting market/product demand can be challenging

And more challenging to predict wafer demand (which adds risk to capacity planning)

### Leads to underutilization and/or lost demand upside

And can't be mitigated completely by changing factory size (relative to demand)

#### The size of the problem\*:

Multiple Billion \$ of capex and underutilization is at risk from volatility on each new node

#### A robust external corridor allows:

- Development of a "smart" sourcing strategy to help the reduce the risk to internal loadings

- 2. BU access to best available external process (equal to or greater than competition)

- 3. Access to additional capacity to help cover extreme demand upside cases

Good results but partial success so far:

Volatility analysis used in partnership with FMSC

Strategic Planning to inform Intel Foundry Capacity

strategy in 2024

...full benefit requires Cooperation from Intel Products, Intel Foundry, and Intel Corp. to develop comprehensive end-to-end capacity strategy

using industry benchmarks and published capacity plans

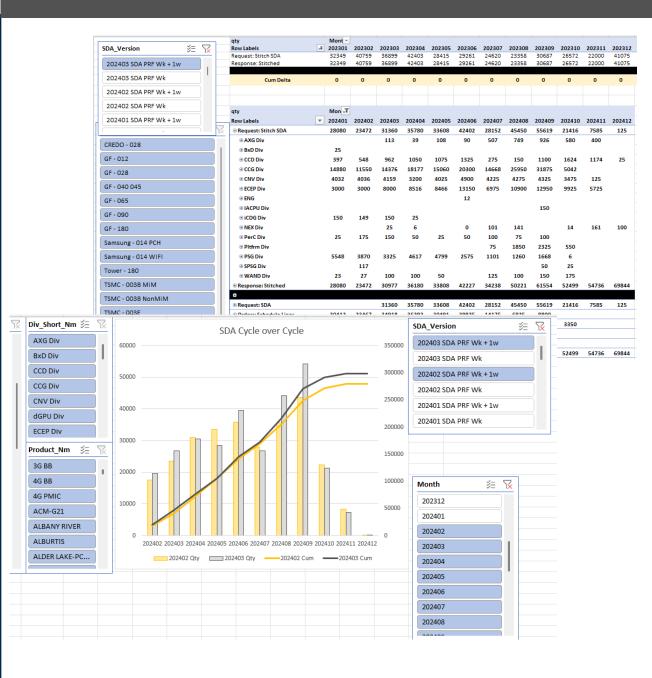

## PRF Volatility Dashboard

Using data and transparency to reduce cost and improve supply of external wafers

Tian He

**Dave Bonner**

oject Team:

Sachin Rastogi

Bernhard Fiegl

Rob Olsztyn

202310

202311

202312

202401

202402

202309

Fiscal Month

202403

202404

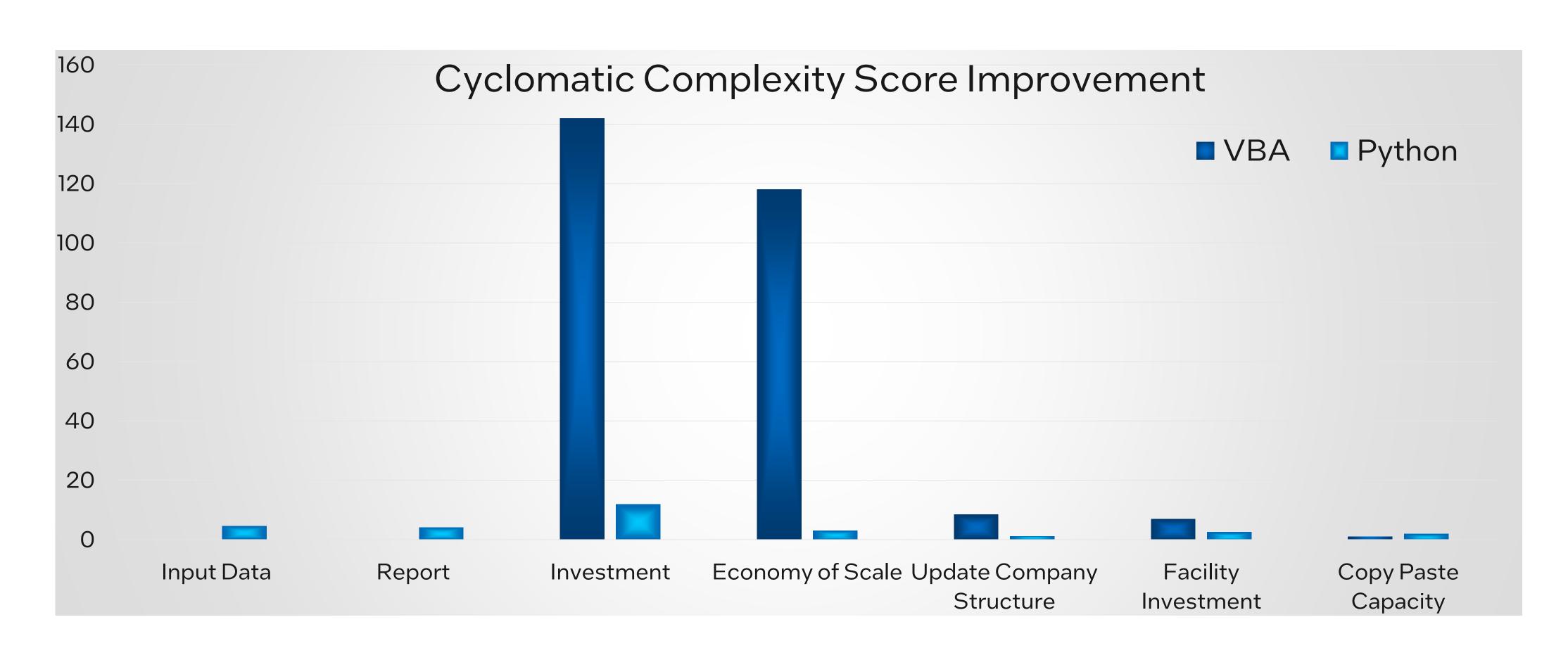

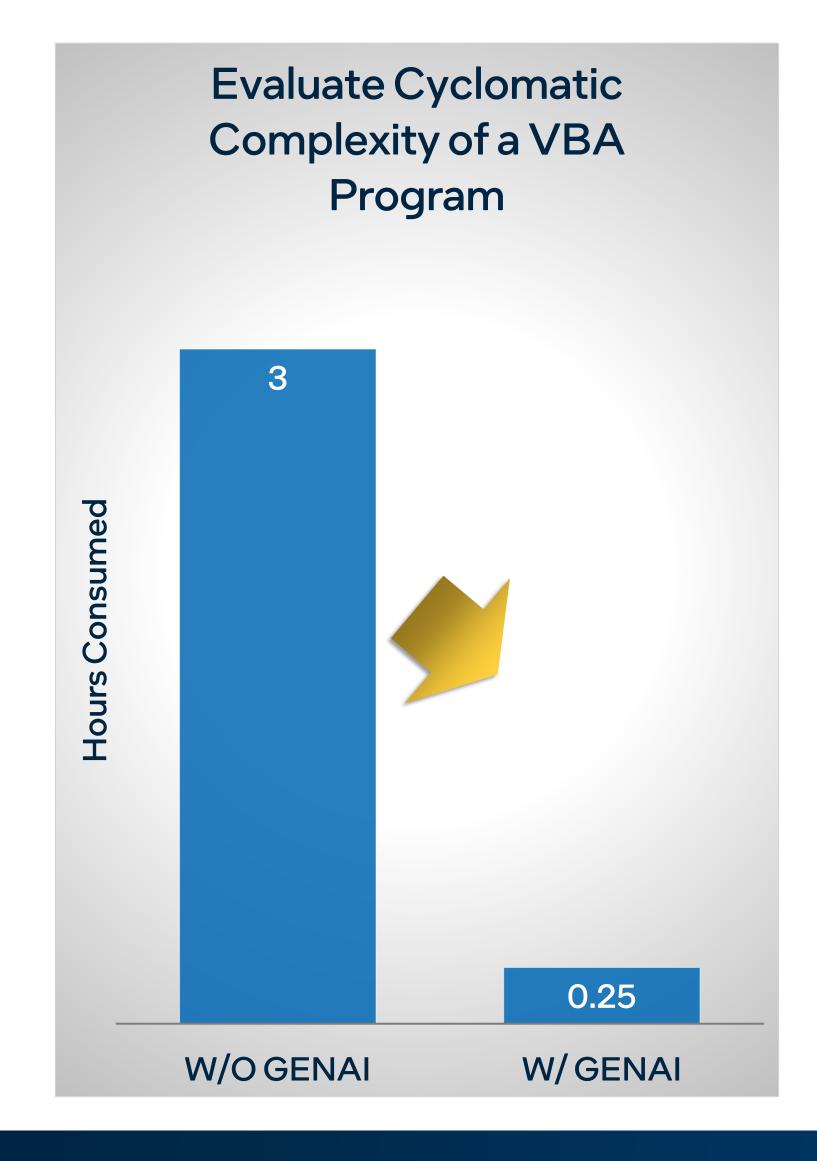

## Foundry Business Model Python Refactor

Foundry Business Model is a Top-Down End-to-End Profit and Loss Simulation of a Foundry

Set Reference Prices

Support FSM

Assess Production Expenses

Aid TD/MSO

±5% Delta

Compared to

Actual PnL

#### **Major Improvements**

Maintainability

Reduced Cyclomatic Complexity by 90%

**Flexibility**

Modular Code Simplifies Feature Addition

Stability

Corrected 7 Hidden Issues

Speed

91% Time Reduction

intel. OPTANE

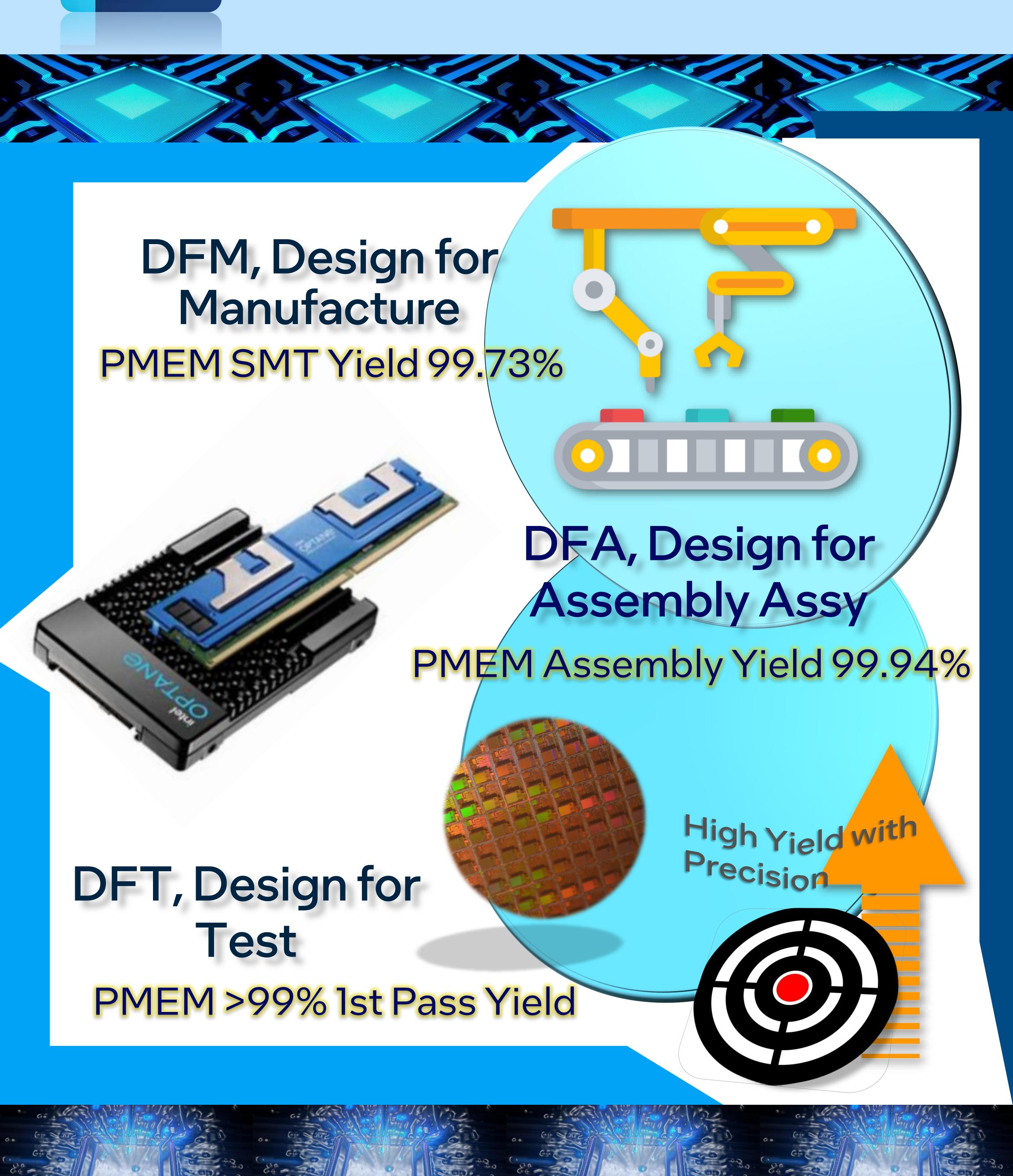

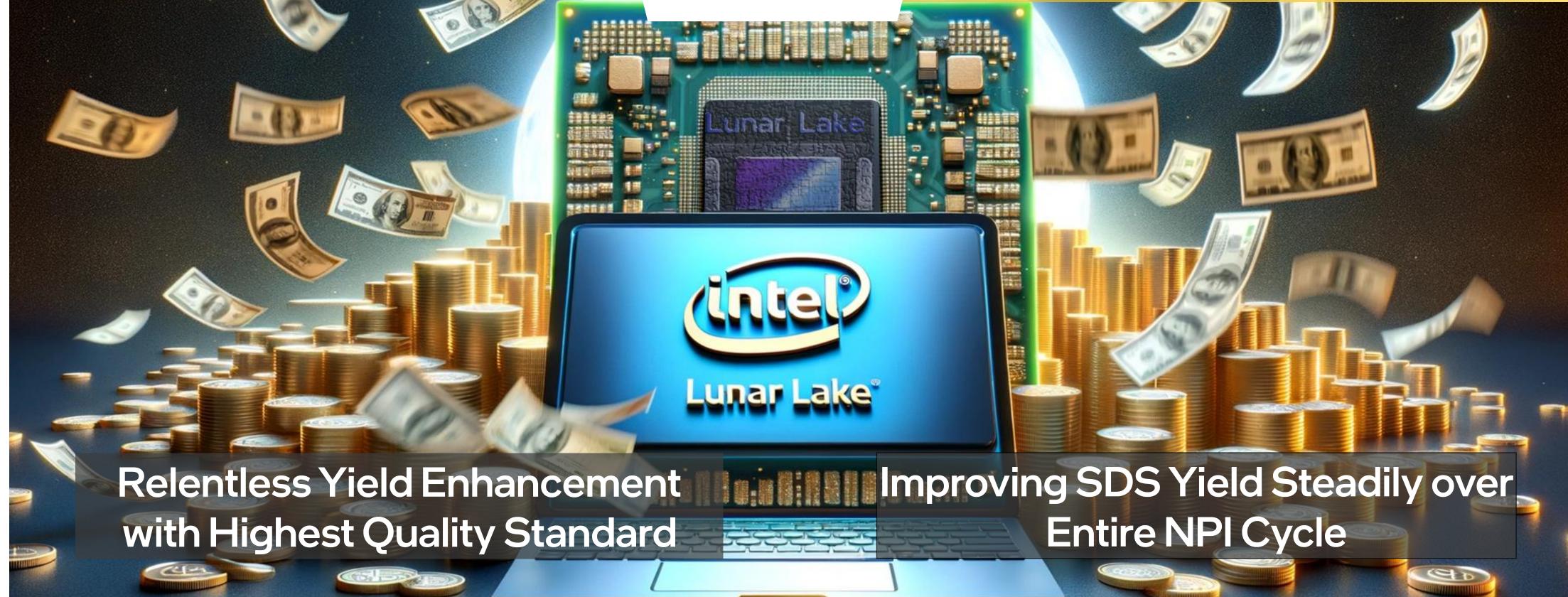

## Manufacturing Disciplines Ensure Product Yields

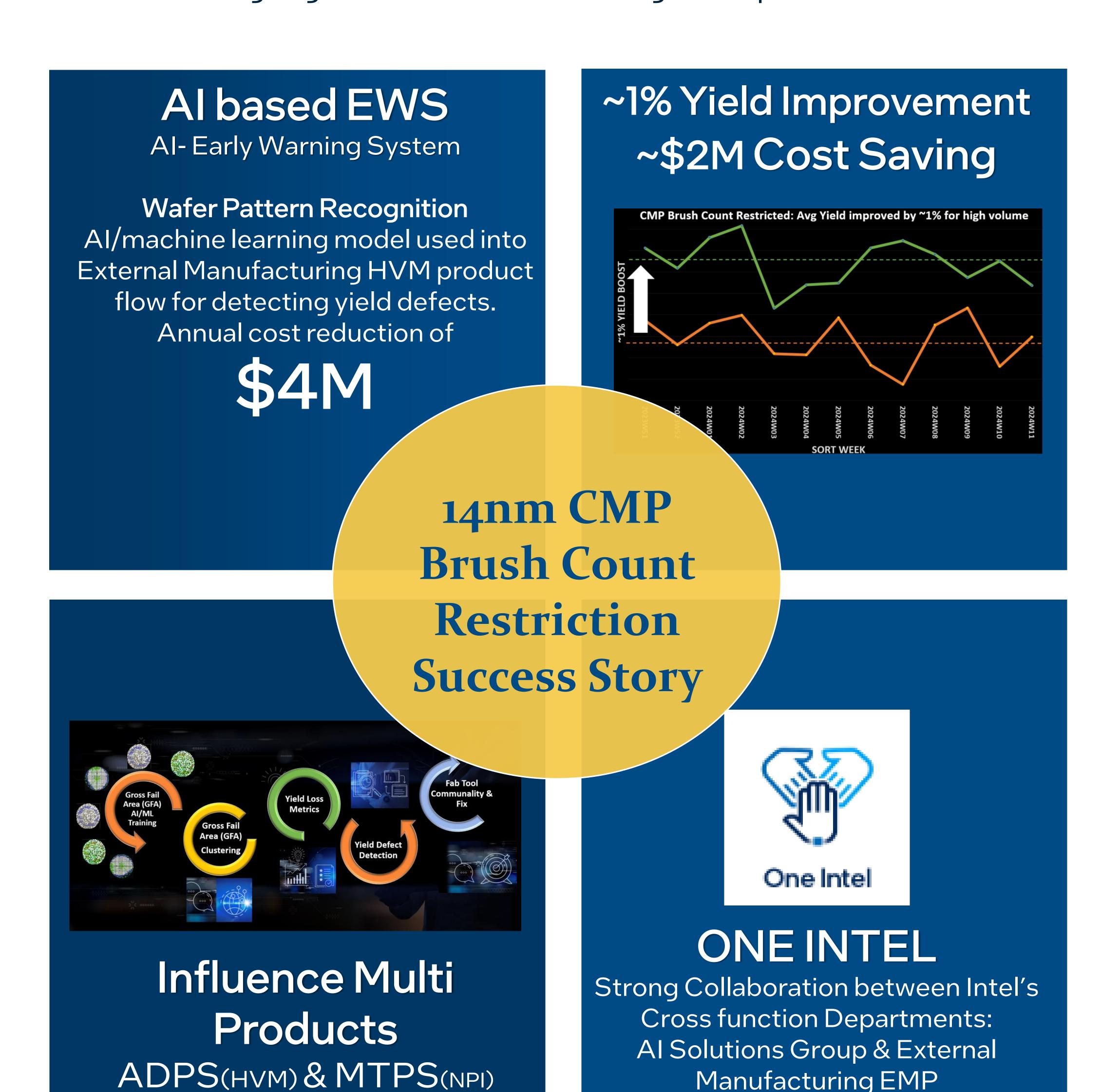

#### Al-Powered Manufacturing

Revolutionizing High Volume Manufacturing for Superior Yield Outcomes!

Artificial Intelligence-based Wafer Auto Crash flow identified yield loss correlating to Chemical Mechanical Polishing (CMP) brush lifetime resulting into ~1% yield gain and minimum of \$2M in cost saving

## Needle in high volume manufacturing...

Enabling automation and fast external manufacturing data and KPI access.

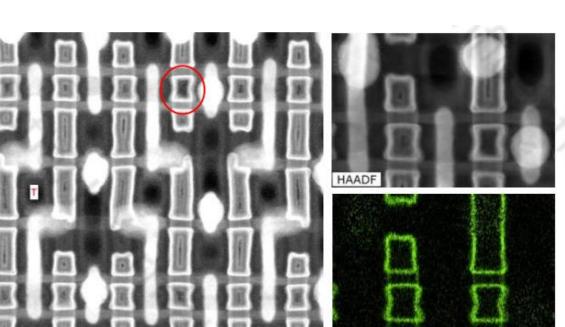

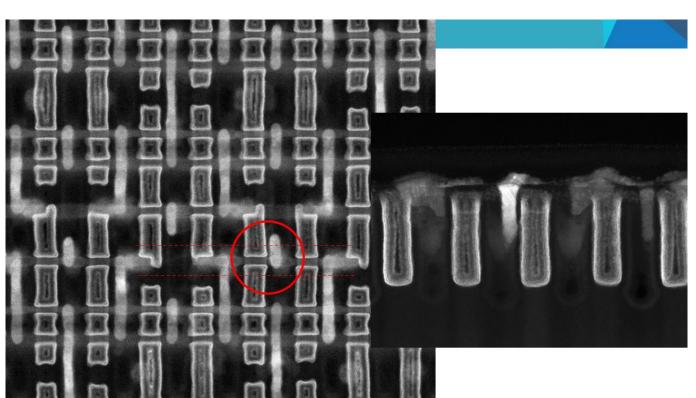

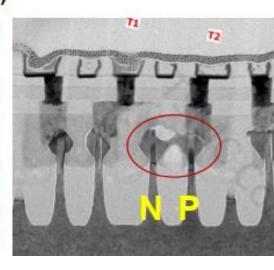

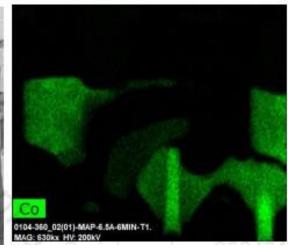

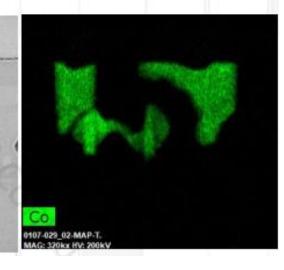

## Efficient Diagnosis / FIFA for RCA in MTL Products

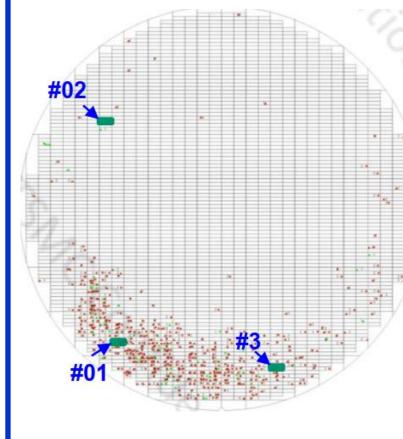

More than 1.6K wafer impacted – Impacted yield ~0.6% below the Q1′24 goal

#### Problem

Process defect / excursion has impacted

1.6k wafers affecting ~0.6% yield

#### Root Cause

pWF remaining cannot be detected from KLA (in-line) Cell-aware/chain diagnosis are demonstrated

More than \$6M savings

#### FIFA

Diagnosis / further FA delayering / TEM/EDX analysis confirmation

#### CIP

Several Foundry CIP in place 3<sup>rd</sup> party FIFA vendor Tool procedure improvement

Case: I - Bin 21

pWF remaining

Other Cases Supported for Yield Improvement:

Case: II – Bin 8

MD misalignment

Case: III – Bin 26

Nepi burn out

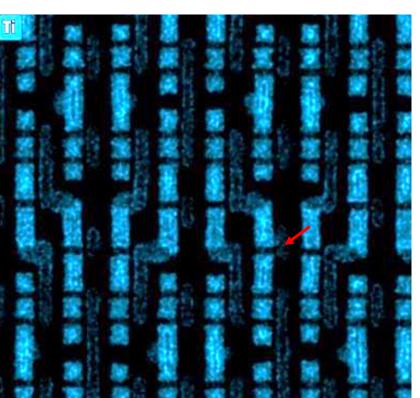

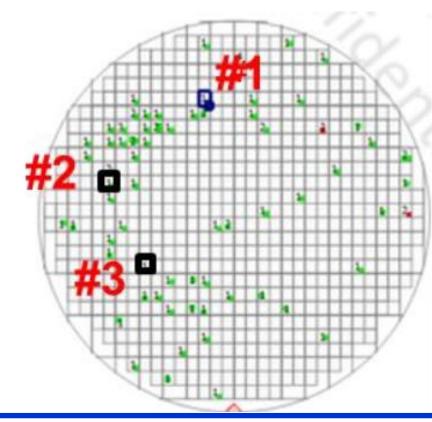

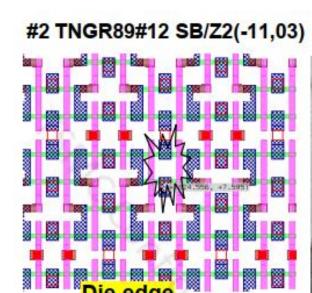

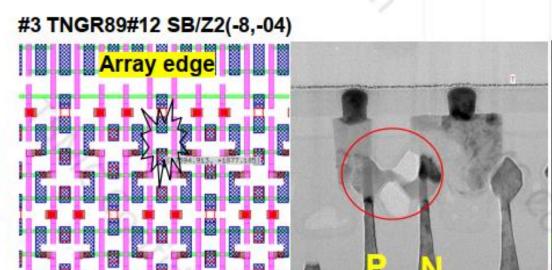

## Find Sensitive Layout Patterns

Find layout patterns that cause systematic defects in High-Volume Manufacturing Production

#### Capture & Matching Result (Hits/ Matches)

ID#1 pattern has been repeated 12 times in entire chip layout

| ID | Fault Type      | Layers                                                   | Pattern Image | Hits | Matches    |  |

|----|-----------------|----------------------------------------------------------|---------------|------|------------|--|

| #1 | Open-1          | $M_{N+1}$ $V_{N}$ $M_{N}$                                |               | 1    | 12         |  |

| #2 | Open-0          | M <sub>N</sub><br>V <sub>N-1</sub><br>M <sub>N-1</sub>   |               | 1    | 642        |  |

| #3 | Bridge<br>-both | $M_{N+3}$ $V_{N+2}$ $M_{N+2}$                            |               | 1    | 507        |  |

| #4 | Open<br>-both   | M <sub>N+6</sub><br>V <sub>N+5</sub><br>M <sub>N+5</sub> |               | 6    | 131,704,20 |  |

#### **Analysis Results**

Certain net with ID#1 has been checked 6 times in different fail Dies (L/W/D)

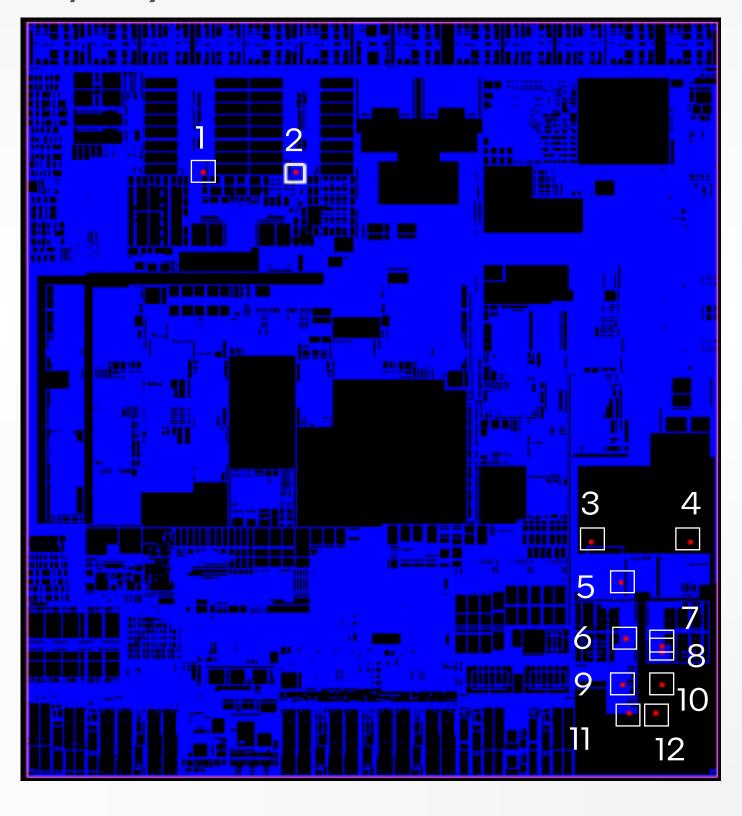

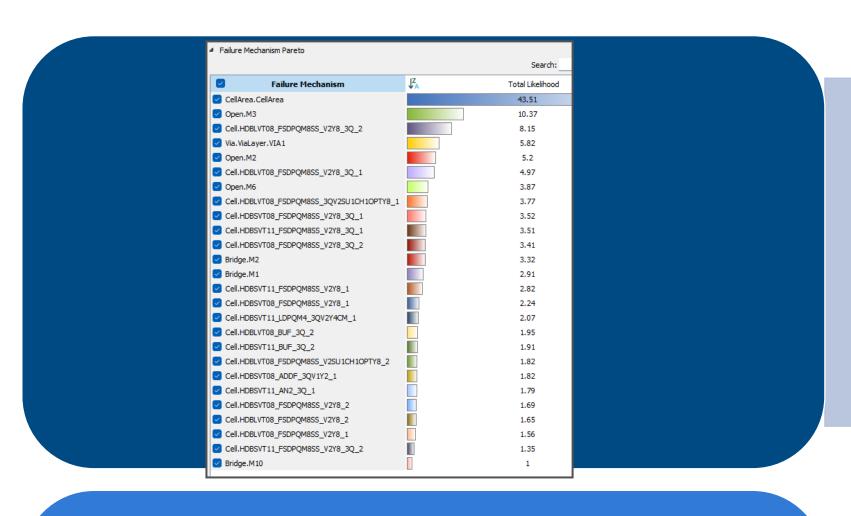

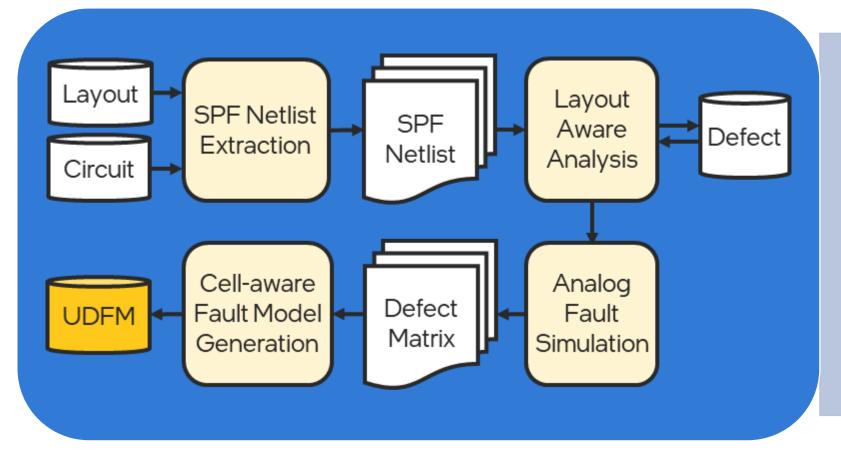

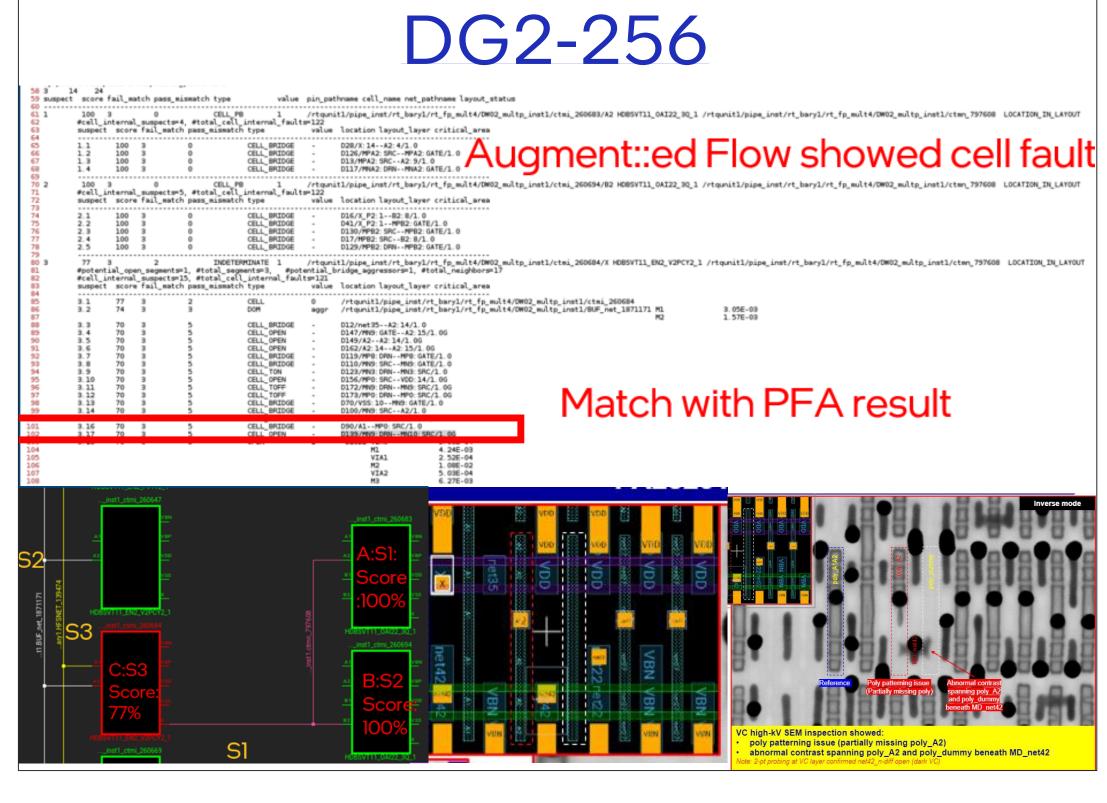

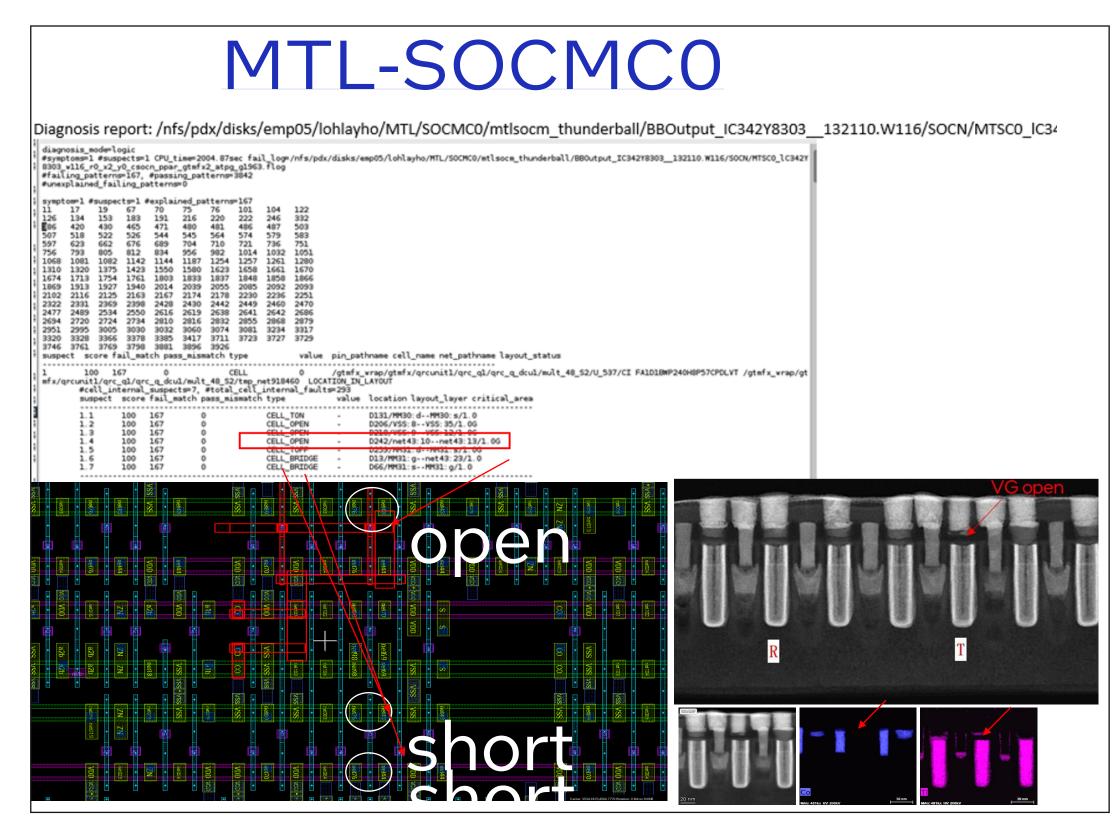

### Cell-Aware Diagnostics

#### A Technique to Refine the Failure Analysis Candidate Selection

#### **Motivation**

- Cell faults can be one of the significant failure mechanisms

- Cell-aware diagnostics can enhance Physical Failure Analysis

(PFA) candidate selection by pinpointing faults within specific cell locations.

- Suspect area can be reduced to 10%-1% of the cells' area

|           | Component of Spice Netlist<br>@Standard cell library |      |   | ATPG<br>UDFM | DFM-Aware<br>UDFM |

|-----------|------------------------------------------------------|------|---|--------------|-------------------|

|           | Res<br>Cap                                           | X/Y  | 0 | 0            | 0                 |

| Dorocitio |                                                      | BBox | 0 | Х            | 0                 |

| Parasitic |                                                      | X/Y  | 0 | 0            | 0                 |

|           |                                                      | BBox | 0 | Х            | 0                 |

| Device    | MOSFET                                               | X/Y  | 0 | Х            | 0                 |

#### Challenges

- The absence of cell-aware patterns

- Unavailability of cell-aware diagnostics flow during production

- Unavailability of the DFM Aware User Defined Fault Model (UDFM) library (N6)

#### Solutions

- Developed the augmented diagnostics flow that operates offline as needed

- Used the existing production Stuck-at patterns and failure logs for the cell-aware diagnostics

- Developed and validated the DFM-Aware UDFM library (N6)

- Validated the effectiveness of cell-aware diagnostics with a few PFAs

#### Results

- Library creation methodology is being disseminated to the relevant Intel teams

- Ready to deploy for HVM of new designs with advanced nodes (N6 and N3B)

- Can analyze logic failures within standard cells

Deployed on 2 designs (N6) - Two successful PFA are shown below

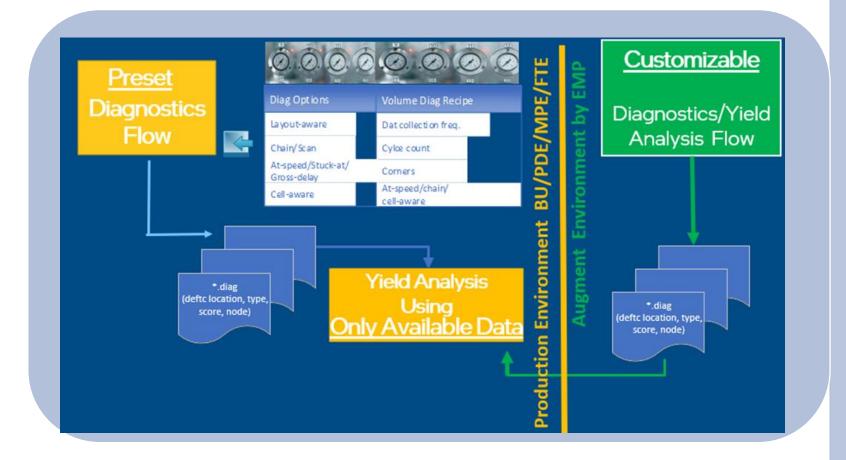

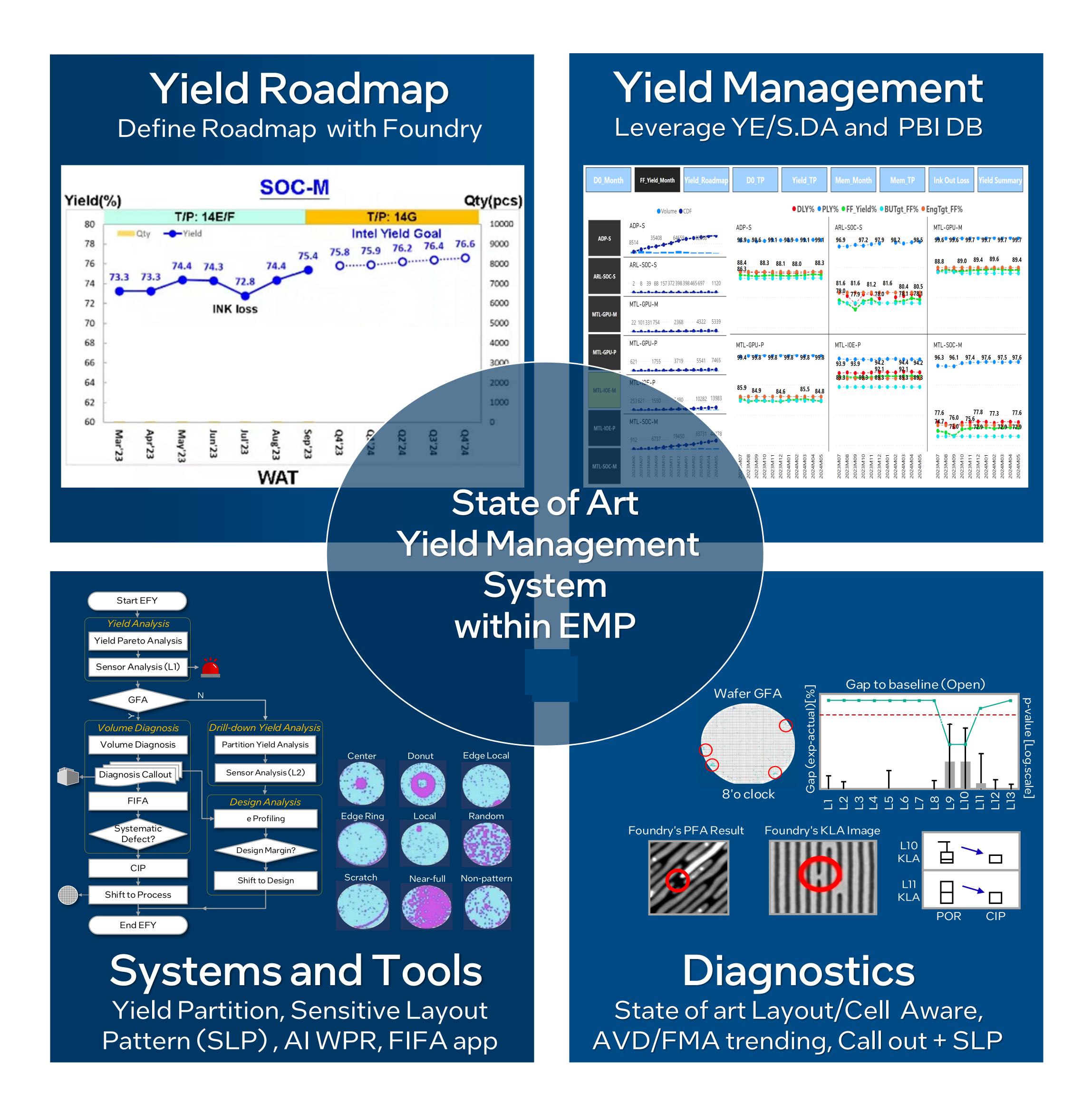

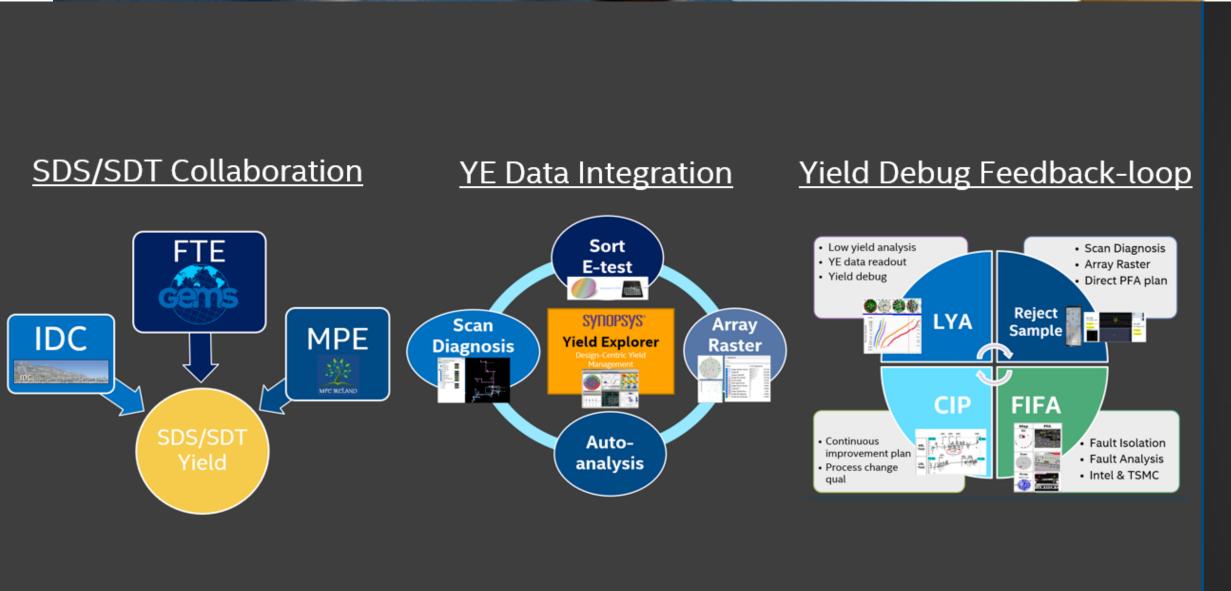

#### Advanced Yield Management

Developed a High Efficiency Yield Management System

Integrated an efficient HVM yield management system in EMP with start of art tools and metrologies. Contribute to savings in \$\$ Millions Annually

## Scan Yield Loss debug

MTL SoC South Scan Yield Loss of +1% ⇔ +2% is debugged by utilizing Yield to design marginality timing closure feedback loop. Preventing future products Yield Loss (save \$\$) via co-developed TFM

Sort Yield Segregation

Scan Yield loss Diagnostics

Design Profiling Design signoff: IR drop aware STA

Scan Mode Yield segregation to narrow down design and %Yield impact **Chain Failures** MAX NOM MIN 98.5% ₹ 2500 ı 2000 ± 96.5% 96.0% 95.5% 95.0% 94.5% CHAIN TRANS Test C0 Corner Lot C302Y020, Program Rev 14C SORT\_WAFER 501 502 505 511 503 507 509 Scan Device\_Skew FS SF SS TT SubPartition PARGBE Mode IR 100.00% 100.00% 100.00% 100.00% 100.00% 100.00% 99.84% MAX CHAIN 100.00% 99.84% 100.00% 100.00% 99.68% 99.51% 89.35% NOM drop >> 84.69% 99.27% 98.99% 100.00% 100.00% 97.91% 98.19% **Functional** PRE and POST DVD back annotation - Timing Endpoints Distribution Mode 100% 1757 90% 80% PRE-DVD Net('pargbe/vccaon 0p7...) Total Demand Current number of End 70% Net('pargbe/vccaon\_0p7...Total Demand Current#1 129 **Points** 370 1.5 60% 57 6 1.25 50% 9904 **POST-DVD** urrent (amp) 40% number of End **Points** 30% 20%

IR drop Induced VDD droop increases hold timing slack and fails

less than

**15ps**

129

47

2.0

2.5

1e-8

■ POST-DVD number of End Points

■ PRE-DVD number of End Points

10%

0%

less than 0

0

less than 5ps

0

less then

**10ps**

**57**

0

less than

**20**ps

370

96

0.25

0.5

1.0

time (sec)

1.5

More than

**20**ps

1757

9904

## Generative AI: Revolutionizing Intel

How Generative AI Fuels Productivity, Sparks Innovation, and Enhances Decision-Making Through Tangible Success Stories

Accelerating

Excellence

#### Development

25% time-saving for software developers

#### Innovation

15% enhancement on creative output

#### Documentation

20% increase in productivity

#### Communication

10% reduction in miscommunication

#### Improvements on different use cases

| 0~5%           | 5~10%                 | 10~20%            | >20%                     |  |  |

|----------------|-----------------------|-------------------|--------------------------|--|--|

| Data Analytics | OKR                   | Creative Thinking | Coding/Debugging         |  |  |

| Calculation    | Email Coach           | Job Description   | <b>Proof of Concepts</b> |  |  |

| Reasoning      | Data Visualization    | Translation       | <b>Content Creation</b>  |  |  |

| Prediction     | Experiments<br>Design | Meeting Minutes   | Automated Documentation  |  |  |

#### Balancing Advantages and Considerations

#### Advantages

- Increased Productivity

- Enhanced Creativity

- Streamlined Processes

- Improved Communication

#### Considerations

- Data Security

- Accuracy Risks

- Ethical Use

- Responsible Implementation

#### The Future of Gen Al in GEMS

- AGS based GEMS RAG Chatbot Pilot 4Q24

- Exploring more use cases to increase productivity and efficiency

- Inspiring Gen Al insights in weekly open forum

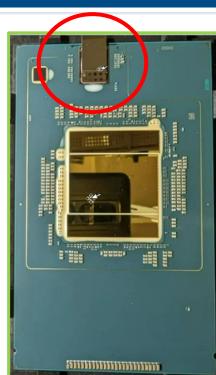

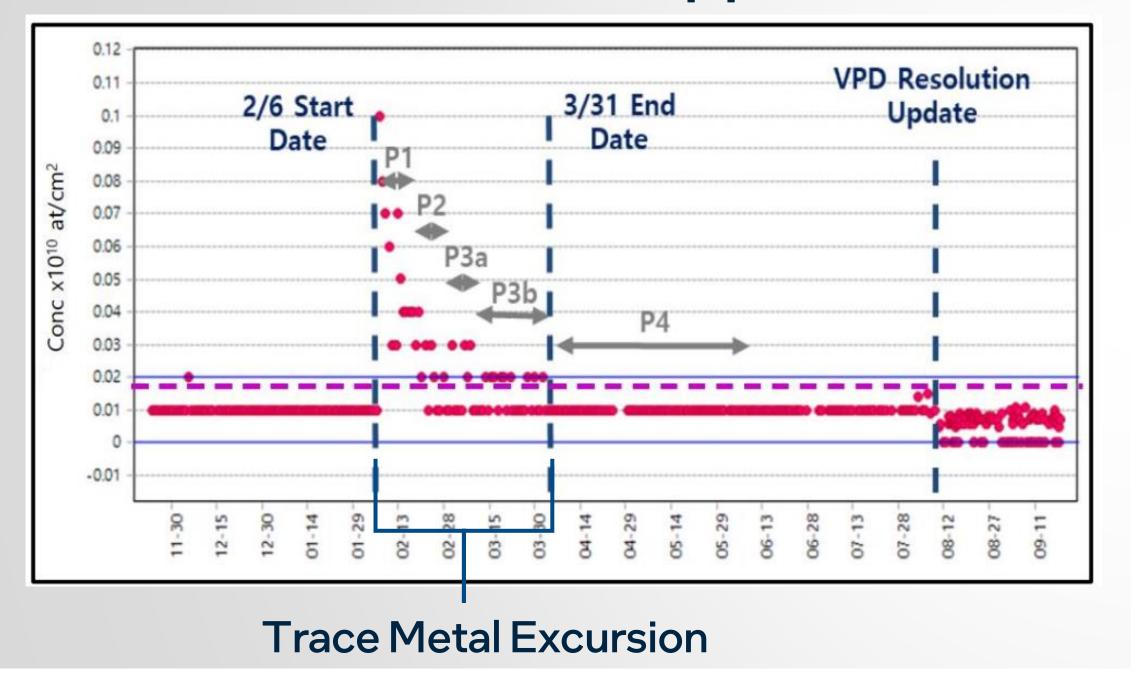

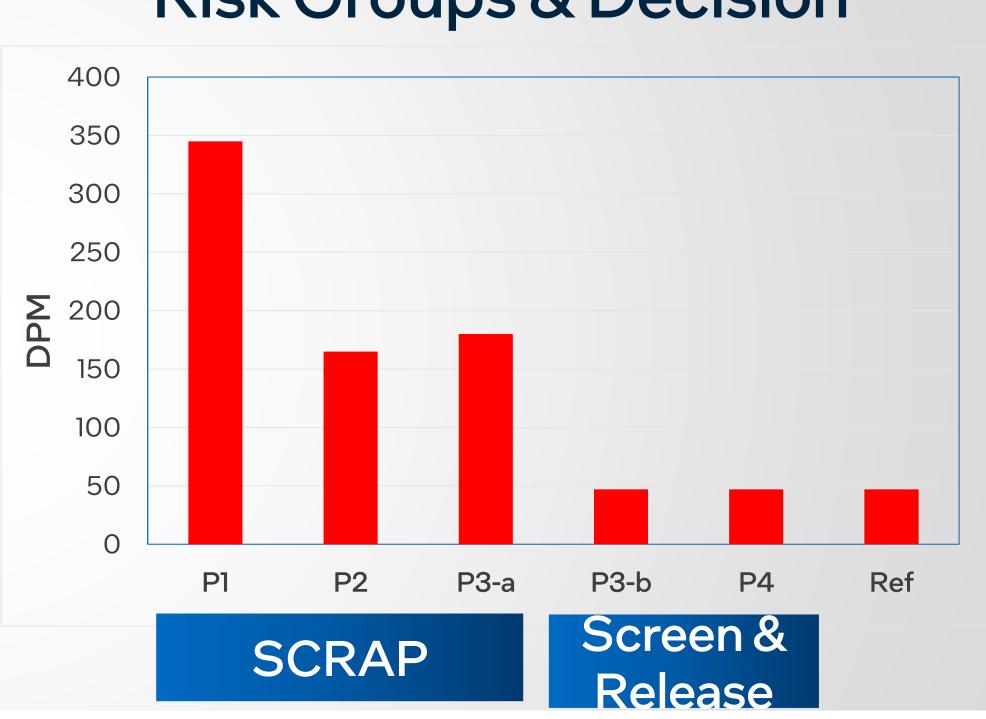

## 14nm PCH

### Total Management of Supplier Excursion

Si reliability detected, root-cause identified, customer recall prevented, materials screened, scrapped and replaced at \$0 to Intel

#### Data Driven

Al detection, DOEs, Screening Development Scrap Decision

#### Supplier Partnersh

Fab root-cause

Containment & Prevention

Compensation

Build ahead

\$18M Value in 2024

#### One Intel Team

GEMS Engineering Q&R, Production Foundry Account Team Logistics & Planning

#### Execution

Tests, Shipment Mgmt Materials Disposition Replacement & Credit

#### Supplier Fab Excursion

Total Impacted

13,644 wafers (~8Mu)

~7 Weeks of Wafer Supply (Shortage Avoided by Build Ahead)

Shipped to Intel 12,279 wafers (7Mu)

Released

7127 wafers

(4Mu)

Scrapped at Intel 5152 wafers (3Mu)

Scrapped at Supplier 1,365 wafers (~1Mu)

~ \$670M Potential Recall Avoided (Intel Reputation Protected) \$18M Si Compensated

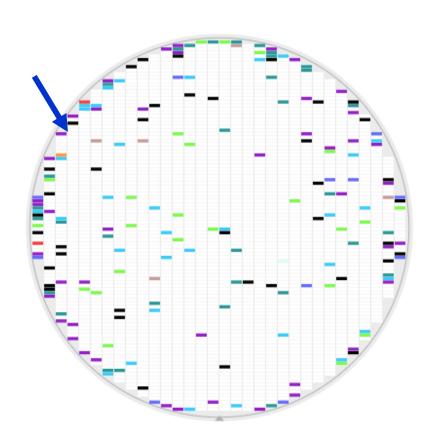

#### Metal Excursion, Supplier Tool

#### Risk Groups & Decision

Team Acknowledgement: EMP, QnR, EMS

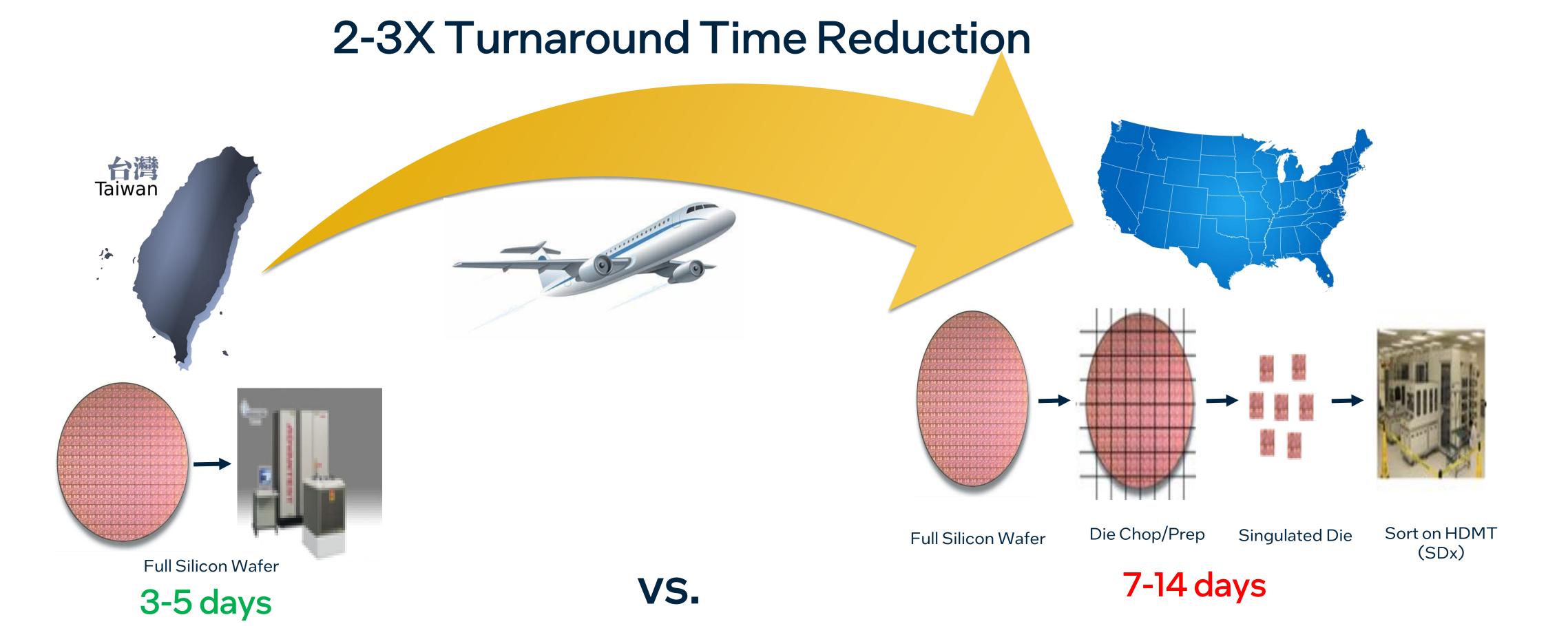

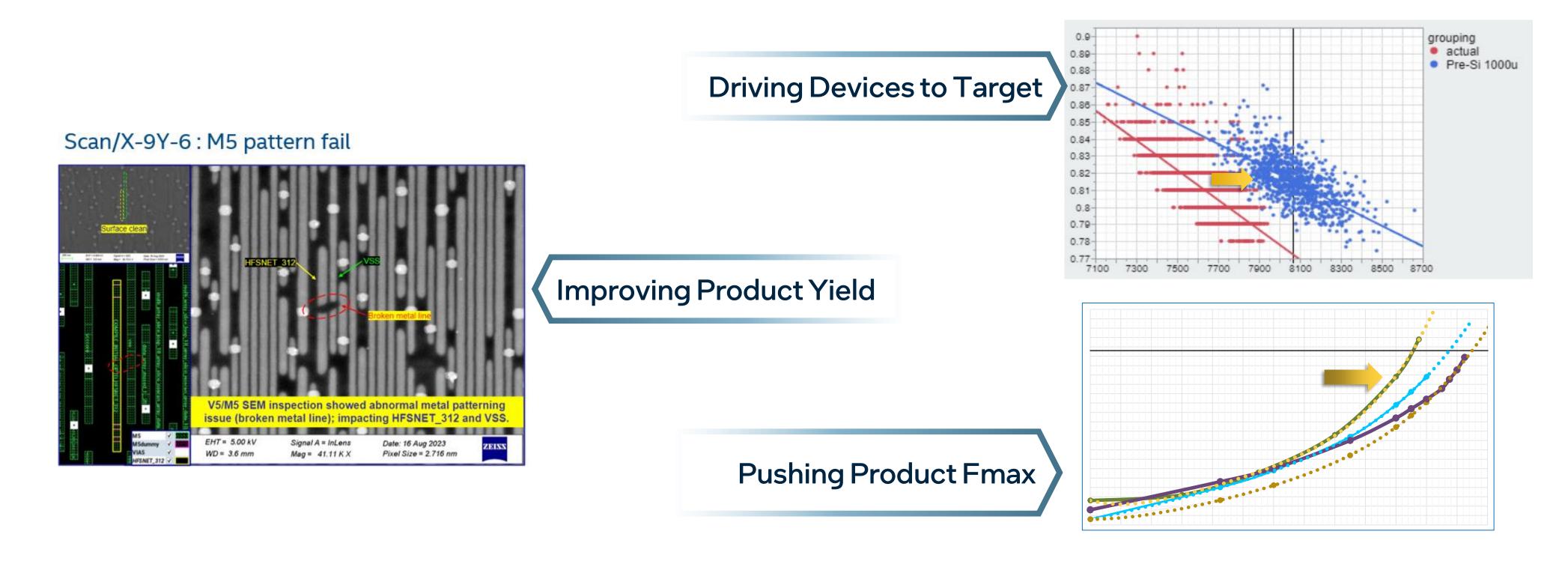

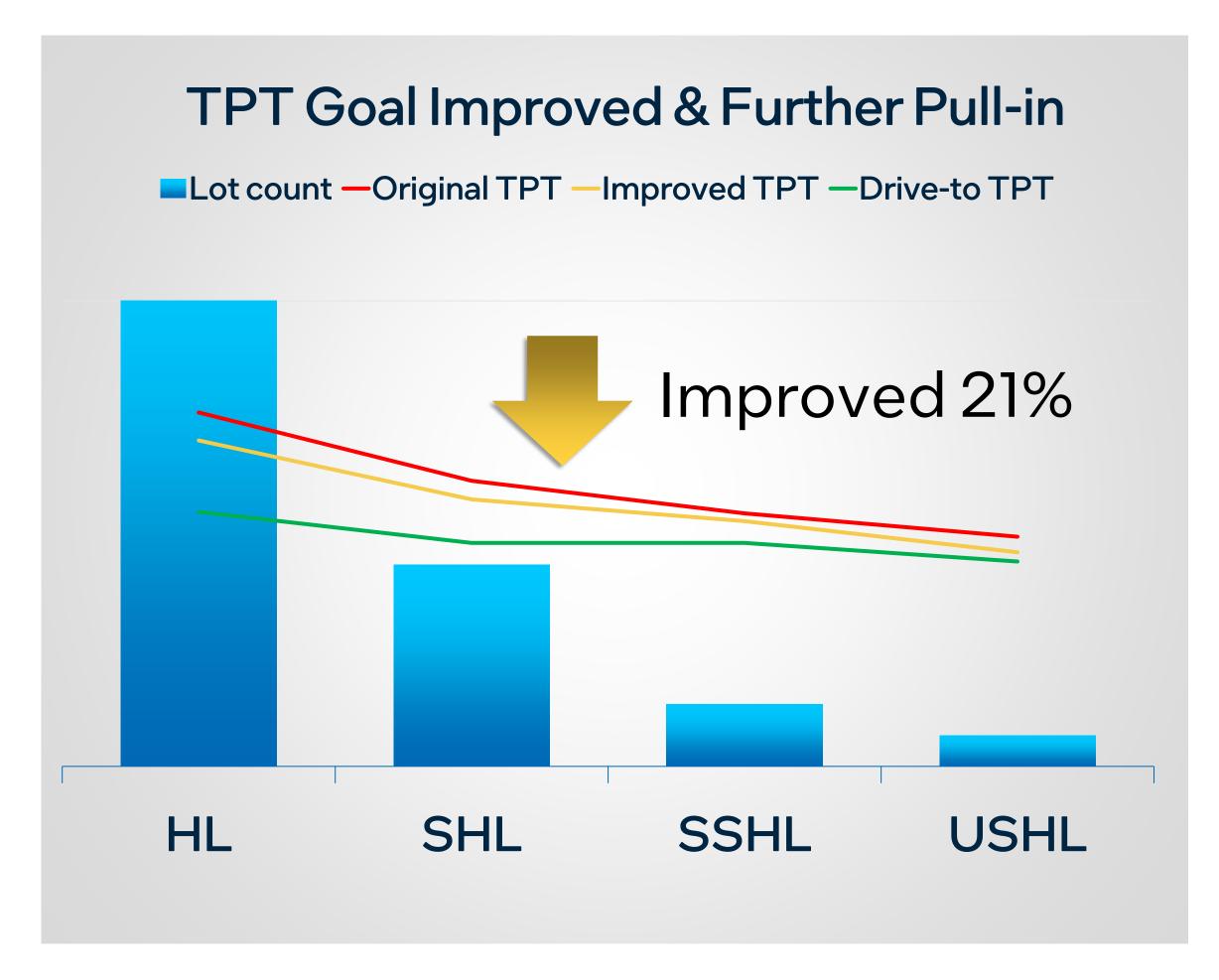

### Time to Yield Acceleration

On-Site Wafer Sort Enabling 2Q Pulled-in & 5% Fmax Push

#### Wafer Sort @ TSMC

- >\$10M wafers + CPU grade testers

(\$15 million) free of cost

- Physical Failure Analysis done by TSMC

## Improvement

>\$10M Free Wafers

2-3x TAT

~2Q Yield Pull-in

### Industry Standard V93K Test

- Access to best foundry talent

- Leverage Advantest Eco-System

#### **ARL NPI Impact**

- Earlier Sort PO (3 days)

- Atom bug identified; lead to quick A1

- CIP data I week before SDS

### Fast CIP & Yield Feedback

- Shorten yield learning cycle

- 5% Improved FMAX

- Quick TAT for ARL HPC drive

#### Faster Failure Analysis (FA), Yield Debug and Performance Improvement

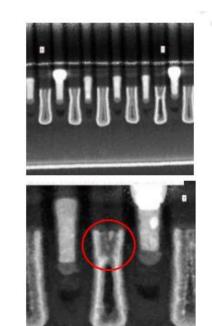

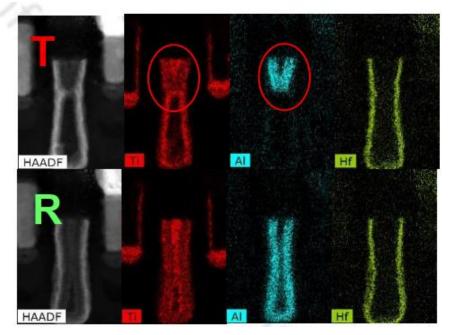

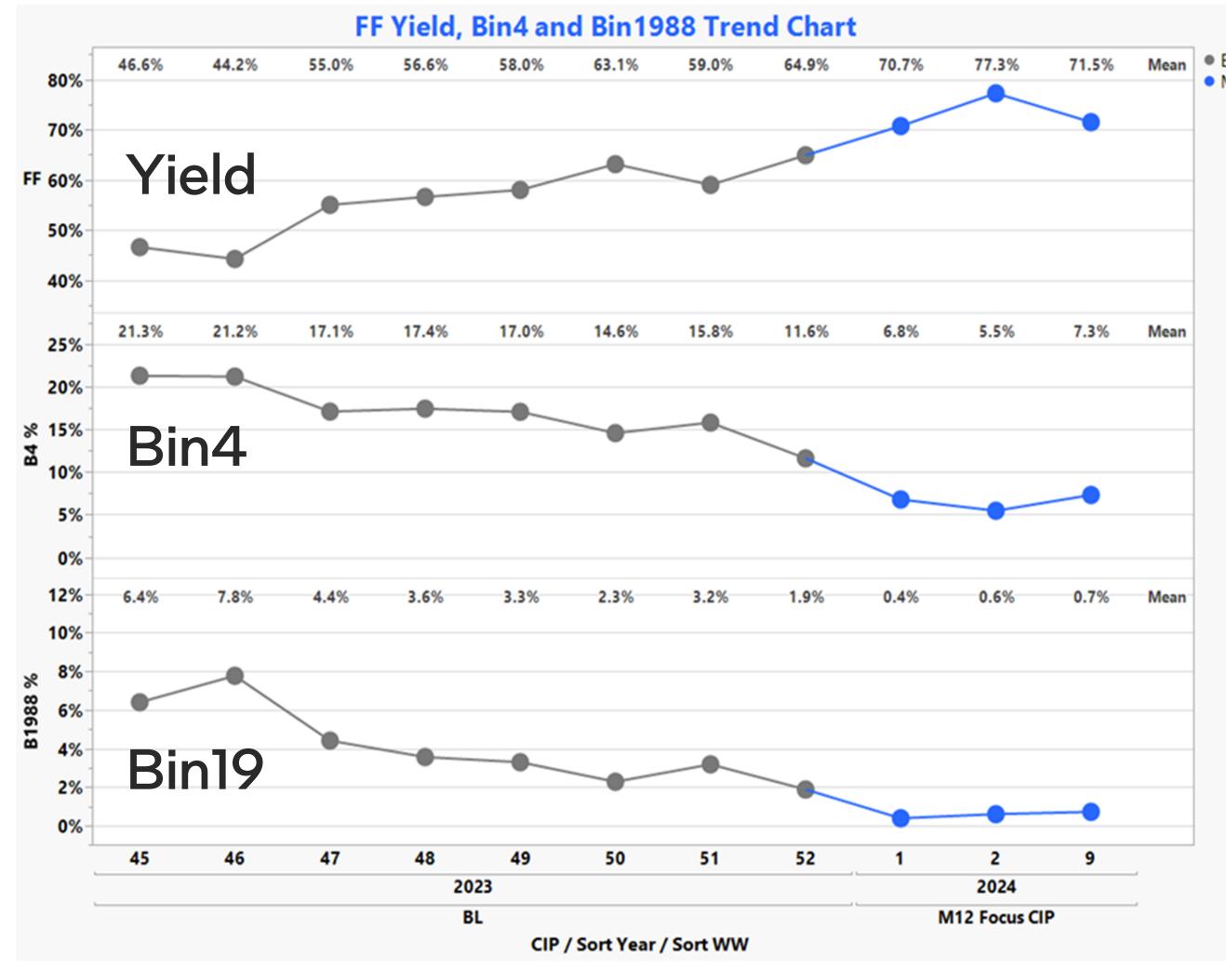

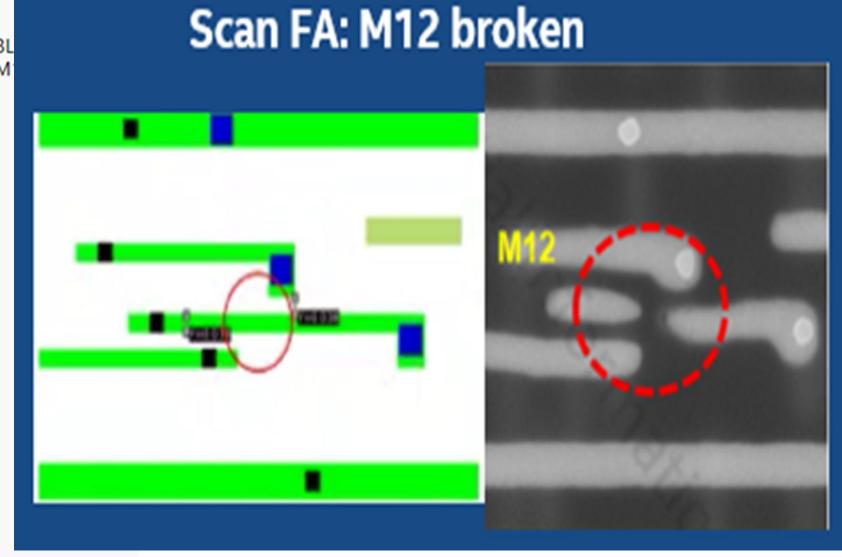

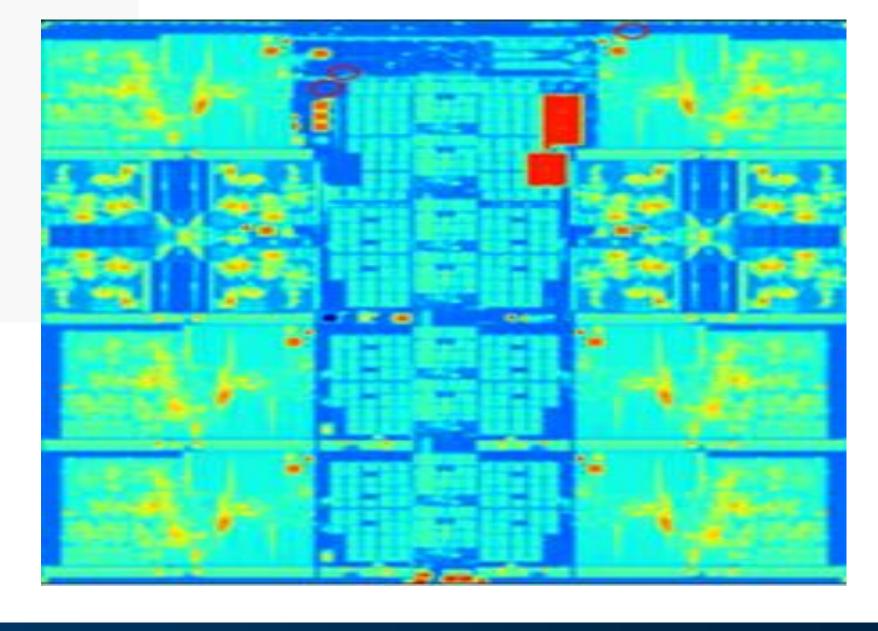

## N3B Yield Improvement

N3B ARL S816 A2 DTCO to improve yield by >10% Timely resolution enabled healthy ARL B0 production Silicon

#### Problem

- A2 Si showed ~ 23%

yield loss from

Bin4+Bin19

- 10% loss higher than projection

#### **Root Cause**

M12 broken due to interaction of

- M11 low density

- M12 unique layout

- Litho process

## A2 Yield increased by

>10% hitting 678 RISO

~2Q Yield Pull-in

#### **FIFA**

- FIFA challenging for Bin4/Bin19

- Leverage Scan and DC for fast FA TPT

#### **DTCO**

- ARL unique M12

Litho focus optimization

- Tailor process for design

- Baseline

- M12 focus CIP

#### M11 Density Map

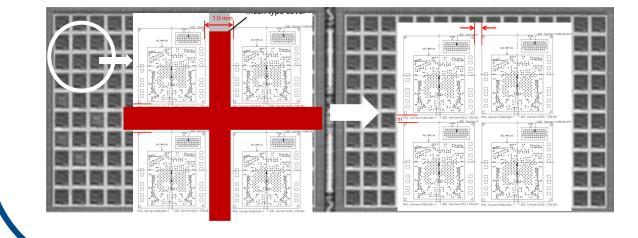

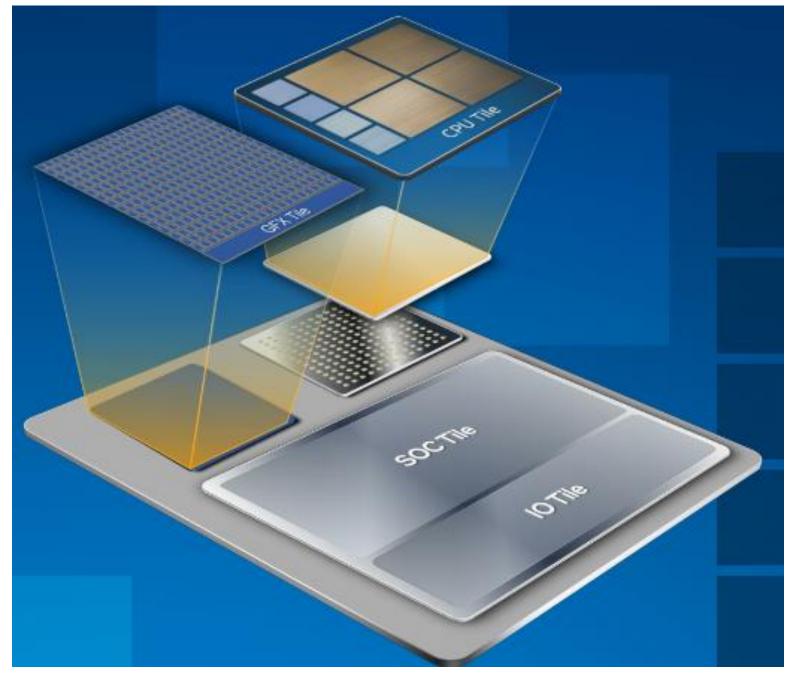

## Meteor Lake- flawless 5 Tiles execution to PRQ

Total \$176M cost savings /\$158M cost avoidance GEMS contributed to production since 2023

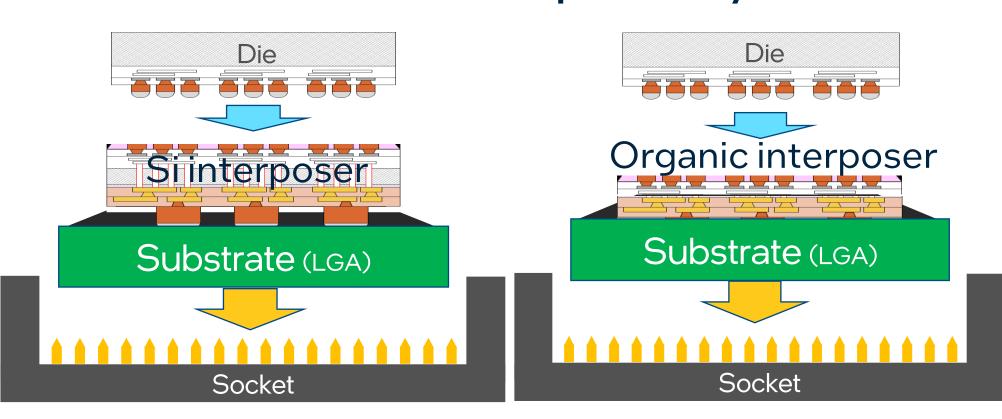

## Disaggregated architecture

N6 SOC/IOE, N5 GPU and intel 4 CPU assembled together by Foveros.

#### FA/Yield Learning

FA for systematic defect reduction and led to effective process CIP.

#### Enabled:

N6 SOC, IOE & N5 GPU and beat yield & DPM target

#### Process improvement

Total >70 CIPs to improve PnP, beating yield target.

#### **DPM < 400**

20 proactive CIPs to reduce BEOL voids enabling bake removal.

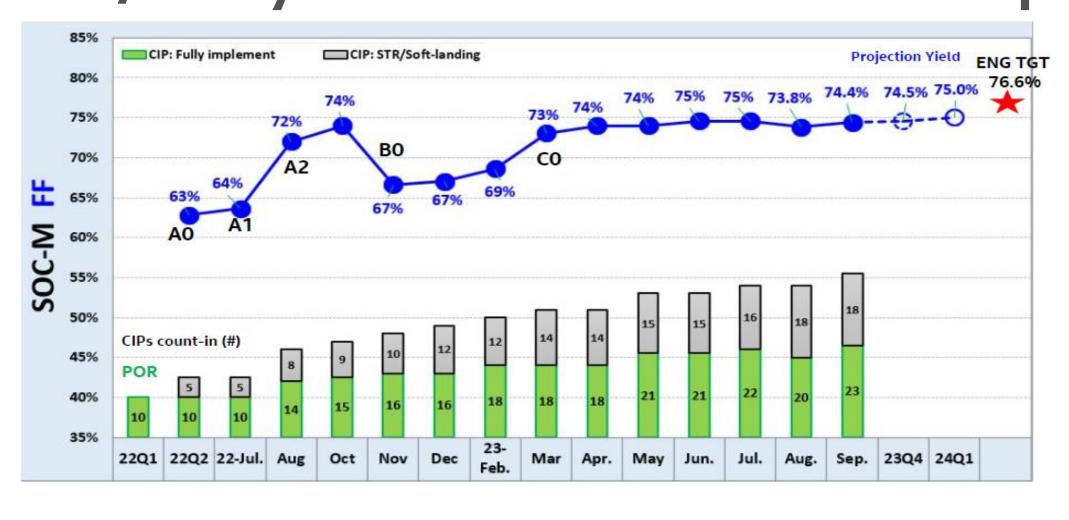

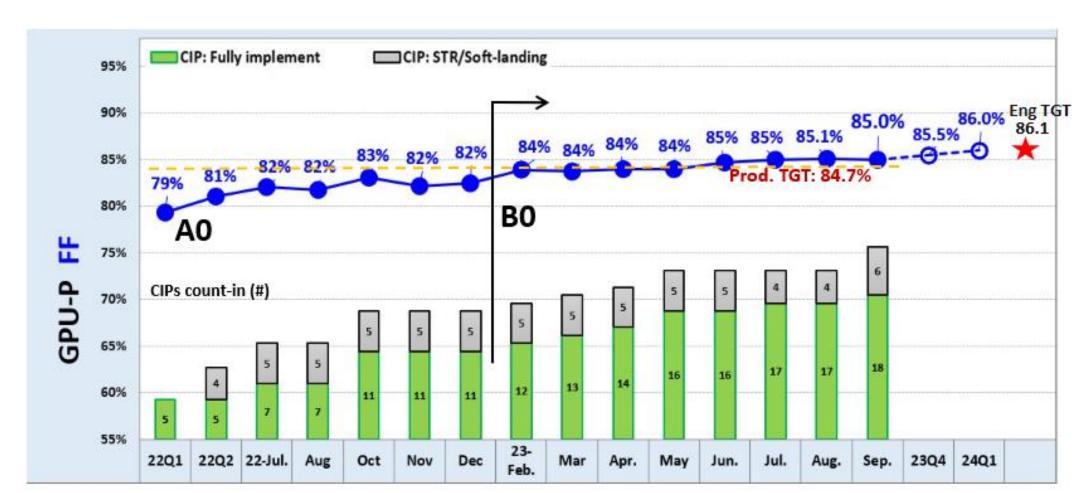

#### N6/N5 yield trend with CIP implemented

#### Meteor lake CPU architecture

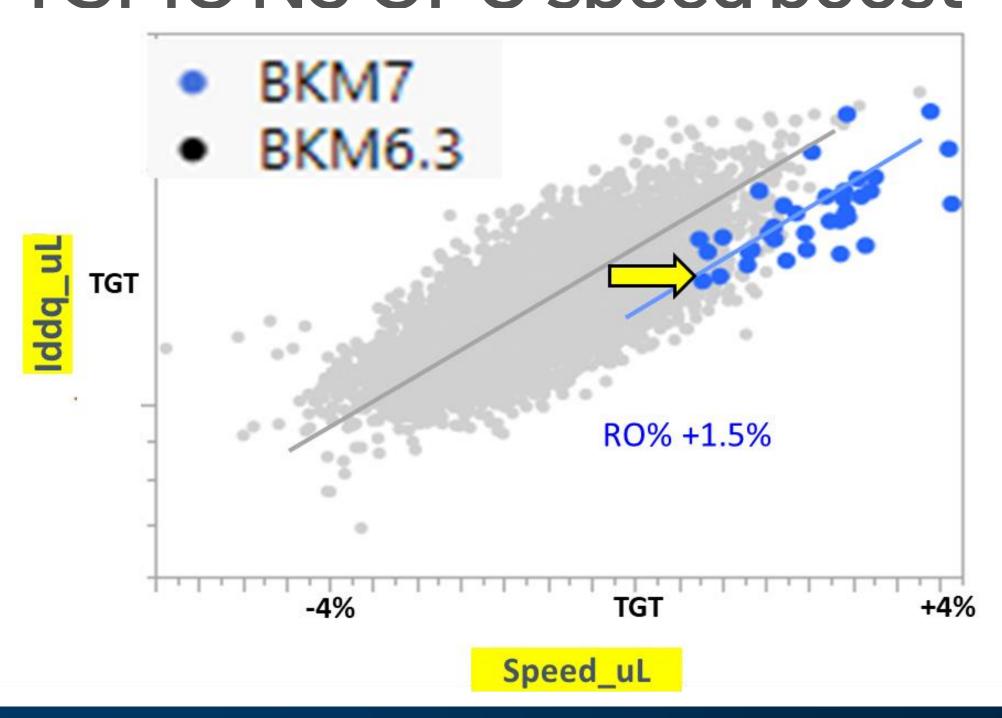

#### TSMC N5 GPU speed boost

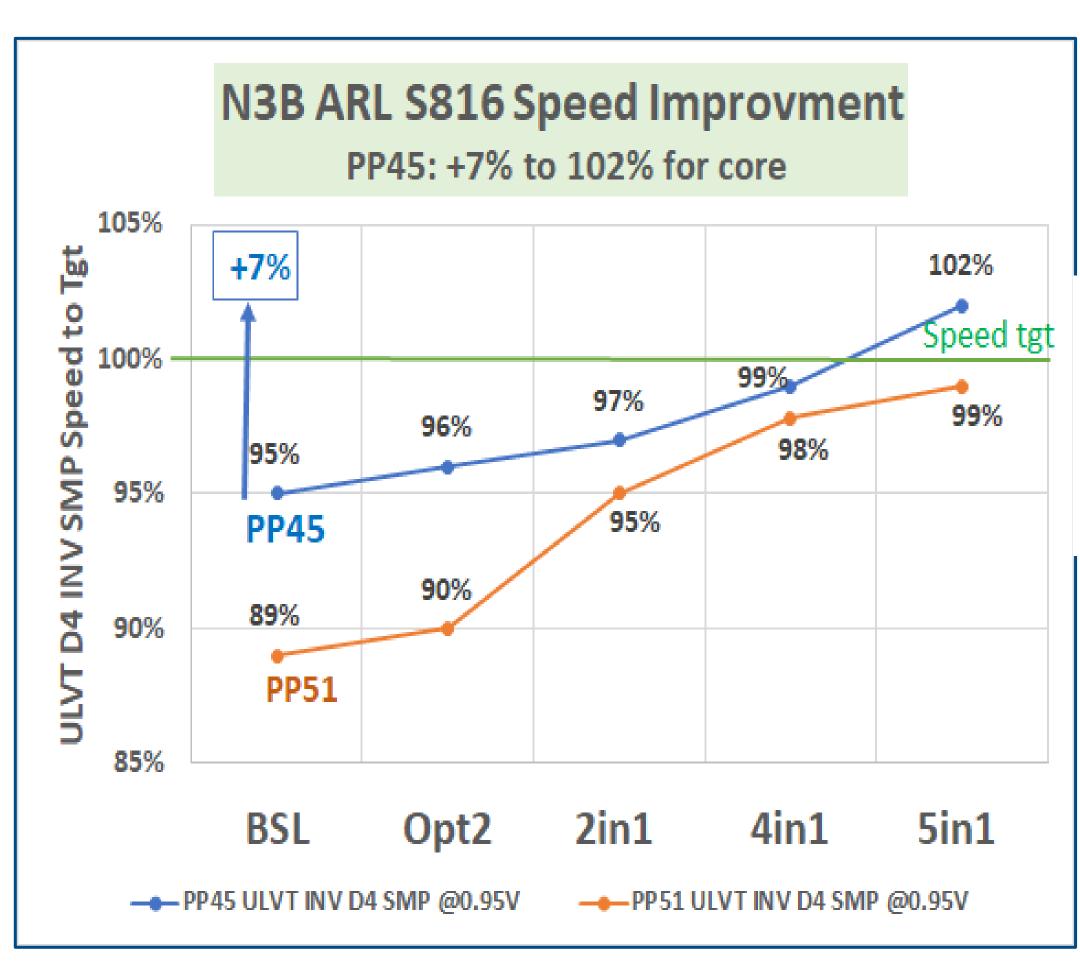

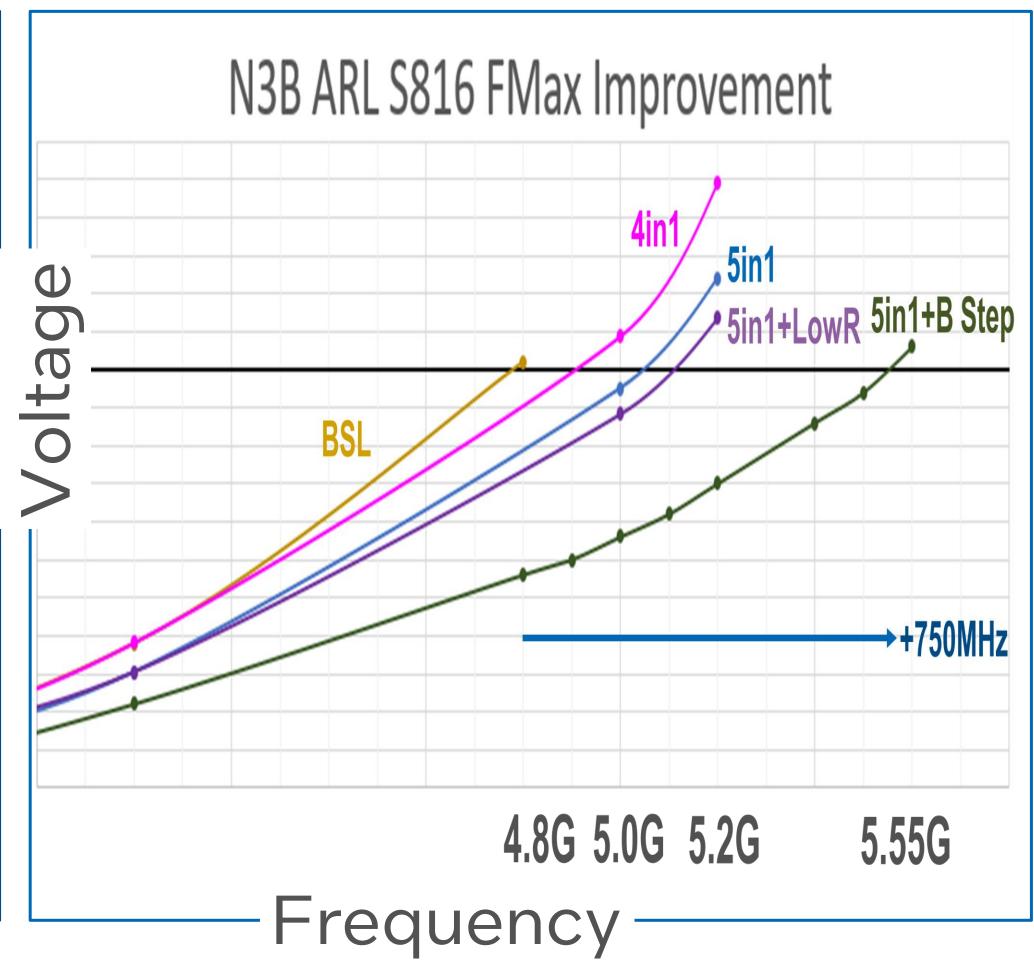

## Initiating, Driving, & Executing ½ Node Performance on TSMC N3B through Post Si Tuning with Iso-Design

Aggressive Targets

Set up clear perf targets beating PDK1.0

Acceleration

Drive left shift w/ V93K & MPE for Perf data collection

Perf data collection with 2X TPT

Development Partner

102%

Speed at

0.8X Pre-Si

Pwr Tgt

Work with TSMC for > 10 device CIPs executing in < 3 qtr

**Joint Ratification**

Finalize Proc POR w/ CCG, MPE, DEG

#### Risk/Decision Matrix

| CIP Gorup            | TSMC RO %<br>ULVT P45/51 | TSMC RO Poff<br>ULVT P45/51 | Core (5G) Vmin<br>MLC<br>1.09V | Total SICC<br>vs tgt | ARR Ring Vmin<br>(0.8G)<br>LLCDATA | Cdyn<br>LNC /SKT 0.95V<br>(% tgt) | Yield (FF+DF)<br>(CIP/ BSL) | TSMC<br>Rel risk | Go/no go to B0 |

|----------------------|--------------------------|-----------------------------|--------------------------------|----------------------|------------------------------------|-----------------------------------|-----------------------------|------------------|----------------|

| Starting BSL (A0/A1) | 89% / 84%                | 1.0X / 0.7X                 | 1.09                           | 0.5X                 | 0.62                               | 102%/ 82%                         | 82%                         |                  |                |

| Opt1+ Opt2 (A2 BSL)  | 91% / 87%                | 1.1X / 0.8X                 | 1.07                           | 0.5x                 | 0.60                               | 110%/83%                          | 74.8% (81F)<br>76.4% (81G)  |                  |                |

| 2-in1                | 91% / 91%                | 1.0X / 1.2X                 | 1.06                           | 0.8X                 | 0.58                               | TP issue/84%                      | 74%/82%                     |                  |                |

| 4-in-1               | 94% / 94%                | 1.2X / 1.4X                 | 1.01                           | 0.8X                 | 0.59                               | 111%/84%                          | 71%/81%                     |                  |                |

| 5-in-1               | 98% / 96%                | 1.5X / 1.3X                 | <1                             | 0.8X                 | 0.60                               | 111%/84%                          | 85%/78%                     |                  | GO WW4723      |

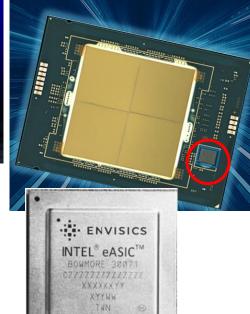

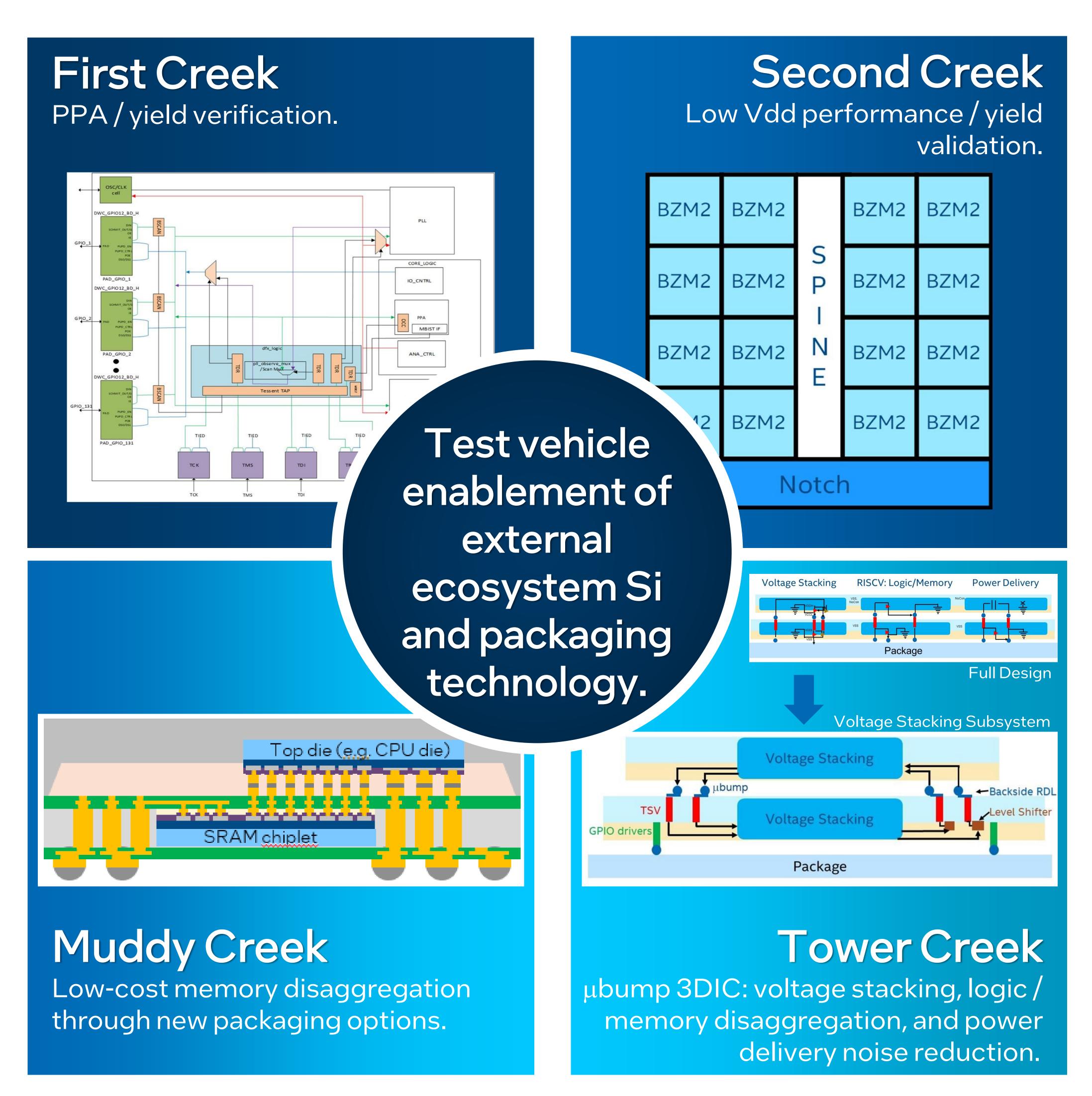

## FTE FTiP: External Technology Pathfinding Bringing Technology to Intel Products

Enabling external Si and packaging technology through Proof-of-Concept test vehicle design / test / optimization in support of Intel's roadmap.

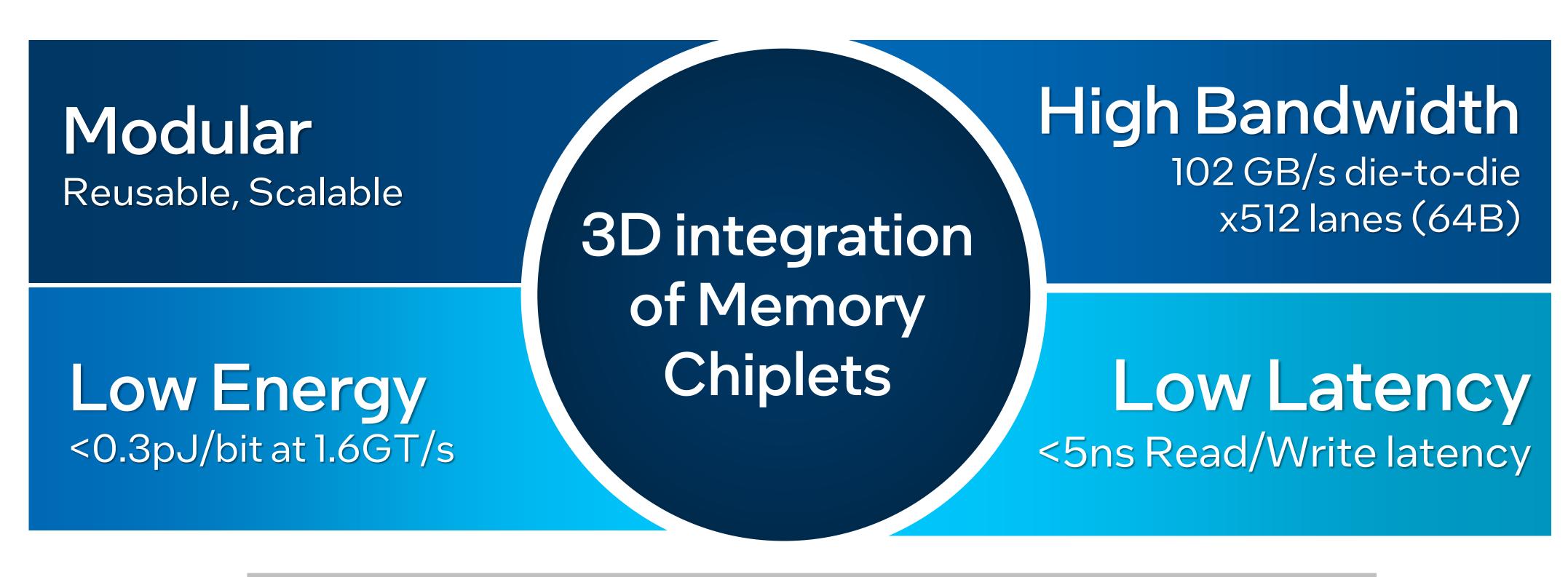

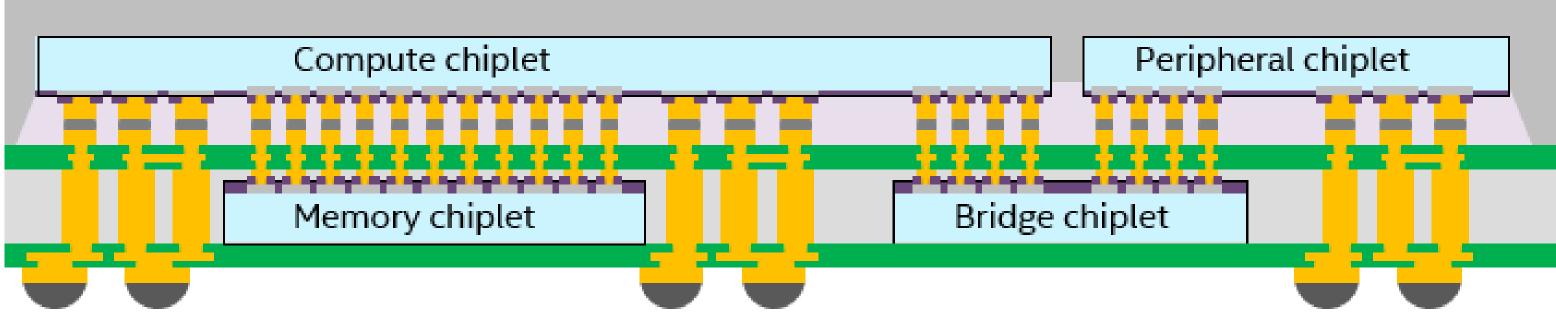

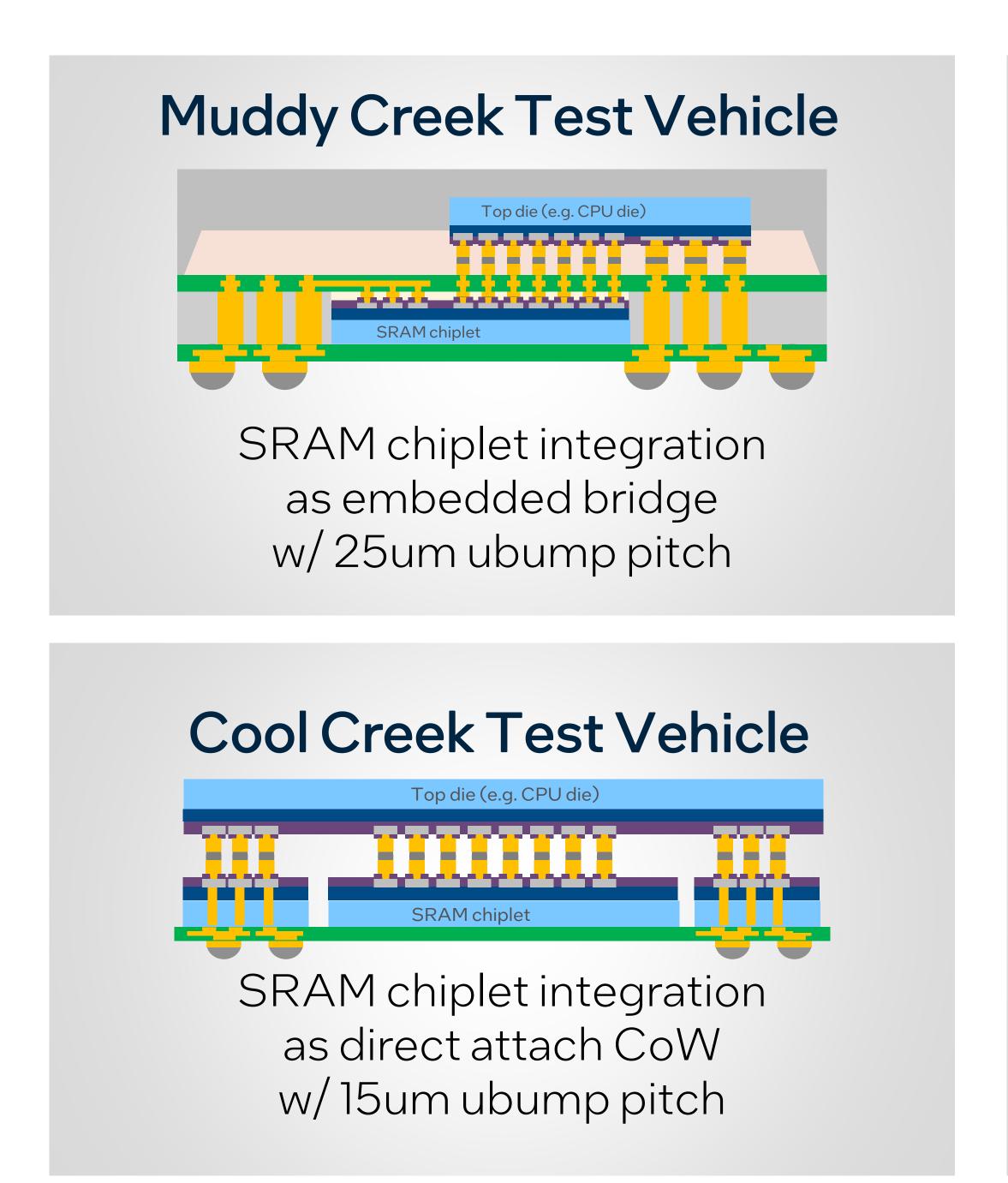

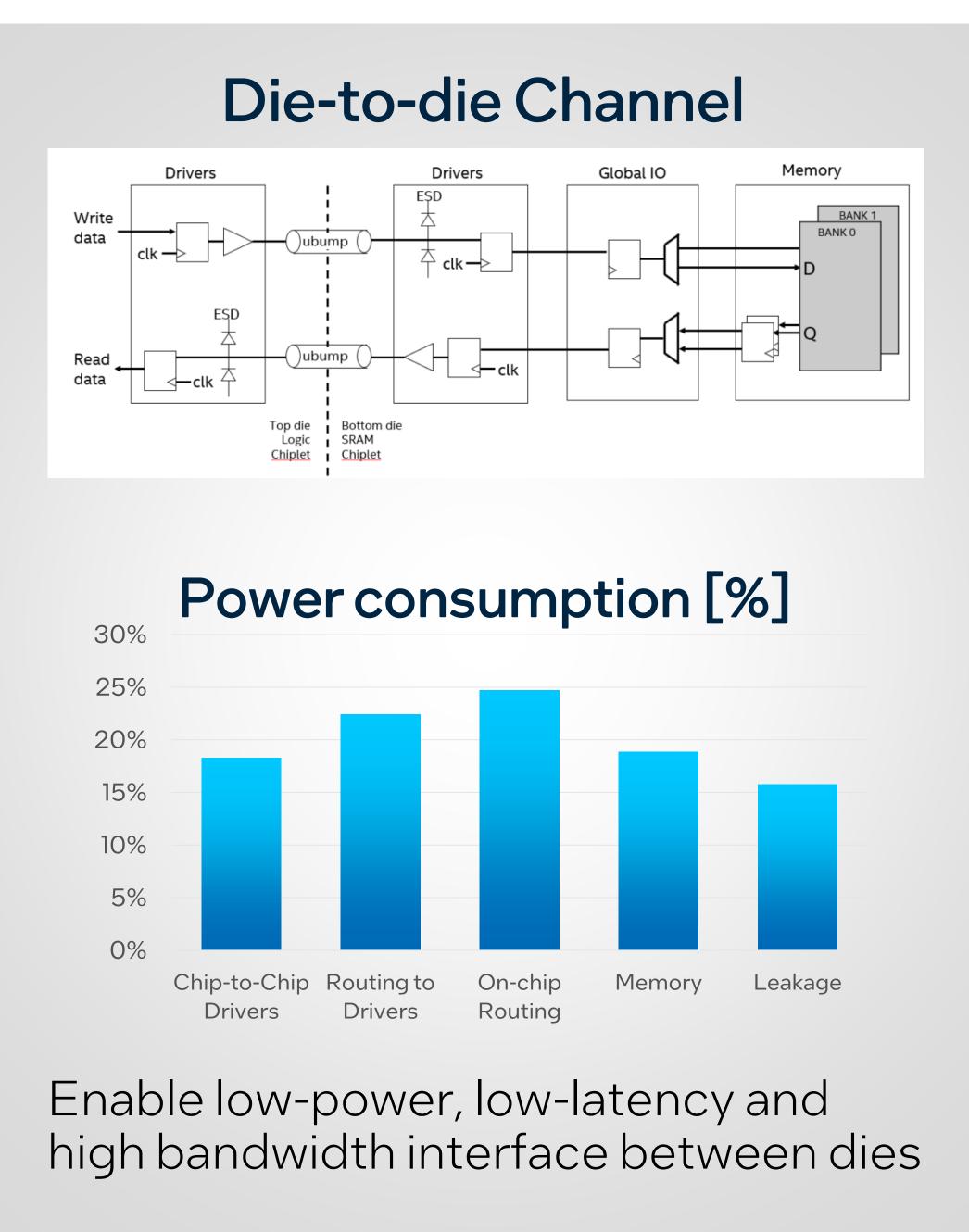

## 3D vertical integration of modular memory chiplets

Achieving low-cost 3D vertical integration of SRAM memory chiplets

Leverage supply chain to enable new capabilities

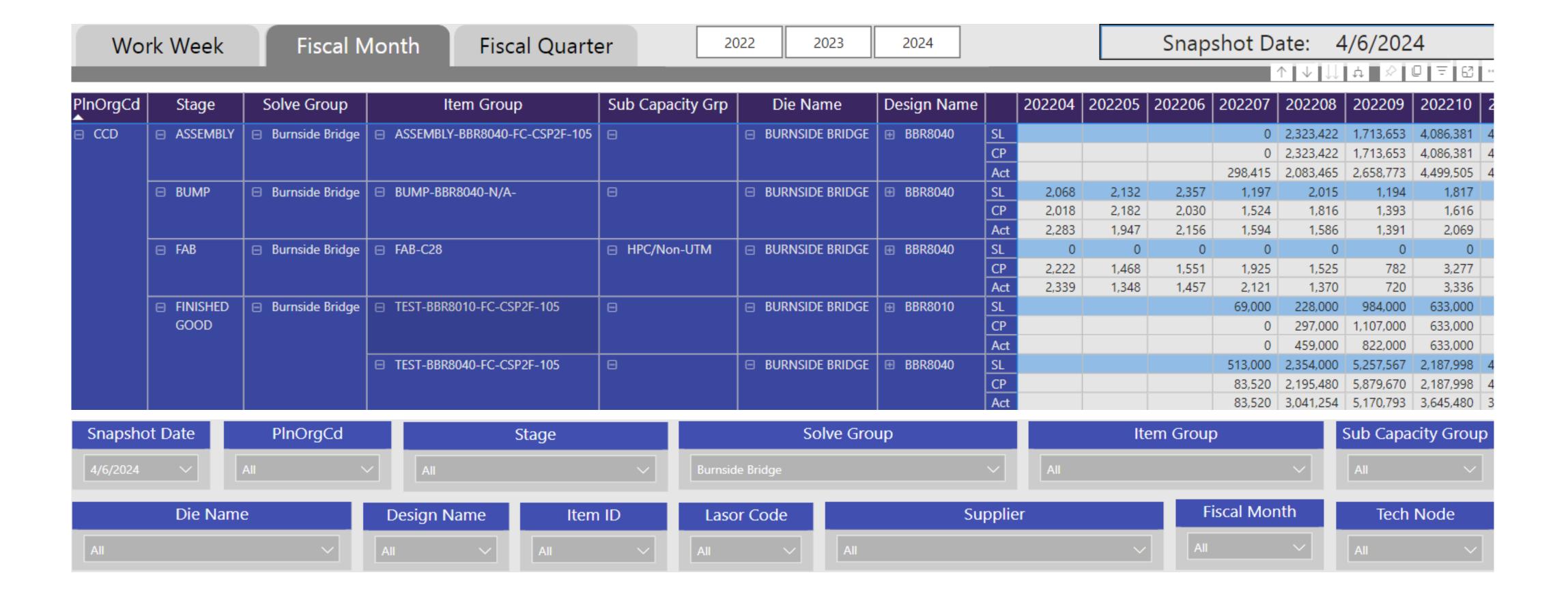

## Ext Mfg Order Report

Aligning historic Actuals/SL/CP stitch to data from SDA horizon. Result of collaboration between FOP SC, DCP, FOPO, DSPA, FOP OE & IT.

#### Product PHD (Predictive & Holistic Digital Strategy)

Authors: Marta Teixeira, Beilei Zhu, Virginia Pulmano

## Strategic Analytics Unleashed: Revolutionizing GEMS Strategic Planning and Spending

#### 0-5 yrs. Evergreen Forecast

- Pioneer Unification of 3 Planning horizons (SDA/MRP/LRP) Reporting for Comprehensive Product and Supplier Analytics

- External Manufacturing One Stop

Shop for Biz Units, Supplier Management and Planning Teams

- Near real-time reporting capabilities for about 1/7 of Intel's LRP COS

- Data load automation of >3.5k data entries and over 50k attributes

- Improved data protection by elimination of decentralized data sources highly susceptible to data breaches

- Automated Volume and Pricing Data Feed reduced Financial reporting time from 8 business days to ~1 hour

## >4Khours Saved per Year

- Report output time from 4-5 weeks to less than I week

- Publication of datasets time reduction from 24 to 1.5 hours

- Increased focus on Value-add,

Strategic work

## Azure Cloud Centralized Analytics

- Safeguarded Azure Cloud Infrastructure

- On Demand end –to –end Analytics

- Dynamic Data Source with Versioning and "What If" Scenarios

- Strengthened Self-Service BI Process

- Embarking on an Al Odyssey to Uncover Strategic Insights!

100% Employee & Stakeholder Satisfaction

- Data Quality, Reliability and Readiness has continuously improved stakeholder satisfaction cycle over cycle

- Improved Work-Life balance no more working extra-hours or weekends with noticeable stress reduction

### N3B Best-in-Class CPU Yield

Exceeding 6% product yield target before PRQ

#### **Great Collaboration with** MPE Sort/Yield

Established workflow to ensure content bring up with reasonable stability

product yield target achieved

>\$100M

#### Fulfill ES2 Upside Demand Meet EOL

2X more LNL design wins

**Successful Collaboration**

>\$10M FOC ENG wafers for

Fast PFA TPT support

with TSMC

yield learning

Increase Intel true AI PC MSS in 2024

#### FIFA Acceleration

- ARR Raster/SCN SPOFI enabled < 5 wks from first Si at sort

- 100+ PFA samples done at Intel PFA labs in PNG/Oregon/IDC and TSMC

Cost savings

LNL\_CPU SDS Yield% (FF) 1000 900 75 70 800 65 700 SDS YIELD (%) Q T 600 60 55 500 50 400 45 300 40 200 ımprovement 100 35 306 304 308 308 318 318 310 315 316 32A 32B 32E 32F 32G Max Yield (FF) Qty(pcs) Yield(FF,%)

100+ yield debug FA performed

Increasing Test Coverage

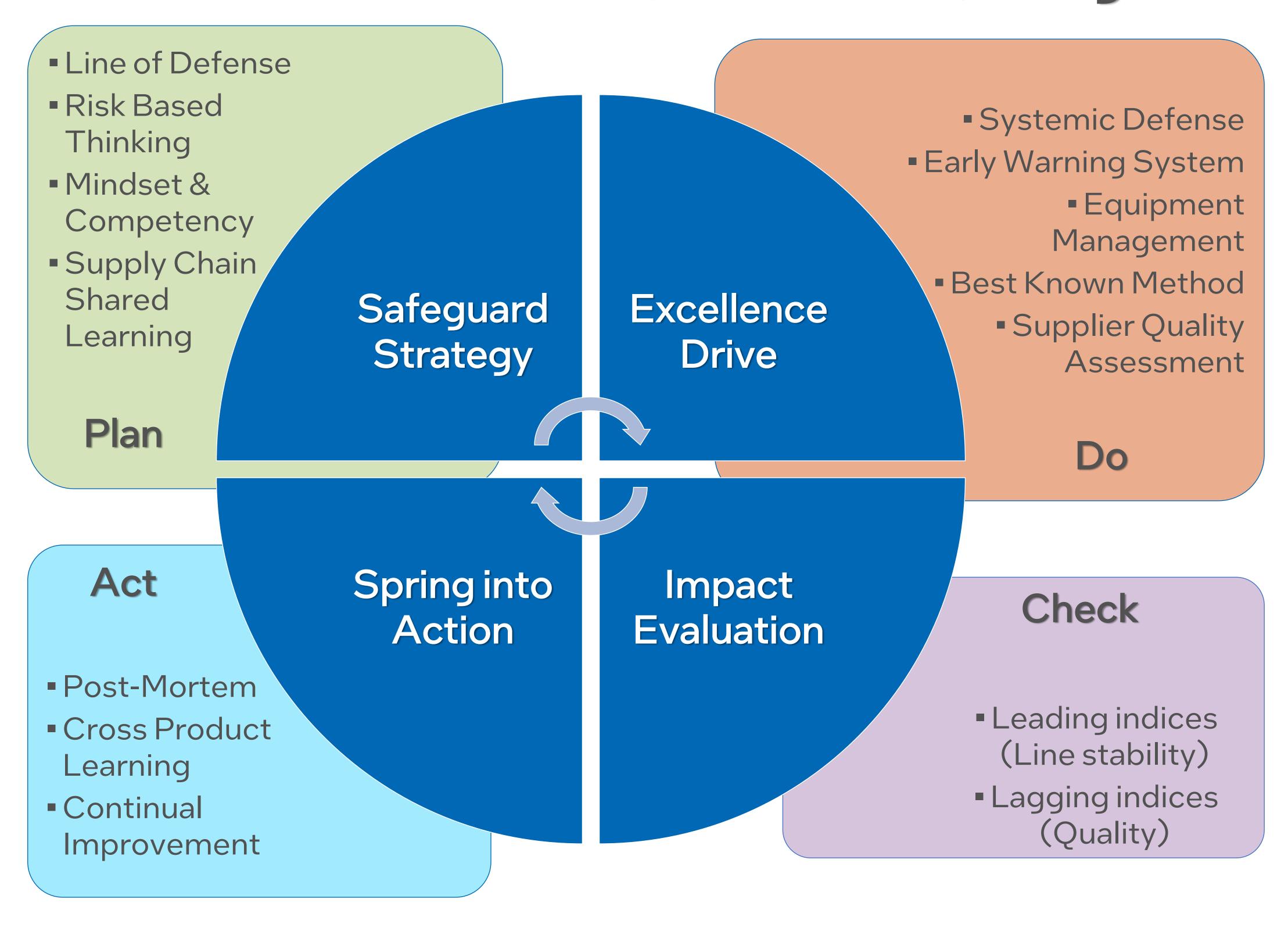

## Quality Mindset 1<sup>st</sup> Zero Defect Zero Excursion

Quality as Top Priority in meeting Primary Customer's Expectation Strong Partnership with our External Supplier as One INTEL Influence Value of Quality Mindset First Avoid Supply Chain Impact & Cost Saving

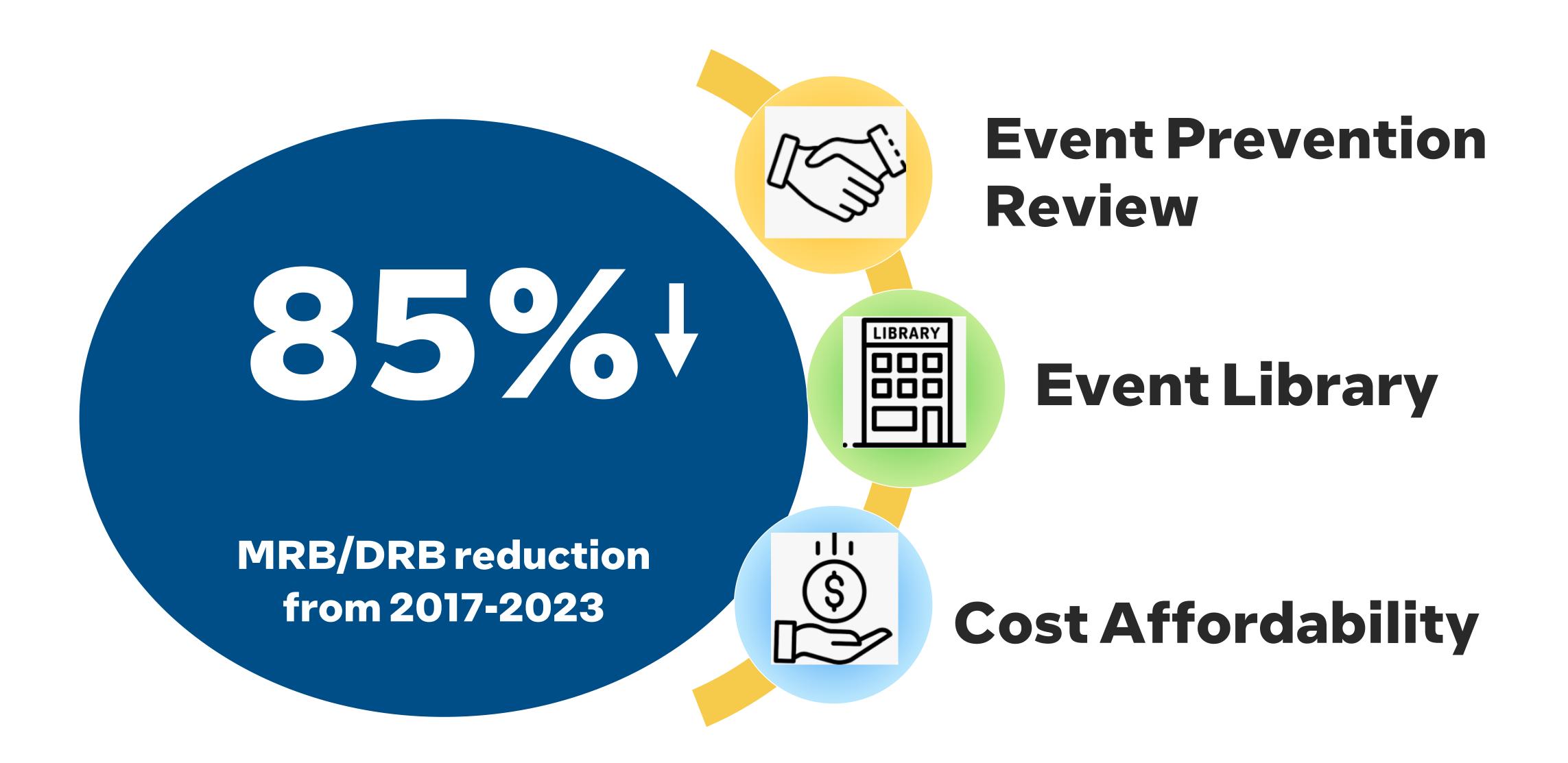

#### Excursion Reduction (Prevention) Program

Quality performance of a Foundry Supplier

Partnering with Our Suppliers

makes Total Quality Defense

Never have to say Sorry

to your Customer

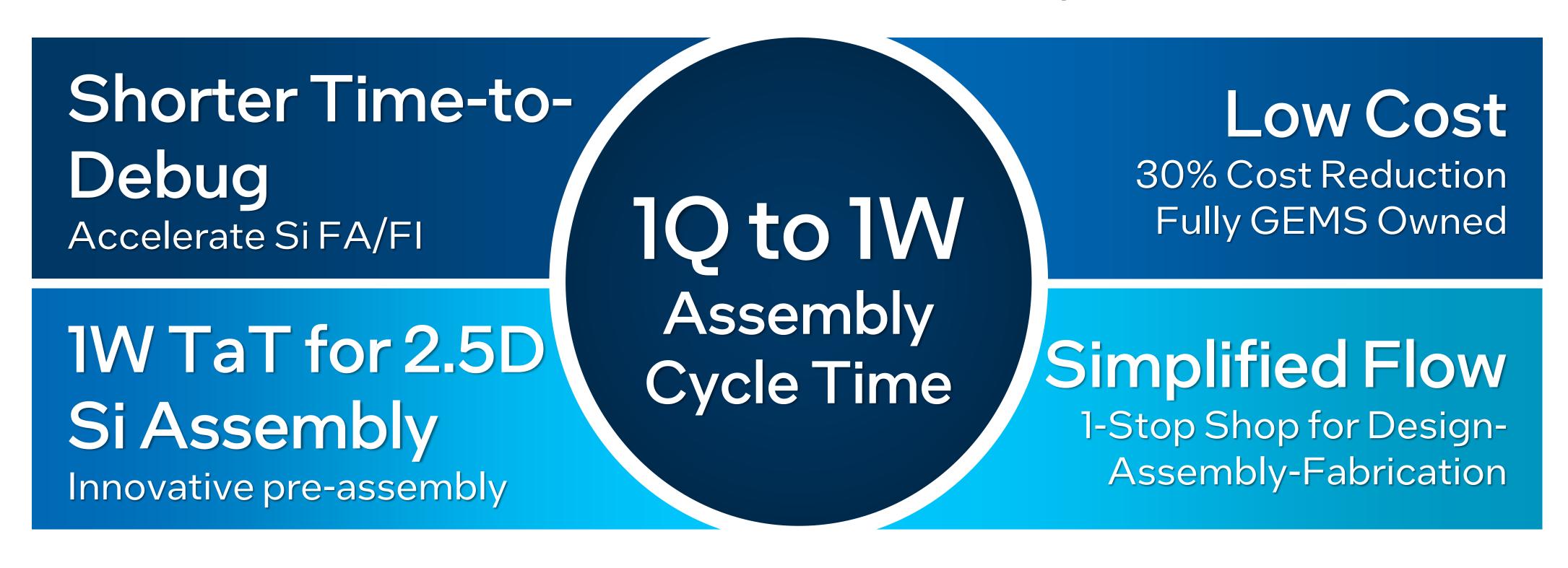

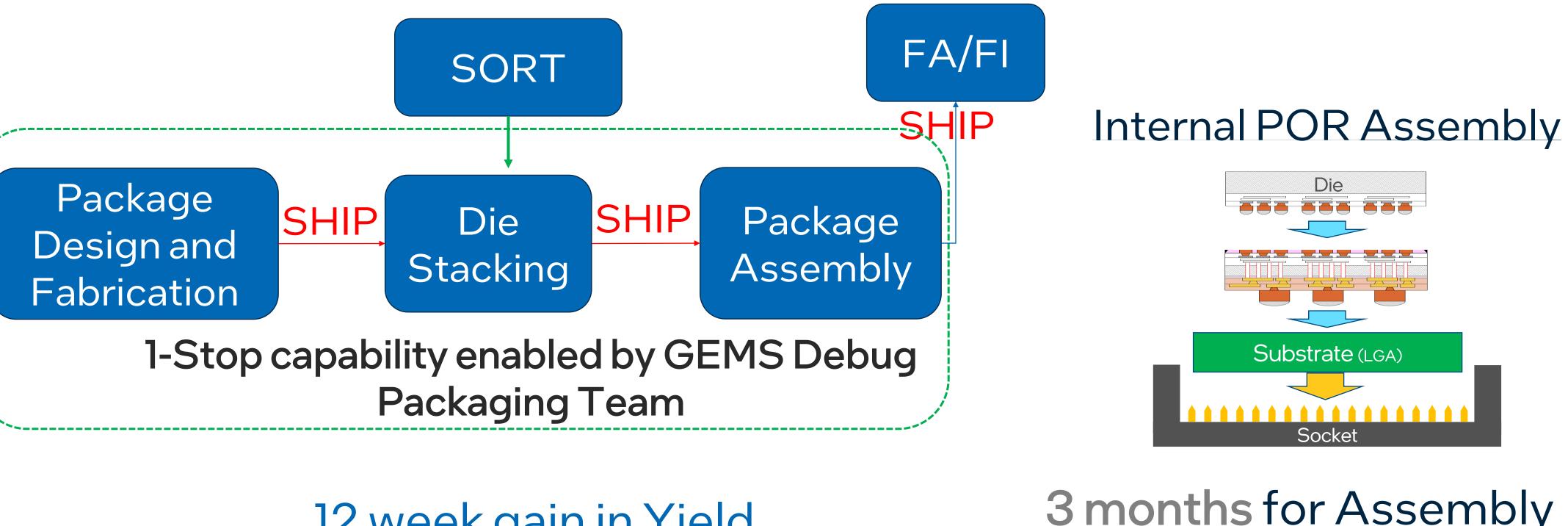

## Torrid CT for 2.5D Assembly

Cost-Effective Solution for Accelerated Si Debug with 1W TaT for Assembly

#### Simplified flow in GEMS Package Debug Assembly

Trend

A1

A2

51.6% (171pcs)

67% (42pcs)

72.5% (26pcs)

1.1%

1.1%

1.1%

1.1%

1.1%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1.5%

1

3 months for Assembly VS.

**GEMS** Capability

1 week for Assembly

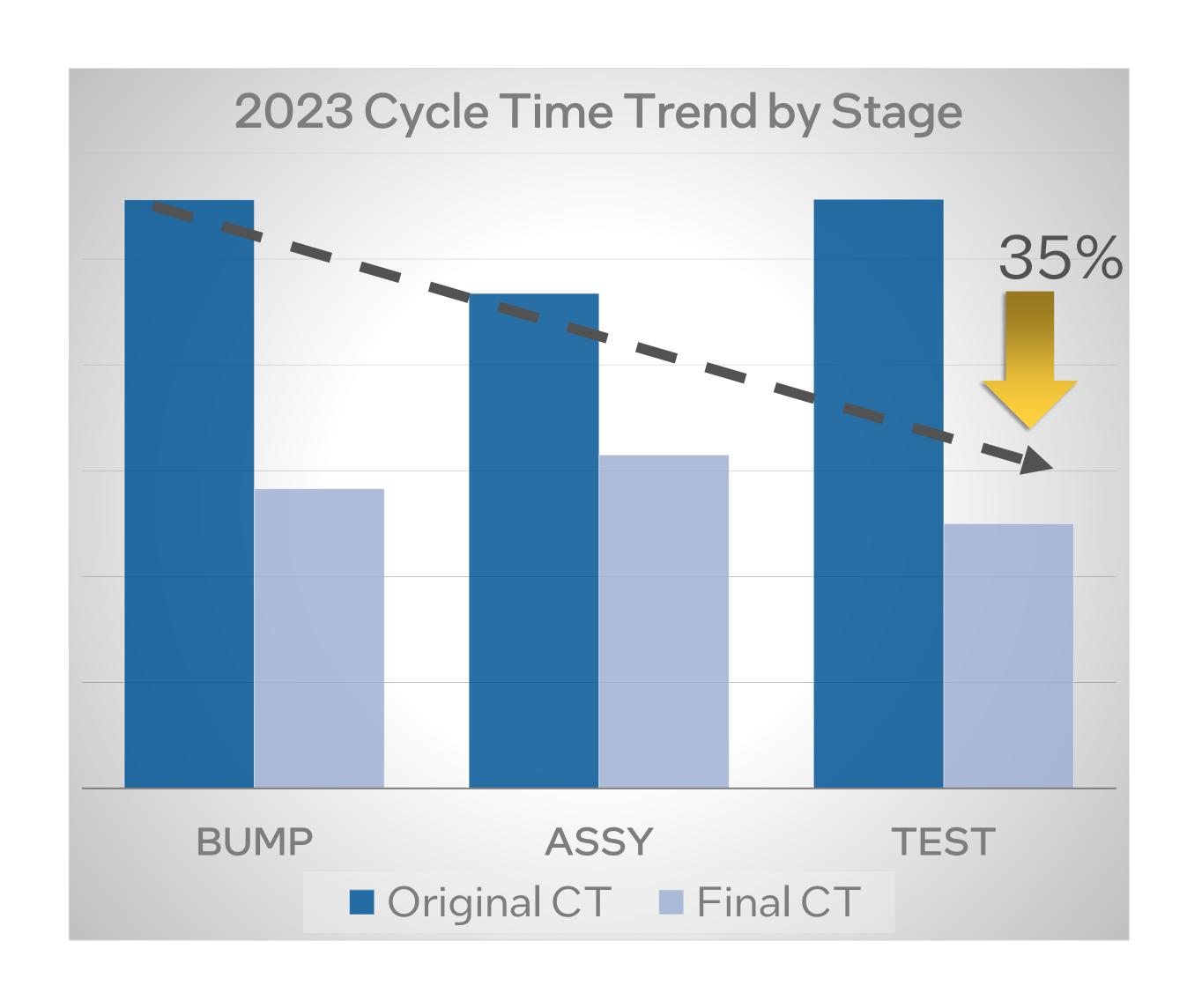

## High velocity OSAT Cycle Time

35% CT reduction for production volume

#### Partnership

Collaboration

Negotiation with OSAT

#### Capacity

Supply improvement Enhanced supply flexibility \$7M Positive cash flow

#### Intelligence

Data driven approach Benchmarking

#### Execution

Disciplined monitoring Continuous improvement

Optimizing end-to-end CT across manufacturing stages by 1-2 weeks

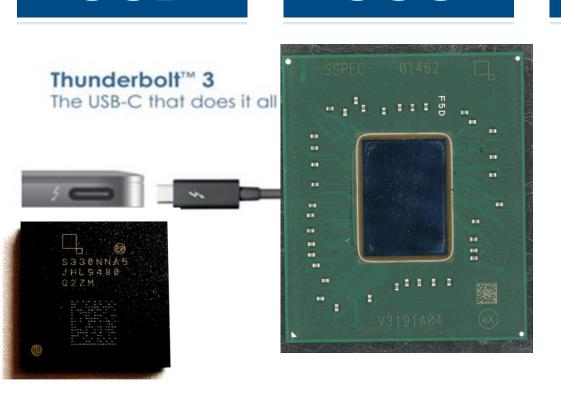

Products

Thunderbolt

OSAT CT improvement

From 34 to 25 days

WIFI

From 27 to 18 days

Established systemized approach for application to other products and technologies, e.g MTL-PCH

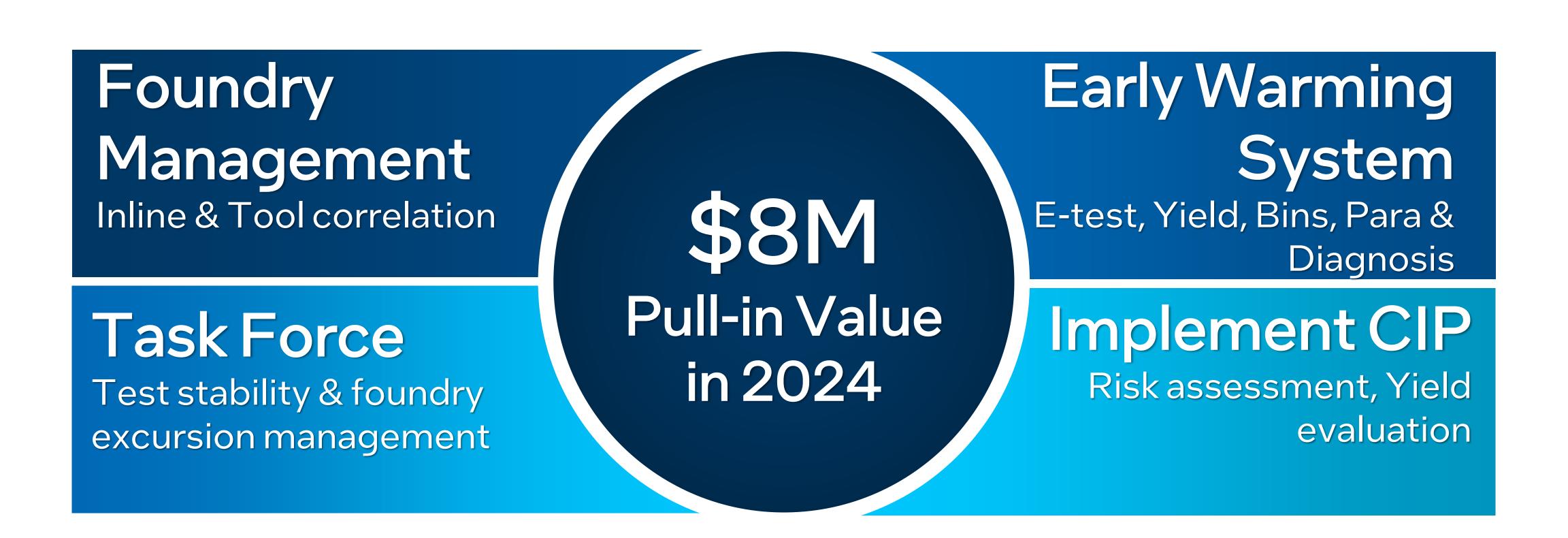

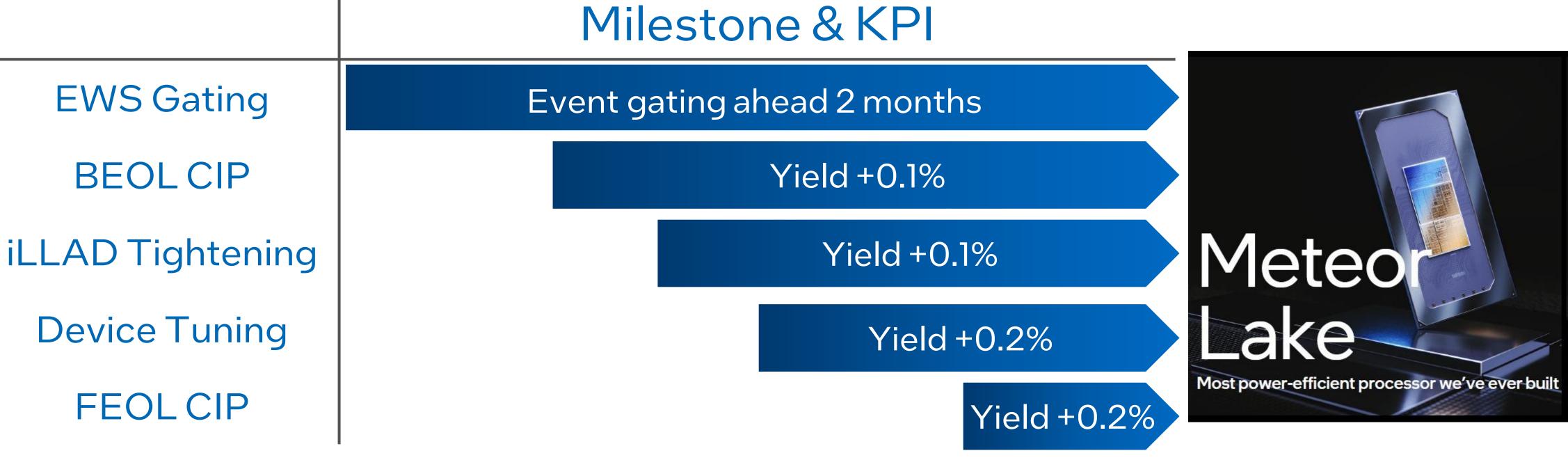

### MTL HVM Achievements

Developed a promising system for foundry management and test stability

## iLLIAD rule tightening Hold rate reduction 10% Hold rate

24'M3

24'M4

Test Overkill Reduction

#### g - - 0 Q2 Q3 Q4 Q3 **Q4** Q1 2024 2023

Yield Roadmap

24'M2

24'M5

## Change Control Board Powering Intel's IDM 2.0

\$+2.1B

Cost Affordability GEMS Contributed

#### Yield Improvement

- 1. Contributed \$9.8M for cost saving and \$2.8M for cost avoidance

- 2. Evaluated over 100 BKM from 4 foundries

## **Business Continuity**

- 1. Contributed Revenue support of \$2 Billion

- 2. Avoided revenue interruption for 10K+ wafers and 10+ products annually.

#### Reliability Enhancement

- 1. Further enhance wafer quality and reliability

- 2. Achieved 6.5% VBD improvement by BKM implementation

## **Excursion Prevention**

Zero excursion to CCB change in 2022 and 2023

## Long Road to the Victory 14nm PCH Foundry Excursion Management

Work accomplished by One Intel Team GEMS EMP FM, MQE, EMS, QnR, F24/F28/CDAT/VNAT

Wi-Fi7 Yield +3%

## \$2.6B

### WIRELESS

#### **Outstanding Products**

GEMS secures billions in revenue preservation and over \$10 million in cost saving by foundries':

#### Sustainable Delivery

Second-source photoresist sustained business continuity plan and prevented \$2.6 billion in cost losses.

# MVT Yield

#### Continuous Process Improvements

in Wi-Fi 6E with strategic Si gate height control, contributing \$1.82 million cost avoidance from module yield enhancement.

Wi-Fi 7 executed defect reduction and device optimization, leading to \$11.76 million cost saving from a 3% yield gain.

Capability

Affordability

Stability

## Manufacturing Affordability

+50 Products Sustain

+90 Projects Acceleration

+131M Affordability Contribution

---One Intel---

# PROPELLING 28NM PRODUCTION YIELD TO GLORY

Achieved cost savings of \$6.9 million through collaboration with BU and Foundry

Synergized with BU to achieve remarkable yield improvement

FXL +\$4.0M Yield +2.8% HDB +\$1.4M Yield +33.0%

4\$6.9 Million

Engineered foundry

CIPs to elevate

product quality

MPR & HDB +\$0.3M Yield +0.8%

Investigated device window and strategically prioritized to fulfill customer demand

CLF+\$1.2M

## EARLY WARNING SYSTEM IN HVM

Monitoring overall exceeds 400 diverse items to early detect abnormality including inline/device performance/testing automatically daily.

#### PCM

- BSL Drift & Variation

- Excursion abnormal (Lot/Wafer/Site)

## Datalog BSL Drift &

- BSL Drift & Variation

- WiW Uniformity

#### Performance

RO performance monitoring

### Yield

- Yield P90&P10 monitor

- Field related index

### Diagnosis

- FMA for Logic

- Signature analysis for ARR

## EWS pre-warned 30+ cases successfully for MTL in 2024

#### Achievement

**Automation System**

Daily Warning

Trigger rate Monitoring **2024 Goal**

**Execute in ARL/LNL**

Accuracy reinforcement

### **Excellence in Foundry Excursions** Castaway

Contributors: EMP\_FM and GSMQR

#### Efficient preventive action review

#### Web-view event library cross suppliers

### Leads to save invisible cost affordability

## Torrid Fast Cycle Time

Expedited >6,000 days for >430 NPI lots without extra cost (average pull-in 2 weeks/lot)

#### NPI Wafers Pull-in

Meteor Lake 173 lots, 17 days Time-to-market

Lunar Lake 36 lots, 10 days

Arrow Lake 53 lots, 22 days

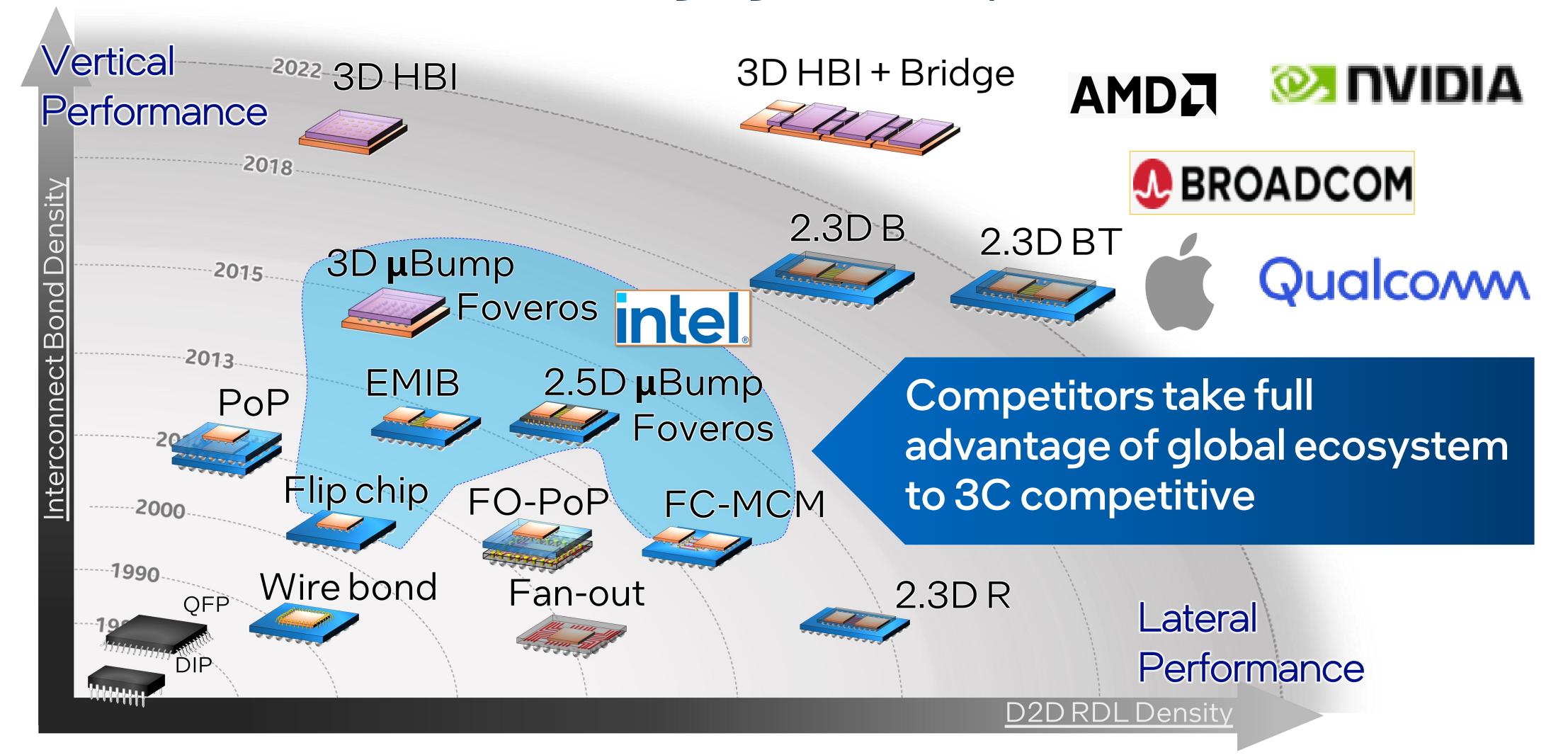

## Packaging Idea to Production

External Packaging End to End Solution to Enable IDM2.0

#### NPI Project Summary

#### External Packaging Landscape vs. Intel's

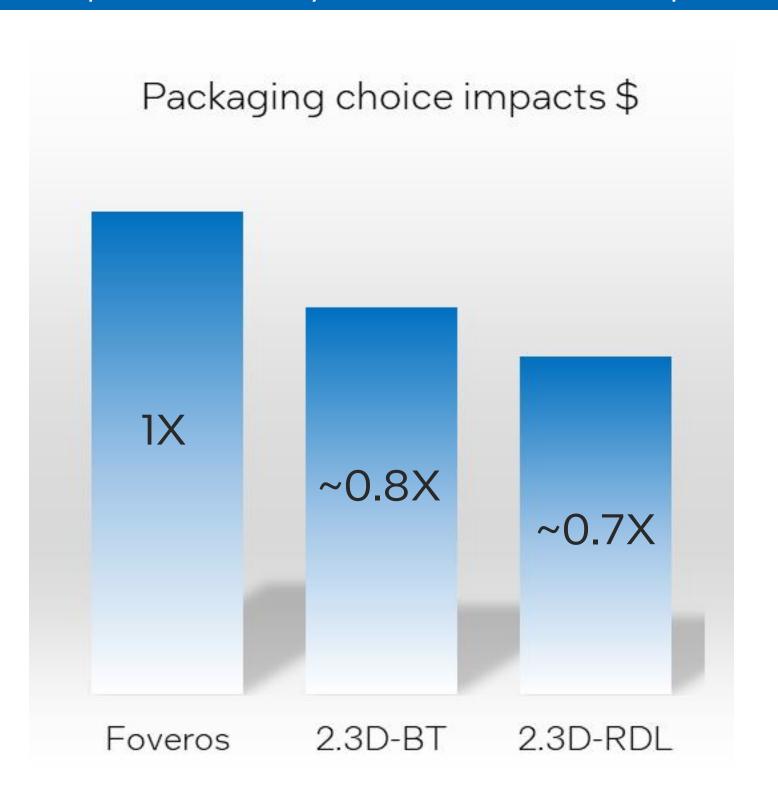

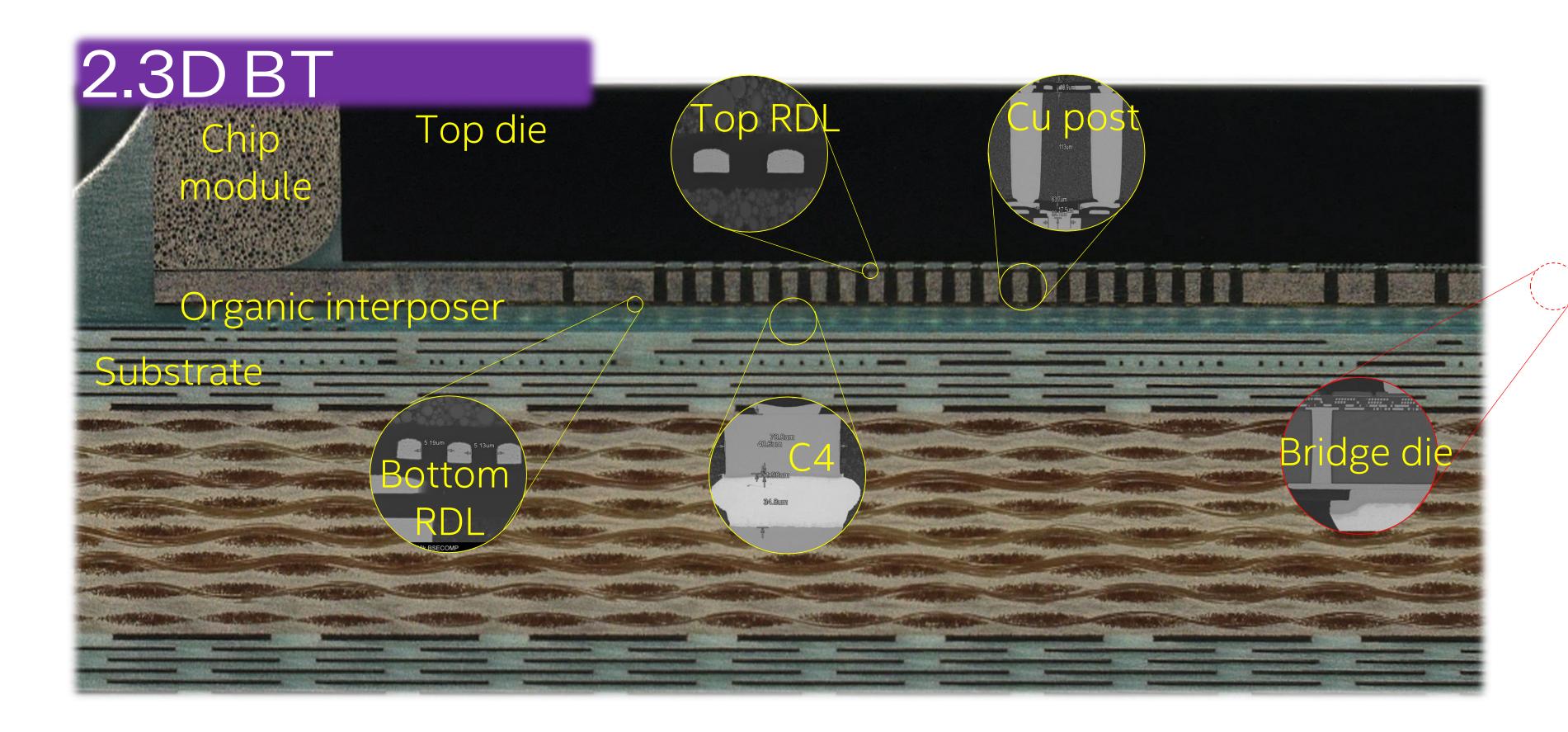

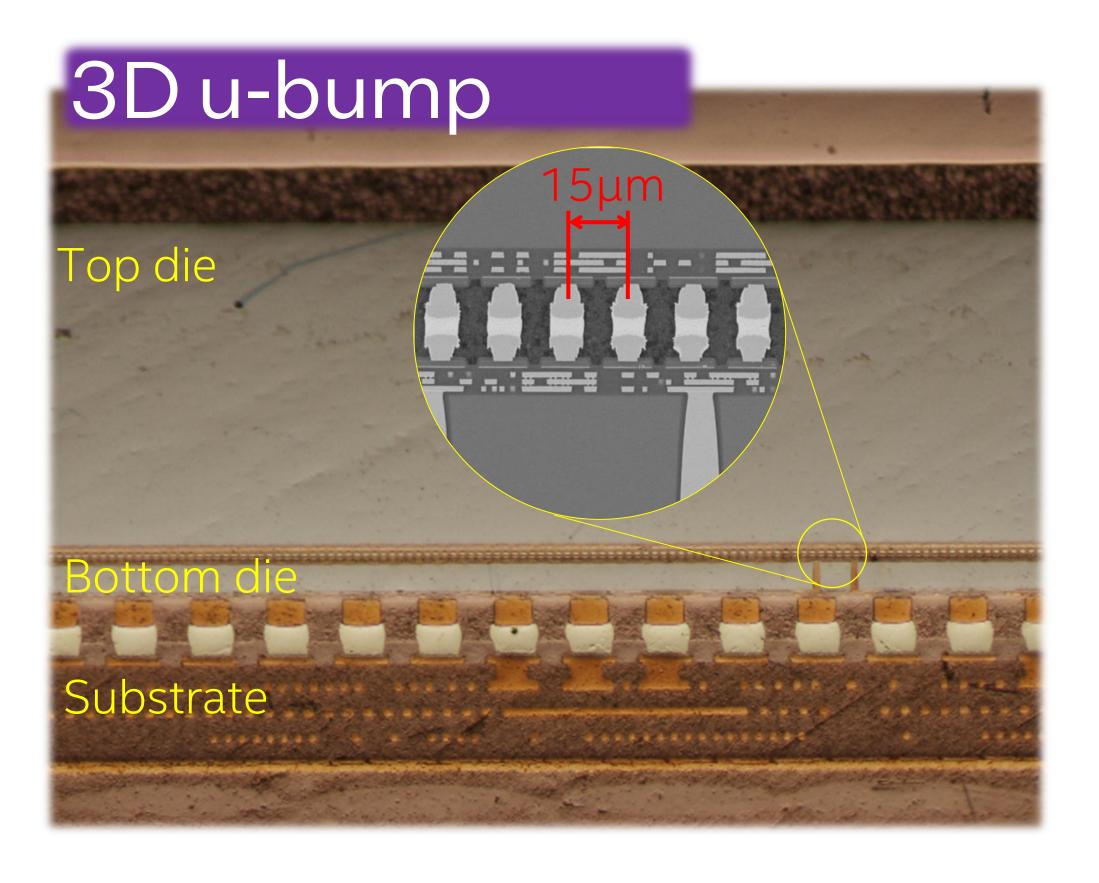

## External Packaging Technology Enablement

Advanced packaging solutions with external partners - Shorter Time-to-Market at lower cost -

#### Advanced Packaging

Variety of packaging options 2.3D BT

3D u-bump (15um pitch)

Co-design Flow

Assembly design kit (PDK)

25% Shorter Develop Time

#### Silicon Integration

Silicon from multiple sources Variety of silicon nodes At various OSATs

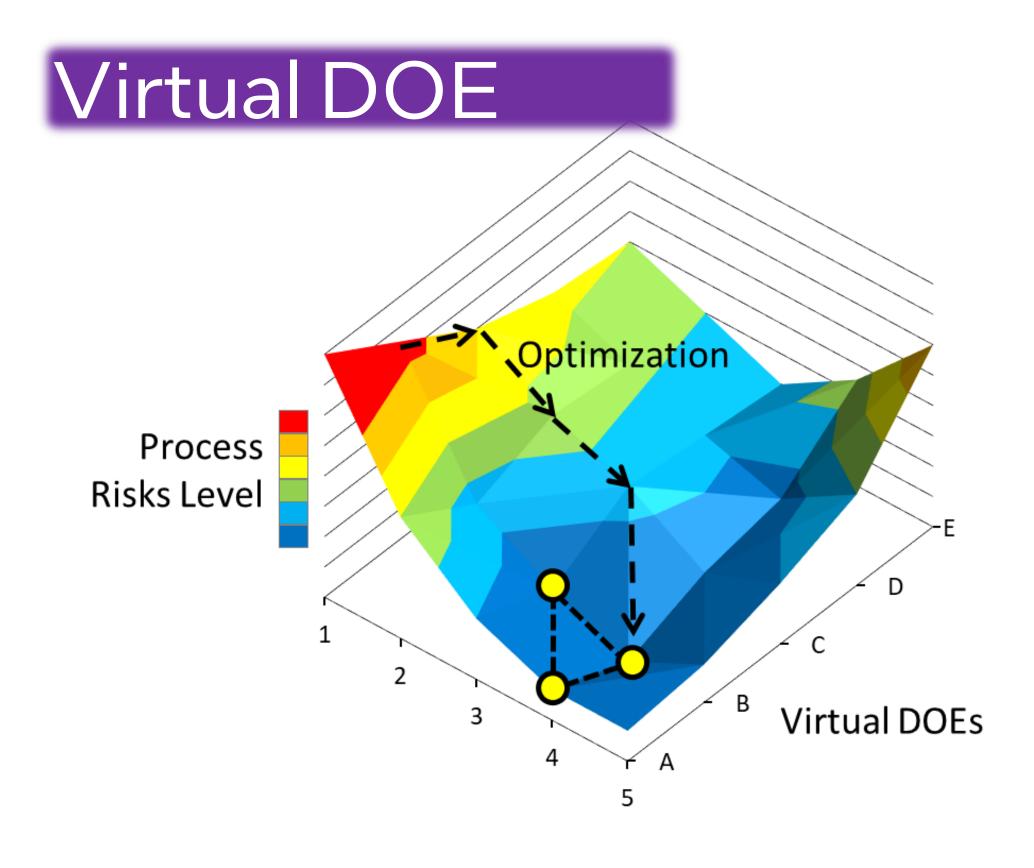

#### Virtual DOE

Reducing DOEs by 50% Reducing cycle time by >17 weeks

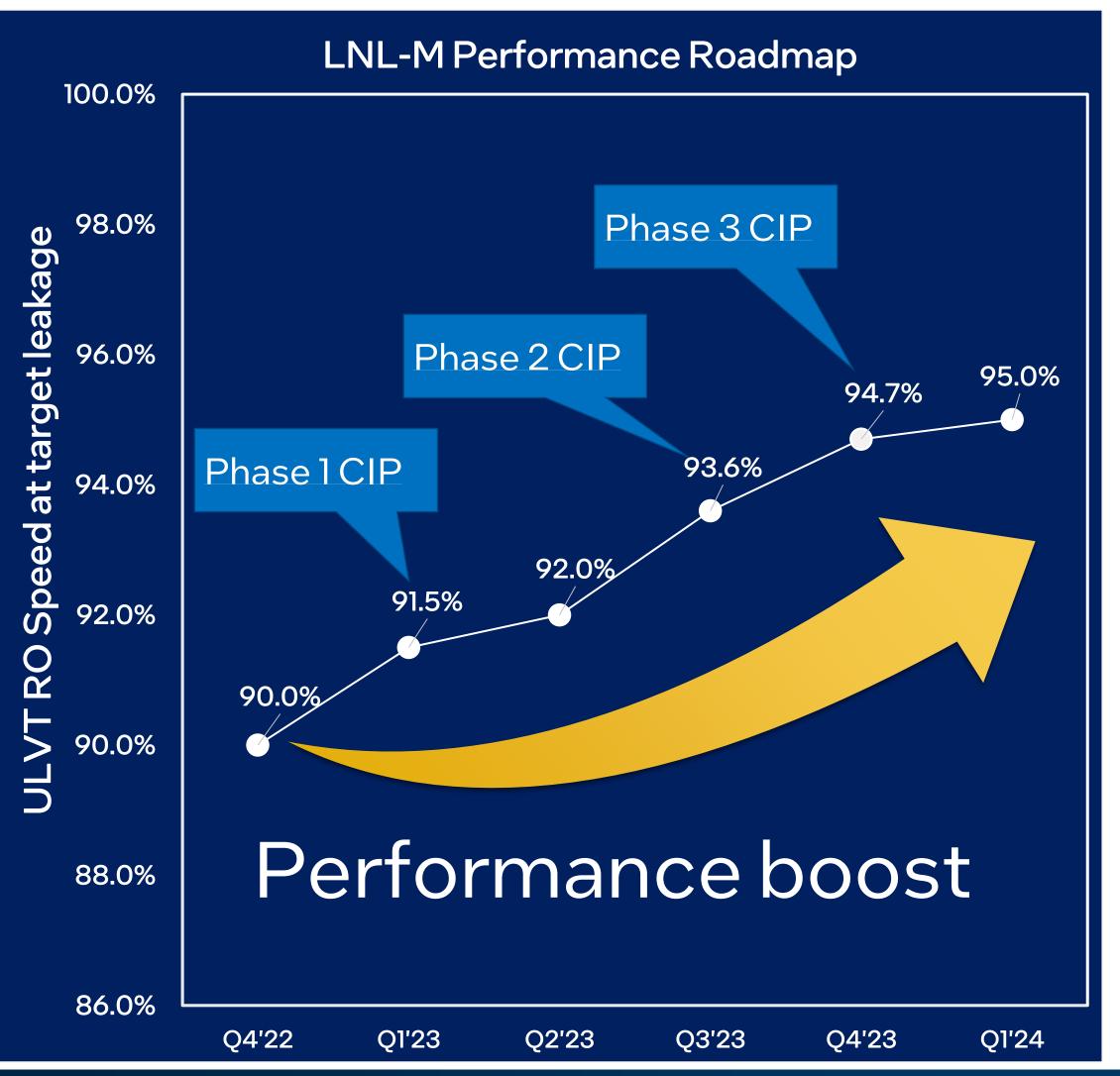

## PC Renaissance -

First Intel 47 TOPS AI PC - LNL is coming

#### Performance

Implemented 9 Process

Device CIPs to Boost

Performance

- Fmax +3% (+150MHz)

- Vmin -30 mV

- SMP +5%

Low Leakage

Reduce 20% stand-by power consumption meeting battery lifetime spec.

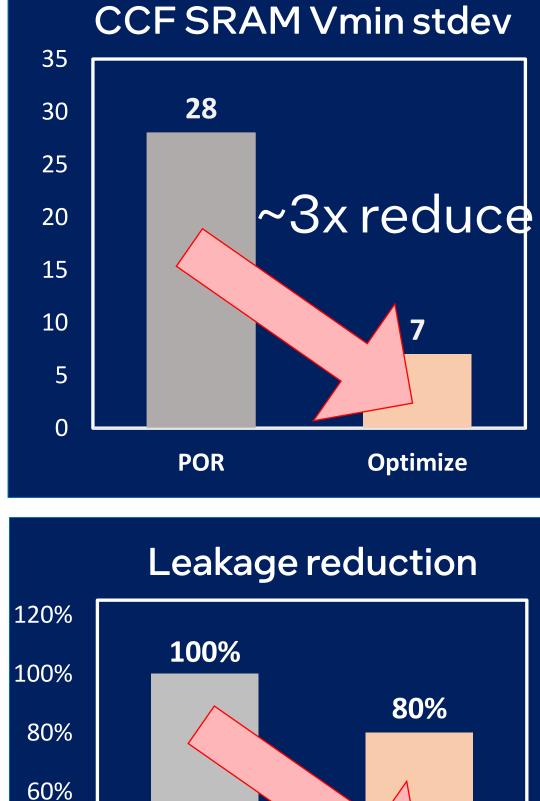

#### Quality

Optimized Process and Testing

Stable Array (1 \sigma Vmin<10mV)

Diagnostic De-bug flow

Tighten In-line control with

CP/CPK monitoring

>\$6B

Additional Revenue

Due to the Superior

Performance

#### ESG Value

Lower power consumption is estimated to potential carbon emission reduction by 146000tons annually.

#### Performance

#### Quality

~3x rec

POR

**Optimize**

#### ESG Value

Potential yearly 146000 tons CO<sub>2</sub> reduction

Equivalent to 5000 soccer field areas of trees to absorb!

40%

20%

0%

## Capacity Reporting evolved

The Foundry Capacity Report is a keystone record which centralizes critical data for external foundry planning

#### Data in...

#### ...Stitch Engine...

#### ...Information out

- 24-month wafer demand

- Supplier Capacity Response

- Orders, Shipments, Commits

#### Comprehensive

Single Source of Truth

**Enabling Analytics**

and the backbone of other supply planning reports and analysis among user base

# Cycle-on-cycle Supply constraint

#### Reporting evolution

2023 AUTOMATE

Massive automation upgrade 4x update freq.; 95% time savings Longer horizon, higher accuracy

With contributions from:

John Pete Sachin Rastogi Rob Olsztyn Bernhard Fiegl

#### 2024 ENTERPRISE

Shared DB structure

Custom PBI views

Auto-scheduled runs

#### 2024+ SCALE

Additional data sources

Integration with a full

suite of KPIs, dashboards